#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Active                                                                    |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A5                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 536MHz                                                                    |

| Co-Processors/DSP               | -                                                                         |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                                       |

| Graphics Acceleration           | No                                                                        |

| Display & Interface Controllers | LCD, Touchscreen                                                          |

| Ethernet                        | 10/100Mbps (1)                                                            |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.2V, 1.8V, 3.3V                                                          |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                         |

| Security Features               | AES, SHA, TDES, TRNG                                                      |

| Package / Case                  | 324-TFBGA                                                                 |

| Supplier Device Package         | 324-TFBGA (15x15)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d31a-cfu |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 15.10.7 Write Protect Status Register

| Name:    | MATRIX_WPSR |    |     |      |    |    |      |

|----------|-------------|----|-----|------|----|----|------|

| Address: | 0xFFFFEDE8  |    |     |      |    |    |      |

| Access:  | Read-only   |    |     |      |    |    |      |

| 31       | 30          | 29 | 28  | 27   | 26 | 25 | 24   |

| -        | -           | -  | -   | -    | -  | -  | -    |

| 23       | 22          | 21 | 20  | 19   | 18 | 17 | 16   |

|          |             |    | WPV | /SRC |    |    |      |

| 15       | 14          | 13 | 12  | 11   | 10 | 9  | 8    |

|          |             |    | WPV | /SRC |    |    |      |

| 7        | 6           | 5  | 4   | 3    | 2  | 1  | 0    |

| _        | -           | _  | -   | -    | -  | -  | WPVS |

For more details on MATRIX\_WPSR, refer to Section 15.9 "Write Protect Registers" on page 93.

# • WPVS: Write Protect Violation Status

0: No Write Protect Violation has occurred since the last write of the MATRIX\_WPMR.

1: At least one Write Protect Violation has occurred since the last write of the MATRIX\_WPMR.

# • WPVSRC: Write Protect Violation Source

When WPVS is active, this field indicates the register address offset in which a write access has been attempted. Otherwise it reads as 0.

# 16.3.3 APB Bridge Configuration Register

Name: SFR\_BRIDGE

Access: Read-write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24         |

|----|----|----|----|----|----|----|------------|

| _  | _  | -  | —  | -  | -  | -  | -          |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16         |

| -  | _  | -  | -  | -  | -  | -  | -          |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8          |

| -  | _  | I  | _  | I  | -  | -  | AXI2AHBSEL |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0          |

| _  | _  | _  | _  | _  | _  | _  | APBTURBO   |

# • APBTURBO: AHB to APB Bridge Mode

0: AHB transaction optimization disabled.

1: AHB transaction optimization enabled.

# • AXI2AHBSEL: AXI to AHB Bridge for DDR Controller Selection

0 (SINGLE): Uses single port bridge.

1 (DUAL): Uses dual port bridge.

| Figure 2 | 25-3. Fuse Write |    |            |    |    |            |

|----------|------------------|----|------------|----|----|------------|

| Clock    |                  |    |            |    | 1  |            |

| WSEL     | XX               | 00 | 1          | _X | 01 |            |

| DATA     | XX               | X  | Fuse[31:0] | >  | F  | use[63:32] |

| WRQ      |                  |    |            |    |    |            |

| WS       |                  |    |            |    |    |            |

| RS       |                  |    |            |    |    |            |

# 25.4.3 Fuse Masking

It is possible to mask the first 8 FUSE\_SRx registers so that they will be read at a value of '0', regardless of the fuse state.

To activate fuse masking on the first 8 FUSE\_SRx registers, the MSK bit of the Fuse Mode register (FUSE\_MR) must be written to level '1'. The MSK bit is write-only. Only a general reset can disable fuse masking.

#### 26.1.5.2 12 MHz Fast RC Oscillator Clock Frequency Adjustment

It is possible for the user to adjust the main RC oscillator frequency through PMC\_OCR. By default, SEL is low, so the RC oscillator is driven with fuse calibration bits which are programmed during the chip production.

The user can adjust the trimming of the 12 MHz Fast RC oscillator through the PMC\_OCR in order to obtain more accurate frequency (to compensate derating factors such as temperature and voltage).

In order to calibrate the 12 MHz oscillator frequency, SEL must be set to 1 and a correct frequency value must be configured in CAL.

It is possible to restart, at anytime, a measurement of the main frequency by means of the RCMEAS bit in Main Clock Frequency Register (CKGR\_MCFR). Thus, when MAINFRDY flag reads 1, another read access on CKGR\_MCFR provides an image of the frequency of the main clock on MAINF field. The software can calculate the error with an expected frequency and correct the CAL field accordingly. This may be used to compensate frequency drift due to derating factors such as temperature and/or voltage.

#### 26.1.5.3 8 to 48 MHz Crystal Oscillator

After reset, the 8 to 48 MHz Crystal Oscillator is disabled and it is not selected as the source of MAINCK.

The user can select the 8 to 48 MHz crystal oscillator to be the source of MAINCK, as it provides a more accurate frequency. The software enables or disables the main oscillator so as to reduce power consumption by clearing the MOSCXTEN bit in the Main Oscillator Register (CKGR\_MOR).

When disabling the main oscillator by clearing the MOSCXTEN bit in CKGR\_MOR, the MOSCXTS bit in PMC\_SR is automatically cleared, indicating the Main Clock is off.

When enabling the main oscillator, the user must initiate the main oscillator counter with a value corresponding to the startup time of the oscillator. This startup time depends on the crystal frequency connected to the oscillator.

When the MOSCXTEN bit and the MOSCXTCNT are written in CKGR\_MOR to enable the main oscillator, the MOSCXTS bit in the PMC\_SR is cleared and the counter starts counting down on the slow clock divided by 8 from the MOSCXTCNT value. Since the MOSCXTCNT value is coded with 8 bits, the maximum startup time is about 62 ms.

When the counter reaches 0, the MOSCXTS bit is set, indicating that the main clock is valid. Setting the MOSCXTS bit in PMC\_IMR can trigger an interrupt to the processor.

#### 26.1.5.4 Main Clock Oscillator Selection

The user can select either the 12 MHz Fast RC Oscillator or the Crystal Oscillator to be the source of Main Clock.

The selection is made by writing the MOSCSEL bit in the CKGR\_MOR. The switch of the Main Clock source is glitch free, so there is no need to run out of SLCK or PLLACK in order to change the selection. The MOSCSELS bit of the PMC\_SR indicates when the switch sequence is done.

Setting the MOSCSELS bit in PMC\_IMR can trigger an interrupt to the processor.

#### 26.1.5.5 Switching Main Clock between the Main RC Oscillator and Fast Crystal Oscillator

Both sources must be enabled during the switch operation. Only after completion can the unused oscillator be disabled. If switching to Fast Crystal Oscillator, the clock presence must first be checked according to what is described in Section 26.1.5.6 "Software Sequence to Detect the Presence of Fast Crystal" because the source may not be reliable (crystal failure or bypass on a non-existent clock).

#### 26.1.5.6 Software Sequence to Detect the Presence of Fast Crystal

The frequency meter carried on the CKGR\_MCFR is operating on the selected main clock and not on the fast crystal clock nor on the fast RC Oscillator clock.

Therefore, to check for the presence of the fast crystal clock, it is necessary to switch the main clock on the fast crystal clock.

The following software sequence must be followed (during this sequence the Main RC oscillator must be kept enabled (MOSCRCEN = 1)):

#### 29.5.2.1 All Banks Auto Refresh

The All Banks Auto Refresh command performs a refresh operation on all banks. An auto refresh command is used to refresh the MPDDRC. Refresh addresses are generated internally by the DDR-SDRAM device and incremented after each auto-refresh automatically. The MPDDRC generates these auto-refresh commands periodically. A timer is loaded in the MPDDRC\_RTR with the value that indicates the number of clock cycles between refresh cycles (see Section 29.8.2 "MPDDRC Refresh Timer Register"). When the MPDDRC initiates a refresh of the DDR-SDRAM device, internal memory accesses are not delayed. However, if the CPU tries to access the DDR-SDRAM device, the slave indicates that the device is busy. A refresh request does not interrupt a burst transfer in progress. This feature is activated by setting Per-bank Refresh bit (REF\_PB) to 0 in the MPDDRC\_RTR (see Section 29.8.2 "MPDDRC Refresh Timer Register").

#### 29.5.2.2 Per-bank Auto Refresh

The low-power DDR2-SDRAM embeds a new Per-bank Refresh command which performs a refresh operation on the bank scheduled by the bank counter in the memory device. The Per-bank Refresh command is executed in a fixed sequence order of round-robin type: "0-1-2-3-4-5-6-7-0-1-...". The bank counter is automatically cleared upon issuing a RESET command or when exiting from self-refresh mode, in order to ensure the synchronism between SDRAM memory device and the MPDDRC controller. The bank addressing for the Per-bank Refresh count is the same as established in the Single-bank Precharge command. This feature is activated by setting the Per-bank Refresh bit (REF\_PB) to 1 in the MPDDRC\_RTR (see Section 29.8.2 "MPDDRC Refresh Timer Register"). This feature masks the latency due to the refresh procedure. The target bank is inaccessible during the Per-bank Refresh cycle period (t<sub>RFCpb</sub>), however other banks within the device are accessible and may be addressed during the "Per-bank Refresh" cycle. During the REFpb operation, any bank other than the one being refreshed can be maintained in active state or accessed by a read or a write command. When the "Per-bank Refresh" cycle is completed, the affected bank will be in idle state.

#### 29.5.2.3 Adjust Auto Refresh Rate

The low-power DDR2-SDRAM embeds an internal register, Mode Register 19 (Refresh Mode). The content of this register allows to adjust the interval of auto-refresh operations according to temperature variation. This feature is activated by setting the Adjust Refresh bit [ADJ\_REF] to 1 in the MPDDRC\_RTR (see Section 29.8.2 "MPDDRC Refresh Timer Register"). When this feature is enabled, a mode register read command (MRR) is performed every 16 \* t<sub>REF1</sub> (average time between REFRESH commands). Depending on the read value, the auto refresh interval will be modified. In case of high temperature, the interval is reduced and in case of low temperature, the interval is increased.

#### 29.5.3 Power Management

#### 29.5.3.1 Self-refresh Mode

This mode is activated by writing a one to the Low-power Command bit (LPCB) in the MPDDRC\_LPR register.

Self-refresh mode is used in power-down mode, i.e., when no access to the DDR-SDRAM device is possible. In this case, power consumption is very low. In self-refresh mode, the DDR-SDRAM device retains data without external clocking and provides its own internal clocking, thus performing its own auto refresh cycles. During self-refresh period CKE is driven low. As soon as the DDR-SDRAM device is selected, the MPDDRC provides a sequence of commands and exits self-refresh mode.

The MPDDRC re-enables self-refresh mode as soon as the DDR-SDRAM device is not selected. It is possible to define when self-refresh mode is to be enabled by configuring the TIMEOUT field in the MPDDRC\_LPR register:

- 0: Self-refresh mode is enabled as soon as the DDR-SDRAM device is not selected.

- 1: Self-refresh mode is enabled 64 clock cycles after completion of the last access.

- 2: Self-refresh mode is enabled 128 clock cycles after completion of the last access.

This controller also interfaces the low-power DDR-SDRAM. To optimize power consumption, the Low Power DDR SDRAM provides programmable self-refresh options comprised of Partial Array Self Refresh (full, half, quarter and 1/8 and 1/16 array).

Disabled banks are not refreshed in self-refresh mode. This feature permits to reduce the self-refresh current. In case of low-power DDR1-SDRAM, the Extended Mode register controls this feature. It includes Temperature Compensated Self-refresh (TSCR) and Partial Array Self-refresh (PASR) parameters and the drive strength (DS) (see Section 29.8.7)

## 32.6.15 Input FIFO

The LCD module includes one input FIFO per overlay. These input FIFOs are used to buffer the AHB burst and serialize the stream of pixels.

## 32.6.16 Output FIFO

The LCD module includes one output FIFO that stores the blended pixel.

# 32.7.1 LCD Controller Configuration Register 0

| Name:    | LCDC_LCDCFG | 0       |          |           |           |           |           |

|----------|-------------|---------|----------|-----------|-----------|-----------|-----------|

| Address: | 0xF0030000  |         |          |           |           |           |           |

| Access:  | Read-write  |         |          |           |           |           |           |

| Reset:   | 0x00000000  |         |          |           |           |           |           |

| 31       | 30          | 29      | 28       | 27        | 26        | 25        | 24        |

| -        | -           | _       | _        | -         | -         | _         | -         |

| 23       | 22          | 21      | 20       | 19        | 18        | 17        | 16        |

|          |             |         | CLM      | (DIV      |           |           |           |

| 15       | 14          | 13      | 12       | 11        | 10        | 9         | 8         |

| -        | -           | CGDISPP | CGDISHCR | CGDISHEO  | CGDISOVR2 | CGDISOVR1 | CGDISBASE |

| 7        | 6           | 5       | 4        | 3         | 2         | 1         | 0         |

| _        | -           | _       | —        | CLKPWMSEL | CLKSEL    | _         | CLKPOL    |

## • CLKPOL: LCD Controller Clock Polarity

- 0: Data/Control signals are launched on the rising edge of the Pixel Clock.

- 1: Data/Control signals are launched on the falling edge of the Pixel Clock.

## CLKSEL: LCD Controller Clock Source Selection

- 0: The Asynchronous output stage of the LCD controller is fed by the System Clock.

- 1: The Asynchronous output state of the LCD controller is fed by the 2x System Clock.

## CLKPWMSEL: LCD Controller PWM Clock Source Selection

- 0: The slow clock is selected and feeds the PWM module.

- 1: The system clock is selected and feeds the PWM module.

# • CGDISBASE: Clock Gating Disable Control for the Base Layer

- 0: Automatic Clock Gating is enabled for the Base Layer.

- 1: Clock is running continuously.

# CGDISOVR1: Clock Gating Disable Control for the Overlay 1 Layer

- 0: Automatic Clock Gating is enabled for the Overlay 1 Layer.

- 1: Clock is running continuously.

# • CGDISOVR2: Clock Gating Disable Control for the Overlay 2 Layer

- 0: Automatic Clock Gating is enabled for the Overlay 2 Layer.

- 1: Clock is running continuously.

# • CGDISHEO: Clock Gating Disable Control for the High End Overlay

- 0: Automatic Clock Gating is enabled for the High End Overlay Layer.

- 1: Clock is running continuously.

# • CGDISHCR: Clock Gating Disable Control for the Hardware Cursor Layer

- 0: Automatic Clock Gating is enabled for the Hardware Cursor Layer.

- 1: Clock is running continuously.

# 32.7.27 Base Layer Configuration 0 Register

| Name:<br>Address:<br>Access: | LCDC_BASECFG0<br>0xF003006C<br>Read-write |    |     |    |    |    |      |  |

|------------------------------|-------------------------------------------|----|-----|----|----|----|------|--|

| Reset:                       | 0x00000000                                |    |     |    |    |    |      |  |

| 31                           | 30                                        | 29 | 28  | 27 | 26 | 25 | 24   |  |

| -                            | -                                         | _  | _   | -  | -  | -  | -    |  |

| 23                           | 22                                        | 21 | 20  | 19 | 18 | 17 | 16   |  |

| -                            | -                                         | –  | -   | -  | -  | -  | -    |  |

| 15                           | 14                                        | 13 | 12  | 11 | 10 | 9  | 8    |  |

| -                            | -                                         | —  | -   | -  | -  | -  | DLBO |  |

| 7                            | 6                                         | 5  | 4   | 3  | 2  | 1  | 0    |  |

| _                            | _                                         | В  | LEN | -  | -  | -  | SIF  |  |

## • SIF: Source Interface

0: Base Layer data is retrieved through AHB interface 0.

1: Base Layer data is retrieved through AHB interface 1.

## • BLEN: AHB Burst Length

| Value | Name       | Description                                                                                                                                                                                                                                 |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | AHB_SINGLE | AHB Access is started as soon as there is enough space in the FIFO to store one data. SINGLE, INCR, INCR4, INCR8 and INCR16 bursts are used. INCR is used for a burst of 2 and 3 beats.                                                     |

| 1     | AHB_INCR4  | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 4 data.<br>An AHB INCR4 Burst is used. SINGLE, INCR and INCR4 bursts are used. INCR is used for a burst of 2<br>and 3 beats.                  |

| 2     | AHB_INCR8  | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 8 data.<br>An AHB INCR8 Burst is used. SINGLE, INCR, INCR4 and INCR8 bursts are used. INCR is used for a<br>burst of 2 and 3 beats.           |

| 3     | AHB_INCR16 | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 16 data.<br>An AHB INCR16 Burst is used. SINGLE, INCR, INCR4, INCR8 and INCR16 bursts are used. INCR is<br>used for a burst of 2 and 3 beats. |

# • DLBO: Defined Length Burst Only For Channel Bus Transaction.

0: Undefined length INCR burst is used for a burst of 2 and 3 beats.

1: Only Defined Length burst is used (SINGLE, INCR4, INCR8 and INCR16).

# 32.7.32 Base Layer Configuration 5 Register

| Name:    | LCDC_BASECFO | 95 |      |      |    |          |    |  |

|----------|--------------|----|------|------|----|----------|----|--|

| Address: | 0xF0030080   |    |      |      |    |          |    |  |

| Access:  | Read-write   |    |      |      |    |          |    |  |

| Reset:   | 0x00000000   |    |      |      |    |          |    |  |

| 31       | 30           | 29 | 28   | 27   | 26 | 25       | 24 |  |

| -        | -            | _  | -    | —    |    | DISCYPOS |    |  |

| 23       | 22           | 21 | 20   | 19   | 18 | 17       | 16 |  |

|          |              |    | DISC | YPOS |    |          |    |  |

| 15       | 14           | 13 | 12   | 11   | 10 | 9        | 8  |  |

| -        | -            | _  | -    |      |    | DISCXPOS |    |  |

| 7        | 6            | 5  | 4    | 3    | 2  | 1        | 0  |  |

|          |              |    | DISC | XPOS |    |          |    |  |

## • DISCXPOS: Discard Area horizontal coordinate

Horizontal Position of the Discard Area.

# • DISCYPOS: Discard Area Vertical coordinate

Vertical Position of the Discard Area.

# 32.7.121High End Overlay Layer Configuration 26 Register

| Name:    | LCDC_HEOCFG26 |    |        |       |    |    |    |

|----------|---------------|----|--------|-------|----|----|----|

| Address: | 0xF00303F4    |    |        |       |    |    |    |

| Access:  | Read-write    |    |        |       |    |    |    |

| Reset:   | 0x00000000    |    |        |       |    |    |    |

| 31       | 30            | 29 | 28     | 27    | 26 | 25 | 24 |

| -        | -             | _  | -      | -     | -  | -  | -  |

| 23       | 22            | 21 | 20     | 19    | 18 | 17 | 16 |

| _        | -             | _  | -      | -     | -  | -  | -  |

| 15       | 14            | 13 | 12     | 11    | 10 | 9  | 8  |

| _        | -             | _  | -      | -     | _  | _  | -  |

| 7        | 6 5 4 3 2 1 0 |    |        |       |    |    |    |

|          |               |    | XPHI40 | OEFF4 |    |    |    |

# • XPHI4COEFF4: Horizontal Coefficient for phase 4 tap 4

Coefficient format is 1 sign bit and 7 fractional bits.

- RXRDY\_TXKL: Received OUT Data Interrupt Enable

- 0: No effect.

- 1: Enable Received OUT Data Interrupt.

# 37.6.8 Interrupt Status Register

| Name:    | EMAC_ISR   |      |      |       |       |       |     |

|----------|------------|------|------|-------|-------|-------|-----|

| Address: | 0xF802C024 |      |      |       |       |       |     |

| Access:  | Read-write |      |      |       |       |       |     |

| 31       | 30         | 29   | 28   | 27    | 26    | 25    | 24  |

| -        | -          | -    | -    | -     | -     | -     | -   |

| 23       | 22         | 21   | 20   | 19    | 18    | 17    | 16  |

| -        | -          | -    | -    | -     | -     | -     | -   |

| 15       | 14         | 13   | 12   | 11    | 10    | 9     | 8   |

| -        | WOL        | PTZ  | PFRE | HRESP | ROVR  | -     | -   |

| 7        | 6          | 5    | 4    | 3     | 2     | 1     | 0   |

| TCOMP    | TXERR      | RLEX | TUND | TXUBR | RXUBR | RCOMP | MFD |

#### • MFD: Management Frame Done

The PHY maintenance register has completed its operation. Cleared on read.

#### • RCOMP: Receive Complete

A frame has been stored in memory. Cleared on read.

#### • RXUBR: Receive Used Bit Read

Set when a receive buffer descriptor is read with its used bit set. Cleared on read.

#### • TXUBR: Transmit Used Bit Read

Set when a transmit buffer descriptor is read with its used bit set. Cleared on read.

#### • TUND: Ethernet Transmit Buffer Underrun

The transmit DMA did not fetch frame data in time for it to be transmitted or hresp returned not OK. Also set if a used bit is read mid-frame or when a new transmit queue pointer is written. Cleared on read.

#### • RLEX: Retry Limit Exceeded

Cleared on read.

## • TXERR: Transmit Error

Transmit buffers exhausted in mid-frame - transmit error. Cleared on read.

#### • TCOMP: Transmit Complete

Set when a frame has been transmitted. Cleared on read.

#### • ROVR: Receive Overrun

Set when the receive overrun status bit gets set. Cleared on read.

#### • HRESP: Hresp not OK

Set when the DMA block sees a bus error. Cleared on read.

Atmel

- 9. Read the penultimate character in TWI\_RHR.

- 10. Wait for the RXRDY flag in the TWI\_SR.

- 11. Read the last character in TWI\_RHR.

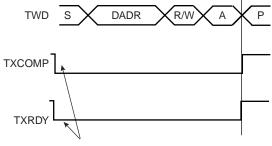

- 12. (Optional) Wait for the TXCOMP flag in TWI\_SR before disabling the peripheral clock if required.

# 40.8.8 SMBUS Quick Command (Master Mode Only)

The TWI interface can perform a Quick Command:

- 1. Configure the master mode (DADR, CKDIV, etc.).

- 2. Write the MREAD bit in the TWI\_MMR at the value of the one-bit command to be sent.

- 3. Start the transfer by setting the QUICK bit in the TWI\_CR.

## Figure 40-15.SMBUS Quick Command

Write QUICK command in TWI\_CR

# 40.8.9 Read-write Flowcharts

The following flowcharts shown in Figure 40-17 on page 1246, Figure 40-18 on page 1247, Figure 40-19 on page 1248, Figure 40-20 on page 1249 and Figure 40-21 on page 1250 give examples for read and write operations. A polling or interrupt method can be used to check the status bits. The interrupt method requires that the interrupt enable register (TWI\_IER) be configured first.

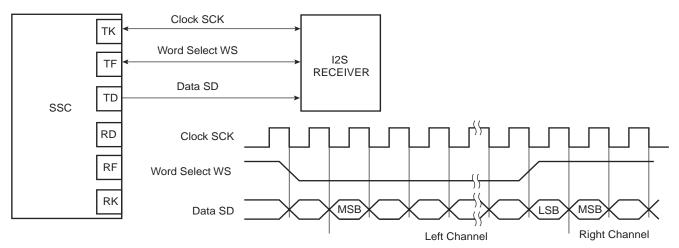

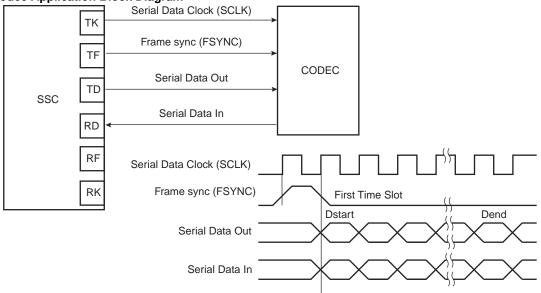

# 41.8 SSC Application Examples

The SSC can support several serial communication modes used in audio or high speed serial links. Some standard applications are shown in the following figures. All serial link applications supported by the SSC are not listed here.

#### Figure 41-17. Audio Application Block Diagram

#### Figure 41-18.Codec Application Block Diagram

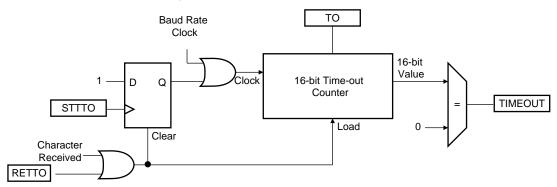

If STTTO is performed, the counter clock is stopped until a first character is received. The idle state on RXD before the start of the frame does not provide a time-out. This prevents having to obtain a periodic interrupt and enables a wait of the end of frame when the idle state on RXD is detected.

If RETTO is performed, the counter starts counting down immediately from the value TO. This enables generation of a periodic interrupt so that a user time-out can be handled, for example when no key is pressed on a keyboard.

Figure 44-24 shows the block diagram of the Receiver Time-out feature.

#### Figure 44-24.Receiver Time-out Block Diagram

Table 44-11 gives the maximum time-out period for some standard baud rates.

| Baud Rate (Bit/s) | Bit Time (µs) | Time-out (ms) |

|-------------------|---------------|---------------|

| 600               | 1,667         | 109,225       |

| 1,200             | 833           | 54,613        |

| 2,400             | 417           | 27,306        |

| 4,800             | 208           | 13,653        |

| 9,600             | 104           | 6,827         |

| 14,400            | 69            | 4,551         |

| 19,200            | 52            | 3,413         |

| 28,800            | 35            | 2,276         |

| 38,400            | 26            | 1,704         |

| 56,000            | 18            | 1,170         |

| 57,600            | 17            | 1,138         |

| 200,000           | 5             | 328           |

#### Table 44-11. Maximum Time-out Period

#### 44.7.3.12 Framing Error

The receiver is capable of detecting framing errors. A framing error happens when the stop bit of a received character is detected at level 0. This can occur if the receiver and the transmitter are fully desynchronized.

A framing error is reported on the FRAME bit of the Channel Status Register (US\_CSR). The FRAME bit is asserted in the middle of the stop bit as soon as the framing error is detected. It is cleared by writing the Control Register (US\_CR) with the RSTSTA bit to 1.

# • DRPT: Disable Repeat

0: When a transmit mailbox loses the bus arbitration, the transfer request remains pending.

1: When a transmit mailbox lose the bus arbitration, the transfer request is automatically aborted. It automatically raises the MABT and MRDT flags in the corresponding CAN\_MSRx.

| Mailbox Object Type    | Description                                                                                                                                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive with overwrite | Set when at least two messages intended for the mailbox have been sent. The last one is available in the mailbox data register. Previous ones have been lost.                                                                                |

| Transmit               | Reserved                                                                                                                                                                                                                                     |

| Consumer               | A remote frame has been sent by the mailbox but several messages have been received. The first one is available in the mailbox data register. Others have been ignored. Another mailbox with a lower priority may have accepted the message. |

| Producer               | A remote frame has been received, but no data are available to be sent.                                                                                                                                                                      |

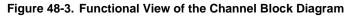

#### 48.6.2 PWM Channel

#### 48.6.2.1 Channel Block Diagram

Each of the 4 channels is composed of six blocks:

- A clock selector which selects one of the clocks provided by the clock generator (described in Section 48.6.1 on page 1550).

- A counter clocked by the output of the clock selector. This counter is incremented or decremented according to the channel configuration and comparators matches. The size of the counter is 16 bits.

- A comparator used to compute the OCx output waveform according to the counter value and the configuration. The counter value can be the one of the channel counter or the one of the channel 0 counter according to SYNCx bit in the "PWM Sync Channels Mode Register" (PWM\_SCM).

- A 2-bit configurable gray counter enables the stepper motor driver. One gray counter drives 2 channels.

- A dead-time generator providing two complementary outputs (DTOHx/DTOLx) which allows to drive external power control switches safely.

- An output override block that can force the two complementary outputs to a programmed value (OOOHx/OOOLx).

- An asynchronous fault protection mechanism that has the highest priority to override the two complementary outputs (PWMHx/PWMLx) in case of fault detection (outputs forced to '0', '1').

# 51.6.3 AES Interrupt Enable Register

| Name:    | AES_IER    |    |    |    |    |    |        |

|----------|------------|----|----|----|----|----|--------|

| Address: | 0xF8038010 |    |    |    |    |    |        |

| Access:  | Write-only |    |    |    |    |    |        |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24     |

| -        | -          | _  | -  | -  | _  | _  | -      |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16     |

| _        | -          | _  | _  | _  | _  | _  | _      |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8      |

| _        | _          | _  | _  | _  | _  | _  | URAD   |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0      |

| _        | _          | _  | -  | _  | _  | -  | DATRDY |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Enables the corresponding interrupt.

- DATRDY: Data Ready Interrupt Enable

- URAD: Unspecified Register Access Detection Interrupt Enable

# 53.5.6 SHA Interrupt Status Register

| Name:    | SHA_ISR    |      |    |    |    |    |        |

|----------|------------|------|----|----|----|----|--------|

| Address: | 0xF803401C |      |    |    |    |    |        |

| Access:  | Read-only  |      |    |    |    |    |        |

| 31       | 30         | 29   | 28 | 27 | 26 | 25 | 24     |

| _        | -          | _    | _  | _  | _  | _  | _      |

| 23       | 22         | 21   | 20 | 19 | 18 | 17 | 16     |

| -        | -          | -    | _  | -  | _  | _  | -      |

| 15       | 14         | 13   | 12 | 11 | 10 | 9  | 8      |

|          |            | URAT |    | _  | _  | _  | URAD   |

| 7        | 6          | 5    | 4  | 3  | 2  | 1  | 0      |

| _        | _          | _    | _  | _  | _  | _  | DATRDY |

## • DATRDY: Data Ready

0: Output data is not valid.

1: 512-bit block process is completed.

DATRDY is cleared when a Manual process occurs (START bit in SHA\_CR) or when a software triggered hardware reset of the SHA interface is performed (SWRST bit in SHA\_CR).

## • URAD: Unspecified Register Access Detection Status

0: No unspecified register access has been detected since the last SWRST.

1: At least one unspecified register access has been detected since the last SWRST.

URAD bit is reset only by the SWRST bit in the SHA\_CR control register.

URAT field indicates the unspecified access type.

# • URAT: Unspecified Register Access Type

| Value | Description                                                                                                                                         |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x0   | Input Data Register 0 to 15 written during the data processing in DMA mode. (URAD=0x1 and URAT=0x0 can occur only if DUALBUFF is cleared in SHA_MR) |  |  |

| 0x1   | Output Data Register read during the data processing.                                                                                               |  |  |

| 0x2   | Mode Register written during the data processing.                                                                                                   |  |  |

| 0x3   | Write-only register read access.                                                                                                                    |  |  |

Only the last Unspecified Register Access Type is available through the URAT field.

URAT field is reset only by the SWRST bit in the SHA\_CR control register.