## Microchip Technology - ATSAMA5D31A-CU Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

ĿХF

| Product Status                  | Active                                                                   |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A5                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 536MHz                                                                   |

| Co-Processors/DSP               | -                                                                        |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                                      |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | LCD, Touchscreen                                                         |

| Ethernet                        | 10/100Mbps (1)                                                           |

| SATA                            | -                                                                        |

| USB                             | USB 2.0 (3)                                                              |

| Voltage - I/O                   | 1.2V, 1.8V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                        |

| Security Features               | AES, SHA, TDES, TRNG                                                     |

| Package / Case                  | 324-LFBGA                                                                |

| Supplier Device Package         | 324-LFBGA (15x15)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d31a-cu |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |            |          | Primary Alterna |     | ate PIO Peripheral A |     | PIO Peripheral B |     | PIO Peripheral C |     | Reset State |     |                              |

|-----------|------------|----------|-----------------|-----|----------------------|-----|------------------|-----|------------------|-----|-------------|-----|------------------------------|

|           |            |          |                 |     |                      |     |                  |     |                  |     |             |     | Signal, Dir,<br>PU, PD, HiZ, |

| Pin       | Power Rail | I/O Type | Signal          | Dir | Signal               | Dir | Signal           | Dir | Signal           | Dir | Signal      | Dir | ST                           |

| P13       | VDDIOM     | EBI      | PE0             | I/O | -                    |     | A0/NBS0          | 0   | -                | -   | -           |     | A,I, PD, ST                  |

| R14       | VDDIOM     | EBI      | PE1             | I/O | _                    | -   | A1               | 0   | _                | -   | _           | -   | A,I, PD, ST                  |

| R13       | VDDIOM     | EBI      | PE2             | I/O | _                    | —   | A2               | 0   | -                | —   | -           |     | A,I, PD, ST                  |

| V18       | VDDIOM     | EBI      | PE3             | I/O | -                    | -   | A3               | 0   | _                | _   | -           | -   | A,I, PD, ST                  |

| P14       | VDDIOM     | EBI      | PE4             | I/O | -                    | —   | A4               | 0   | _                | —   | -           | —   | A,I, PD, ST                  |

| U18       | VDDIOM     | EBI      | PE5             | I/O |                      | -   | A5               | 0   |                  | -   |             | -   | A,I, PD, ST                  |

| T18       | VDDIOM     | EBI      | PE6             | I/O | -                    | —   | A6               | 0   | —                | —   | -           | —   | A,I, PD, ST                  |

| R15       | VDDIOM     | EBI      | PE7             | I/O | -                    | _   | A7               | 0   | _                | _   | -           | _   | A,I, PD, ST                  |

| P17       | VDDIOM     | EBI      | PE8             | I/O | _                    | _   | A8               | 0   | _                | _   | _           | —   | A,I, PD, ST                  |

| P15       | VDDIOM     | EBI      | PE9             | I/O | -                    |     | A9               | 0   | -                | -   | -           | -   | A,I, PD, ST                  |

| P18       | VDDIOM     | EBI      | PE10            | I/O | -                    | —   | A10              | 0   | -                | —   | -           |     | A,I, PD, ST                  |

| R16       | VDDIOM     | EBI      | PE11            | I/O | _                    | —   | A11              | 0   | _                | —   | _           | —   | A,I, PD, ST                  |

| N16       | VDDIOM     | EBI      | PE12            | I/O | _                    | _   | A12              | 0   | _                | —   | _           | _   | A,I, PD, ST                  |

| R17       | VDDIOM     | EBI      | PE13            | I/O | _                    | _   | A13              | 0   | _                | _   | _           | _   | A,I, PD, ST                  |

| N17       | VDDIOM     | EBI      | PE14            | I/O | _                    | _   | A14              | 0   | _                | _   | _           | _   | A,I, PD, ST                  |

| R18       | VDDIOM     | EBI      | PE15            | I/O | -                    | —   | A15              | 0   | SCK3             | I/O | -           | _   | A,I, PD, ST                  |

| N18       | VDDIOM     | EBI      | PE16            | I/O | -                    | —   | A16              | 0   | CTS3             | I   | _           | _   | A,I, PD, ST                  |

| P16       | VDDIOM     | EBI      | PE17            | I/O | _                    | —   | A17              | 0   | RTS3             | 0   | _           | —   | A,I, PD, ST                  |

| M18       | VDDIOM     | EBI      | PE18            | I/O | -                    | _   | A18              | 0   | RXD3             | 1   | -           | _   | A,I, PD, ST                  |

| N15       | VDDIOM     | EBI      | PE19            | I/O | -                    | _   | A19              | 0   | TXD3             | 0   | -           | —   | A,I, PD, ST                  |

| M15       | VDDIOM     | EBI      | PE20            | I/O | _                    | _   | A20              | 0   | SCK2             | I/O | _           | _   | A,I, PD, ST                  |

| N14       | VDDIOM     | EBI      | PE21            | I/O | _                    | _   | A21/NANDALE      | 0   | _                | —   | _           | _   | A,I, PD, ST                  |

| M17       | VDDIOM     | EBI      | PE22            | I/O | _                    | _   | A22/NANDCLE      | 0   | _                | _   | _           | _   | A,I, PD, ST                  |

| M13       | VDDIOM     | EBI      | PE23            | I/O | _                    | _   | A23              | 0   | CTS2             | I   | _           | _   | A,I, PD, ST                  |

| M16       | VDDIOM     | EBI      | PE24            | I/O | _                    | _   | A24              | 0   | RTS2             | 0   | _           | _   | A,I, PD, ST                  |

| N12       | VDDIOM     | EBI      | PE25            | I/O | _                    | _   | A25              | 0   | RXD2             | I   | _           | _   | A,I, PD, ST                  |

| M14       | VDDIOM     | EBI      | PE26            | I/O | _                    | _   | NCS0             | 0   | TXD2             | 0   | _           | _   | A,I, PD, ST                  |

| M12       | VDDIOM     | EBI      | PE27            | I/O | _                    | -   | NCS1             | 0   | TIOA2            | I/O | LCDDAT22    | 0   | PIO,I, PD, ST                |

| L13       | VDDIOM     | EBI      | PE28            | I/O | _                    |     | NCS2             | 0   | TIOB2            | I/O | LCDDAT23    | 0   | PIO, I, PD, ST               |

| L15       | VDDIOM     | EBI      | PE29            | I/O | _                    | _   | NWR1/NBS1        | 0   | TCLK2            | I   | _           | _   | PIO, I, PD, ST               |

| L14       | VDDIOM     | EBI      | PE30            | I/O | _                    | _   | NWAIT            | I   | _                | _   | _           | _   | PIO, I, PD, ST               |

| L16       | VDDIOM     | EBI      | PE31            | I/O | _                    | _   | IRQ              | 1   | PWML1            | 0   | _           | _   | PIO,I, PD, ST                |

| U15       | VDDBU      | SYSC     | TST             | I   | _                    | _   | _                | _   | _                | _   | _           | _   | I, PD,                       |

| U9        | VDDIOP0    | SYSC     | BMS             | 1   | _                    | _   | _                | _   | _                | _   | _           | _   | 1                            |

| U8        | VDDIOP0    | CLOCK    | XIN             | 1   | _                    |     | _                | _   | _                | _   | _           |     | I                            |

| V8        | VDDIOP0    | CLOCK    | XOUT            | 0   | _                    | _   | _                | _   | _                | _   | _           | _   | 0                            |

| U16       | VDDBU      | CLOCK    | XIN32           | 1   | _                    | _   | _                | _   | _                | _   | _           | _   | -                            |

| V16       | VDDBU      | CLOCK    | XOUT32          | 0   | _                    | _   | _                | _   | _                | _   | _           | _   | 0                            |

| T12       | VDDBU      | SYSC     | SHDN            | 0   | _                    | _   | _                | _   | _                | _   | _           |     | 0                            |

| T10       | VDDBU      | SYSC     | WKUP            | 1   | _                    | _   | _                |     | _                |     | _           | _   | I, ST                        |

| V9        | VDDIOP0    | RSTJTAG  | NRST            | I/O | _                    |     |                  |     | _                |     | _           | _   | I, PU, ST                    |

| V9<br>P11 | VDDIOP0    | RSTJTAG  | NTRST           | 1/0 | _                    | _   |                  |     | _                |     | _           | _   | I, PU, ST                    |

|           | VDDIOP0    | RSTJTAG  | TDI             |     |                      |     |                  | _   |                  | _   |             |     |                              |

| R8        | VDDIOPU    | KSTJTAG  | IDI             | I   | —                    |     |                  | _   | —                |     | _           | —   | I, ST                        |

## Table 4-1. SAMA5D3 Pinout for 324-ball LFBGA Package (Continued)

Atmel

# 5. Power Considerations

# 5.1 Power Supplies

Table 5-1 defines the power supply rails and the estimated power consumption at typical voltage.

| Name     | Voltage Range, Nominal             | Associated Ground | Powers                                                                                           |

|----------|------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|

| VDDCORE  | 1.1–1.32V, 1.2V                    | GNDCORE           | The core, including the processor, the embedded memories and the peripherals                     |

| VDDIODDR | 1.7–1.9V, 1.8V                     | GNDIODDR          | LPDDR/DDR2 Interface I/O lines                                                                   |

| VDDIODDK | 1.14–1.30, 1.2V                    | GINDIODDK         | LPDDR2 Interface I/O lines                                                                       |

| VDDIOM   | 1.65–1.95V, 1.8V<br>3.0–3.6V, 3.3V | GNDIOM            | NAND and HSMC Interface I/O lines                                                                |

| VDDIOP0  | 1.65–3.6V                          | GNDIOP            | Peripheral I/O lines                                                                             |

| VDDIOP1  | 1.65–3.6V                          | GNDIOP            | Peripheral I/O lines                                                                             |

| VDDBU    | DDBU 1.65–3.6V GNDBU               |                   | The Slow Clock Oscillator, the internal 32 kHz RC Oscillator and a part of the System Controller |

| VDDUTMIC | 1.1–1.32V, 1.2V                    | GNDUTMI           | The USB device and host UTMI+ core<br>The UTMI PLL                                               |

| VDDUTMII | 3.0–3.6V, 3.3V                     | GNDUTMI           | The USB device and host UTMI+ interface                                                          |

| VDDPLLA  | 1.1–1.32V, 1.2V                    | GNDPLL            | The PLLA cell                                                                                    |

| VDDOSC   | 1.65–3.6V                          | GNDOSC            | Main Oscillator Cell and PLL UTMI. If PLL UTMI is used the range is to be 3.0V to 3.6V.          |

| VDDANA   | 3.0–3.6V, 3.3V                     | GNDANA            | The Analog-to-Digital Converter                                                                  |

|          |                                    |                   | Fuse box for programming.                                                                        |

| VDDFUSE  | 2.25–2.75V, 2.5V                   | GNDFUSE           | It can be tied to ground with a 100 $\Omega$ resistor for fuse reading only.                     |

| Table 5-1. | SAMA5D3      | Power | supplies |

|------------|--------------|-------|----------|

|            | 0/ 111/ 1000 |       | Sappiloo |

# 5.2 Power-up Consideration

The user must first activate VDDIOP and VDDIOM, then VDDPLL and VDDCORE with the constraint that VDDPLL is established no later than 1 ms after VDDCORE.

The VDDCORE and VDDBU power supplies rising time must be defined according to the Core and Backup Power-On-Reset characteristics to ensure VDDCORE or VDDBU has reached  $V_{IH}$  after the POR reset time.

Please refer to the "Core Power Supply POR Characteristics" and "Backup Power Supply POR Characteristics" sections of the product datasheet for power-up constraints.

# 5.3 Power-down Consideration

The user must remove VDDPLL first, then VDDCORE, and at last VDDIOP and VDDIOM, to ensure a reliable operation of the device.

Figure 40-24.Multi-master Flowchart

# Atmel

### 41.7.4 Start

The transmitter and receiver can both be programmed to start their operations when an event occurs, respectively in the Transmit Start Selection (START) field of SSC\_TCMR and in the Receive Start Selection (START) field of SSC\_RCMR.

Under the following conditions the start event is independently programmable:

- Continuous. In this case, the transmission starts as soon as a word is written in SSC\_THR and the reception starts as soon as the Receiver is enabled.

- Synchronously with the transmitter/receiver

- On detection of a falling/rising edge on TF/RF

- On detection of a low level/high level on TF/RF

- On detection of a level change or an edge on TF/RF

A start can be programmed in the same manner on either side of the Transmit/Receive Clock Register (RCMR/TCMR). Thus, the start could be on TF (Transmit) or RF (Receive).

Moreover, the Receiver can start when data is detected in the bit stream with the Compare Functions.

Detection on TF/RF input/output is done by the field FSOS of the Transmit/Receive Frame Mode Register (TFMR/RFMR).

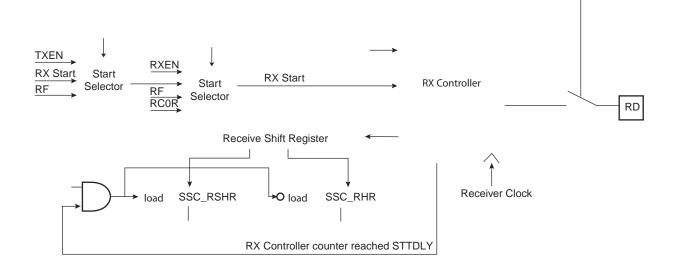

### Figure 44-21.Receiver Status

### 44.7.3.8 Parity

The USART supports five parity modes selected by writing to the PAR field in the US\_MR. The PAR field also enables the Multidrop mode, see "Multidrop Mode" on page 1385. Even and odd parity bit generation and error detection are supported.

If even parity is selected, the parity generator of the transmitter drives the parity bit to 0 if a number of 1s in the character data bit is even, and to 1 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If odd parity is selected, the parity generator of the transmitter drives the parity bit to 1 if a number of 1s in the character data bit is even, and to 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit to 1 if a number of 1s in the character data bit is even, and to 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If the mark parity is used, the parity generator of the transmitter drives the parity bit to 1 for all characters. The receiver parity checker reports an error if the parity bit is sampled to 0. If the space parity is used, the parity generator of the transmitter drives the parity bit to 0 for all characters. The receiver parity checker reports an error if the parity bit is sampled to 1. If parity is disabled, the transmitter does not generate any parity bit and the receiver does not report any parity error.

Table 44-9 shows an example of the parity bit for the character 0x41 (character ASCII "A") depending on the configuration of the USART. Because there are two bits to 1, 1 bit is added when a parity is odd, or 0 is added when a parity is even.

| Character | Hexadecimal | Binary    | Parity Bit | Parity Mode |

|-----------|-------------|-----------|------------|-------------|

| А         | 0x41        | 0100 0001 | 1          | Odd         |

| A         | 0x41        | 0100 0001 | 0          | Even        |

| A         | 0x41        | 0100 0001 | 1          | Mark        |

| A         | 0x41        | 0100 0001 | 0          | Space       |

| A         | 0x41        | 0100 0001 | None       | None        |

#### Table 44-9. Parity Bit Examples

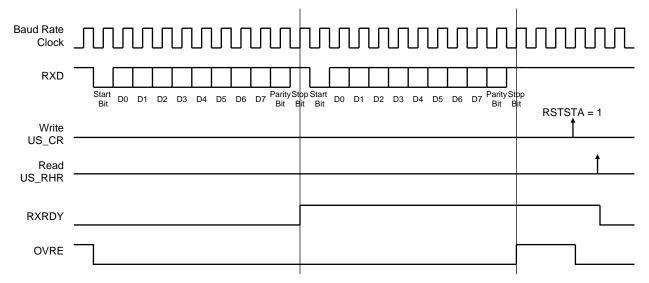

When the receiver detects a parity error, it sets the PARE (Parity Error) bit in the US\_CSR. The PARE bit can be cleared by writing the US\_CR with the RSTSTA bit to 1. Figure 44-22 illustrates the parity bit status setting and clearing.

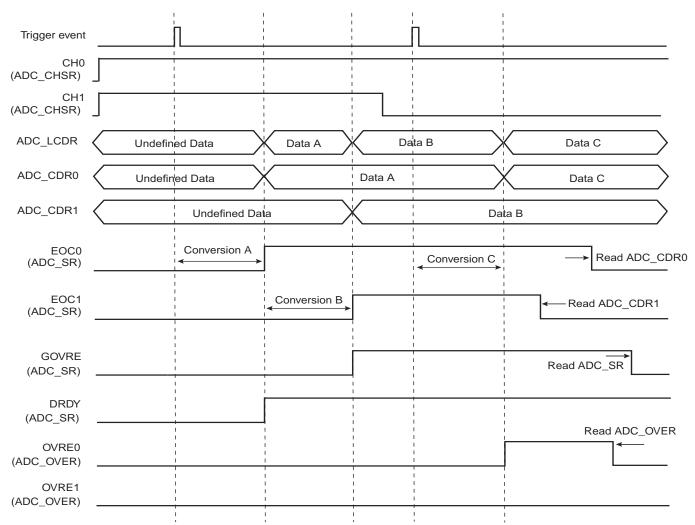

**Warning:** If the corresponding channel is disabled during a conversion or if it is disabled and then reenabled during a conversion, its associated data and its corresponding EOC and OVRE flags in ADC\_SR are unpredictable.

## 49.8.19 ADC Analog Control Register

| Name:    | ADC_ACR    |    |    |    |    |       |       |

|----------|------------|----|----|----|----|-------|-------|

| Address: | 0xF8018094 |    |    |    |    |       |       |

| Access:  | Read-write |    |    |    |    |       |       |

| 31       | 30         | 29 | 28 | 27 | 26 | 25    | 24    |

| -        | -          | _  | —  | —  | —  | —     | —     |

| 23       | 22         | 21 | 20 | 19 | 18 | 17    | 16    |

| _        | -          | _  | _  | _  | _  | —     | —     |

| 15       | 14         | 13 | 12 | 11 | 10 | 9     | 8     |

| —        | -          | —  | —  | —  | _  | —     | —     |

| 7        | 6          | 5  | 4  | 3  | 2  | 1     | 0     |

| -        | -          | -  | -  | -  | _  | PENDE | TSENS |

This register can only be written if the WPEN bit is cleared in "ADC Write Protect Mode Register" .

### • PENDETSENS: Pen Detection Sensitivity

Allows to modify the pen detection input pull-up resistor value. (See the product electrical characteristics for further details).

### 54.4.2 Master Clock Characteristics

The master clock is the maximum clock at which the system is able to run. It is given by the smallest value of the internal bus clock and EBI clock.

Table 54-10. Master Clock Waveform Parameters

| Symbol                  | Parameter              | Conditions                                                                       | Min                | Max | Unit |

|-------------------------|------------------------|----------------------------------------------------------------------------------|--------------------|-----|------|

| 1/(t <sub>CPMCK</sub> ) | Master Clock Frequency | VDDCORE[1.08V, 1.32V], T <sub>A</sub> = 85°C                                     | 125 <sup>(1)</sup> | 134 |      |

|                         |                        | VDDCORE[1.2V, 1.32V], VDDIODDR[1.75V, 1.9V], DDR2 mode only, $T_A = 85^{\circ}C$ | 125 <sup>(1)</sup> | 166 | MHz  |

Note: 1. Limitation for DDR2 usage only. There are no limitations to LP-DDR and LP-DDR2.