# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 14                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f14k50-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.13.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared by either one of the following:

- Any Reset

- By toggling the SCS1 bit of the OSCCON register

Both of these conditions restart the OST. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device automatically switches over to the external clock source. The Fail-Safe condition need not be cleared before the OSCFIF flag is cleared.

### 2.13.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after

any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

#### TABLE 2-6: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|----------|----------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| CONFIG1H | IESO     | FCMEN     | PCLKEN  | PLLEN   | FOSC3   | FOSC2  | FOSC1  | FOSC0  | 283                        |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RABIE   | TMR0IF | INT0IF | RABIF  | 66                         |

| OSCCON   | IDLEN    | IRCF2     | IRCF1   | IRCF0   | OSTS    | HFIOFS | SCS1   | SCS0   | 18                         |

| OSCTUNE  | INTSRC   | SPLLEN    | TUN5    | TUN4    | TUN3    | TUN2   | TUN1   | TUN0   | 20                         |

| PIE2     | OSCFIE   | C1IE      | C2IE    | EEIE    | BCLIE   | USBIE  | TMR3IE | _      | 72                         |

| PIR2     | OSCFIF   | C1IF      | C2IF    | EEIF    | BCLIF   | USBIF  | TMR3IF |        | 70                         |

| T1CON    | RD16     | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 99                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

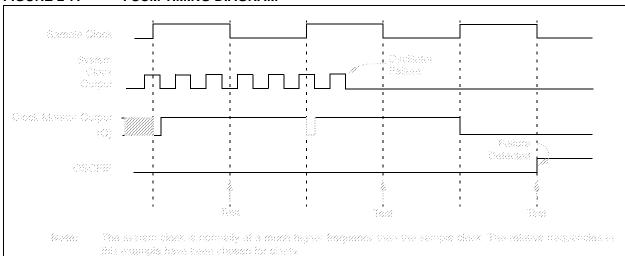

#### FIGURE 2-7: FSCM TIMING DIAGRAM

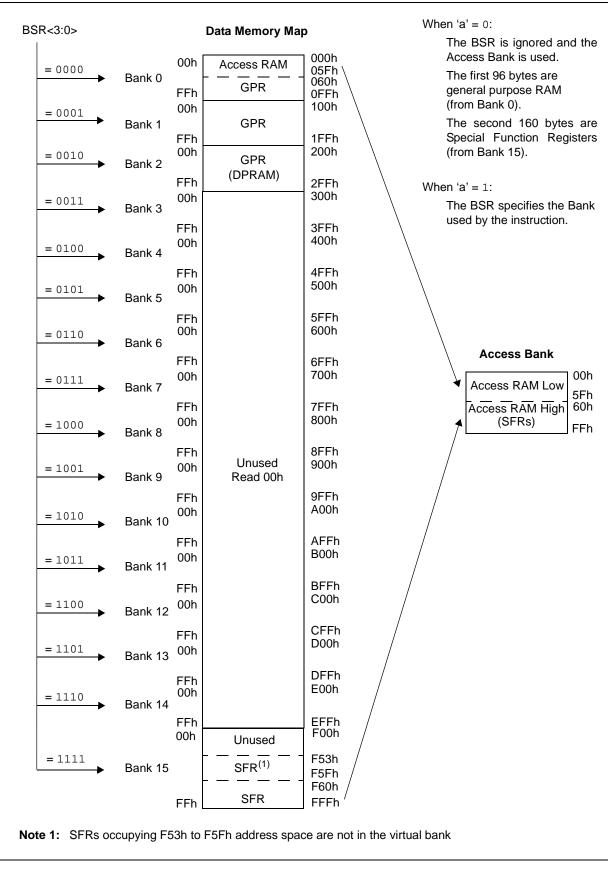

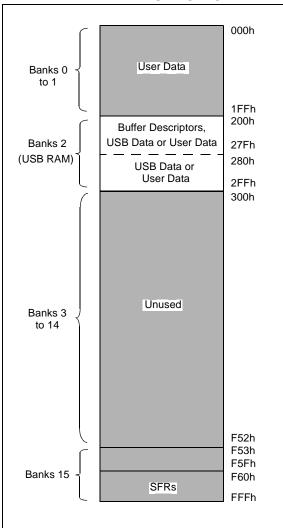

#### FIGURE 3-6: DATA MEMORY MAP FOR PIC18F14K50/PIC18LF14K50 DEVICES

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 3.4.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## 3.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

## 3.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 3.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 3-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 25.2.1** "Extended Instruction Syntax".

#### 9.2 PORTB, TRISB and LATB Registers

PORTB is an 4-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The PORTB Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

EXAMPLE 9-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by    |

|-------|-------|--------------------------|

|       |       | ; clearing output        |

|       |       | ; data latches           |

| CLRF  | LATB  | ; Alternate method       |

|       |       | ; to clear output        |

|       |       | ; data latches           |

| MOVLW | OFOh  | ; Value used to          |

|       |       | ; initialize data        |

|       |       | ; direction              |

| MOVWF | TRISB | ; Set RB<7:4> as outputs |

|       |       |                          |

All PORTB pins are individually configurable as interrupt-on-change pins. Control bits in the IOCB register enable (when set) or disable (when clear) the interrupt function for each pin.

When set, the RABIE bit of the INTCON register enables interrupts on all pins which also have their corresponding IOCB bit set. When clear, the RABIE bit disables all interrupt-on-changes.

Only pins configured as inputs can cause this interrupt to occur (i.e., any pin configured as an output is excluded from the interrupt-on-change comparison).

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTB. The 'mismatch' outputs of the last read are OR'd together to set the PORTB Change Interrupt flag bit (RABIF) in the INTCON register.

This interrupt can wake the device from the Sleep mode, or any of the Idle modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB to clear the mismatch condition (except when PORTB is the source or destination of a MOVFF instruction).

- b) Clear the flag bit, RABIF.

A mismatch condition will continue to set the RABIF flag bit. Reading or writing PORTB will end the mismatch condition and allow the RABIF bit to be cleared. The latch holding the last read value is not affected by a MCLR nor Brown-out Reset. After either one of these Resets, the RABIF flag will continue to be set if a mismatch is present.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set. Furthermore, since a read or write on a port affects all bits of that port, care must be taken when using multiple pins in Interrupt-on-change mode. Changes on one pin may not be seen while servicing changes on another pin.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

All PORTB pins have individually controlled weak internal pull-up. When set, each bit of the WPUB register enables the corresponding pin pull-up. When cleared, the RABPU bit of the INTCON2 register enables pullups on all pins which also have their corresponding WPUB bit set. When set, the RABPU bit disables all weak pull-ups. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Note: On a Power-on Reset, RB<5:4> are configured as analog inputs by default and read as '0'.

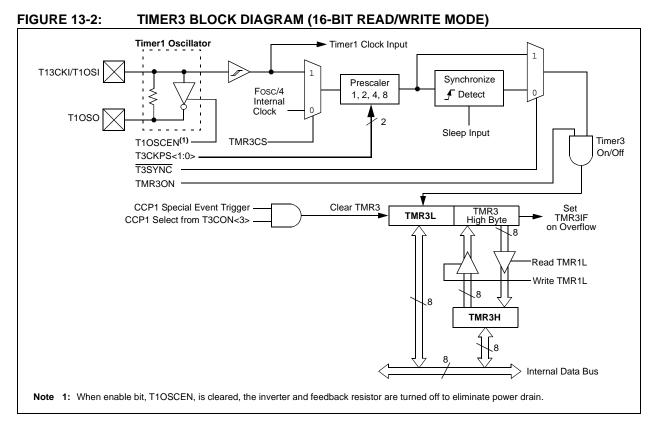

## 13.0 TIMER3 MODULE

The Timer3 module timer/counter incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The Timer3 module is controlled through the T3CON register (Register 13-1). It also selects the clock source options for the CCP modules (see **Section 14.1.1** "**CCP Module and Timer Resources**" for more information).

### REGISTER 13-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|--------|--------|--------|--------|

| RD16  | —   | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 | •   |         |         |        |        |        | bit 0  |

| Legend:<br>R = Readable I | -i+                                                                                             | M = Mritable bit                                                     | 11 - Unimplomostad bit         | road on '0'                |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------|----------------------------|--|--|--|--|

|                           |                                                                                                 | W = Writable bit                                                     | U = Unimplemented bit          |                            |  |  |  |  |

| -n = Value at P           | OR                                                                                              | '1' = Bit is set                                                     | '0' = Bit is cleared           | x = Bit is unknowr         |  |  |  |  |

| bit 7                     | RD16: 16                                                                                        | S-bit Read/Write Mode Enabl                                          | e bit                          |                            |  |  |  |  |

|                           | 1 = Enab                                                                                        | les register read/write of Tim<br>les register read/write of Tim     | er3 in one 16-bit operation    |                            |  |  |  |  |

| bit 6                     | Unimple                                                                                         | mented: Read as '0'                                                  |                                |                            |  |  |  |  |

| bit 5-4                   | T3CKPS                                                                                          | <1:0>: Timer3 Input Clock P                                          | rescale Select bits            |                            |  |  |  |  |

|                           | 10 = 1:4<br>01 = 1:2                                                                            | Prescale value<br>Prescale value<br>Prescale value<br>Prescale value |                                |                            |  |  |  |  |

| bit 3                     | T3CCP1:                                                                                         | Timer3 and Timer1 to CCP                                             | 1 Enable bits                  |                            |  |  |  |  |

|                           |                                                                                                 | er3 is the clock source for co<br>er1 is the clock source for co     |                                |                            |  |  |  |  |

| bit 2                     |                                                                                                 | : Timer3 External Clock Inpu<br>ble if the device clock comes        | t Synchronization Control bit  |                            |  |  |  |  |

|                           |                                                                                                 | 1R3CS = 1:                                                           |                                |                            |  |  |  |  |

|                           | 1 = Do not synchronize external clock input                                                     |                                                                      |                                |                            |  |  |  |  |

|                           |                                                                                                 | hronize external clock input                                         |                                |                            |  |  |  |  |

|                           | <u>When TMR3CS = 0:</u><br>This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0. |                                                                      |                                |                            |  |  |  |  |

| 1.11.4                    |                                                                                                 | -                                                                    |                                | = 0.                       |  |  |  |  |

| bit 1                     |                                                                                                 | : Timer3 Clock Source Selec                                          |                                | ising adap ofter the first |  |  |  |  |

|                           |                                                                                                 | g edge)                                                              | oscillator or T13CKI (on the r | ising edge alter the first |  |  |  |  |

|                           |                                                                                                 | nal clock (Fosc/4)                                                   |                                |                            |  |  |  |  |

| bit 0                     | TMR3ON                                                                                          | I: Timer3 On bit                                                     |                                |                            |  |  |  |  |

|                           | 1 = Enab                                                                                        | les Timer3                                                           |                                |                            |  |  |  |  |

|                           | 0 = Stops                                                                                       | Timor?                                                               |                                |                            |  |  |  |  |

### 13.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit of the T3CON register is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

### 13.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN bit of the T1CON register. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in **Section 11.0** "Timer1 Module".

### 13.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF of the PIR2 register. This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE of the PIE2 register.

#### 14.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Table 14-2.

| Note: | The associated TRIS bits must be set to      |

|-------|----------------------------------------------|

|       | output ('0') to enable the pin output driver |

|       | in order to see the PWM signal on the pin.   |

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 14.4.4 "Enhanced PWM Auto-Shutdown mode"**. An auto-shutdown event will only affect pins that have PWM outputs enabled.

### **REGISTER 14-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0                                                                                                                                                                    | U-0                                 | R/W-0               | R/W-0            | R/W-0            | R/W-0           | R/W-1    |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------|------------------|------------------|-----------------|----------|--|--|--|--|--|

| _            | —                                                                                                                                                                      | —                                   | STRSYNC             | STRD             | STRC             | STRB            | STRA     |  |  |  |  |  |

| bit 7        |                                                                                                                                                                        |                                     |                     |                  |                  |                 | bit (    |  |  |  |  |  |

| Legend:      |                                                                                                                                                                        |                                     |                     |                  |                  |                 |          |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                | W = Writable                        | e bit               | U = Unimpler     | nented bit, read | d as '0'        |          |  |  |  |  |  |

| -n = Value a |                                                                                                                                                                        | '1' = Bit is se                     |                     | '0' = Bit is cle |                  | x = Bit is unkr | nown     |  |  |  |  |  |

|              |                                                                                                                                                                        |                                     | -                   |                  |                  |                 |          |  |  |  |  |  |

| bit 7-5      | Unimpleme                                                                                                                                                              | ented: Read as                      | <b>'</b> 0 <b>'</b> |                  |                  |                 |          |  |  |  |  |  |

| bit 4        | STRSYNC:                                                                                                                                                               | STRSYNC: Steering Sync bit          |                     |                  |                  |                 |          |  |  |  |  |  |

|              | <ul> <li>1 = Output steering update occurs on next PWM period</li> <li>0 = Output steering update occurs at the beginning of the instruction cycle boundary</li> </ul> |                                     |                     |                  |                  |                 |          |  |  |  |  |  |

|              |                                                                                                                                                                        |                                     |                     |                  |                  |                 |          |  |  |  |  |  |

| bit 3        | STRD: Stee                                                                                                                                                             | ering Enable bit                    | D                   |                  |                  |                 |          |  |  |  |  |  |

|              | 1 = P1D pir                                                                                                                                                            | has the PWM                         | waveform with p     | olarity control  | from CCP1M<      | 1:0>            |          |  |  |  |  |  |

|              | 0 = P1D pir                                                                                                                                                            | n is assigned to                    | port pin            |                  |                  |                 |          |  |  |  |  |  |

| bit 2        | STRC: Stee                                                                                                                                                             | ering Enable bit                    | С                   |                  |                  |                 |          |  |  |  |  |  |

|              | 1 = P1C pir                                                                                                                                                            | has the PWM                         | waveform with p     | olarity control  | from CCP1M<      | 1:0>            |          |  |  |  |  |  |

|              | 0 = P1C pir                                                                                                                                                            | n is assigned to                    | port pin            |                  |                  |                 |          |  |  |  |  |  |

| bit 1        | STRB: Stee                                                                                                                                                             | ering Enable bit                    | В                   |                  |                  |                 |          |  |  |  |  |  |

|              | 1 = P1B pir                                                                                                                                                            | has the PWM                         | waveform with p     | olarity control  | from CCP1M<      | 1:0>            |          |  |  |  |  |  |

|              | 0 = P1B pin                                                                                                                                                            | 0 = P1B pin is assigned to port pin |                     |                  |                  |                 |          |  |  |  |  |  |

| bit 0        | STRA: Stee                                                                                                                                                             | ering Enable bit                    | A                   |                  |                  |                 |          |  |  |  |  |  |

|              | 1 = P1A pir                                                                                                                                                            | has the PWM                         | waveform with p     | olarity control  | from CCP1M<      | 1:0>            |          |  |  |  |  |  |

|              | 0 = P1A pir                                                                                                                                                            | is assigned to                      | port pin            |                  |                  |                 |          |  |  |  |  |  |

| Note 1. T    | ha PWM Steer                                                                                                                                                           | ina mode is ava                     | ilable only wher    |                  | N register bits  | CCP1M-3.2~      | - 11 and |  |  |  |  |  |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

## PIC18(L)F1XK50

#### FIGURE 16-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| VOLE DE                                 | 30       | il ast by t |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 3 N.S.N.S.N.<br>                             | <u> </u>                                                                        | <u>Nanva</u> | ninnu                           | antarur.                     |                         | unununun<br>Asto Oseres     | d No. |

|-----------------------------------------|----------|-------------|---------------------------------|-----------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|--------------|---------------------------------|------------------------------|-------------------------|-----------------------------|-------|

|                                         |          |             |                                 | -4.<br>                                 | <br>:<br>' <i>1111111111111</i><br>'         | 1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1 | ;<br>;<br>;; |                                 |                              | , y.,<br>y., y.,<br>g., |                             |       |

| - Maaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa | <br><br> |             | i<br>Milianiania<br>Verseise es |                                         | <br>r<br><b>Hillinini</b><br>Biltini Barbart |                                                                                 |              | - Olyaceri da<br>Millillillilli | s to Şisar Raor<br>Millimini | s et 3000<br>Millinnin  | 9052<br><i>иниципици</i> ни | HIR.  |

© 2008-2015 Microchip Technology Inc.

The PPBRST bit (UCON<6>) controls the Reset status when Double-Buffering mode (ping-pong buffering) is used. When the PPBRST bit is set, all Ping-Pong Buffer Pointers are set to the Even buffers. PPBRST has to be cleared by firmware. This bit is ignored in buffering modes not using ping-pong buffering.

The PKTDIS bit (UCON<4>) is a flag indicating that the SIE has disabled packet transmission and reception. This bit is set by the SIE when a SETUP token is received to allow setup processing. This bit cannot be set by the microcontroller, only cleared; clearing it allows the SIE to continue transmission and/or reception. Any pending events within the Buffer Descriptor Table will still be available, indicated within the USTAT register's FIFO buffer.

The RESUME bit (UCON<2>) allows the peripheral to perform a remote wake-up by executing Resume signaling. To generate a valid remote wake-up, firmware must set RESUME for 10 ms and then clear the bit. For more information on "resume signaling", see the **"Universal Serial Bus Specification Revision 2.0**".

The SUSPND bit (UCON<1>) places the module and supporting circuitry in a Low-Power mode. The input clock to the SIE is also disabled. This bit should be set by the software in response to an IDLEIF interrupt. It should be reset by the microcontroller firmware after an ACTVIF interrupt is observed. When this bit is active, the device remains attached to the bus but the transceiver outputs remain Idle. The voltage on the VUSB pin may vary depending on the value of this bit. Setting this bit before a IDLEIF request will result in unpredictable bus behavior.

Note: While in Suspend mode, a typical bus-powered USB device is limited to  $500 \ \mu A$  of current. This is the complete current which may be drawn by the PIC<sup>®</sup> device and its supporting circuitry. Care should be taken to assure minimum current draw when the device enters Suspend mode.

#### 22.2.2 USB CONFIGURATION REGISTER (UCFG)

Prior to communicating over USB, the module's associated internal and/or external hardware must be configured. Most of the configuration is performed with the UCFG register (Register 22-2).The UFCG register contains most of the bits that control the system level behavior of the USB module. These include:

- Bus Speed (full speed versus low speed)

- On-Chip Pull-up Resistor Enable

- Ping-Pong Buffer Usage

The UTEYE bit, UCFG<7>, enables eye pattern generation, which aids in module testing, debugging and USB certifications.

| Note: | The USB speed, transceiver and pull-up should only be configured during the mod-<br>ule setup phase. It is not recommended to |

|-------|-------------------------------------------------------------------------------------------------------------------------------|

|       | switch these settings while the module is enabled.                                                                            |

#### 22.2.2.1 Internal Transceiver

The USB peripheral has a built-in, USB 2.0, full-speed and low-speed capable transceiver, internally connected to the SIE. This feature is useful for low-cost, single chip applications. Enabling the USB module (USBEN = 1) will also enable the internal transceiver. The FSEN bit (UCFG<2>) controls the transceiver speed; setting the bit enables full-speed operation.

The on-chip USB pull-up resistors are controlled by the UPUEN bit (UCFG<4>). They can only be selected when the on-chip transceiver is enabled.

The internal USB transceiver obtains power from the VUSB pin. In order to meet USB signaling level specifications, VUSB must be supplied with a voltage source between 3.0V and 3.6V. The best electrical signal quality is obtained when a 3.3V supply is used and locally bypassed with a high quality ceramic capacitor. The capacitor should be placed as close as possible to the VUSB and VSS pins found on the same edge of the package (i.e., route ground of the capacitor to VSS pin 20 on 20-lead PDIP, SOIC, SSOP and QFN packaged parts).

The D+ and D- signal lines can be routed directly to their respective pins on the USB connector or cable (for hard-wired applications). No additional resistors, capacitors, or magnetic components are required as the D+ and D- drivers have controlled slew rate and output impedance intended to match with the characteristic impedance of the USB cable.

In order to meet the USB specifications, the traces should be less than 30 cm long. Ideally, these traces should be designed to have a characteristic impedance matching that of the USB cable.

#### 22.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

#### 22.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number registers are primarily used for isochronous transfers. The contents of the UFRMH and UFRML registers are only valid when the 48 MHz SIE clock is active (i.e., contents are inaccurate when SUSPND (UCON<1>) bit = 1).

### 22.3 USB RAM

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual access memory that is mapped into the normal data memory space in Bank 2 (200h to 2FFh) for a total of 256 bytes (Figure 22-4).

Bank 2 (200h through 27Fh) is used specifically for endpoint buffer control. Depending on the type of buffering being used, all but eight bytes of Bank 2 may also be available for use as USB buffer space.

Although USB RAM is available to the microcontroller as data memory, the sections that are being accessed by the SIE should not be accessed by the microcontroller. A semaphore mechanism is used to determine the access to a particular buffer at any given time. This is discussed in **Section 22.4.1.1 "Buffer Ownership"**.

#### FIGURE 22-4: IMPLEMENTATION OF USB RAM IN DATA MEMORY SPACE

## PIC18(L)F1XK50

#### TABLE 22-2: ASSIGNMENT OF BUFFER DESCRIPTORS FOR THE DIFFERENT BUFFERING MODES

|          |                          | BDs Assigned to Endpoint |                     |                     |                   |                |                                                       |                |  |  |  |  |  |

|----------|--------------------------|--------------------------|---------------------|---------------------|-------------------|----------------|-------------------------------------------------------|----------------|--|--|--|--|--|

| Endpoint | Mode 0<br>(No Ping-Pong) |                          | Moo<br>(Ping-Pong o | de 1<br>on EP0 OUT) | Moc<br>(Ping-Pong |                | Mode 3<br>(Ping-Pong on all other EPs,<br>except EP0) |                |  |  |  |  |  |

|          | Out                      | In                       | Out                 | In                  | Out               | In             | Out                                                   | In             |  |  |  |  |  |

| 0        | 0                        | 1                        | 0 (E), 1 (O)        | 2                   | 0 (E), 1 (O)      | 2 (E), 3 (O)   | 0                                                     | 1              |  |  |  |  |  |

| 1        | 2                        | 3                        | 3                   | 4                   | 4 (E), 5 (O)      | 6 (E), 7 (O)   | 2 (E), 3 (O)                                          | 4 (E), 5 (O)   |  |  |  |  |  |

| 2        | 4                        | 5                        | 5                   | 6                   | 8 (E), 9 (O)      | 10 (E), 11 (O) | 6 (E), 7 (O)                                          | 8 (E), 9 (O)   |  |  |  |  |  |

| 3        | 6                        | 7                        | 7                   | 8                   | 12 (E), 13 (O)    | 14 (E), 15 (O) | 10 (E), 11 (O)                                        | 12 (E), 13 (O) |  |  |  |  |  |

| 4        | 8                        | 9                        | 9                   | 10                  | 16 (E), 17 (O)    | 18 (E), 19 (O) | 14 (E), 15 (O)                                        | 16 (E), 17 (O) |  |  |  |  |  |

| 5        | 10                       | 11                       | 11                  | 12                  | 20 (E), 21 (O)    | 22 (E), 23 (O) | 18 (E), 19 (O)                                        | 20 (E), 21 (O) |  |  |  |  |  |

| 6        | 12                       | 13                       | 13                  | 14                  | 24 (E), 25 (O)    | 26 (E), 27 (O) | 22 (E), 23 (O)                                        | 24 (E), 25 (O) |  |  |  |  |  |

| 7        | 14                       | 15                       | 15                  | 16                  | 28 (E), 29 (O)    | 30 (E), 31 (O) | 26 (E), 27 (O)                                        | 28 (E), 29 (O) |  |  |  |  |  |

Legend: (E) = Even transaction buffer, (O) = Odd transaction buffer

#### TABLE 22-3: SUMMARY OF USB BUFFER DESCRIPTOR TABLE REGISTERS

| Name                   | Bit 7      | Bit 6               | Bit 5               | Bit 4               | Bit 3                                       | Bit 2                                        | Bit 1 | Bit 0 |  |  |

|------------------------|------------|---------------------|---------------------|---------------------|---------------------------------------------|----------------------------------------------|-------|-------|--|--|

| BDnSTAT <sup>(1)</sup> | UOWN       | DTS <sup>(4)</sup>  | PID3 <sup>(2)</sup> | PID2 <sup>(2)</sup> | PID1 <sup>(2)</sup><br>DTSEN <sup>(3)</sup> | PID0 <sup>(2)</sup><br>BSTALL <sup>(3)</sup> | BC9   | BC8   |  |  |

| BDnCNT <sup>(1)</sup>  | Byte Count | Byte Count          |                     |                     |                                             |                                              |       |       |  |  |

| BDnADRL <sup>(1)</sup> | Buffer Add | Buffer Address Low  |                     |                     |                                             |                                              |       |       |  |  |

| BDnADRH <sup>(1)</sup> | Buffer Add | Buffer Address High |                     |                     |                                             |                                              |       |       |  |  |

**Note 1:** For buffer descriptor registers, n may have a value of 0 to 31. For the sake of brevity, all 32 registers are shown as one generic prototype. All registers have indeterminate Reset values (xxxx xxxx).

2: Bits 5 through 2 of the BDnSTAT register are used by the SIE to return PID<3:0> values once the register is turned over to the SIE (UOWN bit is set). Once the registers have been under SIE control, the values written for DTSEN and BSTALL are no longer valid.

**3:** Prior to turning the buffer descriptor over to the SIE (UOWN bit is cleared), bits 5 through 2 of the BDnSTAT register are used to configure the DTSEN and BSTALL settings.

**4:** This bit is ignored unless DTSEN = 1.

#### 22.5.2 USB INTERRUPT ENABLE REGISTER (UIE)

The USB Interrupt Enable register (Register 22-8) contains the enable bits for the USB Status interrupt sources. Setting any of these bits will enable the respective interrupt source in the UIR register.

The values in this register only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polled and serviced without actually generating an interrupt.

#### REGISTER 22-8: UIE: USB INTERRUPT ENABLE REGISTER

| U-0   | R/W-0 | R/W-0   | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|--------|-------|--------|--------|--------|

| —     | SOFIE | STALLIE | IDLEIE | TRNIE | ACTVIE | UERRIE | URSTIE |

| bit 7 |       |         |        |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------|

| bit 6 | SOFIE: Start-of-Frame Token Interrupt Enable bit                                                                  |

|       | <ul><li>1 = Start-of-Frame token interrupt enabled</li><li>0 = Start-of-Frame token interrupt disabled</li></ul>  |

| bit 5 | STALLIE: STALL Handshake Interrupt Enable bit                                                                     |

|       | <ul><li>1 = STALL interrupt enabled</li><li>0 = STALL interrupt disabled</li></ul>                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                                                                          |

|       | <ul><li>1 = Idle detect interrupt enabled</li><li>0 = Idle detect interrupt disabled</li></ul>                    |

| bit 3 | TRNIE: Transaction Complete Interrupt Enable bit                                                                  |

|       | <ul><li>1 = Transaction interrupt enabled</li><li>0 = Transaction interrupt disabled</li></ul>                    |

| bit 2 | ACTVIE: Bus Activity Detect Interrupt Enable bit                                                                  |

|       | <ul> <li>1 = Bus activity detect interrupt enabled</li> <li>0 = Bus activity detect interrupt disabled</li> </ul> |

| bit 1 | UERRIE: USB Error Interrupt Enable bit                                                                            |

|       | <ul><li>1 = USB error interrupt enabled</li><li>0 = USB error interrupt disabled</li></ul>                        |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit                                                                            |

|       | <ul><li>1 = USB Reset interrupt enabled</li><li>0 = USB Reset interrupt disabled</li></ul>                        |

|         | INTALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Address | Power-on Reset,<br>Brown-out Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Wake-up via WDT<br>or Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| F63h    | -xxx xxx-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -xxx xxx-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -uuu uuu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| F62h    | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -uuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| F61h    | 00 -000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00 -000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uu -uuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| F60h    | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -uuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| F5Fh    | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| F5Eh    | xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | uuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| F5Dh    | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xxxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| F5Ch    | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -uuu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| F5Bh    | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |