Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 14                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

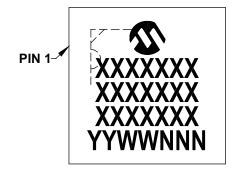

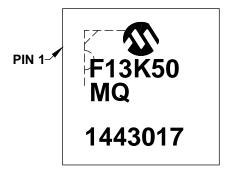

| Package / Case             | 20-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 20-VQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf13k50-i-mq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 1K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. Using a bootloader routine located in the code protected Boot Block, it is possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F1XK50 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include:

- Auto-Shutdown, for disabling PWM outputs on interrupt or other select conditions

- Auto-Restart, to reactivate outputs once the condition has cleared

- Output steering to selectively enable one or more of four outputs to provide the PWM signal.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution.

- 10-bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit postscaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 27.0 "Electrical Specifications" for time-out periods.

#### 1.3 Details on Individual Family Members

Devices in the PIC18(L)F1XK50 family are available in 20-pin packages. Block diagrams for the two groups are shown in Figure 1-1.

The devices are differentiated from each other in the following ways:

- 1. Flash program memory:

- 8 Kbytes for PIC18F13K50/PIC18LF13K50

- 16 Kbytes for PIC18F14K50/PIC18LF14K50

- 2. On-chip 3.2V LDO regulator for PIC18F13K50 and PIC18F14K50.

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1 and I/O description are in Table 1-2.

#### 2.6 Oscillator Control

The Oscillator Control (OSCCON) (Register 2-1) and the Oscillator Control 2 (OSCCON2) (Register 2-2) registers control the system clock and frequency selection options.

#### REGISTER 2-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0        | R/W-0                                                                                                                                    | R/W-1                                                | R/W-1            | R-q                 | R-0                              | R/W-0           | R/W-0       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------|---------------------|----------------------------------|-----------------|-------------|

| IDLEN        | IRCF2                                                                                                                                    | IRCF1                                                | IRCF0            | OSTS <sup>(1)</sup> | HFIOFS                           | SCS1            | SCS0        |

| bit 7        |                                                                                                                                          | 1                                                    |                  |                     | •                                |                 | bit (       |

| Lonondi      |                                                                                                                                          |                                                      |                  |                     |                                  |                 |             |

| Legend:      |                                                                                                                                          | Muitable bit                                         |                  |                     |                                  | a denometo o    | n eenditien |

| R = Readab   |                                                                                                                                          | Writable bit                                         | •                | emented bit, re     |                                  | q = depends o   |             |

| -n = Value a | at POR 1'=                                                                                                                               | Bit is set                                           | '0' = Bit is c   | lieared             |                                  | x = Bit is unkn | own         |

| bit 7        |                                                                                                                                          | nters Idle mod                                       | e on SLEEP ins   |                     |                                  |                 |             |

| bit 6-4      | IRCF<2:0>: I<br>111 = 16 MHz<br>110 = 8 MHz<br>101 = 4 MHz<br>100 = 2 MHz<br>011 = 1 MHz<br>010 = 500 kH<br>001 = 250 kH<br>000 = 31 kHz | z<br>(3)<br>Iz<br>Iz                                 | tor Frequency \$ | Select bits         |                                  |                 |             |

| bit 3        | 1 = Device is                                                                                                                            | running from                                         |                  | ed by FOSC<2        | ::0> of the CON<br>OSC or LFINTC |                 |             |

| bit 2        | 1 = HFINTOS                                                                                                                              | NTOSC Frequ<br>SC frequency i<br>SC frequency i      |                  |                     |                                  |                 |             |

| bit 1-0      | <b>SCS&lt;1:0&gt;:</b> S<br>1x = Internal<br>01 = Seconda                                                                                | ystem Clock S<br>oscillator block<br>ary (Timer1) os | elect bits       | G1H[FOSC<3:         | 0>]).                            |                 |             |

| <b>2</b> : S | Reset state depen<br>Source selected b                                                                                                   | y the INTSRC                                         | bit of the OSC   | TUNE register,      | see text.                        |                 |             |

3: Default output frequency of HFINTOSC on Reset.

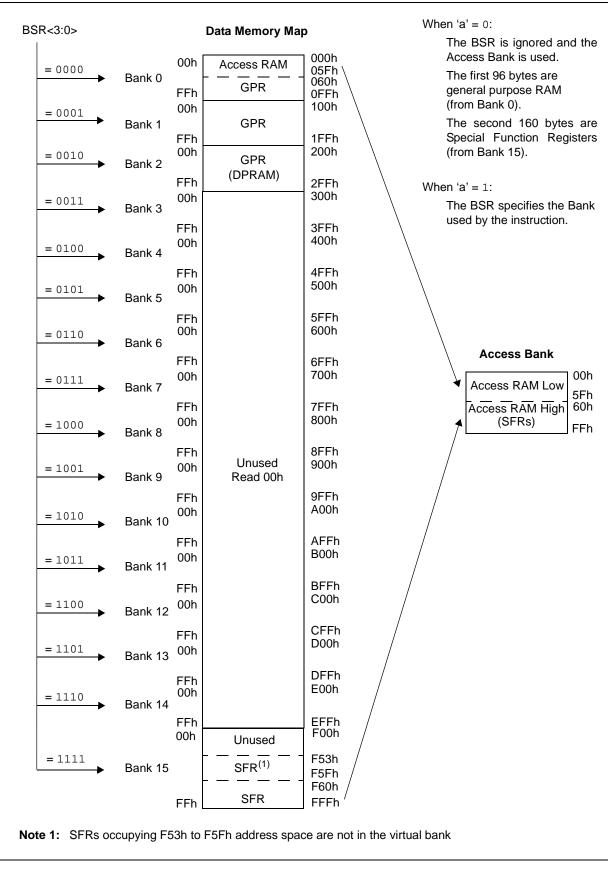

#### 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 4.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 5.0 "Data EEPROM Memory"**.

#### 3.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

This family of devices contain the following:

- PIC18F13K50: 8 Kbytes of Flash memory, up to 4,096 single-word instructions

- PIC18F14K50: 16 Kbytes of Flash memory, up to 8,192 single-word instructions

PIC18 devices have two interrupt vectors and one Reset vector. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for PIC18(L)F1XK50 devices is shown in Figure 3-1. Memory block details are shown in Figure 24-2.

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC18(L)F1XK50 DEVICES

|                                             | PC<                                | :20:0>          |                    |                   |

|---------------------------------------------|------------------------------------|-----------------|--------------------|-------------------|

| CALL, RCALL, RET                            |                                    | 21 <u></u>      |                    |                   |

| RETFIE, RETLW                               | 01                                 |                 |                    |                   |

|                                             | Stack                              | Level 1         |                    |                   |

|                                             | <u> </u>                           | •               |                    |                   |

|                                             | Stack L                            | _evel 31        |                    |                   |

|                                             | Reset                              | Vector          | 0000h              | <del>.</del>      |

|                                             | High Priority I                    | nterrupt Vector | 0008h              |                   |

|                                             | Low Priority Ir                    | nterrupt Vector | 0018h              |                   |

| On-Chip<br>Program Memory<br>1FFFh<br>2000h | On-Chip<br>Program Memory<br>3FFFh |                 |                    |                   |

| PIC18F13K50                                 | 4000h                              |                 |                    |                   |

|                                             | PIC18F14K50                        |                 |                    | User Memory Space |

| Read '0'                                    | Read '0'                           |                 |                    |                   |

|                                             |                                    |                 | 1FFFFFh<br>200000h | <u> </u>          |

#### FIGURE 3-6: DATA MEMORY MAP FOR PIC18F14K50/PIC18LF14K50 DEVICES

| EXAMPLE 4-3:   | WRITI         | NG TO FLASH PROGR              | AM MEMORY (CONTINUED)                   |

|----------------|---------------|--------------------------------|-----------------------------------------|

|                | DECFSZ<br>BRA | COUNTER<br>WRITE_WORD_TO_HREGS | ; loop until holding registers are full |

| PROGRAM_MEMORY |               |                                |                                         |

|                | BSF           | EECON1, EEPGD                  | ; point to Flash program memory         |

|                | BCF           | EECON1, CFGS                   | ; access Flash program memory           |

|                | BSF           | EECON1, WREN                   | ; enable write to memory                |

|                | BCF           | INTCON, GIE                    | ; disable interrupts                    |

|                | MOVLW         | 55h                            |                                         |

| Required       | MOVWF         | EECON2                         | ; write 55h                             |

| Sequence       | MOVLW         | 0AAh                           |                                         |

|                | MOVWF         | EECON2                         | ; write OAAh                            |

|                | BSF           | EECON1, WR                     | ; start program (CPU stall)             |

|                | DCFSZ         | COUNTER2                       | ; repeat for remaining write blocks     |

|                | BRA           | WRITE_BYTE_TO_HREGS            | ;                                       |

|                | BSF           | INTCON, GIE                    | ; re-enable interrupts                  |

|                | BCF           | EECON1, WREN                   | ; disable write to memory               |

|                |               |                                | -                                       |

WRITING TO FLACU BROODAM MEMORY (CONTINUED)

#### 4.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 4.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

#### 4.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

#### 4.6 Flash Program Operation During Code Protection

See Section 24.3 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                               | Bit 6       | Bit 5     | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|-----------------------------------------------------|-------------|-----------|---------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | —                                                   | —           | bit 21    | Program Me    | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 275                        |

| TBPLTRH | Program Me                                          | emory Table | Pointer H | ligh Byte (TE | BLPTR<15:8    | S>)          |               |            | 275                        |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |             |           |               |               |              |               | 275        |                            |

| TABLAT  | Program Memory Table Latch                          |             |           |               |               |              |               | 275        |                            |

| INTCON  | GIE/GIEH                                            | PEIE/GIEL   | TMR0IE    | INT0IE        | RABIE         | TMR0IF       | <b>INT0IF</b> | RABIF      | 275                        |

| EECON2  | EEPROM Control Register 2 (not a physical register) |             |           |               |               |              |               | 277        |                            |

| EECON1  | EEPGD                                               | CFGS        |           | FREE          | WRERR         | WREN         | WR            | RD         | 277                        |

| IPR2    | OSCFIP                                              | C1IP        | C2IP      | EEIP          | BCLIP         | USBIP        | TMR3IP        | _          | 278                        |

| PIR2    | OSCFIF                                              | C1IF        | C2IF      | EEIF          | BCLIF         | USBIF        | TMR3IF        | —          | 278                        |

| PIE2    | OSCFIE                                              | C1IE        | C2IE      | EEIE          | BCLIE         | USBIE        | TMR3IE        |            | 278                        |

TABLE 4-3:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

| Pin            | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                                     |

|----------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/AN4/       | RC0      | 0               | 0   | DIG         | LATC<0> data output.                                                                                                                            |

| C12IN+/VREF+/  |          | 1               | 1   | ST          | PORTC<0> data input.                                                                                                                            |

| INT0           | AN4      | 1               | Ι   | ANA         | A/D input channel 4.                                                                                                                            |

|                | C12IN+   | 1               | Ι   | ANA         | Comparators C1 and C2 non-inverting input. Analog select is shared with ADC.                                                                    |

|                | Vref+    | 1               | Ι   | ANA         | ADC and comparator voltage reference high input.                                                                                                |

|                | INT0     | 1               |     | ST          | External Interrupt 0 input.                                                                                                                     |

| RC1/AN5/       | RC1      | 0               | 0   | DIG         | LATC<1> data output.                                                                                                                            |

| C12IN1-/VREF-/ |          | 1               |     | ST          | PORTC<1> data input.                                                                                                                            |

| INT1           | AN5      | 1               |     | ANA         | A/D input channel 5.                                                                                                                            |

|                | C12IN1-  | 1               | Ι   | ANA         | Comparators C1 and C2 inverting input. Analog select is shared with ADC.                                                                        |

|                | VREF-    | 1               | I   | ANA         | ADC and comparator voltage reference low input.                                                                                                 |

|                | INT1     | 1               |     | ST          | External Interrupt 1 input.                                                                                                                     |

| RC2/AN6/       | RC2      | 0               | 0   | DIG         | LATC<2> data output.                                                                                                                            |

| C12IN2-/CVREF/ |          | 1               |     | ST          | PORTC<2> data input.                                                                                                                            |

| P1D/INT2       | AN6      | 1               | Ι   | ANA         | A/D input channel 6.                                                                                                                            |

|                | C12IN2-  | 1               | Ι   | ANA         | Comparators C1 and C2 inverting input, channel 2. Analog select is shared with ADC.                                                             |

|                | CVREF    | х               | 0   | ANA         | Voltage reference output. Enabling this feature disables digital I/O.                                                                           |

|                | P1D      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel D. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

|                | INT2     | 1               | Ι   | ST          | External Interrupt 2 input.                                                                                                                     |

| RC3/AN7/       | RC3      | 0               | 0   | DIG         | LATC<3> data output.                                                                                                                            |

| C12IN3-/P1C/   |          | 1               | Ι   | ST          | PORTC<3> data input.                                                                                                                            |

| PGM            | AN7      | 1               | Ι   | ANA         | A/D input channel 7.                                                                                                                            |

|                | C12IN3-  | 1               | I   | ANA         | Comparators C1 and C2 inverting input, channel 3. Analog select is shared with ADC.                                                             |

|                | P1C      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel C. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

|                | PGM      | x               | Ι   | ST          | Single-Supply Programming mode entry (ICSP <sup>™</sup> ). Enabled by LVP Configuration bit; all other pin functions disabled.                  |

| RC4/C12OUT/    | RC4      | 0               | 0   | DIG         | LATC<4> data output.                                                                                                                            |

| P1B            |          | 1               | Ι   | ST          | PORTC<4> data input.                                                                                                                            |

|                | C12OUT   | 0               | 0   | DIG         | Comparator 1 and 2 output; takes priority over port data.                                                                                       |

|                | P1B      | 0               | 0   | DIG         | ECCP1 Enhanced PWM output, channel B. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority over<br>port data. |

TABLE 9-14:

PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$  input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

#### 9.5 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

#### REGISTER 9-17: SLRCON: SLEW RATE CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     |     |     | —   | —   | SLRC  | SLRB  | SLRA  |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | SLRC: PORTC Slew Rate Control bit                                                                                                         |

|         | <ul><li>1 = All outputs on PORTC slew at 0.1 times the standard rate</li><li>0 = All outputs on PORTC slew at the standard rate</li></ul> |

| bit 1   | SLRB: PORTB Slew Rate Control bit                                                                                                         |

|         | <ul><li>1 = All outputs on PORTB slew at 0.1 times the standard rate</li><li>0 = All outputs on PORTB slew at the standard rate</li></ul> |

| bit 0   | SLRA: PORTA Slew Rate Control bit                                                                                                         |

|         | 1 = All outputs on PORTA slew at 0.1 times the standard rate <sup>(1)</sup><br>0 = All outputs on PORTA slew at the standard rate         |

Note 1: The slew rate of RA4 defaults to standard rate when the pin is used as CLKOUT.

|               | R/W-0                                                                                                                                                                  | R/W-0                                                         | R/W-0                                                                                                  | R/W-0                                                                                    | R/W-0                                        | R/W-0           | R/W-0            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|------------------|

| WCOL          | SSPOV                                                                                                                                                                  | SSPEN                                                         | CKP                                                                                                    | SSPM3                                                                                    | SSPM2                                        | SSPM1           | SSPM0            |

| bit 7         |                                                                                                                                                                        |                                                               |                                                                                                        |                                                                                          |                                              |                 | bit C            |

|               |                                                                                                                                                                        |                                                               |                                                                                                        |                                                                                          |                                              |                 |                  |

| Legend:       |                                                                                                                                                                        |                                                               |                                                                                                        |                                                                                          |                                              |                 |                  |

| R = Readable  |                                                                                                                                                                        | W = Writable                                                  | bit                                                                                                    | -                                                                                        | mented bit, rea                              |                 |                  |

| -n = Value at | POR                                                                                                                                                                    | '1' = Bit is set                                              |                                                                                                        | '0' = Bit is cl                                                                          | eared                                        | x = Bit is unk  | nown             |

| bit 7         | WCOL: Writ                                                                                                                                                             | e Collision Dete                                              | ct bit                                                                                                 |                                                                                          |                                              |                 |                  |

|               |                                                                                                                                                                        | ansmit mode:                                                  |                                                                                                        |                                                                                          |                                              |                 |                  |

|               | mission                                                                                                                                                                | to the SSPBUF i<br>to be started (m                           |                                                                                                        |                                                                                          | the I <sup>2</sup> C conditi                 | ons were not va | alid for a trans |

|               | 0 = No collis                                                                                                                                                          |                                                               |                                                                                                        |                                                                                          |                                              |                 |                  |

|               | software                                                                                                                                                               | PBUF register is<br>e)                                        | written while                                                                                          | it is still transn                                                                       | nitting the previ                            | ous word (must  | be cleared b     |

|               | 0 = No collis<br><u>In Receive n</u><br>This is a "do                                                                                                                  | node (Master or                                               | Slave modes)                                                                                           | <u>::</u>                                                                                |                                              |                 |                  |

| bit 6         |                                                                                                                                                                        | ceive Overflow I                                              | ndicator bit                                                                                           |                                                                                          |                                              |                 |                  |

|               | In Receive n<br>1 = A byte i                                                                                                                                           | <u>node:</u><br>s received while                              |                                                                                                        | register is stil                                                                         | I holding the pr                             | evious byte (m  | ust be cleare    |

|               | by softw<br>0 = No over                                                                                                                                                |                                                               |                                                                                                        |                                                                                          |                                              |                 |                  |

|               | <u>In Transmit r</u><br>This is a "do                                                                                                                                  | <u>mode:</u><br>n't care" bit in Ti                           | ansmit mode.                                                                                           |                                                                                          |                                              |                 |                  |

| bit 5         | SSPEN: Syr                                                                                                                                                             | nchronous Seria                                               | I Port Enable                                                                                          | bit                                                                                      |                                              |                 |                  |

|               | 0 = Disables                                                                                                                                                           | the serial port a serial port and ed, the SDA and             | configures the                                                                                         | ese pins as I/O                                                                          | port pins                                    |                 | S                |

| h:+ 1         | When enabled, the SDA and SCL pins must be properly configured as inputs.<br>CKP: SCK Release Control bit                                                              |                                                               |                                                                                                        |                                                                                          |                                              |                 |                  |

| bit 4         |                                                                                                                                                                        | Release Control                                               | bit                                                                                                    |                                                                                          |                                              |                 |                  |

| DIT 4         | <u>In Slave mod</u><br>1 = Release                                                                                                                                     | <u>de:</u><br>clock                                           |                                                                                                        |                                                                                          |                                              |                 |                  |

| DIT 4         | 1 = Release<br>0 = Holds clo                                                                                                                                           | <u>de:</u><br>clock<br>ock low (clock st                      |                                                                                                        |                                                                                          | setup time                                   |                 |                  |

| DIT 4         | 1 = Release                                                                                                                                                            | <u>de:</u><br>clock<br>ock low (clock st<br>ode:              |                                                                                                        |                                                                                          | setup time                                   |                 |                  |

| bit 3-0       | 1 = Release<br>0 = Holds clo<br><u>In Master mo</u><br>Unused in th                                                                                                    | <u>de:</u><br>clock<br>ock low (clock st<br>ode:              | retch), used to                                                                                        | o ensure data                                                                            | setup time                                   |                 |                  |

|               | 1 = Release<br>0 = Holds clo<br>In Master modulused in the<br>SSPM<3:0><br>1111 = $I^2C$ S<br>1110 = $I^2C$ S<br>1011 = $I^2C$ H<br>1000 = $I^2C$ H<br>0111 = $I^2C$ S | <u>de:</u><br>clock<br>ock low (clock st<br>ode:<br>nis mode. | retch), used to<br>Serial Port Mo<br>bit address wit<br>olled Master m<br>ock = Fosc/(4<br>bit address | o ensure data<br>de Select bits<br>th Start and Sto<br>o Start and Sto<br>ode (Slave Idl | top bit interrupt<br>op bit interrupts<br>e) |                 |                  |

### REGISTER 15-4: SSPCON1: MSSP CONTROL 1 REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

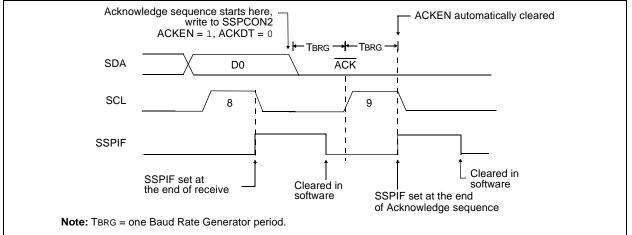

#### 15.3.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 15-23).

#### 15.3.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

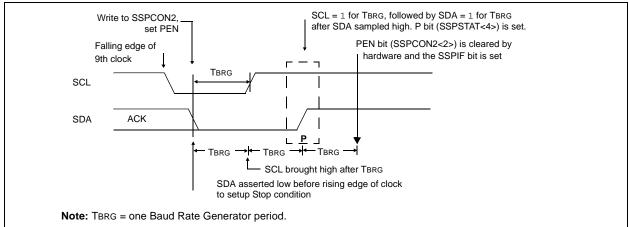

#### 15.3.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-24).

#### 15.3.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 15-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 15-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 16.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRG register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF Interrupt Flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 16.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 16-7), and asynchronously if the device is in Sleep mode (Figure 16-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 16.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared by hardware by a rising edge on RX/DT. The interrupt condition is then cleared by software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### 17.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed),

an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 3.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

=

$$5\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} \ charged \ to \ within \ 1/2 \ lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED}$$

$$V_{APPLIED}\left(1-e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{2047}\right) \quad (combining [1] and [2])$$

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/2047)$$

= -13.5pF(1k\Omega + 700\Omega + 10k\Omega) \ln(0.0004885)

= 1.20\u03c0s

Therefore:

$$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.45\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

1/2 lsb

# PIC18(L)F1XK50

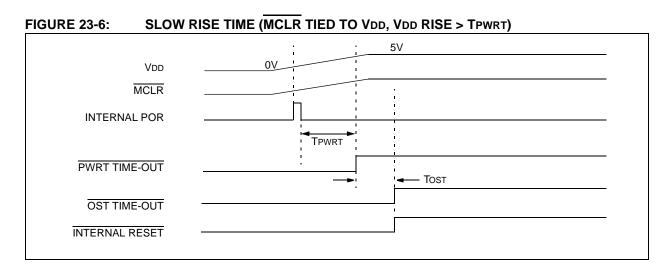

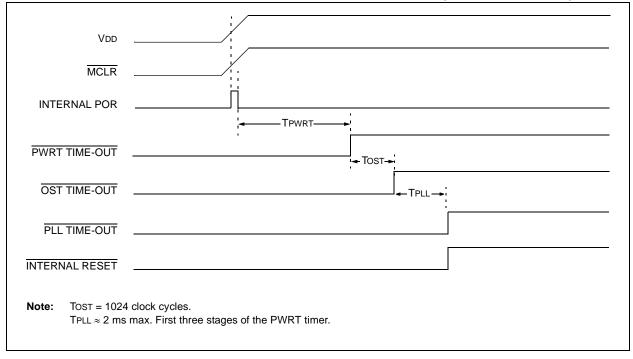

#### FIGURE 23-7: TIME-OUT SEQUENCE ON POR W/PLL ENABLED (MCLR TIED TO VDD)

#### 24.3.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

#### 24.3.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

#### 24.4 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

#### 24.5 In-Circuit Serial Programming

PIC18(L)F1XK50 devices can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

#### 24.6 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 24-4 shows which resources are required by the background debugger.

| <b>TABLE 24-4</b> : | DEBUGGER RESOURCES |

|---------------------|--------------------|

|                     |                    |

| I/O pins:       | RA0, RA1  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to the following pins:

- MCLR/VPP/RA3

- VDD

- Vss

- RA0

- RA1

This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

#### 24.7 Single-Supply ICSP Programming

The LVP Configuration bit enables Single-Supply ICSP Programming (formerly known as Low-Voltage ICSP Programming or LVP). When Single-Supply Programmed <u>without</u> requiring high voltage being applied to the MCLR/VPP/RA3 pin, but the RC3/PGM pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

While programming, using Single-Supply Programming mode, VDD is applied to the MCLR/VPP/RA3 pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: By default, Single-Supply ICSP is enabled in unprogrammed devices (as supplied from Microchip) and erased devices.

- **3:** When Single-Supply Programming is enabled, the RC3 pin can no longer be used as a general purpose I/O pin.

- 4: When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Single-Supply ICSP Programming mode will not be used, the LVP bit can be cleared. RC3/PGM then becomes available as the digital I/O pin, RC3. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/ VPP/RA3 pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased using either a block erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a block erase is required.

## 25.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18(L)F1XK50 family of devices. This includes the MPLAB<sup>®</sup> C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- · A command line option

- A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

#### 27.3 DC Characteristics

#### TABLE 27-1: SUPPLY VOLTAGE, PIC18(L)F1XK50-I/E (INDUSTRIAL, EXTENDED)

| PIC18LF1XK50  |        |                                                              | Standard Operating Conditions (unless otherwise stated) |     |                   |             |                                                                                                                                      |  |  |  |

|---------------|--------|--------------------------------------------------------------|---------------------------------------------------------|-----|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC18F1       | XK50   |                                                              | Standard Operating Conditions (unless otherwise stated) |     |                   |             |                                                                                                                                      |  |  |  |

| Param.<br>No. | Sym.   | Sym. Characteristic Min. Typ.† Max. Units Conditions         |                                                         |     |                   |             |                                                                                                                                      |  |  |  |

| D001          | Vdd    | Supply Voltage                                               |                                                         |     |                   |             |                                                                                                                                      |  |  |  |

|               |        | PIC18LF1XK50                                                 | 2.0<br>3.0<br>1.8                                       |     | 3.6<br>3.6<br>3.6 | V<br>V<br>V | $\begin{array}{l} \mbox{Fosc} \leq 20 \mbox{ MHz} \\ \mbox{Fosc} \leq 48 \mbox{ MHz} \\ \mbox{Fosc} \leq 16 \mbox{ MHz} \end{array}$ |  |  |  |

| D001          |        | PIC18F1XK50                                                  | 2.0<br>3.0<br>1.8                                       |     | 5.5<br>5.5<br>5.5 | V<br>V<br>≤ | $\begin{array}{l} Fosc \leq 20 \; MHz \\ Fosc \leq 48 \; MHz \\ Fosc \leq 16 \; MHz \end{array}$                                     |  |  |  |

| D002*         | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                    |                                                         |     |                   |             |                                                                                                                                      |  |  |  |

|               |        | PIC18LF1XK50                                                 | 1.5                                                     | —   | —                 | V           | Device in Sleep mode                                                                                                                 |  |  |  |

| D002*         |        | PIC18F1XK50                                                  | 1.7                                                     | —   | _                 | V           | Device in Sleep mode                                                                                                                 |  |  |  |

|               | VPOR*  | Power-on Reset Release Voltage                               |                                                         | 1.6 |                   | V           |                                                                                                                                      |  |  |  |

|               | VPORR* | Power-on Reset Rearm Voltage                                 |                                                         | 1.4 |                   | V           |                                                                                                                                      |  |  |  |

| D004*         | SVDD   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal | 0.05                                                    | —   | —                 | V/ms        |                                                                                                                                      |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

| DC CHA        | RACTER | ISTICS                                                               | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |              |                  |       |                                                                      |  |

|---------------|--------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-------|----------------------------------------------------------------------|--|

| Param.<br>No. | Sym.   | Characteristic                                                       | Min.                                                                                                                     | Typ.† Max. U |                  | Units | Conditions                                                           |  |

|               |        | Internal Program Memory<br>Programming Specifications <sup>(1)</sup> |                                                                                                                          |              |                  |       |                                                                      |  |

| D110          | VPP    | Voltage on MCLR/VPP/RA3 pin                                          | 8                                                                                                                        | _            | 9                | V     | (Note 3, Note 4)                                                     |  |

| D113          | IDDP   | Supply Current during Programming                                    | _                                                                                                                        | _            | 10               | mA    |                                                                      |  |

|               |        | Data EEPROM Memory <sup>(2)</sup>                                    |                                                                                                                          |              |                  |       |                                                                      |  |

| D120          | ED     | Byte Endurance                                                       | 100K                                                                                                                     | _            | _                | E/W   | -40°C to +85°C                                                       |  |

| D121          | Vdrw   | VDD for Read/Write                                                   | VDDMIN                                                                                                                   | _            | VDDMAX           | V     | Using EECON to read/write                                            |  |

| D122          | TDEW   | Erase/Write Cycle Time                                               | _                                                                                                                        | 3            | 4                | ms    |                                                                      |  |

| D123          | TRETD  | Characteristic Retention                                             | —                                                                                                                        | 40           | —                | Year  | Provided no other specifications are violated                        |  |

| D124          | TREF   | Number of Total Erase/Write Cycles before Refresh <sup>(2)</sup>     | 1M                                                                                                                       | 10M          | —                | E/W   | -40°C to +85°C                                                       |  |

| D130          |        | Program Flash Memory                                                 |                                                                                                                          |              |                  |       |                                                                      |  |

|               | Eр     | Cell Endurance                                                       | 10k                                                                                                                      | —            | —                | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D131          | Vpr    | VDD for Read                                                         | Vddmin                                                                                                                   | _            | VDDMAX           | V     |                                                                      |  |

| D131A         |        | Voltage on MCLR/VPP during<br>Erase/Program                          | 8.0                                                                                                                      | —            | 9.0              | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D131B         | VBE    | VDD for Bulk Erase                                                   | 2.7                                                                                                                      | —            | VDDMAX           | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D132          | Vpew   | VDD for Write or Row Erase                                           | 2.2<br>Vddmin                                                                                                            | _            | Vddmax<br>Vddmax | V     | PIC18LF1XK50<br>PIC18F1XK50                                          |  |

| D132A         | IPPPGM | Current on MCLR/VPP during<br>Erase/Write                            | _                                                                                                                        | 1.0          | —                | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D132B         | IDDPGM | Current on VDD during Erase/Write                                    | —                                                                                                                        | 5.0          | —                | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D133          | TPEW   | Erase/Write cycle time                                               | _                                                                                                                        | 2.0          | 2.8              | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$ |  |

| D134          | TRETD  | Characteristic Retention                                             | _                                                                                                                        | 40           | _                | Year  | Provided no other specifications are violated                        |  |

#### TABLE 27-5: MEMORY PROGRAMMING REQUIREMENTS

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: These specifications are for programming the on-chip program memory through the use of table write instructions.

2: Refer to Section 5.8 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

**3:** Required only if single-supply programming is disabled.

4: The MPLAB ICD 2 does not support variable VPP output. Circuitry to limit the ICD 2 VPP voltage must be placed between the ICD 2 and target system when programming or debugging with the ICD 2.

#### TABLE 27-6: USB MODULE SPECIFICATIONS

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C \le TA \le +85^{\circ}C$

| Param.<br>No. | Sym.   | Characteristic                         | Min. | Тур. | Max. | Units | Conditions                                                                     |

|---------------|--------|----------------------------------------|------|------|------|-------|--------------------------------------------------------------------------------|

| D313          | VUSB   | USB Voltage                            | 3.0  | _    | 3.6  | V     | Voltage on VUSB pin must be in<br>this range for proper USB<br>operation       |

| D314          | lı∟    | Input Leakage on pin                   | —    | _    | ±1   | μA    | Vss $\leq$ VPIN $\leq$ VDD pin at high impedance                               |

| D315          | VILUSB | Input Low Voltage for USB<br>Buffer    | —    | _    | 0.8  | V     | For VUSB range                                                                 |

| D316          | VIHUSB | Input High Voltage for USB<br>Buffer   | 2.0  | _    | _    | V     | For VUSB range                                                                 |

| D318          | VDIFS  | Differential Input Sensitivity         | _    | _    | 0.2  | V     | The difference between D+ and<br>D- must exceed this value while<br>VCM is met |

| D319          | Vсм    | Differential Common Mode<br>Range      | 0.8  | _    | 2.5  | V     |                                                                                |

| D320          | Zout   | Driver Output Impedance <sup>(1)</sup> | 28   | —    | 44   | Ω     |                                                                                |

| D321          | Vol    | Voltage Output Low                     | 0.0  | —    | 0.3  | V     | 1.5 k $\Omega$ load connected to 3.6V                                          |

| D322          | Voн    | Voltage Output High                    | 2.8  | —    | 3.6  | V     | 1.5 k $\Omega$ load connected to ground                                        |

**Note 1:** The D+ and D- signal lines have been built-in impedance matching resistors. No external resistors, capacitors or magnetic components are necessary on the D+/D- signal paths between the PIC18(L)F1XK50 family device and USB cable.

#### TABLE 27-7: THERMAL CONSIDERATIONS

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                           |      |       |                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------|------|-------|----------------------------------------------------------|--|--|

| Param.<br>No.                                                                                                            | Sym.      | Characteristic                            | Тур. | Units | Conditions                                               |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to<br>Ambient | 62.2 | °C/W  | 20-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                           | 77.7 | °C/W  | 20-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                           | 87.3 | °C/W  | 20-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                           | 36.1 | °C/W  | 20-pin QFN 5x5mm package                                 |  |  |

| TH02                                                                                                                     | θJC       | θJC Thermal Resistance Junction to Case   | 27.5 | °C/W  | 20-pin PDIP package                                      |  |  |

|                                                                                                                          |           |                                           | 23.1 | °C/W  | 20-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                           | 31.1 | °C/W  | 20-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                           | 12.2 | °C/W  | 20-pin QFN 5x5mm package                                 |  |  |

| TH03                                                                                                                     | TJMAX     | Maximum Junction Temperature              | 150  | °C    |                                                          |  |  |

| TH04                                                                                                                     | PD        | Power Dissipation                         |      | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation                | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                     | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                                                                                     | Pder      | Derated Power                             | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature, TJ = Junction Temperature

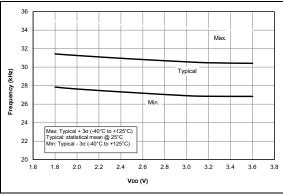

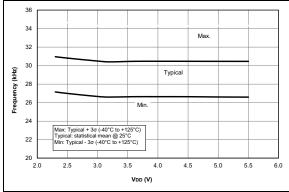

#### TABLE 27-9: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated)         Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                          |                    |      |              |      |            |                                                                               |