Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART, USB                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 14                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf13k50-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Switch From | Switch To            | Oscillator Delay                 |

|-------------|----------------------|----------------------------------|

| Sleep/POR   | LFINTOSC<br>HFINTOSC | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR   | LP, XT, HS           | 1024 clock cycles                |

| Sleep/POR   | EC, RC               | 8 clock cycles                   |

#### TABLE 2-2: EXAMPLES OF DELAYS DUE TO CLOCK SWITCHING

#### 2.9 4x Phase Lock Loop Frequency Multiplier

A Phase-Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency external oscillator or to operate at 32 MHz with the HFINTOSC. The PLL is designed for an input frequency from 4 MHz to 12 MHz. The PLL multiplies its input frequency by a factor of four when the PLL is enabled. This may be useful for customers who are concerned with EMI, due to high-frequency crystals.

Two bits control the PLL: the PLLEN bit of the CONFIG1H Configuration register and the SPLLEN bit of the OSCTUNE register. The PLL is enabled when the PLLEN bit is set and it is under software control when the PLLEN bit is cleared.

TABLE 2-3: PLL CONFIGURATION

| PLLEN | SPLLEN | PLL Status   |

|-------|--------|--------------|

| 1     | x      | PLL enabled  |

| 0     | 1      | PLL enabled  |

| 0     | 0      | PLL disabled |

#### 2.9.1 32 MHZ INTERNAL OSCILLATOR FREQUENCY SELECTION

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in CONFIG1H must be set to use the INTOSC source as the device system clock (FOSC<3:0> = 1000 or 1001).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<3:0> in CONFIG1H (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<2:0> = 110).

- The SPLLEN bit in the OSCTUNE register must be set to enable the 4xPLL, or the PLLEN bit of CONFIG1H must be programmed to a '1'.

| Note: | When using the PLLEN bit of CONFIG1H,    |

|-------|------------------------------------------|

|       | the 4xPLL cannot be disabled by software |

|       | and the 8 MHz HFINTOSC option will no    |

|       | longer be available.                     |

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

#### 2.10 CPU Clock Divider

The CPU Clock Divider allows the system clock to run at a slower speed than the Low/Full Speed USB module clock while sharing the same clock source. Only the oscillator defined by the settings of the FOSC bits of the CONFIG1H Configuration register may be used with the CPU Clock Divider. The CPU Clock Divider is controlled by the CPUDIV bits of the CONFIG1L Configuration register. Setting the CPUDIV bits will set the system clock to:

- Equal the clock speed of the USB module

- Half the clock speed of the USB module

- · One third the clock speed of the USB module

- · One fourth the clock speed of the USB module

For more information on the CPU Clock Divider, see Figure 2-1 and Register 24-1 CONFIG1L.

#### 3.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 3-1) contains the Stack Pointer value, the STKFUL (stack full) bit and the STKUNF (Stack Underflow) bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 24.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an underflow has the effect of vectoring the |

|-------|-------------------------------------------------------------------------------------|

|       | program to the Reset vector, where the                                              |

|       | stack conditions can be verified and                                                |

|       | appropriate actions can be taken. This is                                           |

|       | not the same as a Reset, as the contents                                            |

|       | of the SFRs are not affected.                                                       |

#### 3.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

#### REGISTER 3-1: STKPTR: STACK POINTER REGISTER

| R/C-0                                                                      | R/C-0                 | U-0              | R/W-0 | R/W-0            | R/W-0 | R/W-0              | R/W-0 |  |  |

|----------------------------------------------------------------------------|-----------------------|------------------|-------|------------------|-------|--------------------|-------|--|--|

| STKFUL <sup>(1)</sup>                                                      | STKUNF <sup>(1)</sup> | —                | SP4   | SP3              | SP2   | SP1                | SP0   |  |  |

| bit 7                                                                      |                       |                  |       | ·                |       | ·                  | bit 0 |  |  |

|                                                                            |                       |                  |       |                  |       |                    |       |  |  |

| Legend:                                                                    |                       |                  |       |                  |       |                    |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented C = Clearable only bit |                       |                  |       |                  |       |                    |       |  |  |

| -n = Value at POR '1' = Bit                                                |                       | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unknown |       |  |  |

|                                                                            |                       |                  |       |                  |       |                    |       |  |  |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack became full or overflowed</li> <li>0 = Stack has not become full or overflowed</li> </ul> |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                                              |

|         | <ul><li>1 = Stack underflow occurred</li><li>0 = Stack underflow did not occur</li></ul>                     |

| bit 5   | Unimplemented: Read as '0'                                                                                   |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                                                         |

|         |                                                                                                              |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

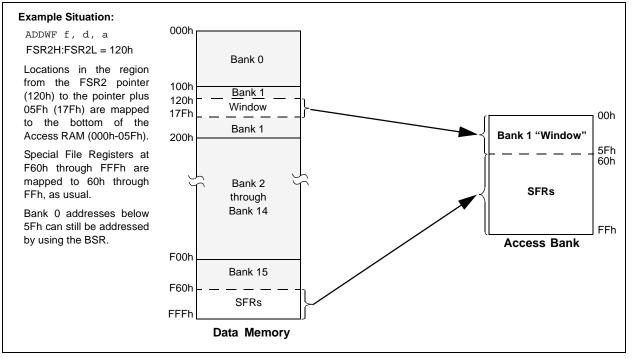

#### 3.5.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 3.3.3 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 3-10. Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

### 3.6 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 25.2 "Extended Instruction Set"**.

#### FIGURE 3-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

#### EXAMPLE 4-3: WRITING TO FLASH PROGRAM MEMORY

| ENAIVIFLE 4-3.   | WRITING | U FLASH FRUGRAM M |                                                                              |

|------------------|---------|-------------------|------------------------------------------------------------------------------|

|                  | MOVLW   | D'64′             | ; number of bytes in erase block                                             |

|                  | MOVWF   | COUNTER           |                                                                              |

|                  | MOVLW   | BUFFER_ADDR_HIGH  | ; point to buffer                                                            |

|                  | MOVWF   | FSR0H             |                                                                              |

|                  | MOVLW   | BUFFER_ADDR_LOW   |                                                                              |

|                  | MOVWF   | FSROL             |                                                                              |

|                  | MOVLW   | CODE_ADDR_UPPER   | ; Load TBLPTR with the base                                                  |

|                  | MOVWF   | TBLPTRU           | ; address of the memory block                                                |

|                  | MOVLW   | CODE_ADDR_HIGH    |                                                                              |

|                  | MOVWF   | TBLPTRH           |                                                                              |

|                  | MOVLW   | CODE_ADDR_LOW     |                                                                              |

|                  | MOVWF   | TBLPTRL           |                                                                              |

| READ_BLOCK       |         |                   |                                                                              |

|                  | TBLRD*+ |                   | ; read into TABLAT, and inc                                                  |

|                  | MOVF    | TABLAT, W         | ; get data                                                                   |

|                  | MOVWF   | POSTINCO          | ; store data                                                                 |

|                  | DECFSZ  | COUNTER           | ; done?                                                                      |

|                  | BRA     | READ_BLOCK        | ; repeat                                                                     |

| MODIFY_WORD      |         |                   | - <b>F</b>                                                                   |

|                  | MOVLW   | BUFFER_ADDR_HIGH  | ; point to buffer                                                            |

|                  | MOVWF   | FSR0H             |                                                                              |

|                  | MOVLW   | BUFFER_ADDR_LOW   |                                                                              |

|                  | MOVER   | FSR0L             |                                                                              |

|                  | MOVLW   | NEW_DATA_LOW      | ; update buffer word                                                         |

|                  | MOVWF   | POSTINC0          |                                                                              |

|                  | MOVLW   | NEW_DATA_HIGH     |                                                                              |

|                  | MOVWF   | INDF0             |                                                                              |

| ERASE_BLOCK      |         |                   |                                                                              |

|                  | MOVLW   | CODE_ADDR_UPPER   | ; load TBLPTR with the base                                                  |

|                  | MOVWF   | TBLPTRU           | ; address of the memory block                                                |

|                  | MOVLW   | CODE_ADDR_HIGH    |                                                                              |

|                  | MOVWF   | TBLPTRH           |                                                                              |

|                  | MOVLW   | CODE_ADDR_LOW     |                                                                              |

|                  | MOVWF   | TBLPTRL           |                                                                              |

|                  | BSF     | EECON1, EEPGD     | ; point to Flash program memory                                              |

|                  | BCF     | EECON1, CFGS      | ; access Flash program memory                                                |

|                  | BSF     | EECON1, WREN      | ; enable write to memory                                                     |

|                  | BSF     | EECON1, FREE      | ; enable Erase operation                                                     |

|                  | BCF     | INTCON, GIE       | ; disable interrupts                                                         |

|                  | MOVLW   | 55h               | -                                                                            |

| Required         | MOVWF   | EECON2            | ; write 55h                                                                  |

| Sequence         | MOVLW   | 0AAh              |                                                                              |

|                  | MOVWF   | EECON2            | ; write OAAh                                                                 |

|                  | BSF     | EECON1, WR        | ; start erase (CPU stall)                                                    |

|                  | BSF     | INTCON, GIE       | ; re-enable interrupts                                                       |

|                  | TBLRD*- |                   | ; dummy read decrement                                                       |

|                  | MOVLW   | BUFFER_ADDR_HIGH  | ; point to buffer                                                            |

|                  | MOVWF   | FSROH             | -                                                                            |

|                  | MOVLW   | BUFFER_ADDR_LOW   |                                                                              |

|                  | MOVWF   | FSROL             |                                                                              |

| WRITE_BUFFER_BAC |         |                   |                                                                              |

| ·                | MOVLW   | BlockSize         | ; number of bytes in holding register                                        |

|                  | MOVWF   | COUNTER           |                                                                              |

|                  | MOVLW   | D'64'/BlockSize   | ; number of write blocks in 64 bytes                                         |

|                  | MOVWF   | COUNTER2          |                                                                              |

| WRITE_BYTE_TO_HF |         |                   |                                                                              |

|                  | MOVF    | POSTINC0, W       | ; get low byte of buffer data                                                |

|                  | MOVWF   | TABLAT            | ; present data to table latch                                                |

|                  |         |                   | _                                                                            |

|                  | TBLWT+* |                   | ; write data, perform a short write                                          |

|                  | TBLWT+* |                   | ; write data, perform a short write<br>; to internal TBLWT holding register. |

| EXAMPLE 4-3:   | WRITI         | NG TO FLASH PROGR              | AM MEMORY (CONTINUED)                   |

|----------------|---------------|--------------------------------|-----------------------------------------|

|                | DECFSZ<br>BRA | COUNTER<br>WRITE_WORD_TO_HREGS | ; loop until holding registers are full |

| PROGRAM_MEMORY |               |                                |                                         |

|                | BSF           | EECON1, EEPGD                  | ; point to Flash program memory         |

|                | BCF           | EECON1, CFGS                   | ; access Flash program memory           |

|                | BSF           | EECON1, WREN                   | ; enable write to memory                |

|                | BCF           | INTCON, GIE                    | ; disable interrupts                    |

|                | MOVLW         | 55h                            |                                         |

| Required       | MOVWF         | EECON2                         | ; write 55h                             |

| Sequence       | MOVLW         | 0AAh                           |                                         |

|                | MOVWF         | EECON2                         | ; write OAAh                            |

|                | BSF           | EECON1, WR                     | ; start program (CPU stall)             |

|                | DCFSZ         | COUNTER2                       | ; repeat for remaining write blocks     |

|                | BRA           | WRITE_BYTE_TO_HREGS            | ;                                       |

|                | BSF           | INTCON, GIE                    | ; re-enable interrupts                  |

|                | BCF           | EECON1, WREN                   | ; disable write to memory               |

|                |               |                                | -                                       |

WRITING TO FLACU BROODAM MEMORY (CONTINUED)

#### 4.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 4.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

#### 4.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

#### 4.6 Flash Program Operation During Code Protection

See Section 24.3 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7      | Bit 6         | Bit 5       | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|------------|---------------|-------------|---------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | —          | —             | bit 21      | Program Me    | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 275                        |

| TBPLTRH | Program Me | emory Table   | Pointer H   | ligh Byte (TE | BLPTR<15:8    | S>)          |               |            | 275                        |

| TBLPTRL | Program Me | emory Table   | Pointer L   | ow Byte (TB   | LPTR<7:0>     | )            |               |            | 275                        |

| TABLAT  | Program Me | emory Table   | Latch       |               |               |              |               |            | 275                        |

| INTCON  | GIE/GIEH   | PEIE/GIEL     | TMR0IE      | INT0IE        | RABIE         | TMR0IF       | <b>INT0IF</b> | RABIF      | 275                        |

| EECON2  | EEPROM C   | Control Regis | ster 2 (not | a physical r  | egister)      |              |               |            | 277                        |

| EECON1  | EEPGD      | CFGS          |             | FREE          | WRERR         | WREN         | WR            | RD         | 277                        |

| IPR2    | OSCFIP     | C1IP          | C2IP        | EEIP          | BCLIP         | USBIP        | TMR3IP        | _          | 278                        |

| PIR2    | OSCFIF     | C1IF          | C2IF        | EEIF          | BCLIF         | USBIF        | TMR3IF        | —          | 278                        |

| PIE2    | OSCFIE     | C1IE          | C2IE        | EEIE          | BCLIE         | USBIE        | TMR3IE        |            | 278                        |

TABLE 4-3:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

| R/W-x        | R/W-x                              | U-0                                  | R/W-0          | R/W-x                                  | R/W-0           | R/S-0            | R/S-0          |

|--------------|------------------------------------|--------------------------------------|----------------|----------------------------------------|-----------------|------------------|----------------|

| EEPGD        | CFGS                               | —                                    | FREE           | WRERR                                  | WREN            | WR               | RD             |

| bit 7        |                                    |                                      |                |                                        |                 |                  | bit 0          |

|              |                                    |                                      |                |                                        |                 |                  |                |

| Legend:      |                                    |                                      |                |                                        |                 |                  |                |

| R = Readab   |                                    | W = Writable I                       |                |                                        |                 |                  |                |

|              | be set by software                 |                                      | ed             |                                        | nented bit, rea |                  |                |

| -n = Value a | t POR                              | '1' = Bit is set                     |                | '0' = Bit is cle                       | ared            | x = Bit is unki  | nown           |

| hit 7        | EEPCD: Elos                        | h Drogrom or F                       |                | Momony Solo                            | at hit          |                  |                |

| bit 7        |                                    | lash program r                       |                | / Memory Selec                         | JUDIL           |                  |                |

|              |                                    | lata EEPROM r                        |                |                                        |                 |                  |                |

| bit 6        |                                    |                                      | •              | Configuration S                        | elect bit       |                  |                |

|              | 1 = Access C                       | Configuration re                     | gisters        | C C                                    |                 |                  |                |

|              | 0 = Access F                       | lash program c                       | or data EEPR   | OM memory                              |                 |                  |                |

| bit 5        | Unimplemen                         | ted: Read as '                       | )'             |                                        |                 |                  |                |

| bit 4        |                                    | Row (Block) Er                       |                |                                        |                 |                  |                |

|              |                                    |                                      |                | dressed by TBL                         | PTR on the ne   | ext WR comman    | nd             |

|              | 0 = Perform                        | by completion of write-only          | or erase opera | allon)                                 |                 |                  |                |

| bit 3        |                                    | ,                                    | ta EEPROM I    | Error Flag bit <sup>(1)</sup>          |                 |                  |                |

|              |                                    |                                      |                | inated (any Res                        | et during self- | timed programr   | ning in normal |

|              | operation                          | n, or an imprope                     | er write attem | • •                                    | U               |                  | 0              |

|              | 0 = The write                      | e operation com                      | pleted         |                                        |                 |                  |                |

| bit 2        | WREN: Flash                        | n Program/Data                       | EEPROM W       | rite Enable bit                        |                 |                  |                |

|              |                                    |                                      |                | data EEPROM                            |                 |                  |                |

|              |                                    | •                                    | lash program   | /data EEPROM                           |                 |                  |                |

| bit 1        | WR: Write Co                       |                                      |                |                                        |                 |                  |                |

|              |                                    |                                      |                | cycle or a progra<br>bit is cleared by |                 |                  |                |

|              |                                    |                                      |                | ed) by software                        |                 |                  |                |

|              | 0 = Write cyc                      | le to the EEPR                       | OM is comple   | ete                                    |                 |                  |                |

| bit 0        | RD: Read Co                        | ntrol bit                            |                |                                        |                 |                  |                |

|              |                                    |                                      |                | s one cycle. RD                        |                 |                  |                |

|              | •                                  | ot cleared) by se<br>initiate an EEF |                | it cannot be set                       | when EEPGD      | = 1  or  CFGS =  | 1.)            |

|              |                                    |                                      |                |                                        |                 |                  |                |

|              | Vhen a WRERR of<br>rror condition. | occurs, the EEF                      | GD and CFG     | S bits are not o                       | leared. This a  | llows tracing of | the            |

| e            |                                    |                                      |                |                                        |                 |                  |                |

#### REGISTER 5-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

#### 7.0 INTERRUPTS

The PIC18(L)F1XK50 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 0008h and the low priority interrupt vector is at 0018h. A high priority interrupt event will interrupt a low priority interrupt that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

#### 7.1 Mid-Range Compatibility

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> microcontroller mid-range devices. In Compatibility mode, the interrupt priority bits of the IPRx registers have no effect. The PEIE bit of the INTCON register is the global interrupt enable for the peripherals. The PEIE bit disables only the peripheral interrupt sources when the GIE bit is also set. The GIE bit of the INTCON register is the global interrupt enable which enables all non-peripheral interrupt sources and disables all interrupt sources, including the peripherals. All interrupts branch to address 0008h in Compatibility mode.

#### 7.2 Interrupt Priority

The interrupt priority feature is enabled by setting the IPEN bit of the RCON register. When interrupt priority is enabled the GIE and PEIE global interrupt enable bits of Compatibility mode are replaced by the GIEH high priority, and GIEL low priority, global interrupt enables. When set, the GIEH bit of the INTCON register enables all interrupts that have their associated IPRx register or INTCONx register priority bit set (high priority). When clear, the GIEH bit disables all interrupt sources including those selected as low priority. When clear, the GIEL bit of the INTCON register disables only the interrupts that have their associated priority bit set (low priority). When set, the GIEL bit of the INTCON register disables only the interrupts that have their associated priority bit cleared (low priority). When set, the GIEL bit enables the low priority sources when the GIEH bit is also set.

When the interrupt flag, enable bit and appropriate global interrupt enable bit are all set, the interrupt will vector immediately to address 0008h for high priority, or 0018h for low priority, depending on level of the interrupting source's priority bit. Individual interrupts can be disabled through their corresponding interrupt enable bits.

#### 7.3 Interrupt Response

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. The GIE bit is the global interrupt enable when the IPEN bit is cleared. When the IPEN bit is set, enabling interrupt priority levels, the GIEH bit is the high priority global interrupt enable and the GIEL bit is the low priority global interrupt enable. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits in the INTCONx and PIRx registers. The interrupt flag bits must be cleared by software before re-enabling interrupts to avoid repeating the same interrupt.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB interrupt-on-change, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one-cycle or 2-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bits or the global interrupt enable bit.

| Name    | Bit 7    | Bit 6     | Bit 5                 | Bit 4                 | Bit 3                | Bit 2  | Bit 1                | Bit 0                | Reset<br>Values on<br>page |

|---------|----------|-----------|-----------------------|-----------------------|----------------------|--------|----------------------|----------------------|----------------------------|

| PORTA   |          |           | RA5 <sup>(1)</sup>    | RA4 <sup>(1)</sup>    | RA3 <sup>(2)</sup>   | _      | RA1 <sup>(3)</sup>   | RA0 <sup>(3)</sup>   | 278                        |

| LATA    | —        | _         | LATA5 <sup>(1)</sup>  | LATA4 <sup>(1)</sup>  | —                    | —      | —                    | _                    | 278                        |

| TRISA   | —        |           | TRISA5 <sup>(1)</sup> | TRISA4 <sup>(1)</sup> | _                    | _      |                      |                      | 278                        |

| ANSEL   | ANS7     | ANS6      | ANS5                  | ANS4                  | ANS3                 |        |                      |                      | 278                        |

| SLRCON  | —        | _         | —                     | _                     | _                    | SLRC   | SLRB                 | SLRA                 | 278                        |

| IOCA    | _        | -         | IOCA5                 | IOCA4                 | IOCA3 <sup>(2)</sup> | _      | IOCA1 <sup>(3)</sup> | IOCA0 <sup>(3)</sup> | 278                        |

| WPUA    | —        | -         | WPUA5                 | WPUA4                 | WPUA3 <sup>(2)</sup> | _      | _                    | _                    | 275                        |

| UCON    | _        | PPBRST    | SE0                   | PKTDIS                | USBEN                | RESUME | SUSPND               | _                    | 278                        |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE                | INT0IE                | RABIE                | TMR0IF | <b>INT0IF</b>        | RABIF                | 275                        |

| INTCON2 | RABPU    | INTEDG0   | INTEDG1               | INTEDG2               |                      | TMR0IP |                      | RABIP                | 275                        |

| TABLE 9-2: \$ | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|---------------|--------------------------------------------|

|---------------|--------------------------------------------|

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<5:4> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

2: Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

**3:** RA1 and RA0 are only available as port pins when the USB module is disabled (UCON<3 > = 0).

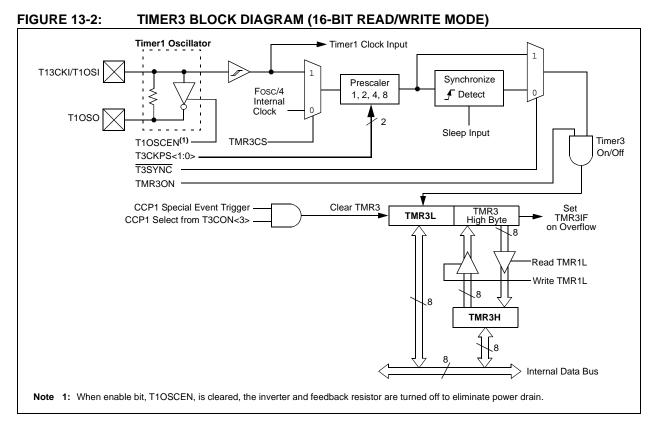

#### 13.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit of the T3CON register is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 13.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN bit of the T1CON register. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in **Section 11.0** "Timer1 Module".

#### 13.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF of the PIR2 register. This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE of the PIE2 register.

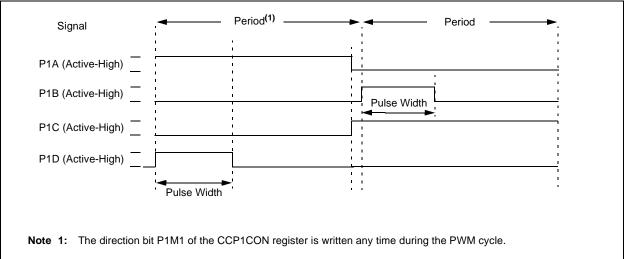

#### 14.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 14-10 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 14-11 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 14-8) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 14-10: EXAMPLE OF PWM DIRECTION CHANGE

### 14.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 14.4.8.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the RC\_RUN Power-Managed mode and the OSCFIF bit of the PIR2 register will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 14.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the enhanced CCP module to reset to a state compatible with the standard CCP module.

#### REGISTER 24-13: DEVID1: DEVICE ID REGISTER 1 FOR PIC18(L)F1XK50

| R                                                             | R                        | R               | R              | R            | R                | R        | R     |

|---------------------------------------------------------------|--------------------------|-----------------|----------------|--------------|------------------|----------|-------|

| DEV2                                                          | DEV1                     | DEV0            | REV4           | REV3         | REV2             | REV1     | REV0  |

| bit 7                                                         | ·                        |                 |                |              | •                |          | bit C |

|                                                               |                          |                 |                |              |                  |          |       |

| Legend:                                                       |                          |                 |                |              |                  |          |       |

| R = Readabl                                                   | e bit                    |                 |                | U = Unimpler | nented bit, read | l as '0' |       |

| -n = Value when device is unprogrammed C = Clearable only bit |                          |                 |                |              |                  |          |       |

|                                                               |                          |                 |                |              |                  |          |       |

| bit 7-5                                                       | <b>DEV&lt;2:0&gt;:</b> D | evice ID bits   |                |              |                  |          |       |

|                                                               | 010 = PIC18F             | -13K50          |                |              |                  |          |       |

|                                                               | 011 = PIC18F             | -14K50          |                |              |                  |          |       |

| bit 4-0                                                       | <b>REV&lt;4:0&gt;:</b> R | evision ID bits |                |              |                  |          |       |

|                                                               | These bits are           | e used to indic | ate the device | revision.    |                  |          |       |

|                                                               |                          |                 |                |              |                  |          |       |

| REGISTER                                                      | 24-14: DEVID             | 2: DEVICE I     | D REGISTEI     | R 2 FOR PIC1 | 8(L)F1XK50       |          |       |

|                                                               |                          | <b>D</b>        |                | P            | <b>D</b>         | P        |       |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:                                |                                    |

|----------------------------------------|------------------------------------|

| R = Readable bit                       | U = Unimplemented bit, read as '0' |

| -n = Value when device is unprogrammed | C = Clearable only bit             |

bit 7-0 **DEV<10:3>:** Device ID bits These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number. 0010 0000 = PIC18(L)F1XK50 devices

**Note 1:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

|                                   | Bit Clear                                                                                                                                                                                                                                                                                                                                                                                                                                            | f                  |      |                           |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|---------------------------|--|

| Syntax:                           | BCF f, b                                                                                                                                                                                                                                                                                                                                                                                                                                             | {,a}               |      |                           |  |

| Operands:                         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                |                    |      |                           |  |

| Operation:                        | $0 \rightarrow f < b >$                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |      |                           |  |

| Status Affected:                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |      |                           |  |

| Encoding:                         | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bbba               | ffff | ffff                      |  |

|                                   | Bit 'b' in register 'f' is cleared.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details |                    |      |                           |  |

| Literal Offset Mode" for details. |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |      |                           |  |

| Words:                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |      |                           |  |

| Words:<br>Cycles:                 | 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |      |                           |  |

|                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |      |                           |  |

| Cycles:                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3                 | 3    | Q4                        |  |

| Cycles:<br>Q Cycle Activity:      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3<br>Proce<br>Dat | ess  | Q4<br>Write<br>gister 'f' |  |

| Syntax:                       | BN n                                                                                                                                                                                                                                                                                            | BN n                                                     |                 |  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|--|--|--|--|--|

| Operands:                     | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                                    | -128 ≤ n ≤ 127                                           |                 |  |  |  |  |  |

| Operation:                    |                                                                                                                                                                                                                                                                                                 | if NEGATIVE bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |                 |  |  |  |  |  |

| Status Affected:              | None                                                                                                                                                                                                                                                                                            | None                                                     |                 |  |  |  |  |  |

| Encoding:                     | 1110                                                                                                                                                                                                                                                                                            | 0110 nn:                                                 | nn nnnn         |  |  |  |  |  |

| Description:                  | <ul> <li>If the NEGATIVE bit is '1', then the program will branch.</li> <li>The 2's complement number '2n' is added to the PC. Since the PC will hav incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a 2-cycle instruction.</li> </ul> |                                                          |                 |  |  |  |  |  |

| Words:                        | 1                                                                                                                                                                                                                                                                                               | 1                                                        |                 |  |  |  |  |  |

| Cycles:                       | 1(2)                                                                                                                                                                                                                                                                                            | 1(2)                                                     |                 |  |  |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                                                                                                                                                                                                                                                                                 |                                                          |                 |  |  |  |  |  |

| Q1                            | Q2                                                                                                                                                                                                                                                                                              | Q3                                                       | Q4              |  |  |  |  |  |

| Decode                        | Read literal<br>'n'                                                                                                                                                                                                                                                                             | Process<br>Data                                          | Write to PC     |  |  |  |  |  |

| No<br>operation               | No<br>operation                                                                                                                                                                                                                                                                                 | No<br>operation                                          | No<br>operation |  |  |  |  |  |

| If No Jump:                   |                                                                                                                                                                                                                                                                                                 |                                                          |                 |  |  |  |  |  |

| Q1                            | Q2                                                                                                                                                                                                                                                                                              | Q3                                                       | Q4              |  |  |  |  |  |

| Decode                        | Read literal                                                                                                                                                                                                                                                                                    | Process                                                  | No              |  |  |  |  |  |

|                               | 'n'                                                                                                                                                                                                                                                                                             | Data                                                     | operation       |  |  |  |  |  |

|                               | Example: HERE BN Jump                                                                                                                                                                                                                                                                           |                                                          |                 |  |  |  |  |  |

| 10                                     | - |                                                  |

|----------------------------------------|---|--------------------------------------------------|

| After Instruction                      |   |                                                  |

| If NEGATIVE<br>PC<br>If NEGATIVE<br>PC | = | 1;<br>address (Jump)<br>0;<br>address (HERE + 2) |

|                                        |   |                                                  |

| COMF              | Complement f                                                   |                         | CPFSEQ                  | Compare                     | f with W, sk                      | tip if f = W    |

|-------------------|----------------------------------------------------------------|-------------------------|-------------------------|-----------------------------|-----------------------------------|-----------------|

| Syntax:           | COMF f {,d {,a}}                                               |                         | Syntax:                 | CPFSEQ                      | f {,a}                            |                 |

| Operands:         | $0 \le f \le 255$                                              |                         | Operands:               | $0 \leq f \leq 255$         |                                   |                 |

| ·                 | d ∈ [0,1]                                                      |                         |                         | a ∈ [0,1]                   |                                   |                 |

|                   | a ∈ [0,1]                                                      |                         | Operation:              | (f) - (W),                  | (1.4.1)                           |                 |

| Operation:        | $(\overline{f}) \rightarrow dest$                              |                         |                         | skip if (f) =               | (VV)<br>comparison)               |                 |

| Status Affected:  | N, Z                                                           |                         | Status Affected:        | None                        | ionipaneen)                       |                 |

| Encoding:         | 0001 11da fff                                                  | f ffff                  | Encoding:               | 0110                        | 001a ffi                          | ff ffff         |

| Description:      | The contents of register 'f'                                   | are                     | Description:            |                             |                                   | f data memory   |

|                   | complemented. If 'd' is '0',                                   |                         | Docomption              | •                           | o the contents                    |                 |

|                   | stored in W. If 'd' is '1', the                                |                         |                         |                             | an unsigned s                     |                 |

|                   | stored back in register 'f' (<br>If 'a' is '0', the Access Bar | ,                       |                         |                             | en the fetched                    |                 |

|                   | If 'a' is '1', the BSR is used                                 |                         |                         |                             | nd a NOP is ex<br>king this a 2-c |                 |

|                   | GPR bank (default).                                            |                         |                         | instruction.                |                                   | yele            |

|                   | If 'a' is '0' and the extende                                  |                         |                         | lf 'a' is '0', t            | he Access Bar                     | nk is selected. |

|                   | set is enabled, this instruc<br>in Indexed Literal Offset A    | •                       |                         | ,                           |                                   | d to select the |

|                   | mode whenever $f \le 95$ (5F                                   | -                       |                         | GPR bank<br>If 'a' is '0' a | nd the extende                    | ed instruction  |

|                   | Section 25.2.3 "Byte-Ori                                       |                         |                         |                             | ed, this instruc                  |                 |

|                   | Bit-Oriented Instructions<br>Literal Offset Mode" for          |                         |                         |                             | Literal Offset A                  | -               |

|                   |                                                                | Jelans.                 |                         |                             | ever f ≤ 95 (5l                   | ,               |

| Words:            | 1                                                              |                         |                         |                             | .2.3 "Byte-Ori<br>d Instruction   |                 |

| Cycles:           | 1                                                              |                         |                         | Literal Offs                | set Mode" for                     | details.        |

| Q Cycle Activity: |                                                                |                         | Words:                  | 1                           |                                   |                 |

| Q1                | Q2 Q3                                                          | Q4                      | Cycles:                 | 1(2)                        |                                   |                 |

| Decode            | Read Process<br>register 'f' Data                              | Write to<br>destination |                         |                             | ycles if skip an                  |                 |

|                   | Tegiotor 1 Data                                                | destination             | Q Cycle Activity:       | by                          | a 2-word instru                   | lction.         |

| Example:          | COMF REG, 0, 0                                                 |                         | Q Cycle Activity.<br>Q1 | Q2                          | Q3                                | Q4              |

| Before Instru     |                                                                |                         | Decode                  | Read                        | Process                           | No              |

| REG               | = 13h                                                          |                         |                         | register 'f'                | Data                              | operation       |

| After Instruc     |                                                                |                         | lf skip:                |                             |                                   |                 |

| REG<br>W          | = 13h<br>= ECh                                                 |                         | Q1                      | Q2                          | Q3                                | Q4              |

| vv                |                                                                |                         | No<br>operation         | No<br>operation             | No<br>operation                   | No<br>operation |

|                   |                                                                |                         | If skip and followe     |                             |                                   | operation       |

|                   |                                                                |                         | Q1                      | Q2                          | Q3                                | Q4              |

|                   |                                                                |                         | No                      | No                          | No                                | No              |

|                   |                                                                |                         | operation               | operation                   | operation                         | operation       |

|                   |                                                                |                         | No                      | No                          | No                                | No              |

|                   |                                                                |                         | operation               | operation                   | operation                         | operation       |

|                   |                                                                |                         | Example:                | HERE                        | CPFSEQ REG                        | B, O            |

|                   |                                                                |                         |                         | NEQUAL<br>EQUAL             | :                                 |                 |

|                   |                                                                |                         | Before Instruc          | ~                           |                                   |                 |

|                   |                                                                |                         | PC Addr                 |                             | RE                                |                 |

|                   |                                                                |                         | W                       | = ?                         |                                   |                 |

|                   |                                                                |                         | REG                     | = ?                         |                                   |                 |

|                   |                                                                |                         | After Instruction       |                             |                                   |                 |

|                   |                                                                |                         | If REG                  | = W;                        |                                   |                 |