Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 14                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 20-VQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf14k50-i-mq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3.1 PRIMARY EXTERNAL OSCILLATOR SHUTDOWN

The Primary External Oscillator can be enabled or disabled via software. To enable software control of the Primary External Oscillator, the PCLKEN bit of the CONFIG1H Configuration register must be set. With the PCLKEN bit set, the Primary External Oscillator is controlled by the PRI\_SD bit of the OSCCON2 register. The Primary External Oscillator will be enabled when the PRI\_SD bit is set, and disabled when the PRI\_SD bit is clear.

**Note:** The Primary External Oscillator cannot be shut down when it is selected as the System Clock. To shut down the oscillator, the system clock source must be either the Secondary Oscillator or the Internal Oscillator.

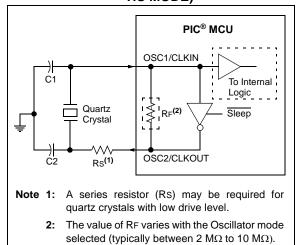

#### 2.3.2 LP, XT AND HS OSCILLATOR MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 2-2). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 2-2 and Figure 2-3 show typical circuits for quartz crystal and ceramic resonators, respectively.

# FIGURE 2-2:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

# 2.12 Two-Speed Start-up Mode

Two-Speed Start-Up mode provides additional power savings by minimizing the latency between external Oscillator Start-up Timer (OST) and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the OST period, which can reduce the overall power consumption of the device.

Two-Speed Start-Up mode is enabled by setting the IESO bit of the CONFIG1H Configuration register. With Two-Speed Start-up enabled, the device will execute instructions using the internal oscillator during the Primary External Oscillator OST period.

When the system clock is set to the Primary External Oscillator and the oscillator is configured for LP, XT or HS modes, the device will not execute code during the OST period. The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-Up mode minimizes the delay in code execution by operating from the internal oscillator while the OST is active. The system clock will switch back to the Primary External Oscillator after the OST period has expired.

Two-speed Start-up will become active after:

- Power-on Reset (POR)

- Power-up Timer (PWRT), if enabled

- Wake-up from Sleep

The OSTS bit of the OSCCON register reports which oscillator the device is currently using for operation. The device is running from the oscillator defined by the FOSC bits of the CONFIG1H Configuration register when the OSTS bit is set. The device is running from the internal oscillator when the OSTS bit is clear.

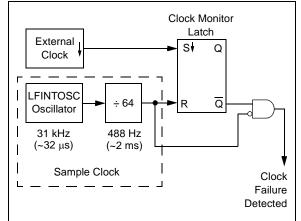

# 2.13 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the CONFIG1H Configuration register. The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC and RC).

#### FIGURE 2-6:

#### **FSCM BLOCK DIAGRAM**

#### 2.13.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 2-6. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

### 2.13.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSCFIF of the PIR2 register. The OSCFIF flag will generate an interrupt if the OSCFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation. An automatic transition back to the failed clock source will not occur.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

| REGISTER 7      | -/: PIE2:1                      | PERIPHERA         | LINIERRU       | PIENABLE         | (FLAG) REG       | ISTER 2         |     |

|-----------------|---------------------------------|-------------------|----------------|------------------|------------------|-----------------|-----|

| R/W-0           | R/W-0                           | R/W-0             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | U-0 |

| OSCFIE          | C1IE                            | C2IE              | EEIE           | BCLIE            | USBIE            | TMR3IE          |     |

| bit 7           | ·                               |                   |                |                  |                  |                 | bi  |

|                 |                                 |                   |                |                  |                  |                 |     |

| Legend:         |                                 |                   |                |                  |                  |                 |     |

| R = Readable    | bit                             | W = Writable      | bit            | U = Unimpler     | mented bit, read | d as '0'        |     |

| -n = Value at F | POR                             | '1' = Bit is set  | t              | '0' = Bit is cle | eared            | x = Bit is unkn | own |

| bit 7           | OSCFIE: Osc                     | illator Fail Inte | rrupt Enable I | oit              |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 6           | C1IE: Compa                     | rator C1 Interr   | upt Enable bit | t                |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 5           | C2IE: Compa                     | rator C2 Interr   | upt Enable bit | t                |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 4           | EEIE: Data E                    | EPROM/Flash       | Write Operat   | ion Interrupt Er | nable bit        |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 3           | BCLIE: Bus (                    | Collision Interru | upt Enable bit |                  |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 2           | USBIE: USB Interrupt Enable bit |                   |                |                  |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

| bit 1           | TMR3IE: TMF                     | R3 Overflow In    | terrupt Enable | e bit            |                  |                 |     |

|                 | 1 = Enabled<br>0 = Disabled     |                   |                |                  |                  |                 |     |

|                 | Unimplemen                      |                   |                |                  |                  |                 |     |

# REGISTER 7-7: PIE2: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 2

# 8.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC18F1XK50 devices differ from the PIC18LF1XK50 devices due to an internal Low Dropout (LDO) voltage regulator. The PIC18F1XK50 contain an internal LDO, while the PIC18LF1XK50 do not.

The lithography of the die allows a maximum operating voltage of the nominal 3.6V on the internal digital logic. In order to continue to support 5.0V designs, a LDO voltage regulator is integrated on the die. The LDO voltage regulator allows for the internal digital logic to operate at 3.3V, while I/O's operate at 5.0V (VDD).

The LDO voltage regulator requires an external bypass capacitor for stability. The VUSB pin is required to have an external bypass capacitor. It is recommended that the capacitor be a ceramic cap between 0.22 to 0.47  $\mu$ F.

On power-up, the external capacitor will look like a large load on the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information, refer to **Section 27.0 "Electrical Specifications"**.

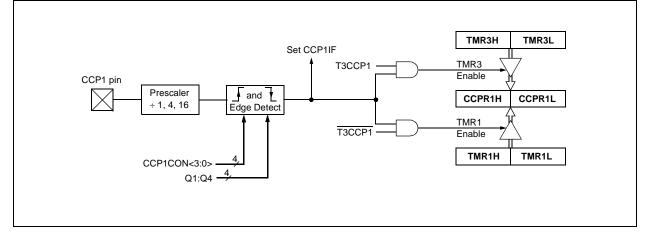

# 14.2 Capture Mode

In Capture mode, the CCPR1H:CCPR1L register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding CCP1 pin. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by the mode select bits, CCP1M<3:0> of the CCP1CON register. When a capture is made, the interrupt request flag bit, CCP1IF, is set; it must be cleared by software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 14.2.1 CCP PIN CONFIGURATION

In Capture mode, the appropriate CCP1 pin should be configured as an input by setting the corresponding TRIS direction bit.

**Note:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### 14.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 14.1.1 "CCP Module and Timer Resources").

### 14.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCP1IF, should also be cleared following any such change in operating mode.

#### 14.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCP1M<3:0>). Whenever the CCP module is turned off or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 14-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 14-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       |             |   | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

### FIGURE 14-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 14.4.7.1 Steering Synchronization

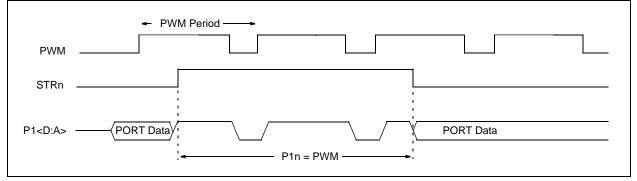

The STRSYNC bit of the PSTRCON register gives the user two selections of when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRCON register. In this case, the output signal at the P1<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

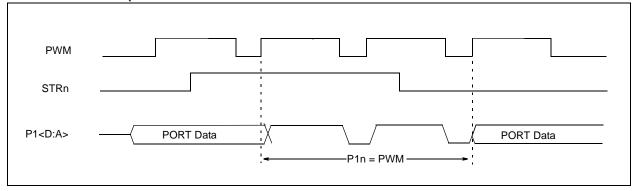

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform. Figures 14-17 and 14-18 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

# FIGURE 14-17: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 14-18: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

#### SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0) **FIGURE 15-5:**

|                                       | ······                   | · · · · · · · · · · · · · · · · · · · | ······ 3 \$······ 3 \$·· |                         | •<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|--------------------------|---------------------------------------|--------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -80K<br>(082 ≈ 0<br>0KE ≈ 0)          | ······                   |                                       |                          |                         | (<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| · · · · · · · · · · · · · · · · · · · |                          |                                       |                          | ;<br>;<br>;             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (CRP = 1<br>(CRP = 1<br>(CRP = 2)     |                          |                                       |                          |                         | 5<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SREET                                 |                          |                                       |                          |                         | )<br>;<br>;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| · · · · · · · · · · · · · · · · · · · |                          |                                       | January January          |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                       | <u>887 X 886 X</u>       |                                       | Care d Xare d V          | X_683_X68.9             | 1 - Second<br>1 - Second |

| - 5559<br>- (58587                    |                          |                                       |                          |                         | ,<br>,<br>,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                       | 27 4 4<br>4 4<br>2 4 2 4 |                                       |                          | - 888 80 - 1<br>- a - a |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                       |                          |                                       |                          |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                       | 8 5<br>2 5<br>2 2        | 5 K<br>5 K<br>2 S                     | 2 5<br>2 5<br>2 2        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Historica (<br>Historica)             | с с<br>                  | * 1<br>* 2                            | с. с.<br>с. с.<br>с. с.  | • •<br>•                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I SARAA II II II                      |                          | 2                                     | 5 K                      | i dije                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

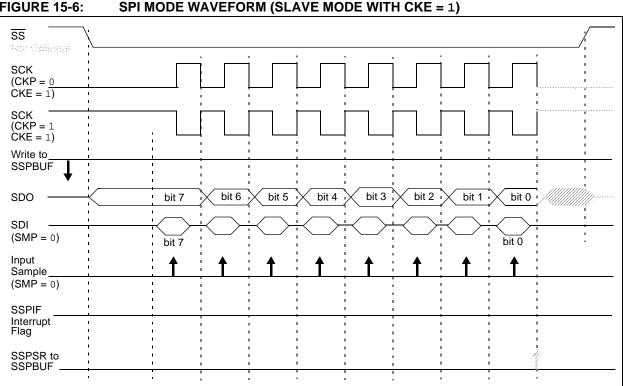

#### FIGURE 15-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

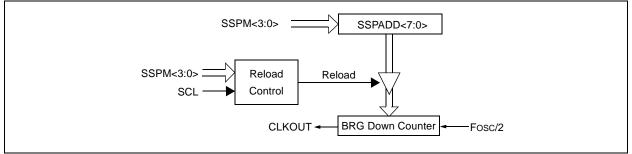

#### 15.3.7 BAUD RATE

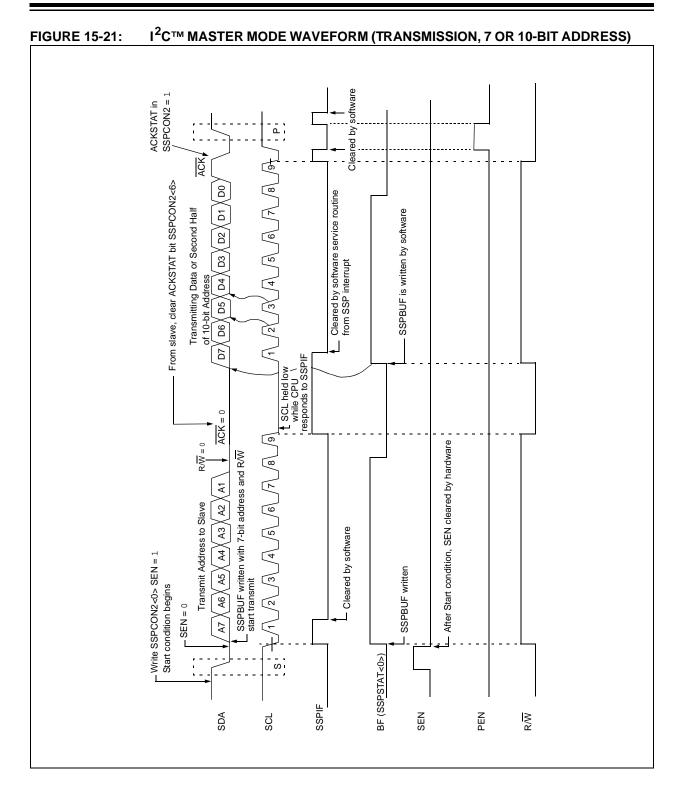

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Figure 15-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 15-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### EQUATION 15-1:

$$FSCL = \frac{FOSC}{(SSPADD + 1)(4)}$$

# FIGURE 15-17: BAUD RATE GENERATOR BLOCK DIAGRAM

### TABLE 15-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE W/BRG

| Fosc   | Fcy    | BRG Value | Fsc∟<br>(2 Rollovers of BRG) |

|--------|--------|-----------|------------------------------|

| 48 MHz | 12 MHz | 0Bh       | 1 MHz <sup>(1)</sup>         |

| 48 MHz | 12 MHz | 1Dh       | 400 kHz                      |

| 48 MHz | 12 MHz | 77h       | 100 kHz                      |

| 40 MHz | 10 MHz | 18h       | 400 kHz <sup>(1)</sup>       |

| 40 MHz | 10 MHz | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz | 4 MHz  | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz  | 1 MHz  | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

#### FIGURE 16-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| VOLE DE                                 | 30       | il ast by t |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 3 N.S.N.S.N.<br>                             | <u> </u>                                                                        | <u>Nanva</u> | ninnu                           | antarur.                     |                         | unununun<br>Asto Oseres      | d No. |

|-----------------------------------------|----------|-------------|---------------------------------|-----------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|--------------|---------------------------------|------------------------------|-------------------------|------------------------------|-------|

|                                         |          |             |                                 | -4.<br>                                 | <br>:<br>' <i>1111111111111</i><br>'         | 1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1 | ;<br>;<br>;; |                                 |                              | , y.,<br>y., y.,<br>g., |                              |       |

| - Maaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa | <br><br> |             | i<br>Milianiania<br>Verseise es |                                         | <br>r<br><b>Hillinini</b><br>Biltini Barbart |                                                                                 |              | - Olyaceri da<br>Millillillilli | s to Şisar Raoc<br>Millimini | s et 3000<br>Millinnin  | 9052<br><i>инииниини</i> ини | HIR.  |

© 2008-2015 Microchip Technology Inc.

### 17.1.6 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital Conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared by software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine. Please see **Section 17.1.6** "**Interrupts**" for more information.

# TABLE 17-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |                         |                         |                               |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------------|

| ADC Clock Source | ADCS<2:0>    | 48 MHz                  | 16 MHz                  | 4 MHz                   | 1 MHz                         |

| Fosc/2           | 000          | 41.67 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                        |

| Fosc/4           | 100          | 83.33 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>   | 1.0 μs                  | 4.0 μs                        |

| Fosc/8           | 001          | 167 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <b>(3)</b>             |

| Fosc/16          | 101          | 333 ns <sup>(2)</sup>   | 1.0 μs                  | 4.0 μs                  | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32          | 010          | 667 ns <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>        |

| Fosc/64          | 110          | 1.33 μs                 | 4.0 μs                  | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>        |

| FRC              | x11          | 1-4 μs <sup>(1,4)</sup> | 1-4 μs <sup>(1,4)</sup> | 1-4 μs <sup>(1,4)</sup> | 1-4 μs <sup>(1,4)</sup>       |

Legend: Shaded cells are outside of recommended range.

- Note 1: The FRC source has a typical TAD time of 1.7  $\mu$ s.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

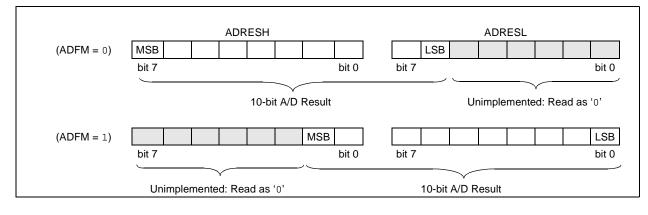

### 17.1.7 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON2 register controls the output format.

Figure 17-2 shows the two output formats.

### FIGURE 17-2: 10-BIT A/D CONVERSION RESULT FORMAT

## **18.8 Additional Comparator Features**

There are four additional comparator features:

- Simultaneous read of comparator outputs

- Internal reference selection

- · Hysteresis selection

- Output Synchronization

#### 18.8.1 SIMULTANEOUS COMPARATOR OUTPUT READ

The MC1OUT and MC2OUT bits of the CM2CON1 register are mirror copies of both comparator outputs. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

| Note 1: | Obtaining                                | the  | status   | of  | C1OUT   | or  |

|---------|------------------------------------------|------|----------|-----|---------|-----|

|         | C2OUT by                                 | read | ling CM2 | 2CO | N1 does | not |

|         | affect the comparator interrupt mismatch |      |          |     |         |     |

|         | registers.                               |      |          |     |         |     |

#### 18.8.2 INTERNAL REFERENCE SELECTION

There are two internal voltage references available to the non-inverting input of each comparator. One of these is the Fixed Voltage Reference (FVR) and the other is the variable Comparator Voltage Reference (CVREF). The CxRSEL bit of the CM2CON register determines which of these references is routed to the Comparator Voltage reference output (CxVREF). Further routing to the comparator is accomplished by the CxR bit of the CMxCON0 register. See **Section 21.1 "Voltage Reference"** and Figure 18-2 and Figure 18-3 for more detail.

### 18.8.3 COMPARATOR HYSTERESIS

The Comparator Cx have selectable hysteresis. The hysteresis can be enable by setting the CxHYS bit of the CM2CON1 register. See **Section 27.0** "**Electrical Specifications**" for more details.

#### 18.8.4 SYNCHRONIZING COMPARATOR OUTPUT TO TIMER 1

The Comparator Cx output can be synchronized with Timer1 by setting the CxSYNC bit of the CM2CON1 register. When enabled, the Cx output is latched on the rising edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the rising edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 18-2 and Figure 18-3) and the Timer1 Block Diagram (Figure 18-2) for more information.

# 19.1.3 MULTIPLE FUNCTIONS OF THE SLEEP COMMAND

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit of the OSCCON register at the time the instruction is executed. All clocks stop and minimum power is consumed when SLEEP is executed with the IDLEN bit cleared. The system clock continues to supply a clock to the peripherals but is disconnected from the CPU when SLEEP is executed with the IDLEN bit set.

# 19.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

### 19.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled (see **Section 2.12 "Two-Speed Start-up Mode"** for details). In this mode, the device operated off the oscillator defined by the FOSC bits of the CONFIGH Configuration register.

### 19.2.2 SEC\_RUN MODE

In SEC\_RUN mode, the CPU and peripherals are clocked from the secondary external oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by setting the SCS<1:0> bits of the OSCCON register to '01'. When SEC\_RUN mode is active all of the following are true:

- The main clock source is switched to the secondary external oscillator

- Primary external oscillator is shut down

- T1RUN bit of the T1CON register is set

- OSTS bit is cleared.

| Note: | The secondary external oscillator should  |

|-------|-------------------------------------------|

|       | already be running prior to entering      |

|       | SEC_RUN mode. If the T1OSCEN bit is       |

|       | not set when the SCS<1:0> bits are set to |

|       | '01', entry to SEC_RUN mode will not      |

|       | occur until T1OSCEN bit is set and        |

|       | secondary external oscillator is ready.   |

# 19.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator. In this mode, the primary external oscillator is shut down. RC\_RUN mode provides the best power conservation of all the Run modes when the LFINTOSC is the system clock.

RC\_RUN mode is entered by setting the SCS1 bit. When the clock source is switched from the primary oscillator to the internal oscillator, the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

### 19.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block from the HFINTOSC multiplexer output. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. It is recommended that SCS0 also be cleared, although its value is ignored, to maintain software compatibility with future devices. The HFINTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the HFINTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the HFINTOSC output is enabled. The IOSF bit becomes set, after the HFINTOSC output becomes stable, after an interval of TiOBST. Clocks to the peripherals continue while the HFINTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the HFINTOSC source was already stable, the IOSF bit will remain set. If the IRCF bits and INTSRC are all clear, the HFINTOSC output will not be enabled, the IOSF bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the HFINTOSC multiplexer output. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the HFINTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The LFINTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 19.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by any one of the following:

- an interrupt

- a Reset

- a Watchdog Time-out

This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 19.2 "Run Modes", Section 19.3 "Sleep Mode" and Section 19.4 "Idle Modes").

#### 19.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The PEIE blt must also be set If the desired interrupt enable bit is in a PIE register. The exit sequence is initiated when the corresponding interrupt flag bit is set.

The instruction immediately following the SLEEP instruction is executed on all exits by interrupt from Idle or Sleep modes. Code execution then branches to the interrupt vector if the GIE/GIEH bit of the INTCON register is set, otherwise code execution continues without branching (see Section 7.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 19.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 19.2 "Run Modes" and Section 19.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by any one of the following:

- executing a **SLEEP** instruction

- executing a CLRWDT instruction

- the loss of the currently selected clock source when the Fail-Safe Clock Monitor is enabled

- modifying the IRCF bits in the OSCCON register when the internal oscillator block is the device clock source

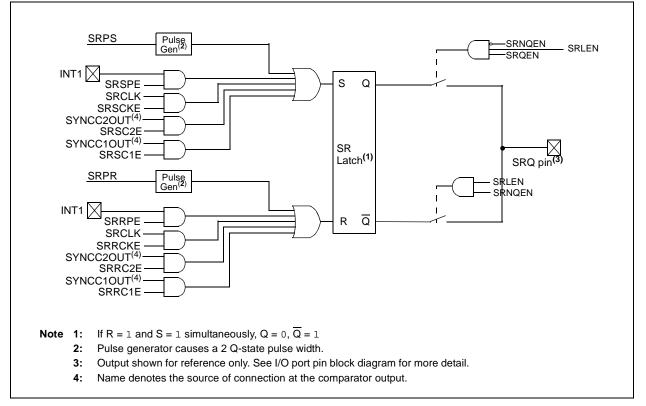

# 20.0 SR LATCH

The module consists of a single SR Latch with multiple Set and Reset inputs as well as selectable latch output. The SR Latch module includes the following features:

- Programmable input selection

- SR Latch output is available internally/externally

- Selectable Q and  $\overline{Q}$  output

- Firmware Set and Reset

# 20.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by CxOUT, INT1 pin, or variable clock. Additionally the SRPS and the SRPR bits of the SRCON0 register may be used to Set or Reset the SR Latch, respectively. The latch is reset-dominant, therefore, if both Set and Reset inputs are high the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

# 20.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the latch output selection. Only one of the SR latch's outputs may be directly output to an I/O pin at a time. Priority is determined by the state of bits SRQEN and SRNQEN in registers SRCON0.

| TABLE 20-1: | SR LATCH OUTPUT |  |  |  |

|-------------|-----------------|--|--|--|

|             | CONTROL         |  |  |  |

| SRLEN | SRQEN | SRNQEN | SR Latch Output<br>to Port I/O |

|-------|-------|--------|--------------------------------|

| 0     | Х     | Х      | I/O                            |

| 1     | 0     | 0      | I/O                            |

| 1     | 0     | 1      | Q                              |

| 1     | 1     | 0      | Q                              |

| 1     | 1     | 1      | Q                              |

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

# 20.3 Effects of a Reset

Upon any device Reset, the SR latch is not initialized. The user's firmware is responsible to initialize the latch output before enabling it to the output pins.

#### FIGURE 20-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

# 22.7 Oscillator

The USB module has specific clock requirements. For full-speed operation, the clock source must be 48 MHz. Even so, the microcontroller core and other peripherals are not required to run at that clock speed. Available clocking options are described in detail in **Section 2.11** "**USB Operation**".

### 22.8 Interrupt-on-Change for D+/D-Pins

The PIC18(L)F1XK50 has interrupt-on-change functionality on both D+ and D- data pins. This feature allows the device to detect voltage level changes when first connected to a USB host/hub.

The USB host/hub has 15K pull-down resistors on the D+ and D- pins. When the PIC18(L)F1XK50 attaches to the bus the D+ and D- pins can detect voltage changes. External resistors are needed for each pin to maintain a high state on the pins when detached. The USB module must be disable (USBEN = 0) for the interrupt-on-change to function. Enabling the USB module (USBEN = 1) will automatically disable the interrupt-on-change for D+ and D- pins. Refer to Section 7.11 "PORTA and PORTB Interrupt-on-Change" for mode detail.

# 22.9 USB Firmware and Drivers

Microchip provides a number of application-specific resources, such as USB firmware and driver support. Refer to www.microchip.com for the latest firmware and driver support.

| Name   | Bit 7    | Bit 6     | Bit 5   | Bit 4  | Bit 3    | Bit 2   | Bit 1         | Bit 0   | Details on<br>Page |

|--------|----------|-----------|---------|--------|----------|---------|---------------|---------|--------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE | RABIE    | TMR0IF  | <b>INT0IF</b> | RABIF   | 66                 |

| IPR2   | OSCFIP   | C1IP      | C2IP    | EEIP   | BCL1IP   | USBIP   | TMR3IP        | _       | 74                 |

| PIR2   | OSCFIF   | C1IF      | C2IF    | EEIF   | BCL1IF   | USBIF   | TMR3IF        | —       | 70                 |

| PIE2   | OSCFIE   | C1IE      | C2IE    | EEIE   | BCL1IE   | USBIE   | TMR3IE        | —       | 72                 |

| UCON   | —        | PPBRST    | SE0     | PKTDIS | USBEN    | RESUME  | SUSPND        | —       | 242                |

| UCFG   | UTEYE    | _         | _       | UPUEN  | _        | FSEN    | PPB1          | PPB0    | 244                |

| USTAT  | _        | ENDP3     | ENDP2   | ENDP1  | ENDP0    | DIR     | PPBI          | —       | 246                |

| UADDR  | —        | ADDR6     | ADDR5   | ADDR4  | ADDR3    | ADDR2   | ADDR1         | ADDR0   | 248                |

| UFRML  | FRM7     | FRM6      | FRM5    | FRM4   | FRM3     | FRM2    | FRM1          | FRM0    | 242                |

| UFRMH  | _        | —         | _       | _      | —        | FRM10   | FRM9          | FRM8    | 242                |

| UIR    | —        | SOFIF     | STALLIF | IDLEIF | TRNIF    | ACTVIF  | UERRIF        | URSTIF  | 256                |

| UIE    | _        | SOFIE     | STALLIE | IDLEIE | TRNIE    | ACTVIE  | UERRIE        | URSTIE  | 258                |

| UEIR   | BTSEF    | _         | _       | BTOEF  | DFN8EF   | CRC16EF | CRC5EF        | PIDEF   | 259                |

| UEIE   | BTSEE    | —         | _       | BTOEE  | DFN8EE   | CRC16EE | CRC5EE        | PIDEE   | 260                |

| UEP0   | _        | _         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP1   | _        | _         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP2   | —        | —         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP3   | _        | _         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP4   | —        | —         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP5   | —        | —         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP6   | _        | _         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

| UEP7   | —        | —         | _       | EPHSHK | EPCONDIS | EPOUTEN | EPINEN        | EPSTALL | 247                |

TABLE 22-4:

REGISTERS ASSOCIATED WITH USB MODULE OPERATION<sup>(1)</sup>

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the USB module.

**Note 1:** This table includes only those hardware mapped SFRs located in Bank 15 of the data memory space. The Buffer Descriptor registers, which are mapped into Bank 4 and are not true SFRs, are listed separately in Table 22-3.

| RCA   | LL             | Relative C                                                                                                                                                                                                                                                                                                                                                      | Relative Call                                                 |      |      |         |  |  |  |  |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------|---------|--|--|--|--|

| Synta | ax:            | RCALL n                                                                                                                                                                                                                                                                                                                                                         | RCALL n                                                       |      |      |         |  |  |  |  |