Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 14                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf14k50-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 OSCILLATOR MODULE

### 2.1 Overview

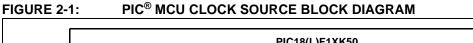

The oscillator module has a variety of clock sources and features that allow it to be used in a wide range of applications, maximizing performance and minimizing power consumption. Figure 2-1 illustrates a block diagram of the oscillator module.

Key features of the oscillator module include:

- System Clock Selection

- Primary External Oscillator

- Secondary External Oscillator

- Internal Oscillator

- Oscillator Start-up Timer

- System Clock Selection

- Clock Switching

- 4x Phase Lock Loop Frequency Multiplier

- CPU Clock Divider

- USB Operation

- Low-Speed

- Full-Speed

- Two-Speed Start-up Mode

- Fail-Safe Clock Monitoring

# 2.2 System Clock Selection

The SCS bits of the OSCCON register select between the following clock sources:

- Primary External Oscillator

- Secondary External Oscillator

Internal Oscillator

| Note: | The frequ | ueno | cy of | the sys | stem clock wi | ill be |

|-------|-----------|------|-------|---------|---------------|--------|

|       | referred  | to   | as    | Fosc    | throughout    | this   |

|       | documer   | ıt.  |       |         |               |        |

| TABLE 2-1: | SYSTEM CLOCK SELECTION |

|------------|------------------------|

|------------|------------------------|

| Configuration               | Selection                          |

|-----------------------------|------------------------------------|

| SCS <1:0>                   | System Clock                       |

| 1x                          | Internal Oscillator                |

| 01                          | Secondary External Oscillator      |

| 00<br>(Default after Reset) | Oscillator defined by<br>FOSC<3:0> |

The default state of the SCS bits sets the system clock to be the oscillator defined by the FOSC bits of the CONFIG1H Configuration register. The system clock will always be defined by the FOSC bits until the SCS bits are modified in software.

When the Internal Oscillator is selected as the system clock, the IRCF bits of the OSCCON register and the INTSRC bit of the OSCTUNE register will select either the LFINTOSC or the HFINTOSC. The LFINTOSC is selected when the IRCF<2:0> = 000 and the INTSRC bit is clear. All other combinations of the IRCF bits and the INTSRC bit will select the HFINTOSC as the system clock.

# 2.3 Primary External Oscillator

The Primary External Oscillator's mode of operation is selected by setting the FOSC<3:0> bits of the CONFIG1H Configuration register. The oscillator can be set to the following modes:

- LP: Low-Power Crystal

- XT: Crystal/Ceramic Resonator

- HS: High-Speed Crystal Resonator

- RC: External RC Oscillator

- EC: External Clock

Additionally, the Primary External Oscillator may be shut down under firmware control to save power.

#### 5.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 5-1.

### 5.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. The sequence in Example 5-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, EECON1, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared by hardware and the EEPROM Interrupt Flag bit, EEIF, is set. The user may either enable this interrupt or poll this bit. EEIF must be cleared by software.

### 5.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

EXAMPLE 5-1: DATA EEPROM READ

|   | MOVLW | data ee adi | DR  | i                             |

|---|-------|-------------|-----|-------------------------------|

|   | MOVWF |             |     | ; Data Memory Address to read |

|   | BCF   | EECON1, EEP | PGD | ; Point to DATA memory        |

|   | BCF   | EECON1, CFG | GS  | ; Access EEPROM               |

|   | BSF   | EECON1, RD  |     | ; EEPROM Read                 |

| ĺ | MOVF  | EEDATA, W   |     | ; W = EEDATA                  |

|   |       |             |     |                               |

#### EXAMPLE 5-2: DATA EEPROM WRITE

|          | MOVLW | DATA_EE_ADDR_LOW | ;                                             |

|----------|-------|------------------|-----------------------------------------------|

|          | MOVWF | EEADR            | ; Data Memory Address to write                |

|          | MOVLW | DATA_EE_DATA     | i                                             |

|          | MOVWF | EEDATA           | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EEPGD    | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS     | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN     | ; Enable writes                               |

|          | BCF   | INTCON, GIE      | ; Disable Interrupts                          |

|          | MOVLW | 55h              | ;                                             |

| Required | MOVWF | EECON2           | ; Write 55h                                   |

| Sequence | MOVLW | 0AAh             | ;                                             |

|          | MOVWF | EECON2           | ; Write OAAh                                  |

|          | BSF   | EECON1, WR       | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE      | ; Enable Interrupts                           |

|          |       |                  |                                               |

|          |       |                  | ; User code execution                         |

|          | BCF   | EECON1, WREN     | ; Disable writes on write complete (EEIF set) |

|          |       |                  |                                               |

|          |       |                  |                                               |

### 5.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to **Section 24.0 "Special Features of the CPU"** for additional information.

### 5.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

# 5.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. If this is the case, then an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### EXAMPLE 5-3: DATA EEPROM REFRESH ROUTINE

|      | CLRF   | EEADR         | ; Start at address 0         |

|------|--------|---------------|------------------------------|

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| Loop |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

|      |        |               |                              |

| Name   | Bit 7                                               | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-----------------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                                            | PEIE/GIEL | TMR0IE | INT0IE | RABIE  | TMR0IF | INT0IF | RABIF  | 275                        |

| EEADR  | EEADR7                                              | EEADR6    | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 | 277                        |

| EEDATA | EEPROM Data Register                                |           |        |        |        |        |        |        | 277                        |

| EECON2 | EEPROM Control Register 2 (not a physical register) |           |        |        |        |        | 277    |        |                            |

| EECON1 | EEPGD                                               | CFGS      | —      | FREE   | WRERR  | WREN   | WR     | RD     | 277                        |

| IPR2   | OSCFIP                                              | C1IP      | C2IP   | EEIP   | BCLIP  | USBIP  | TMR3IP | —      | 278                        |

| PIR2   | OSCFIF                                              | C1IF      | C2IF   | EEIF   | BCLIF  | USBIF  | TMR3IF | —      | 278                        |

| PIE2   | OSCFIE                                              | C1IE      | C2IE   | EEIE   | BCLIE  | USBIE  | TMR3IE | —      | 278                        |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

<sup>© 2008-2015</sup> Microchip Technology Inc.

# 7.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 7-6: PIE1: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                 |

|-------|------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                   |

|       | 1 = Enables the A/D interrupt                              |

|       | 0 = Disables the A/D interrupt                             |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit                  |

|       | 1 = Enables the EUSART receive interrupt                   |

|       | 0 = Disables the EUSART receive interrupt                  |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit                 |

|       | 1 = Enables the EUSART transmit interrupt                  |

|       | 0 = Disables the EUSART transmit interrupt                 |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit |

|       | 1 = Enables the MSSP interrupt                             |

|       | 0 = Disables the MSSP interrupt                            |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                          |

|       | 1 = Enables the CCP1 interrupt                             |

|       | 0 = Disables the CCP1 interrupt                            |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit             |

|       | 1 = Enables the TMR2 to PR2 match interrupt                |

|       | 0 = Disables the TMR2 to PR2 match interrupt               |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                 |

|       | 1 = Enables the TMR1 overflow interrupt                    |

|       | 0 = Disables the TMR1 overflow interrupt                   |

|       |                                                            |

#### **REGISTER 9-8: WPUB: WEAK PULL-UP PORTB REGISTER**

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | WPUB<7:4>: Weak Pull-up Enable bit |

|---------|------------------------------------|

|         | 1 = Pull-up enabled                |

|         | 0 = Pull-up disabled               |

| bit 3-0 | Unimplemented: Read as '0'         |

#### REGISTER 9-9: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-4 IOCB<7:4>: Interrupt-on-change bits 1 = Interrupt-on-change enabled 0 = Interrupt-on-change disabled bit 3-0 Unimplemented: Read as '0'

# REGISTER 9-10: LATB: PORTB DATA LATCH REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| LATB7 | LATB6 | LATB5 | LATB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-4 LATB<7:4>: RB<7:4> Port I/O Output Latch Register bits

bit 3-0 Unimplemented: Read as '0'

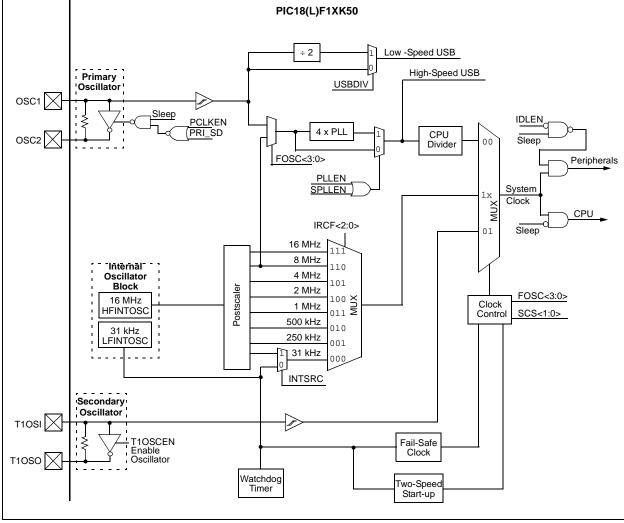

#### 14.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 14-13: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

#### 15.3.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF bit of the SSPSTAT register is set, or bit SSPOV bit of the SSPCON1 register is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF of the PIR1 register, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting the CKP bit of the SSPCON1 register. See **Section 15.3.4** "**Clock Stretching**" for more detail.

#### 15.3.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin SCK/SCL is held low regardless of SEN (see Section 15.3.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin SCK/SCL should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 15-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin SCK/SCL must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### 16.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (HFINTOSC). However, the HFINTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind. The first (preferred) method uses the OSCTUNE register to adjust the HFINTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 2.6.1** "**OSCTUNE Register**" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 16.3.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

# REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0            | R/W-0                                                                                              | R/W-0                                      | R/W-0         | R/W-0             | R/W-0              | R-1               | R/W-0 |

|------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------|---------------|-------------------|--------------------|-------------------|-------|

| CSRC             | TX9                                                                                                | TXEN <sup>(1)</sup>                        | SYNC          | SENDB             | BRGH               | TRMT              | TX9D  |

| bit 7            |                                                                                                    | 11                                         |               |                   |                    | 11                | bit 0 |

|                  |                                                                                                    |                                            |               |                   |                    |                   |       |

| Legend:          |                                                                                                    |                                            |               |                   |                    |                   |       |

| R = Readable b   | bit                                                                                                | W = Writable bit                           |               | U = Unimplem      | ented bit, read as | '0'               |       |

| -n = Value at PO | OR                                                                                                 | '1' = Bit is set                           |               | '0' = Bit is clea | red                | x = Bit is unknow | wn    |

| bit 7            | Asynchronous<br>Don't care<br>Synchronous m<br>1 = Master m                                        |                                            |               | from BRG)         |                    |                   |       |

| bit 6            | <b>TX9:</b> 9-bit Tran<br>1 = Selects 9                                                            |                                            | ,             |                   |                    |                   |       |

| bit 5            | <b>TXEN:</b> Transmit<br>1 = Transmit e<br>0 = Transmit o                                          | enabled                                    |               |                   |                    |                   |       |

| bit 4            | SYNC: EUSAR<br>1 = Synchrono<br>0 = Asynchron                                                      |                                            | t             |                   |                    |                   |       |

| bit 3            | Asynchronous                                                                                       | c Break on next tr<br>ak transmission co   | ansmission (c | leared by hardwa  | are upon completi  | on)               |       |

| bit 2            | BRGH: High Ba<br>Asynchronous<br>1 = High spee<br>0 = Low speed<br>Synchronous m<br>Unused in this | d<br>d<br>node:                            | it            |                   |                    |                   |       |

| bit 1            |                                                                                                    | it Shift Register St                       | atus bit      |                   |                    |                   |       |

| bit 0            | TX9D: Ninth bit                                                                                    | t of Transmit Data<br>s/data bit or a pari |               |                   |                    |                   |       |

Note 1: SREN/CREN overrides TXEN in Sync mode.

#### FIGURE 16-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| VOLE DE                                 | 30       | il ast by t |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 3 N.S.N.S.N.<br>                             | <u> </u>                                                                        | <u>Nanva</u> | ninnu                           | antarur.                     |                         | unununun<br>Asto Disersi    | d No. |

|-----------------------------------------|----------|-------------|---------------------------------|-----------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|--------------|---------------------------------|------------------------------|-------------------------|-----------------------------|-------|

|                                         |          |             |                                 | -4.<br>                                 | <br>:<br>' <i>1111111111111</i><br>'         | 1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1 | ;<br>;<br>;; |                                 |                              | , y.,<br>y., y.,<br>g., |                             |       |

| - Maaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa | <br><br> |             | i<br>Milianiania<br>Verseise es |                                         | <br>r<br><b>Hillinini</b><br>Biltini Barbart |                                                                                 |              | - Olyaceri da<br>Millillillilli | s to Şisar Raor<br>Millimini | s et 3000<br>Millinnin  | 9052<br><i>иниципици</i> ни | HIR.  |

© 2008-2015 Microchip Technology Inc.

| R-0           | R-0                                                                                                     | R/W-0                                                                                                                | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|--|--|--|--|--|

| MC1OUT        | MC2OUT                                                                                                  | C1RSEL                                                                                                               | C2RSEL        | C1HYS            | C2HYS           | C1SYNC          | C2SYNC |  |  |  |  |  |

| bit 7         |                                                                                                         |                                                                                                                      |               |                  |                 |                 | bit C  |  |  |  |  |  |

| Legend:       |                                                                                                         |                                                                                                                      |               |                  |                 |                 |        |  |  |  |  |  |

| R = Readable  | a hit                                                                                                   | W = Writable                                                                                                         | hit           | II – Unimpler    | nented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value at |                                                                                                         | '1' = Bit is set                                                                                                     |               | '0' = Bit is cle |                 | x = Bit is unkr |        |  |  |  |  |  |

|               | FOR                                                                                                     |                                                                                                                      |               |                  |                 |                 | IOWIT  |  |  |  |  |  |

| bit 7         | MC1OUT: Mi                                                                                              | rror Copy of C                                                                                                       | OUT bit       |                  |                 |                 |        |  |  |  |  |  |

| bit 6         | MC2OUT: Mi                                                                                              | rror Copy of C2                                                                                                      | 2OUT bit      |                  |                 |                 |        |  |  |  |  |  |

| bit 5         | C1RSEL: Co                                                                                              | mparator C1 R                                                                                                        | eference Sele | ct bit           |                 |                 |        |  |  |  |  |  |

|               | 1 = FVR rout                                                                                            | ed to C1VREF i                                                                                                       | nput          |                  |                 |                 |        |  |  |  |  |  |

|               | 0 = CVREF ro                                                                                            | uted to C1VRE                                                                                                        | = input       |                  |                 |                 |        |  |  |  |  |  |

| bit 4         | C2RSEL: Co                                                                                              | C2RSEL: Comparator C2 Reference Select bit                                                                           |               |                  |                 |                 |        |  |  |  |  |  |

|               | 1 = FVR rout                                                                                            | 1 = FVR routed to C2VREF input                                                                                       |               |                  |                 |                 |        |  |  |  |  |  |

|               | 0 = CVREF ro                                                                                            | uted to C2VRE                                                                                                        | = input       |                  |                 |                 |        |  |  |  |  |  |

| bit 3         | C1HYS: Comparator C1 Hysteresis Enable bit                                                              |                                                                                                                      |               |                  |                 |                 |        |  |  |  |  |  |

|               |                                                                                                         | rator C1 hyster<br>ator C1 hyster                                                                                    |               |                  |                 |                 |        |  |  |  |  |  |

| bit 2         | C2HYS: Corr                                                                                             | C2HYS: Comparator C2 Hysteresis Enable bit                                                                           |               |                  |                 |                 |        |  |  |  |  |  |

|               | <ul> <li>1 = Comparator C2 hysteresis enabled</li> <li>0 = Comparator C2 hysteresis disabled</li> </ul> |                                                                                                                      |               |                  |                 |                 |        |  |  |  |  |  |

| bit 1         | •                                                                                                       | Output Synch                                                                                                         |               | sit              |                 |                 |        |  |  |  |  |  |

|               |                                                                                                         |                                                                                                                      |               |                  | ock             |                 |        |  |  |  |  |  |

|               |                                                                                                         | <ul> <li>1 = C1 output is synchronous to rising edge to TMR1 clock</li> <li>0 = C1 output is asynchronous</li> </ul> |               |                  |                 |                 |        |  |  |  |  |  |

| bit 0         | •                                                                                                       | 2 Output Synch                                                                                                       |               | oit              |                 |                 |        |  |  |  |  |  |

|               |                                                                                                         | out is synchrono                                                                                                     |               |                  | ock             |                 |        |  |  |  |  |  |

|               |                                                                                                         | out is asynchror                                                                                                     |               | -                |                 |                 |        |  |  |  |  |  |

## REGISTER 18-3: CM2CON1: COMPARATOR 2 CONTROL REGISTER 1

| U-0          | U-0                      | U-0                | R/P-1           | R/P-1           | R/P-1            | R/P-1    | R/P-1 |

|--------------|--------------------------|--------------------|-----------------|-----------------|------------------|----------|-------|

| _            | —                        | _                  | WDTPS3          | WDTPS2          | WDTPS1           | WDTPS0   | WDTEN |

| bit 7        | ÷                        |                    |                 |                 |                  |          | bit ( |

|              |                          |                    |                 |                 |                  |          |       |

| Legend:      |                          |                    |                 |                 |                  |          |       |

| R = Readab   | ble bit                  | P = Program        | mable bit       | U = Unimpler    | nented bit, read | d as '0' |       |

| -n = Value v | when device is un        | orogrammed         |                 | x = Bit is unki | nown             |          |       |

|              |                          |                    |                 |                 |                  |          |       |

| bit 7-5      | Unimplemen               | ted: Read as       | '0'             |                 |                  |          |       |

| bit 4-1      | WDTPS<3:0>               | : Watchdog T       | imer Postscale  | Select bits     |                  |          |       |

|              | 1111 <b>= 1:32</b> ,7    |                    |                 |                 |                  |          |       |

|              | 1110 <b>= 1:16</b> ,3    |                    |                 |                 |                  |          |       |

|              | 1101 = 1:8,19            |                    |                 |                 |                  |          |       |

|              | 1100 = 1:4,09            |                    |                 |                 |                  |          |       |

|              | 1011 = 1:2,04            |                    |                 |                 |                  |          |       |

|              | 1010 = 1:1,02            |                    |                 |                 |                  |          |       |

|              | 1001 = 1:512             |                    |                 |                 |                  |          |       |

|              | 1000 = 1:256             |                    |                 |                 |                  |          |       |

|              | 0111 = 1:128             |                    |                 |                 |                  |          |       |

|              | 0110 = 1:64              |                    |                 |                 |                  |          |       |

|              | 0101 = 1:32              |                    |                 |                 |                  |          |       |

|              | 0100 = 1:16              |                    |                 |                 |                  |          |       |

|              | 0011 = 1:8               |                    |                 |                 |                  |          |       |

|              | 0010 = 1:4<br>0001 = 1:2 |                    |                 |                 |                  |          |       |

|              | 0001 = 1.2<br>0000 = 1.1 |                    |                 |                 |                  |          |       |

|              |                          | · · <del>·</del> · |                 |                 |                  |          |       |

| bit 0        | WDTEN: Wat               | •                  |                 | h               |                  |          |       |

|              |                          |                    | I. SWDTEN bit   |                 | agiatar          |          |       |

|              | 0 = VVDT IS CO           | phirollea by S     | VVDIEN DIT OF T | he WDTCON r     | egister          |          |       |

# REGISTER 24-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH

#### TABLE 25-2: PIC18FXXXX INSTRUCTION SET

| Mnemo     | nic.                            |                                          |            | 16-  | -Bit Instr | uction W | ord  | Status          |            |

|-----------|---------------------------------|------------------------------------------|------------|------|------------|----------|------|-----------------|------------|

| Opera     | ,                               | Description                              | Cycles     | MSb  |            |          | LSb  | Affected        | Notes      |

| BYTE-ORIE | ENTED C                         | PERATIONS                                |            |      |            |          |      |                 |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da0      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and CARRY bit to f              | 1          | 0010 | 0da        | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da       | ffff     | ffff | Z, N            | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a       | ffff     | ffff | Z               | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da       | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a       | ffff     | ffff | None            | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a       | ffff     | ffff | None            | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a       | ffff     | ffff | None            | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1 .        | 0000 | 01da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da       | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da       | ffff     | ffff | None            | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da       | ffff     | ffff | None            | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da       | ffff     | ffff | None            | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1 .        | 0001 | 00da       | ffff     | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da       | ffff     | ffff | Z, N            | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff       | ffff     | ffff | None            |            |

|           |                                 | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff       | ffff     | ffff |                 |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a       | ffff     | ffff | None            |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a       | ffff     | ffff | None            | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a       | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da       | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da       | ffff     | ffff | Z, N            |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da       | ffff     | ffff | C, Z, N         |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da       | ffff     | ffff | Z, N            |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110 | 100a       | ffff     | ffff | None            | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>borrow      | 1          | 0101 | 01da       | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da       | ffff     | ffff | C, DC, Z, OV, N |            |

|           |                                 | borrow                                   |            |      |            |          |      |                 |            |

| SWAPF     | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da       | ffff     | ffff | None            | 4          |

| TSTFSZ    | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 011a       | ffff     | ffff | None            | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1 ΄        | 0001 | 10da       | ffff     | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTE, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| IOR                         | IORLW Inclusive OR literal with W |                     |                                                                                       |   |    | N         |  |

|-----------------------------|-----------------------------------|---------------------|---------------------------------------------------------------------------------------|---|----|-----------|--|

| Synta                       | ax:                               | IORLW k             |                                                                                       |   |    |           |  |

| Oper                        | ands:                             | $0 \le k \le 255$   | 5                                                                                     |   |    |           |  |

| Oper                        | ation:                            | (W) .OR. k          | $\rightarrow W$                                                                       |   |    |           |  |

| Statu                       | s Affected:                       | N, Z                |                                                                                       |   |    |           |  |

| Encoding: 0000 1001 kkkk kk |                                   |                     | kkkk                                                                                  |   |    |           |  |

| Desc                        | ription:                          |                     | The contents of W are ORed with the eight-bit literal 'k'. The result is placed in W. |   |    |           |  |

| Word                        | ls:                               | 1                   | 1                                                                                     |   |    |           |  |

| Cycle                       | es:                               | 1                   | 1                                                                                     |   |    |           |  |

| QC                          | ycle Activity:                    |                     |                                                                                       |   |    |           |  |

|                             | Q1                                | Q2                  | Q3                                                                                    | 3 |    | Q4        |  |

|                             | Decode                            | Read<br>literal 'k' | Proce<br>Dat                                                                          |   | Wı | rite to W |  |

| <u>Exan</u>                 | nple:                             | IORLW               | 35h                                                                                   |   |    |           |  |

|                             | Before Instruction                |                     |                                                                                       |   |    |           |  |

| Operands:         | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|

| Operation:        | (W) .OR. (f                                                                                                                                                                                                                          | $) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                      |

| Status Affected:  | N, Z                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

| Encoding:         | 0001                                                                                                                                                                                                                                 | 00da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ffff | ffff                 |

| Description:      | <ul> <li>'0', the result is<br/>(default).</li> <li>If 'a' is '0', t</li> <li>If 'a' is '1', t</li> <li>GPR bank</li> <li>If 'a' is '0' a</li> <li>set is enab</li> <li>in Indexed</li> <li>mode wher</li> <li>Section 25</li> </ul> | Inclusive OR W with register 'f'. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is placed back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |      |                      |

| Words:            | 1                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

| Cycles:           | 1                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

| Q Cycle Activity: |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

| Q1                | Q2                                                                                                                                                                                                                                   | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3    | Q4                   |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                 | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | Write to destination |

|                   |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                      |

Inclusive OR W with f

IORWF f {,d {,a}}

W = 9Ah

After Instruction

W = BFh

Example:

IORWF Syntax:

IORWF RESULT, 0, 1

| Before Instruct   | ion |     |

|-------------------|-----|-----|

| RESULT            | =   | 13h |

| W                 | =   | 91h |

| After Instruction | n   |     |

| RESULT            | =   | 13h |

| W                 | =   | 93h |

DS40001350F-page 320

| RETFIE Return from Interrupt                |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ax:                                         | RETFIE {                                                                                                                                                                                | RETFIE {s}                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |