Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Betuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART, USB                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 14                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf14k50-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                           | 7   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Module)                                                        | 13  |

| 3.0   | Memory Organization                                                       | 27  |

| 4.0   | Flash Program Memory                                                      | 49  |

| 5.0   | Data EEPROM Memory                                                        | 58  |

| 6.0   | 8 x 8 Hardware Multiplier                                                 | 62  |

| 7.0   | Interrupts                                                                | 64  |

| 8.0   | Low Dropout (LDO) Voltage Regulator                                       |     |

| 9.0   | I/O Ports                                                                 |     |

| 10.0  | Timer0 Module                                                             |     |

| 11.0  | Timer1 Module                                                             | 99  |

| 12.0  | Timer2 Module                                                             | 104 |

| 13.0  | Timer3 Module                                                             | 107 |

| 14.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | 111 |

| 15.0  | Master Synchronous Serial Port (MSSP) Module                              | 133 |

| 16.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 175 |

| 17.0  | Analog-to-Digital Converter (ADC) Module                                  | 202 |

| 18.0  | Comparator Module                                                         | 215 |

| 19.0  | Power-Managed Modes                                                       | 227 |

| 20.0  | SR Latch                                                                  | 233 |

|       | Voltage References                                                        |     |

| 22.0  | Universal Serial Bus (USB)                                                | 241 |

|       | Reset                                                                     |     |

| 24.0  | Special Features of the CPU                                               | 280 |

| 25.0  | Instruction Set Summary                                                   | 297 |

| 26.0  | Development Support                                                       | 347 |

| 27.0  | Electrical Specifications                                                 | 351 |

| 28.0  | DC and AC Characteristics Graphs and Charts                               | 385 |

| 29.0  | Packaging Information                                                     | 398 |

| Appe  | ndix A: Revision History                                                  | 408 |

| Appe  | ndix B: Device Differences                                                | 409 |

| The I | Nicrochip Web Site                                                        | 410 |

| Custo | omer Change Notification Service                                          | 410 |

| Custo | omer Support                                                              | 410 |

| Prod  | uct Identification System                                                 | 411 |

|       |                                                                           |     |

| Features                              | PIC18F13K50                                               | PIC18LF13K50                                                                    | PIC18F14K50         | PIC18LF14K50 |  |  |  |

|---------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|--------------|--|--|--|

| LDO Regulator                         | Yes                                                       | No                                                                              | Yes                 | No           |  |  |  |

| Program Memory (Bytes)                | 8                                                         | K                                                                               | 10                  | 5K           |  |  |  |

| Program Memory (Instructions)         | 40                                                        | 96                                                                              | 81                  | 92           |  |  |  |

| Data Memory (Bytes)                   | 5                                                         | 12                                                                              | 7                   | 68           |  |  |  |

| Operating Frequency                   |                                                           | DC – 4                                                                          | 8 MHz               |              |  |  |  |

| Interrupt Sources                     | 30                                                        |                                                                                 |                     |              |  |  |  |

| I/O Ports                             | Ports A, B, C                                             |                                                                                 |                     |              |  |  |  |

| Timers                                | 4                                                         |                                                                                 |                     |              |  |  |  |

| Enhanced Capture/ Compare/PWM Modules | les 1                                                     |                                                                                 |                     |              |  |  |  |

| Serial Communications                 |                                                           | MSSP, Enhance                                                                   | ed USART, USB       |              |  |  |  |

| 10-Bit Analog-to-Digital Module       |                                                           | 9 Input C                                                                       | Channels            |              |  |  |  |

| Resets (and Delays)                   | POR, BOR, RESI                                            | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                     |              |  |  |  |

| Instruction Set                       | 75 Instructions, 83 with Extended Instruction Set Enabled |                                                                                 |                     |              |  |  |  |

| Packages                              | 20-Pin                                                    | PDIP, SSOP, SOIC                                                                | C (300 mil) and QFI | N (5x5)      |  |  |  |

TABLE 1-1: DEVICE FEATURES FOR THE PIC18(L)F1XK50 (20-PIN DEVICES)

# 2.6 Oscillator Control

The Oscillator Control (OSCCON) (Register 2-1) and the Oscillator Control 2 (OSCCON2) (Register 2-2) registers control the system clock and frequency selection options.

### REGISTER 2-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0        | R/W-0                                                                                                                                    | R/W-1                                                | R/W-1            | R-q                 | R-0                              | R/W-0           | R/W-0       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------|---------------------|----------------------------------|-----------------|-------------|

| IDLEN        | IRCF2                                                                                                                                    | IRCF1                                                | IRCF0            | OSTS <sup>(1)</sup> | HFIOFS                           | SCS1            | SCS0        |

| bit 7        |                                                                                                                                          | 1                                                    |                  |                     |                                  |                 | bit (       |

| Lonondi      |                                                                                                                                          |                                                      |                  |                     |                                  |                 |             |

| Legend:      |                                                                                                                                          | Muitable bit                                         |                  |                     |                                  | a denometo o    | n eenditien |

| R = Readab   |                                                                                                                                          | Writable bit                                         | •                | emented bit, re     |                                  | q = depends o   |             |

| -n = Value a | at POR 1'=                                                                                                                               | Bit is set                                           | '0' = Bit is c   | lieared             |                                  | x = Bit is unkn | own         |

| bit 7        |                                                                                                                                          | nters Idle mod                                       | e on SLEEP ins   |                     |                                  |                 |             |

| bit 6-4      | IRCF<2:0>: I<br>111 = 16 MHz<br>110 = 8 MHz<br>101 = 4 MHz<br>100 = 2 MHz<br>011 = 1 MHz<br>010 = 500 kH<br>001 = 250 kH<br>000 = 31 kHz | z<br>(3)<br>Iz<br>Iz                                 | tor Frequency \$ | Select bits         |                                  |                 |             |

| bit 3        | 1 = Device is                                                                                                                            | running from                                         |                  | ed by FOSC<2        | ::0> of the CON<br>OSC or LFINTC |                 |             |

| bit 2        | 1 = HFINTOS                                                                                                                              | NTOSC Frequ<br>SC frequency i<br>SC frequency i      |                  |                     |                                  |                 |             |

| bit 1-0      | <b>SCS&lt;1:0&gt;:</b> S<br>1x = Internal<br>01 = Seconda                                                                                | ystem Clock S<br>oscillator block<br>ary (Timer1) os | elect bits       | G1H[FOSC<3:         | 0>]).                            |                 |             |

| <b>2</b> : S | Reset state depen<br>Source selected b                                                                                                   | y the INTSRC                                         | bit of the OSC   | TUNE register,      | see text.                        |                 |             |

3: Default output frequency of HFINTOSC on Reset.

### 3.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 3-1) contains the Stack Pointer value, the STKFUL (stack full) bit and the STKUNF (Stack Underflow) bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 24.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an underflow has the effect of vectoring the |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | program to the Reset vector, where the                                              |  |  |  |  |  |  |

|       | stack conditions can be verified and                                                |  |  |  |  |  |  |

|       | appropriate actions can be taken. This is                                           |  |  |  |  |  |  |

|       | not the same as a Reset, as the contents                                            |  |  |  |  |  |  |

|       | of the SFRs are not affected.                                                       |  |  |  |  |  |  |

### 3.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

# REGISTER 3-1: STKPTR: STACK POINTER REGISTER

| R/C-0                                                                   | R/C-0                 | U-0              | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |

|-------------------------------------------------------------------------|-----------------------|------------------|-------|------------------|-------|-----------------|-------|--|--|

| STKFUL <sup>(1)</sup>                                                   | STKUNF <sup>(1)</sup> | —                | SP4   | SP3              | SP2   | SP1             | SP0   |  |  |

| bit 7                                                                   |                       |                  |       | ·                |       | ·               | bit 0 |  |  |

|                                                                         |                       |                  |       |                  |       |                 |       |  |  |

| Legend:                                                                 |                       |                  |       |                  |       |                 |       |  |  |

| R = Readable bitW = Writable bitU = UnimplementedC = Clearable only bit |                       |                  |       |                  |       |                 |       |  |  |

| -n = Value at POR '1' = Bit                                             |                       | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |  |  |

|                                                                         |                       |                  |       |                  |       |                 |       |  |  |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>                                                                |

|---------|-----------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Stack became full or overflowed</li><li>0 = Stack has not become full or overflowed</li></ul> |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                                           |

|         | <ul><li>1 = Stack underflow occurred</li><li>0 = Stack underflow did not occur</li></ul>                  |

| bit 5   | Unimplemented: Read as '0'                                                                                |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                                                      |

|         |                                                                                                           |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

- Note 1: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set. Furthermore, since a read or write on a port affects all bits of that port, care must be taken when using multiple pins in Interrupt-on-Change mode. Changes on one pin may not be seen while servicing changes on another pin.

- 2: When configured for USB operation, interrupt-on-change functionality on RA0 and RA1 is automatically disabled.

- **3:** In order for the digital inputs to function on the RA<1:0> port pins, the interrupton-change pins must be enabled (IOCA <1:0> = 11) and the USB module must be disabled (USBEN = 0).

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTA is only used for the interrupt-on-change feature. Polling of PORTA is not recommended while using the interrupt-on-change feature.

Each of the PORTA pins has an individually controlled weak internal pull-up. When set, each bit of the WPUA register enables the corresponding pin pull-up. When cleared, the RABPU bit of the INTCON2 register enables pull-ups on all pins which also have their corresponding WPUA bit set. When set, the RABPU bit disables all weak pull-ups. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, RA4 is configured  |

|-------|-----------------------------------------|

|       | as analog inputs by default and read as |

|       | '0'; RA<1:0> and RA<5:3> are configured |

|       | as digital inputs.                      |

RA0 and RA1 are multiplexed with the USB module and can serve as the differential data lines for the onchip USB transceiver.

RA0 and RA1 do not have TRISA bits associated with them. As digital port pins, they can only function as digital inputs. When configured for USB operation, the data direction is determined by the configuration and status of the USB module at a given time.

RA3 is an input only pin. Its operation is controlled by the MCLRE bit of the CONFIG3H register. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation.

| Note: | O                          | n a Pow | er-on F | Reset, | RA | 3 is enat | oled as |  |  |  |

|-------|----------------------------|---------|---------|--------|----|-----------|---------|--|--|--|

|       | а                          | digital | input   | only   | if | Master    | Clear   |  |  |  |

|       | functionality is disabled. |         |         |        |    |           |         |  |  |  |

Pins RA4 and RA5 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits"** for details). When they are not used as port pins, RA4 and RA5 and their associated TRIS and LAT bits read as '0'.

Pin RA4 is multiplexed with an analog input. The operation of pin RA4 as analog is selected by setting the ANS3 bit in the ANSEL register which is the default setting after a Power-on Reset.

| Note: | On a Power-on Reset, RA4 is configured |

|-------|----------------------------------------|

|       | as analog inputs and read as '0'.      |

# EXAMPLE 9-1: INITIALIZING PORTA

| CLRF  | PORTA | ; Initialize PORTA by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | 5 1                                        |

|       |       | ; data latches                             |

| CLRF  | LATA  | ; Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 030h  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISA | ; Set RA<5:4> as output                    |

|       |       |                                            |

# 11.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates the following features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable internal or external clock source and Timer1 oscillator options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 11-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 11-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 11-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON of the T1CON register.

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

# REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:<br>R = Readable I | oit           | W = Writable bit                                  | U = Unimplemented bit,                                       | read as '0'        |

|---------------------------|---------------|---------------------------------------------------|--------------------------------------------------------------|--------------------|

| -n = Value at P           | OR            | '1' = Bit is set                                  | '0' = Bit is cleared                                         | x = Bit is unknown |

|                           |               |                                                   |                                                              |                    |

| bit 7                     | RD16: 16      | -bit Read/Write Mode Enab                         | le bit                                                       |                    |

|                           |               |                                                   | mer1 in one 16-bit operation<br>ner1 in two 8-bit operations |                    |

| bit 6                     | T1RUN: T      | imer1 System Clock Status                         | bit                                                          |                    |

|                           |               | system clock is derived from                      |                                                              |                    |

|                           |               | system clock is derived from                      |                                                              |                    |

| bit 5-4                   |               | <1:0>: Timer1 Input Clock P                       | rescale Select bits                                          |                    |

|                           | -             | Prescale value<br>Prescale value                  |                                                              |                    |

|                           |               | Prescale value                                    |                                                              |                    |

|                           | • - • • • • • | Prescale value                                    |                                                              |                    |

| bit 3                     | T1OSCE        | N: Timer1 Oscillator Enable                       | bit                                                          |                    |

|                           |               | 1 oscillator is enabled                           |                                                              |                    |

|                           |               | 1 oscillator is shut off                          | enciptor and turned off to plinnin                           | ata navyan duain   |

| L:1 0                     |               |                                                   | resistor are turned off to elimin                            | late power drain.  |

| bit 2                     |               | R1CS = 1:                                         | It Synchronization Select bit                                |                    |

|                           |               | t synchronize external clock                      | k input                                                      |                    |

|                           |               | ronize external clock input                       |                                                              |                    |

|                           | When TM       | R1CS = 0:                                         |                                                              |                    |

|                           | This bit is   | ignored. Timer1 uses the ir                       | ternal clock when TMR1CS =                                   | 0.                 |

| bit 1                     | TMR1CS:       | Timer1 Clock Source Sele                          | ct bit                                                       |                    |

|                           |               | nal clock from the T13CKI p<br>nal clock (Fosc/4) | pin (on the rising edge)                                     |                    |

| bit 0                     | TMR10N        | : Timer1 On bit                                   |                                                              |                    |

|                           |               | les Timer1                                        |                                                              |                    |

|                           | 0 = Stops     | s Timer1                                          |                                                              |                    |

© 2008-2015 Microchip Technology Inc.

| Name    | Bit 7      | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------|----------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL      | TMR0IE  | INT0IE  | RABIE   | TMR0IF | INT0IF | RABIF  | 275                        |

| PIR1    | —          | ADIF           | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 278                        |

| PIE1    | _          | ADIE           | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 278                        |

| IPR1    | _          | ADIP           | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 278                        |

| TMR1L   | Timer1 Reg | jister, Low B  | yte     |         |         |        |        |        | 276                        |

| TMR1H   | Timer1 Reg | jister, High B | syte    |         |         |        |        |        | 276                        |

| T1CON   | RD16       | T1RUN          | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 276                        |

| TRISC   | TRISC7     | TRISC6         | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0 | 278                        |

| ANSELH  | —          | —              | —       | —       | ANS11   | ANS10  | ANS9   | ANS8   | 278                        |

| SSPCON1 | WCOL       | SSPOV          | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0  | 276                        |

# TABLE 11-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

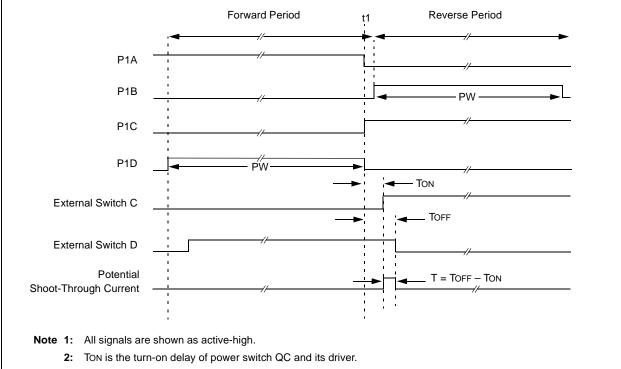

### FIGURE 14-11: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

3: TOFF is the turn-off delay of power switch QD and its driver.

# 14.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from  |

|-------|--------------------------------------------|

|       | Reset, all of the I/O pins are in the      |

|       | high-impedance state. The external cir-    |

|       | cuits must keep the power switch devices   |

|       | in the Off state until the microcontroller |

|       | drives the I/O pins with the proper signal |

|       | levels or activates the PWM output(s).     |

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

# 15.2.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- SSPCON1 Control Register

- SSPSTAT Status register

- SSPBUF Serial Receive/Transmit Buffer

- SSPSR Shift Register (Not directly accessible)

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

# REGISTER 15-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

|               |                                                   |                                                       |                | •                                        | •               |                |               |

|---------------|---------------------------------------------------|-------------------------------------------------------|----------------|------------------------------------------|-----------------|----------------|---------------|

| R/W-0         | R/W-0                                             | R-0                                                   | R-0            | R-0                                      | R-0             | R-0            | R-0           |

| SMP           | CKE                                               | D/A                                                   | Р              | S                                        | R/W             | UA             | BF            |

| bit 7         |                                                   |                                                       |                |                                          | ·               | ·              | bit           |

|               |                                                   |                                                       |                |                                          |                 |                |               |

| Legend:       |                                                   |                                                       |                |                                          |                 |                |               |

| R = Readabl   | e bit                                             | W = Writable                                          | bit            | U = Unimple                              | mented bit, rea | ad as '0'      |               |

| -n = Value at | POR                                               | '1' = Bit is set                                      | t              | '0' = Bit is cle                         | eared           | x = Bit is unk | nown          |

| bit 7         | 0 = Input dat                                     | <u>node:</u><br>ta sampled at e<br>ta sampled at m    |                |                                          |                 |                |               |

|               |                                                   | e cleared when                                        |                | n Slave mode.                            |                 |                |               |

| bit 6         |                                                   | ock Select bit <sup>(1</sup>                          |                |                                          |                 |                |               |

|               |                                                   |                                                       |                | tive to Idle clocl<br>le to active clocl |                 |                |               |

| bit 5         | <b>D/A:</b> Data/Ad<br>Used in I <sup>2</sup> C i |                                                       |                |                                          |                 |                |               |

| bit 4         | <b>P:</b> Stop bit<br>Used in I <sup>2</sup> C i  | mode only. This                                       | bit is cleared | d when the MSS                           | P module is d   | isabled, SSPEN | l is cleared. |

| bit 3         | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C i | mode only.                                            |                |                                          |                 |                |               |

| bit 2         | <b>R/₩</b> : Read/√<br>Used in I <sup>2</sup> C i | Write Informatio                                      | n bit          |                                          |                 |                |               |

| bit 1         | <b>UA:</b> Update<br>Used in I <sup>2</sup> C i   |                                                       |                |                                          |                 |                |               |

| bit 0         | <b>BF:</b> Buffer F<br>1 = Receive                | ull Status bit (R<br>complete, SSP<br>not complete, S | BUF is full    |                                          |                 |                |               |

| Note 1: Pe    |                                                   | not complete, S                                       | SSPBUF is er   |                                          | register.       |                |               |

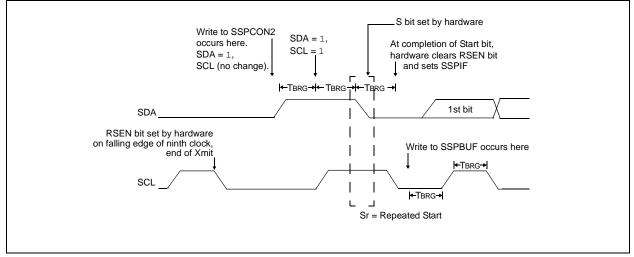

# 15.3.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPCON2 register is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

# 15.3.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

# FIGURE 15-20: REPEAT START CONDITION WAVEFORM

**Note:** Because queuing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated Start condition is complete.

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC        | <b>G16 =</b> 0 |                             |                    |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Foso           | ; = 48.00  | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 12.000 MHz |                |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                | _          | _                           |                   |            | _                           |                   | _              | _                           | _                  | _          |                             |

| 1200   |                | _          | _                           | 1200              | 0.00       | 239                         | 1202              | 0.16           | 155                         | 1200               | 0.00       | 143                         |

| 2400   | _              | _          | _                           | 2400              | 0.00       | 119                         | 2404              | 0.16           | 77                          | 2400               | 0.00       | 71                          |

| 9600   | 9615           | 0.16       | 77                          | 9600              | 0.00       | 29                          | 9375              | -2.34          | 19                          | 9600               | 0.00       | 17                          |

| 10417  | 10417          | 0.00       | 71                          | 10286             | -1.26      | 27                          | 10417             | 0.00           | 17                          | 10165              | -2.42      | 16                          |

| 19.2k  | 19.23k         | 0.16       | 38                          | 19.20k            | 0.00       | 14                          | 18.75k            | -2.34          | 9                           | 19.20k             | 0.00       | 8                           |

| 57.6k  | 57.69k         | 0.16       | 12                          | 57.60k            | 0.00       | 7                           | —                 | _              | _                           | 57.60k             | 0.00       | 2                           |

| 115.2k | —              | —          | —                           | _                 | _          | —                           | _                 | —              | —                           | —                  | —          | —                           |

### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |            |                             |                  | SYNC       | <b>C =</b> 0, <b>BRG</b>    | l = 0, BRG     | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686        | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | 300              | 0.16       | 207                         | 300            | 0.00           | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202           | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00           | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404           | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00           | 23                          | _                | _          | —                           |

| 9600   | 9615           | 0.16       | 12                          | _                | _          | _                           | 9600           | 0.00           | 5                           | _                | _          | —                           |

| 10417  | 10417          | 0.00       | 11                          | 10417            | 0.00       | 5                           | —              | _              | _                           | —                | _          | _                           |

| 19.2k  | _              | _          | _                           | —                | _          | _                           | 19.20k         | 0.00           | 2                           | —                | _          | _                           |

| 57.6k  | —              | _          | —                           | —                | —          | —                           | 57.60k         | 0.00           | 0                           | —                | _          | —                           |

| 115.2k | _              | _          | _                           |                  | _          | _                           |                | _              | _                           |                  | _          | —                           |

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRG        | <b>316 =</b> 0 |                             |                    |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc           | = 48.00    | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 12.000 MHz |                |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              |            | _                           |                   | _          | _                           | _                 | —              | —                           | —                  | —          | _                           |

| 1200   | —              | —          | —                           | —                 | —          | —                           | —                 | —              | —                           | —                  | —          | —                           |

| 2400   | —              | _          | _                           | _                 | _          | _                           | _                 | —              | _                           | —                  | —          | _                           |

| 9600   | —              | _          | _                           | 9600              | 0.00       | 119                         | 9615              | 0.16           | 77                          | 9600               | 0.00       | 71                          |

| 10417  | —              | _          | _                           | 10378             | -0.37      | 110                         | 10417             | 0.00           | 71                          | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16       | 155                         | 19.20k            | 0.00       | 59                          | 19.23k            | 0.16           | 38                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.69k         | 0.16       | 51                          | 57.60k            | 0.00       | 19                          | 57.69k            | 0.16           | 12                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 115.38k        | 0.16       | 25                          | 115.2k            | 0.00       | 9                           | _                 | _              | _                           | 115.2k             | 0.00       | 5                           |

| Name    | Bit 7                                          | Bit 6       | Bit 5       | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------------------------------------------|-------------|-------------|-------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                       | PEIE/GIEL   | TMR0IE      | INT0IE      | RABIE  | TMR0IF | INT0IF | RABIF  | 275                        |

| PIR1    | —                                              | ADIF        | RCIF        | TXIF        | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 278                        |

| PIE1    | —                                              | ADIE        | RCIE        | TXIE        | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 278                        |

| IPR1    | —                                              | ADIP        | RCIP        | TXIP        | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 278                        |

| RCSTA   | SPEN                                           | RX9         | SREN        | CREN        | ADDEN  | FERR   | OERR   | RX9D   | 277                        |

| TRISC   | TRISC7                                         | TRISC6      | TRISC5      | TRISC4      | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 278                        |

| TXREG   | EUSART T                                       | ransmit Reg | ister       |             |        |        |        |        | 277                        |

| TXSTA   | CSRC                                           | TX9         | TXEN        | SYNC        | SENDB  | BRGH   | TRMT   | TX9D   | 277                        |

| BAUDCON | ABDOVF                                         | RCIDL       | DTRXP       | CKTXP       | BRG16  | —      | WUE    | ABDEN  | 277                        |

| SPBRGH  | EUSART Baud Rate Generator Register, High Byte |             |             |             |        |        |        |        |                            |

| SPBRG   | EUSART B                                       | aud Rate G  | enerator Re | gister, Low | Byte   |        |        |        | 277                        |

TABLE 16-7:

REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

#### 16.4.1.6 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 16.4.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.4.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| R/W-0        | R/W-0         | R/W-0                                | R/W-0           | R/W-0            | R/W-0  | R/W-0           | R/W-0      |

|--------------|---------------|--------------------------------------|-----------------|------------------|--------|-----------------|------------|

| SRSPE        | SRSCKE        | SRSC2E                               | SRSC1E          | SRRPE            | SRRCKE | SRRC2E          | SRRC1E     |

| bit 7        |               | ·                                    |                 |                  | ·      | ·               | bit (      |

|              |               |                                      |                 |                  |        |                 |            |

| Legend:      |               |                                      |                 |                  |        |                 |            |

| R = Readab   | le bit        | W = Writable                         | bit             | U = Unimplei     | mented | C = Clearable   | e only bit |

| -n = Value a | t POR         | '1' = Bit is set                     |                 | '0' = Bit is cle | ared   | x = Bit is unki | nown       |

| L:1 7        |               | atab Daviahan                        |                 | . 14             |        |                 |            |

| bit 7        |               | Latch Periphera                      |                 | Dit              |        |                 |            |

|              |               | status sets SR<br>status has no e    |                 | itch             |        |                 |            |

| bit 6        | •             | R Latch Set Clo                      |                 |                  |        |                 |            |

|              |               | of SR latch is                       |                 |                  |        |                 |            |

|              | 0 = Set input | of SR latch is                       | not pulsed with | n SRCLK          |        |                 |            |

| bit 5        |               | Latch C2 Set                         |                 |                  |        |                 |            |

|              |               | parator output                       |                 |                  |        |                 |            |

| 1.11.4       |               | parator output l                     |                 | n SR Latch       |        |                 |            |

| bit 4        |               | Latch C1 Set                         |                 |                  |        |                 |            |

|              |               | parator output s<br>parator output l |                 | n SR Latch       |        |                 |            |

| bit 3        | •             | Latch Periphera                      |                 |                  |        |                 |            |

|              | 1 = INT1 pin  | resets SR Late                       | ch              |                  |        |                 |            |

|              | 0 = INT1 pin  | has no effect of                     | on SR Latch     |                  |        |                 |            |

| bit 2        | SRRCKE: SF    | R Latch Reset (                      | Clock Enable b  | bit              |        |                 |            |

|              |               | out of SR latch<br>out of SR latch   |                 |                  |        |                 |            |

| bit 1        | SRRC2E: SR    | Latch C2 Res                         | et Enable bit   |                  |        |                 |            |

|              |               | oarator output i<br>oarator output l |                 |                  |        |                 |            |

| bit 0        | SRRC1E: SR    | Latch C1 Res                         | et Enable bit   |                  |        |                 |            |

|              | 1 = C1 Comp   | parator output i                     | esets SR Latc   | h                |        |                 |            |

|              | 0 = C1 Comp   | orotor output l                      | and no offect o |                  |        |                 |            |

# REGISTER 20-2: SRCON1: SR LATCH CONTROL REGISTER 1

| TABLE 20-3: | <b>REGISTERS ASSOCIATED WITH THE SR LATCH</b> |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| SRCON0  | SRLEN  | SRCLK2 | SRCLK1 | SRCLK0 | SRQEN  | SRNQEN | SRPS   | SRPR   | 278                        |

| SRCON1  | SRSPE  | SRSCKE | SRSC2E | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 278                        |

| CM2CON1 | MC10UT | MC2OUT | C1RSEL | C2RSEL | C1HYS  | C2HYS  | C1SYNC | C2SYNC | 278                        |

| INTCON3 | INT2IP | INT1IP | —      | INT2IE | INT1IE | _      | INT2IF | INT1IF | 275                        |

| TRISC   | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 278                        |

**Legend:** Shaded cells are not used with the comparator voltage reference.

### 22.2.4 USB ENDPOINT CONTROL

Each of the eight possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits. The prototype is shown in Register 22-4.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions. Note that the corresponding EPINEN and EPOUTEN bits must be set to enable IN and OUT transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware, or until the SIE is reset.

| U-0   | U-0 | U-0 | R/W-0  | R/W-0    | R/W-0   | R/W-0  | R/W-0                  |

|-------|-----|-----|--------|----------|---------|--------|------------------------|

| —     | —   | —   | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL <sup>(1)</sup> |

| bit 7 |     |     |        |          |         |        | bit 0                  |

# REGISTER 22-4: UEPn: USB ENDPOINT n CONTROL REGISTER (UEP0 THROUGH UEP7)

| Legend:                 |                                                                                                                                        |                                                                                                                                                                              |                                    |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|

| R = Readable bit W = Wr |                                                                                                                                        | bit U = Unimplem                                                                                                                                                             | U = Unimplemented bit, read as '0' |  |  |  |  |  |

| -n = Value              | at POR '1' = Bit is set                                                                                                                | t '0' = Bit is clea                                                                                                                                                          | eared x = Bit is unknowr           |  |  |  |  |  |

| bit 7-5                 | <b>Unimplemented:</b> Read as                                                                                                          | ʻ0'                                                                                                                                                                          |                                    |  |  |  |  |  |

| bit 4                   | EPHSHK: Endpoint Handsh                                                                                                                |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         | <ul> <li>1 = Endpoint handshake enabled</li> <li>0 = Endpoint handshake disabled (typically used for isochronous endpoints)</li> </ul> |                                                                                                                                                                              |                                    |  |  |  |  |  |

| bit 3                   | EPCONDIS: Bidirectional Endpoint Control bit                                                                                           |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         |                                                                                                                                        | I = 1 and EPINEN = 1:<br>Endpoint n from control transfers; only IN and OUT transfers allowed<br>Endpoint n for control (SETUP) transfers; IN and OUT transfers also allowed |                                    |  |  |  |  |  |

| bit 2                   | EPOUTEN: Endpoint Output Enable bit                                                                                                    |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         | <ul><li>1 = Endpoint n output enabled</li><li>0 = Endpoint n output disabled</li></ul>                                                 |                                                                                                                                                                              |                                    |  |  |  |  |  |

| bit 1                   | EPINEN: Endpoint Input Enable bit                                                                                                      |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         | <ol> <li>1 = Endpoint n input enable</li> <li>0 = Endpoint n input disable</li> </ol>                                                  |                                                                                                                                                                              |                                    |  |  |  |  |  |

| bit 0                   | EPSTALL: Endpoint STALL Enable bit <sup>(1)</sup>                                                                                      |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         | 1 = Endpoint n is stalled                                                                                                              |                                                                                                                                                                              |                                    |  |  |  |  |  |

|                         | 0 = Endpoint n is not stalled                                                                                                          |                                                                                                                                                                              |                                    |  |  |  |  |  |

**Note 1:** Valid only if Endpoint n is enabled; otherwise, the bit is ignored.

# 22.7 Oscillator

The USB module has specific clock requirements. For full-speed operation, the clock source must be 48 MHz. Even so, the microcontroller core and other peripherals are not required to run at that clock speed. Available clocking options are described in detail in **Section 2.11** "**USB Operation**".

# 22.8 Interrupt-on-Change for D+/D-Pins

The PIC18(L)F1XK50 has interrupt-on-change functionality on both D+ and D- data pins. This feature allows the device to detect voltage level changes when first connected to a USB host/hub.

The USB host/hub has 15K pull-down resistors on the D+ and D- pins. When the PIC18(L)F1XK50 attaches to the bus the D+ and D- pins can detect voltage changes. External resistors are needed for each pin to maintain a high state on the pins when detached. The USB module must be disable (USBEN = 0) for the interrupt-on-change to function. Enabling the USB module (USBEN = 1) will automatically disable the interrupt-on-change for D+ and D- pins. Refer to Section 7.11 "PORTA and PORTB Interrupt-on-Change" for mode detail.

# 22.9 USB Firmware and Drivers

Microchip provides a number of application-specific resources, such as USB firmware and driver support. Refer to www.microchip.com for the latest firmware and driver support.

| Name   | Bit 7    | Bit 6     | Bit 5   | Bit 4  | Bit 3 Bit 2 |                | Bit 1         | Bit 0   | Details on<br>Page |

|--------|----------|-----------|---------|--------|-------------|----------------|---------------|---------|--------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE | RABIE       | TMR0IF         | <b>INT0IF</b> | RABIF   | 66                 |

| IPR2   | OSCFIP   | C1IP      | C2IP    | EEIP   | BCL1IP      | USBIP          | TMR3IP        | _       | 74                 |

| PIR2   | OSCFIF   | C1IF      | C2IF    | EEIF   | BCL1IF      | USBIF          | TMR3IF        | —       | 70                 |

| PIE2   | OSCFIE   | C1IE      | C2IE    | EEIE   | BCL1IE      | USBIE          | TMR3IE        | —       | 72                 |

| UCON   | —        | PPBRST    | SE0     | PKTDIS | USBEN       | RESUME SUSPND  |               | —       | 242                |

| UCFG   | UTEYE    | _         | _       | UPUEN  | _           | FSEN           | PPB1          | PPB0    | 244                |

| USTAT  | _        | ENDP3     | ENDP2   | ENDP1  | ENDP0       | DIR            | PPBI          | —       | 246                |

| UADDR  | —        | ADDR6     | ADDR5   | ADDR4  | ADDR3       | ADDR2          | ADDR1         | ADDR0   | 248                |

| UFRML  | FRM7     | FRM6      | FRM5    | FRM4   | FRM3        | FRM2           | FRM1          | FRM0    | 242                |

| UFRMH  | _        | —         | _       | _      | — FRM10 FRM |                | FRM9          | FRM8    | 242                |

| UIR    | —        | SOFIF     | STALLIF | IDLEIF | TRNIF       | ACTVIF         | UERRIF        | URSTIF  | 256                |

| UIE    | _        | SOFIE     | STALLIE | IDLEIE | TRNIE       | ACTVIE         | UERRIE        | URSTIE  | 258                |

| UEIR   | BTSEF    | _         | _       | BTOEF  | DFN8EF      | CRC16EF        | CRC5EF        | PIDEF   | 259                |

| UEIE   | BTSEE    | —         | _       | BTOEE  | DFN8EE      | CRC16EE        | CRC5EE        | PIDEE   | 260                |

| UEP0   | _        | _         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP1   | _        | _         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP2   | —        | _         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP3   | _        | _         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP4   | —        | —         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP5   | —        | —         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

| UEP6   | _        | _         | _       | EPHSHK | EPCONDIS    | EPOUTEN EPINEN |               | EPSTALL | 247                |

| UEP7   | —        | —         | _       | EPHSHK | EPCONDIS    | EPOUTEN        | EPINEN        | EPSTALL | 247                |

TABLE 22-4:

REGISTERS ASSOCIATED WITH USB MODULE OPERATION<sup>(1)</sup>

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the USB module.

**Note 1:** This table includes only those hardware mapped SFRs located in Bank 15 of the data memory space. The Buffer Descriptor registers, which are mapped into Bank 4 and are not true SFRs, are listed separately in Table 22-3.

#### 24.3.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

#### 24.3.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

# 24.4 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

# 24.5 In-Circuit Serial Programming