Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART, USB                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 14                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf14k50-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

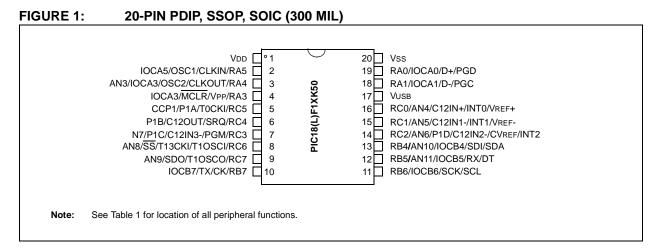

#### **Pin Diagrams**

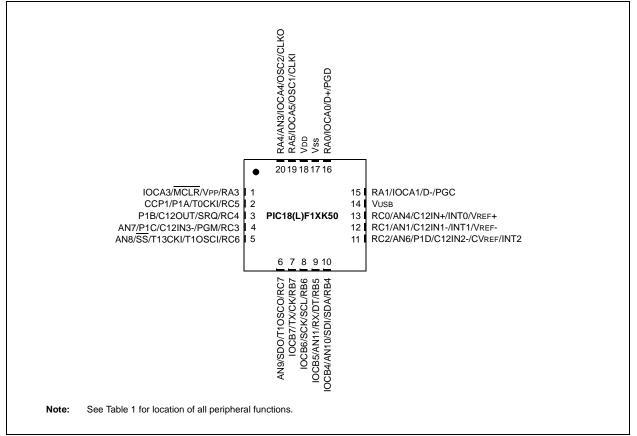

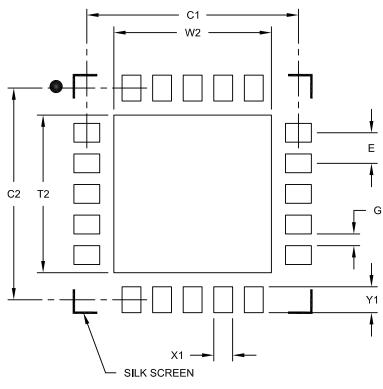

FIGURE 2: 20-PIN QFN (5X5)

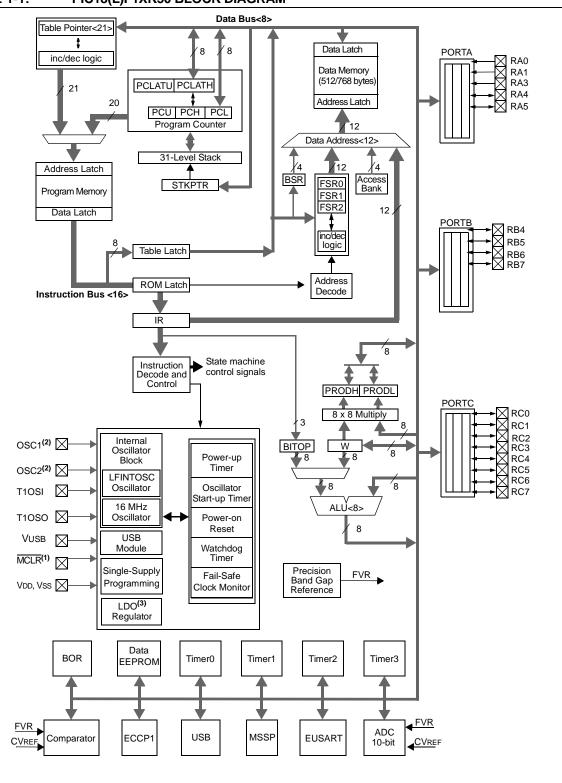

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F13K50 PIC18F14K50

- PIC18LF13K50 PIC18LF14K50

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Flash program memory. On top of these features, the PIC18(L)F1XK50 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F1XK50 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate powersaving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Specifications" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F1XK50 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which contains a 16 MHz HFINTOSC oscillator and a 31 kHz LFINTOSC oscillator which together provide 8 user selectable clock frequencies, from 31 kHz to 16 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the high-speed crystal and internal oscillator modes, which allows clock speeds of up to 48 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

| Features                              | PIC18F13K50                                               | PIC18LF13K50                   | PIC18F14K50                    | PIC18LF14K50    |  |  |

|---------------------------------------|-----------------------------------------------------------|--------------------------------|--------------------------------|-----------------|--|--|

| LDO Regulator                         | Yes                                                       | No                             | Yes                            | No              |  |  |

| Program Memory (Bytes)                | 8                                                         | K                              | 10                             | 5K              |  |  |

| Program Memory (Instructions)         | 40                                                        | 96                             | 81                             | 92              |  |  |

| Data Memory (Bytes)                   | 5                                                         | 12                             | 7                              | 68              |  |  |

| Operating Frequency                   |                                                           | DC – 4                         | 8 MHz                          |                 |  |  |

| Interrupt Sources                     |                                                           | 3                              | 0                              |                 |  |  |

| I/O Ports                             | Ports A, B, C                                             |                                |                                |                 |  |  |

| Timers                                | 4                                                         |                                |                                |                 |  |  |

| Enhanced Capture/ Compare/PWM Modules | 1                                                         |                                |                                |                 |  |  |

| Serial Communications                 |                                                           | MSSP, Enhance                  | ed USART, USB                  |                 |  |  |

| 10-Bit Analog-to-Digital Module       |                                                           | 9 Input C                      | Channels                       |                 |  |  |

| Resets (and Delays)                   | POR, BOR, RESI                                            | T Instruction, Stack<br>(PWR1) | < Full, Stack Under<br>T, OST) | flow, MCLR, WDT |  |  |

| Instruction Set                       | 75 Instructions, 83 with Extended Instruction Set Enabled |                                |                                | et Enabled      |  |  |

| Packages                              | 20-Pin                                                    | PDIP, SSOP, SOIC               | C (300 mil) and QFI            | N (5x5)         |  |  |

TABLE 1-1: DEVICE FEATURES FOR THE PIC18(L)F1XK50 (20-PIN DEVICES)

Note 1: RA3 is only available when MCLR functionality is disabled.

- 2: OSC1/CLKIN and OSC2/CLKOUT are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 2.0 "Oscillator Module" for additional information.

- 3: PIC18F13K50/PIC18F14K50 only.

| Switch From | Switch To            | Oscillator Delay                 |

|-------------|----------------------|----------------------------------|

| Sleep/POR   | LFINTOSC<br>HFINTOSC | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR   | LP, XT, HS           | 1024 clock cycles                |

| Sleep/POR   | EC, RC               | 8 clock cycles                   |

#### TABLE 2-2: EXAMPLES OF DELAYS DUE TO CLOCK SWITCHING

#### 2.9 4x Phase Lock Loop Frequency Multiplier

A Phase-Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency external oscillator or to operate at 32 MHz with the HFINTOSC. The PLL is designed for an input frequency from 4 MHz to 12 MHz. The PLL multiplies its input frequency by a factor of four when the PLL is enabled. This may be useful for customers who are concerned with EMI, due to high-frequency crystals.

Two bits control the PLL: the PLLEN bit of the CONFIG1H Configuration register and the SPLLEN bit of the OSCTUNE register. The PLL is enabled when the PLLEN bit is set and it is under software control when the PLLEN bit is cleared.

TABLE 2-3: PLL CONFIGURATION

| PLLEN | SPLLEN | PLL Status   |

|-------|--------|--------------|

| 1     | x      | PLL enabled  |

| 0     | 1      | PLL enabled  |

| 0     | 0      | PLL disabled |

#### 2.9.1 32 MHZ INTERNAL OSCILLATOR FREQUENCY SELECTION

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in CONFIG1H must be set to use the INTOSC source as the device system clock (FOSC<3:0> = 1000 or 1001).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<3:0> in CONFIG1H (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<2:0> = 110).

- The SPLLEN bit in the OSCTUNE register must be set to enable the 4xPLL, or the PLLEN bit of CONFIG1H must be programmed to a '1'.

| Note: | When using the PLLEN bit of CONFIG1H,    |

|-------|------------------------------------------|

|       | the 4xPLL cannot be disabled by software |

|       | and the 8 MHz HFINTOSC option will no    |

|       | longer be available.                     |

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

#### 2.10 CPU Clock Divider

The CPU Clock Divider allows the system clock to run at a slower speed than the Low/Full Speed USB module clock while sharing the same clock source. Only the oscillator defined by the settings of the FOSC bits of the CONFIG1H Configuration register may be used with the CPU Clock Divider. The CPU Clock Divider is controlled by the CPUDIV bits of the CONFIG1L Configuration register. Setting the CPUDIV bits will set the system clock to:

- Equal the clock speed of the USB module

- Half the clock speed of the USB module

- · One third the clock speed of the USB module

- · One fourth the clock speed of the USB module

For more information on the CPU Clock Divider, see Figure 2-1 and Register 24-1 CONFIG1L.

#### 3.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSb will always read '0' (see Section 3.1.1 "Program Counter").

Figure 3-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 3-4 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 25.0 "Instruction Set Summary" provides further details of the instruction set.

|                |                |                    |         |         | Word Address |

|----------------|----------------|--------------------|---------|---------|--------------|

|                |                |                    | LSB = 1 | LSB = 0 | $\downarrow$ |

|                | Program Memory |                    |         |         | 000000h      |

|                | Byte Locat     | ions $\rightarrow$ |         |         | 000002h      |

|                |                |                    |         |         | 000004h      |

|                |                |                    |         |         | 000006h      |

| Instruction 1: | MOVLW          | 055h               | 0Fh     | 55h     | 000008h      |

| Instruction 2: | GOTO           | 0006h              | EFh     | 03h     | 00000Ah      |

|                |                |                    | F0h     | 00h     | 00000Ch      |

| Instruction 3: | MOVFF          | 123h, 456h         | C1h     | 23h     | 00000Eh      |

|                |                |                    | F4h     | 56h     | 000010h      |

|                |                |                    |         |         | 000012h      |

|                |                |                    |         |         | 000014h      |

#### FIGURE 3-4: INSTRUCTIONS IN PROGRAM MEMORY

#### 3.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instruction always has '1111' as its four Most Significant bits (MSb); the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed

and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 3-4 shows how this works.

Note: See Section 3.6 "PIC18 Instruction Execution and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

| EXAMPLE 3-4: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

| 04054        |                       |

| CASE 1:             |                  |                              |

|---------------------|------------------|------------------------------|

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

| CASE 2:             |                  |                              |

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

| R/W-x        | R/W-x                              | U-0                                  | R/W-0          | R/W-x                                  | R/W-0           | R/S-0            | R/S-0          |

|--------------|------------------------------------|--------------------------------------|----------------|----------------------------------------|-----------------|------------------|----------------|

| EEPGD        | CFGS                               | —                                    | FREE           | WRERR                                  | WREN            | WR               | RD             |

| bit 7        |                                    |                                      |                |                                        |                 |                  | bit 0          |

|              |                                    |                                      |                |                                        |                 |                  |                |

| Legend:      |                                    |                                      |                |                                        |                 |                  |                |

| R = Readab   |                                    | W = Writable I                       |                |                                        |                 |                  |                |

|              | be set by software                 |                                      | ed             |                                        | nented bit, rea |                  |                |

| -n = Value a | t POR                              | '1' = Bit is set                     |                | '0' = Bit is cle                       | ared            | x = Bit is unki  | nown           |

| hit 7        | EEPCD: Elos                        | h Drogrom or F                       |                | Momony Solo                            | at hit          |                  |                |

| bit 7        |                                    | lash program r                       |                | / Memory Selec                         | JUDIL           |                  |                |

|              |                                    | lata EEPROM r                        |                |                                        |                 |                  |                |

| bit 6        |                                    |                                      | •              | Configuration S                        | elect bit       |                  |                |

|              | 1 = Access C                       | Configuration re                     | gisters        | C C                                    |                 |                  |                |

|              | 0 = Access F                       | lash program c                       | or data EEPR   | OM memory                              |                 |                  |                |

| bit 5        | Unimplemen                         | ted: Read as '                       | )'             |                                        |                 |                  |                |

| bit 4        |                                    | Row (Block) Er                       |                |                                        |                 |                  |                |

|              |                                    |                                      |                | dressed by TBL                         | PTR on the ne   | ext WR comman    | nd             |

|              | 0 = Perform                        | by completion of write-only          | or erase opera | allon)                                 |                 |                  |                |

| bit 3        |                                    | ,                                    | ta EEPROM I    | Error Flag bit <sup>(1)</sup>          |                 |                  |                |

|              |                                    |                                      |                | inated (any Res                        | et during self- | timed programr   | ning in normal |

|              | operation                          | n, or an imprope                     | er write attem | • •                                    | U               |                  | 0              |

|              | 0 = The write                      | e operation com                      | pleted         |                                        |                 |                  |                |

| bit 2        | WREN: Flash                        | n Program/Data                       | EEPROM W       | rite Enable bit                        |                 |                  |                |

|              |                                    |                                      |                | data EEPROM                            |                 |                  |                |

|              |                                    | •                                    | lash program   | /data EEPROM                           |                 |                  |                |

| bit 1        | WR: Write Co                       |                                      |                |                                        |                 |                  |                |

|              |                                    |                                      |                | cycle or a progra<br>bit is cleared by |                 |                  |                |

|              |                                    |                                      |                | ed) by software                        |                 |                  |                |

|              | 0 = Write cyc                      | le to the EEPR                       | OM is comple   | ete                                    |                 |                  |                |

| bit 0        | RD: Read Co                        | ntrol bit                            |                |                                        |                 |                  |                |

|              |                                    |                                      |                | s one cycle. RD                        |                 |                  |                |

|              | •                                  | ot cleared) by se<br>initiate an EEF |                | it cannot be set                       | when EEPGD      | = 1  or  CFGS =  | 1.)            |

|              |                                    |                                      |                |                                        |                 |                  |                |

|              | Vhen a WRERR of<br>rror condition. | occurs, the EEF                      | GD and CFG     | S bits are not o                       | leared. This a  | llows tracing of | the            |

| e            |                                    |                                      |                |                                        |                 |                  |                |

#### REGISTER 5-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

#### 14.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18(L)F1XK50 devices have one ECCP (Capture/Compare/PWM) module. The module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. CCP1 is implemented as a standard CCP module with enhanced PWM capabilities. These include:

- Provision for 2 or 4 output channels

- Output steering

- Programmable polarity

- Programmable dead-band control

- Automatic shutdown and restart.

The enhanced features are discussed in detail in Section 14.4 "PWM (Enhanced Mode)".

#### REGISTER 14-1: CCP1CON: ENHANCED CAPTURE/COMPARE/PWM CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | P1M<1:0>: Enhanced PWM Output Configuration bits                                                                                                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $\frac{ f CCP1M<3:2> = 00, 01, 10:}{10}$                                                                                                                                                                                                                                                             |

|         | xx = P1A assigned as Capture/Compare input/output; P1B, P1C, P1D assigned as port pins                                                                                                                                                                                                               |

|         | <u>If CCP1M&lt;3:2&gt; = 11:</u>                                                                                                                                                                                                                                                                     |

|         | 00 = Single output: P1A, P1B, P1C and P1D controlled by steering (See Section 14.4.7 "Pulse Steering<br>Mode").                                                                                                                                                                                      |

|         | <ul> <li>01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive</li> <li>10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins</li> <li>11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive</li> </ul> |

| bit 5-4 | DC1B<1:0>: PWM Duty Cycle bit 1 and bit 0                                                                                                                                                                                                                                                            |

|         | Capture mode:                                                                                                                                                                                                                                                                                        |

|         | Unused.                                                                                                                                                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                                                                                                                                                        |

|         | Unused.                                                                                                                                                                                                                                                                                              |

|         | PWM mode:                                                                                                                                                                                                                                                                                            |

|         | These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in                                                                                                                                                                                              |

|         | CCPR1L.                                                                                                                                                                                                                                                                                              |

| bit 3-0 | CCP1M<3:0>: Enhanced CCP Mode Select bits                                                                                                                                                                                                                                                            |

|         | 0000 = Capture/Compare/PWM off (resets ECCP module)                                                                                                                                                                                                                                                  |

|         | 0001 = Reserved                                                                                                                                                                                                                                                                                      |

|         | 0010 = Compare mode, toggle output on match                                                                                                                                                                                                                                                          |

|         | 0011 = Reserved                                                                                                                                                                                                                                                                                      |

|         | 0100 = Capture mode, every falling edge                                                                                                                                                                                                                                                              |

|         | 0101 = Capture mode, every rising edge                                                                                                                                                                                                                                                               |

|         | 0110 = Capture mode, every 4th rising edge<br>0111 = Capture mode, every 16th rising edge                                                                                                                                                                                                            |

|         | 1000 = Compare mode, initialize CCP1 pin low, set output on compare match (set CCP1IF)                                                                                                                                                                                                               |

|         | 1001 = Compare mode, initialize CCP1 pin high, clear output on compare match (set CCP1IF)                                                                                                                                                                                                            |

|         | 1010 = Compare mode, generate software interrupt only, CCP1 pin reverts to I/O state                                                                                                                                                                                                                 |

|         | 1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, start A/D conversion, sets                                                                                                                                                                                                     |

|         | CC1IF bit)                                                                                                                                                                                                                                                                                           |

|         | 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high                                                                                                                                                                                                                                          |

|         | 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low                                                                                                                                                                                                                                           |

|         | 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high                                                                                                                                                                                                                                           |

|         | 1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low                                                                                                                                                                                                                                            |

|         |                                                                                                                                                                                                                                                                                                      |

#### 16.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

#### 16.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user needs to poll this bit to determine the TSR status.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

#### 16.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 16.1.2.8** "Address **Detection**" for more information on the Address mode.

16.1.1.7 Asynchronous Transmission Set-up:

- 1. Initialize the SPBRGH:SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set the CKTXP control bit if inverted transmit data polarity is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

#### 16.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 16-9 for the timing of the Break character sequence.

#### 16.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit interrupt Flag) TRMT bit (Transmit Shift Reg. Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

#### 16.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 16.3.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### FIGURE 16-9: SEND BREAK CHARACTER SEQUENCE

#### 21.0 VOLTAGE REFERENCES

There are two independent voltage references available:

- Programmable Voltage Reference

- 1.024V Fixed Voltage Reference

#### 21.1 Voltage Reference

The voltage reference module provides an internally generated voltage reference for the comparators and the DAC module. The following features are available:

- Independent from Comparator operation

- Single 32-level voltage ranges

- · Output clamped to Vss

- Ratiometric with VDD

- 1.024V Fixed Reference Voltage (FVR)

The REFCON1 register (Register 21-2) controls the voltage reference module shown in Figure 21-1.

#### EQUATION 21-1: VREF OUTPUT VOLTAGE

# $\frac{IFDIEN = 1}{VOUT} = \left( (VSOURCE + -VSOURCE -) \times \frac{DACIR[4:0]}{2^5} + VSOURCE \right)$

<u>IF D1EN = 0 & D1LPS = 1 & DAC1R[4:0] = 11111:</u>

VOUT = VSOURCE+

<u>IF D1EN = 0 & D1LPS = 1 & DAC1R[4:0] = 00000:</u>

VOUT = VSOURCE

#### 21.1.3 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 27.0 "Electrical Specifications"**.

#### 21.1.4 VOLTAGE REFERENCE OUTPUT

The VREF voltage reference can be output to the device CVREF pin by setting the DAC1OE bit of the REFCON1 register to '1'. Selecting the reference voltage for output on the VREF pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the CVREF pin when it has been configured for reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to CVREF. Figure 21-2 shows an example buffering technique.

#### 21.1.1 INDEPENDENT OPERATION

The voltage reference is independent of the comparator configuration. Setting the D1EN bit of the REFCON1 register will enable the voltage reference by allowing current to flow in the VREF voltage divider. When the D1EN bit is cleared, current flow in the VREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

#### 21.1.2 OUTPUT VOLTAGE SELECTION

The VREF voltage reference has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the REFCON2 register.

The VREF output voltage is determined by the following equations:

#### 21.1.5 OPERATION DURING SLEEP

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the RECON1 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 21.1.6 EFFECTS OF A RESET

A device Reset affects the following:

- · Voltage reference is disabled

- Fixed Voltage Reference is disabled

- VREF is removed from the CVREF pin

- The DAC1R<4:0> range select bits are cleared

#### 22.4.1.3 BDnSTAT Register (SIE Mode)

When the BD and its buffer are owned by the SIE, most of the bits in BDnSTAT take on a different meaning. The configuration is shown in Register 22-6. Once the UOWN bit is set, any data or control settings previously written there by the user will be overwritten with data from the SIE.

The BDnSTAT register is updated by the SIE with the token Packet Identifier (PID) which is stored in BDnSTAT<5:3>. The transfer count in the corresponding BDnCNT register is updated. Values that overflow the 8-bit register carry over to the two Most Significant digits of the count, stored in BDnSTAT<1:0>.

#### 22.4.2 BD BYTE COUNT

The byte count represents the total number of bytes that will be transmitted during an IN transfer. After an IN transfer, the SIE will return the number of bytes sent to the host.

For an OUT transfer, the byte count represents the maximum number of bytes that can be received and stored in USB RAM. After an OUT transfer, the SIE will return the actual number of bytes received. If the number of bytes received exceeds the corresponding byte count, the data packet will be rejected and a NAK handshake will be generated. When this happens, the byte count will not be updated.

The 10-bit byte count is distributed over two registers. The lower eight bits of the count reside in the BDnCNT register. The upper two bits reside in BDnSTAT<1:0>. This represents a valid byte range of 0 to 1023.

#### 22.4.3 BD ADDRESS VALIDATION

The BD Address register pair contains the starting RAM address location for the corresponding endpoint buffer. No mechanism is available in hardware to validate the BD address.

If the value of the BD address does not point to an address in the USB RAM, or if it points to an address within another endpoint's buffer, data is likely to be lost or overwritten. Similarly, overlapping a receive buffer (OUT endpoint) with a BD location in use can yield unexpected results. When developing USB applications, the user may want to consider the inclusion of software-based address validation in their code.

### REGISTER 22-6: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD31STAT), SIE MODE (DATA RETURNED BY THE SIDE TO THE MCU)

| R/W-x | U-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| UOWN  | —   | PID3  | PID2  | PID1  | PID0  | BC9   | BC8   |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7UOWN: USB Own bit<br/>1 = The SIE owns the BD and its corresponding bufferbit 6Reserved: Not written by the SIEbit 5-2PID<3:0>: Packet Identifier bits<br/>The received token PID value of the last transfer (IN, OUT or SETUP transactions only).bit 1-0BC<9:8>: Byte Count 9 and 8 bits<br/>These bits are updated by the SIE to reflect the actual number of bytes received on an OUT transfer<br/>and the actual number of bytes transmitted on an IN transfer.

#### TABLE 25-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                     |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| a               | RAM access bit                                                                                                                                                  |  |  |  |  |

| ~               | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                     |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                    |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |  |  |  |  |

| d               | Destination select bit                                                                                                                                          |  |  |  |  |

|                 | d = 0: store result in WREG                                                                                                                                     |  |  |  |  |

|                 | d = 1: store result in file register f                                                                                                                          |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |  |  |  |  |

| f               | 8-bit Register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                                    |  |  |  |  |

| f <sub>s</sub>  | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                        |  |  |  |  |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                   |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |  |  |  |  |

| label           | Label name.                                                                                                                                                     |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:                     |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                                         |  |  |  |  |

| 11              | CALL/BRANCH and RETURN instructions.                                                                                                                            |  |  |  |  |

| PC              | Program Counter.                                                                                                                                                |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                                       |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                                      |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |  |  |  |  |

| PD              | Power-down bit.                                                                                                                                                 |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |  |  |  |  |

| s               | Fast Call/Return mode select bit                                                                                                                                |  |  |  |  |

|                 | s = 0: do not update into/from shadow registers                                                                                                                 |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                          |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                                     |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                                   |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                                   |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                                            |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                                                 |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                                                 |  |  |  |  |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |

| Zs              | 7-bit offset value for indirect addressing of register files (source).                                                                                          |  |  |  |  |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                                     |  |  |  |  |

| { }             | Optional argument.                                                                                                                                              |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                                                   |  |  |  |  |

| (text)          | The contents of text.                                                                                                                                           |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |  |  |  |  |

| < >             | Register bit field.                                                                                                                                             |  |  |  |  |

| E               | In the set of.                                                                                                                                                  |  |  |  |  |

| italics         | User defined term (font is Courier).                                                                                                                            |  |  |  |  |

| XORWF                                                      | OR W with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f                     |    |                       |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----|-----------------------|--|

| Syntax:                                                    | XORWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f {,d {,a}}           |    |                       |  |

| Operands:                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |    |                       |  |

| Operation:                                                 | (W) .XOR. (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | f) $\rightarrow$ dest |    |                       |  |

| Status Affected:                                           | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |    |                       |  |

| Encoding:                                                  | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10da ff               | ff | ffff                  |  |

|                                                            | register 'f'. If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in the register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                       |    |                       |  |

| Words:                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |    |                       |  |

| Cycles:                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |    |                       |  |

| Q Cycle Activity:                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |    |                       |  |

| Q1                                                         | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3                    |    | Q4                    |  |

| Decode                                                     | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Process<br>Data       |    | Vrite to<br>stination |  |

| Example: XORWF REG, 1, 0                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |    |                       |  |

| Before Instruc<br>REG<br>W<br>After Instructio<br>REG<br>W | = AFh<br>= B5h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |    |                       |  |

#### 27.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

1. TppS2ppS

2. TppS

| Z. TPPO |                                      |     |                |  |

|---------|--------------------------------------|-----|----------------|--|

| Т       |                                      |     |                |  |

| F       | Frequency                            | Т   | Time           |  |

| Lowerc  | ase letters (pp) and their meanings: |     |                |  |

| рр      |                                      |     |                |  |

| сс      | CCP1                                 | OSC | OSC1           |  |

| ck      | CLKOUT                               | rd  | RD             |  |

| CS      | CS                                   | rw  | RD or WR       |  |

| di      | SDI                                  | SC  | SCK            |  |

| do      | SDO                                  | SS  | SS             |  |

| dt      | Data in                              | tO  | TOCKI          |  |

| io      | I/O PORT                             | t1  | T1CKI          |  |

| mc      | MCLR                                 | wr  | WR             |  |

| Upperc  | case letters and their meanings:     |     |                |  |

| S       |                                      |     |                |  |

| F       | Fall                                 | Р   | Period         |  |

| н       | High                                 | R   | Rise           |  |

| 1       | Invalid (High-impedance)             | V   | Valid          |  |

| L       | Low                                  | Z   | High-impedance |  |

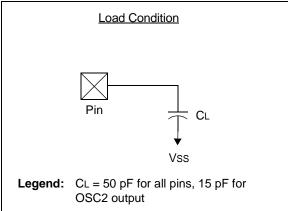

#### FIGURE 27-2: LOAD CONDITIONS

Unless otherwise noted,  $V_{IN}$  = 5V,  $F_{OSC}$  = 300 kHz,  $C_{IN}$  = 0.1  $\mu F,$   $T_A$  = 25°C.

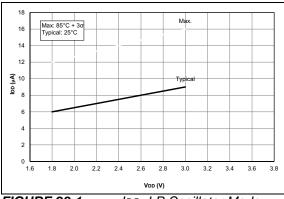

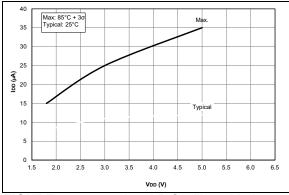

FIGURE 28-1: IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC18LF1XK50 Only.

FIGURE 28-2: IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC18F1XK50 Only.

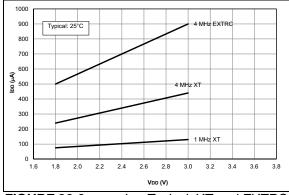

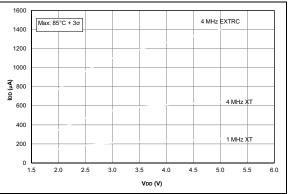

FIGURE 28-3: IDD Typical, XT and EXTRC Oscillator, PIC18LF1XK50 Only.

FIGURE 28-4: IDD Maximum, XT and EXTRC Oscillator, PIC18LF1XK50 Only.

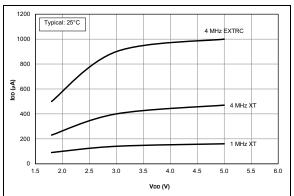

FIGURE 28-5: IDD Typical, XT and EXTRC Oscillator, PIC18F1XK50 Only.

FIGURE 28-6: IDD Maximum, XT and EXTRC Oscillator, PIC18F1XK50 Only.

Unless otherwise noted,  $V_{IN}$  = 5V,  $F_{OSC}$  = 300 kHz,  $C_{IN}$  = 0.1  $\mu F,\,T_A$  = 25°C.

© 2008-2015 Microchip Technology Inc.

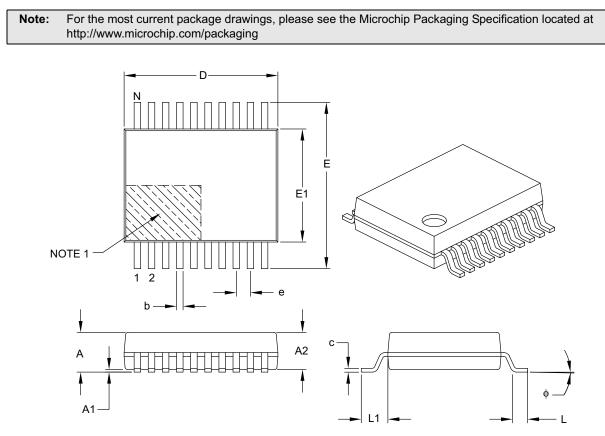

#### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units            |          | MILLIMETERS |      |  |  |

|--------------------------|------------------|----------|-------------|------|--|--|

|                          | Dimension Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins           | N                | 20       |             |      |  |  |

| Pitch                    | e                |          | 0.65 BSC    |      |  |  |

| Overall Height           | A                | -        | -           | 2.00 |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85 |  |  |

| Standoff                 | A1               | 0.05     | -           | -    |  |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20 |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60 |  |  |

| Overall Length           | D                | 6.90     | 7.20        | 7.50 |  |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95 |  |  |

| Footprint                |                  | 1.25 REF |             |      |  |  |

| Lead Thickness           | С                | 0.09     | -           | 0.25 |  |  |

| Foot Angle               | φ                | 0°       | 4°          | 8°   |  |  |

| Lead Width               | b                | 0.22     | _           | 0.38 |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

### 20-Lead Plastic Quad Flat, No Lead Package (MQ) - 5x5 mm Body [QFN] With 0.40mm Contact Length

**RECOMMENDED LAND PATTERN**

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch E            |    | 0.65 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 3.35 |  |

| Optional Center Pad Length | T2 |             |      | 3.35 |  |

| Contact Pad Spacing        | C1 |             | 4.50 |      |  |

| Contact Pad Spacing        | C2 |             | 4.50 |      |  |

| Contact Pad Width (X20)    | X1 |             |      | 0.40 |  |

| Contact Pad Length (X20)   | Y1 |             |      | 0.55 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2139A

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.