Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | SPI, UART/USART, USI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 54                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega325-16mi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

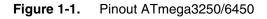

# 1. Pin Configurations

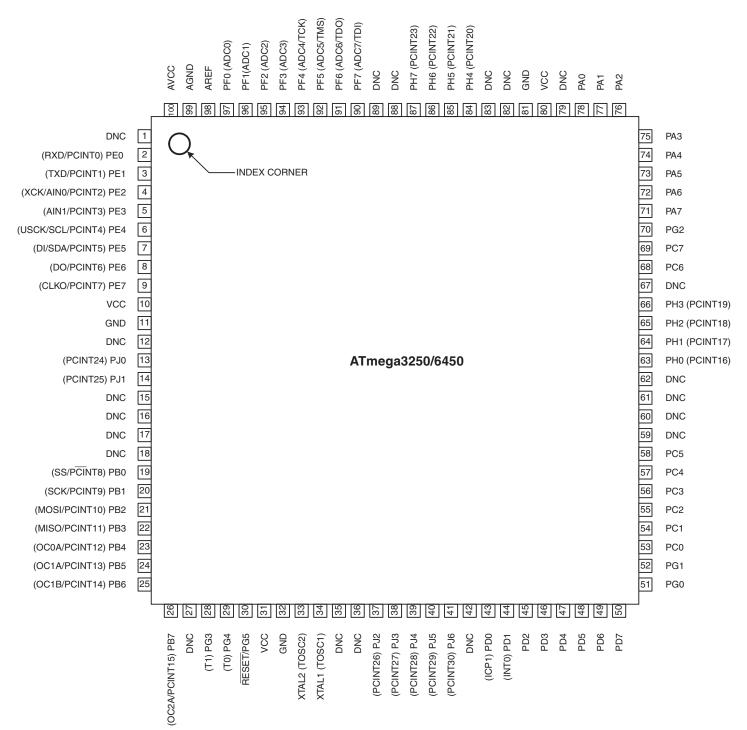

Figure 1-2. Pinout ATmega325/645

Note: The large center pad underneath the QFN/MLF packages is made of metal and internally connected to GND. It should be soldered or glued to the board to ensure good mechanical stability. If the center pad is left unconnected, the package might loosen from the board.

# 2. Overview

The Atmel ATmega325/3250/645/6450 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the Atmel ATmega325/3250/645/6450 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

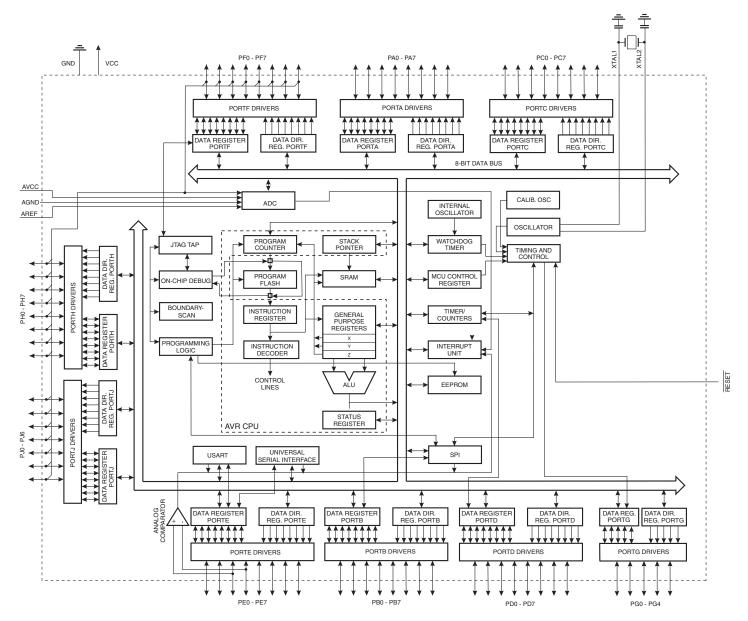

# 2.1 Block Diagram

#### Figure 2-1. Block Diagram

The Atmel<sup>®</sup>AVR<sup>®</sup> core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The

# 2.2 Comparison between ATmega325, ATmega3250, ATmega645 and ATmega6450

The ATmega325, ATmega3250, ATmega645, and ATmega6450 differ only in memory sizes, pin count and pinout. Table 2-1 on page 6 summarizes the different configurations for the four devices.

| Device     | Flash    | EEPROM  | RAM     | General Purpose<br>I/O Pins |

|------------|----------|---------|---------|-----------------------------|

| ATmega325  | 32Kbytes | 1Kbytes | 2Kbytes | 54                          |

| ATmega3250 | 32Kbytes | 1Kbytes | 2Kbytes | 69                          |

| ATmega645  | 64Kbytes | 2Kbytes | 4Kbytes | 54                          |

| ATmega6450 | 64Kbytes | 2Kbytes | 4Kbytes | 69                          |

| Table 2-1. | Configuration | Summary |

|------------|---------------|---------|

|------------|---------------|---------|

## 2.3 Pin Descriptions

The following section describes the I/O-pin special functions.

#### 2.3.1 V<sub>cc</sub>

Digital supply voltage.

#### 2.3.2 GND

Ground.

#### 2.3.3 Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 2.3.4 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B has better driving capabilities than the other ports.

Port B also serves the functions of various special features of the Atmel ATmega325/3250/645/6450 as listed on page 68.

#### 2.3.5 Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 2.3.11 Port J (PJ6..PJ0)

Port J is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port J output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port J pins that are externally pulled low will source current if the pull-up resistors are activated. The Port J pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port J also serves the functions of various special features of the ATmega3250/6450 as listed on page 72.

| 2.3.12 | RESET |                                                                                                                                                                                                                                                            |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |       | Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 28-4 on page 301. Shorter pulses are not guaranteed to generate a reset. |

| 2.3.13 | XTAL1 |                                                                                                                                                                                                                                                            |

|        |       | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                             |

| 2.3.14 | XTAL2 |                                                                                                                                                                                                                                                            |

|        |       | Output from the inverting Oscillator amplifier.                                                                                                                                                                                                            |

| 2.3.15 | AVCC  |                                                                                                                                                                                                                                                            |

|        |       | AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter.                            |

| 2.3.16 | AREF  |                                                                                                                                                                                                                                                            |

This is the analog reference pin for the A/D Converter.

# 7. Register Summary

Note: Registers with bold type only available in ATmega3250/6450.

| Address          | Nome             | D:+ 7  | -      | -      | -        |              | ga3250/6450   |                   | DH 0   | Daga       |

|------------------|------------------|--------|--------|--------|----------|--------------|---------------|-------------------|--------|------------|

| Address          | Name             | Bit 7  | Bit 6  | Bit 5  | Bit 4    | Bit 3        | Bit 2         | Bit 1             | Bit 0  | Page       |

| (0xFF)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xFE)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xFD)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xFC)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xFB)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xFA)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF9)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF8)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF7)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF6)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF5)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF4)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF3)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF2)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| , ,              | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF1)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xF0)           |                  |        |        |        |          |              |               |                   |        |            |

| (0xEF)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xEE)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xED)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xEC)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xEB)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xEA)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE9)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE8)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE7)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE6)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| . ,              | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE5)           | Reserved         | -      | -      | -      | -        | _            | -             | -                 | -      |            |

| (0xE4)           |                  |        |        |        |          |              |               |                   |        |            |

| (0xE3)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE2)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE1)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xE0)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xDF)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xDE)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xDD)           | PORTJ            | -      | PORTJ6 | PORTJ5 | PORTJ4   | PORTJ3       | PORTJ2        | PORTJ1            | PORTJ0 | 84         |

| (0xDC)           | DDRJ             | -      | DDJ6   | DDJ5   | DDJ4     | DDJ3         | DDJ2          | DDJ1              | DDJ0   | 84         |

| (0xDB)           | PINJ             | -      | PINJ6  | PINJ5  | PINJ4    | PINJ3        | PINJ2         | PINJ1             | PINJ0  | 84         |

| (0xDA)           | PORTH            | PORTH7 | PORTH6 | PORTH5 | PORTH4   | PORTH3       | PORTH2        | PORTH1            | PORTH0 | 84         |

| (0xD9)           | DDRH             | DDH7   | DDH6   | DDH5   | DDH4     | DDH3         | DDH2          | DDH1              | DDH0   | 84         |

| , ,              | PINH             | PINH7  | PINH6  | PINH5  | PINH4    | PINH3        | PINH2         | PINH1             | PINHO  | 84         |

| (0xD8)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      | 04         |

| (0xD7)           |                  |        |        |        |          |              |               |                   |        |            |

| (0xD6)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD5)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD4)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD3)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD2)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD1)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xD0)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xCF)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xCE)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xCD)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xCC)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

|                  | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xCB)           |                  |        |        |        |          |              |               |                   |        |            |

| (0xCA)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xC9)           | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0, 00)          | Reserved         | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xC8)           |                  | -      | -      | -      | -        | -            | -             | -                 | -      |            |

| (0xC8)<br>(0xC7) | Reserved         |        |        |        |          |              |               |                   |        |            |

|                  | Reserved<br>UDR0 |        |        |        | USART0 D | ata Register | 1             |                   |        | 179        |

| (0xC7)           |                  |        |        |        | USART0 D | ata Register | USART0 Baud F | ate Register High |        | 179<br>184 |

| Address          | Name            | Bit 7  | Bit 6  | Bit 5  | Bit 4           | Bit 3            | Bit 2   | Bit 1   | Bit 0   | Page |

|------------------|-----------------|--------|--------|--------|-----------------|------------------|---------|---------|---------|------|

| (0xC3)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xC2)           | UCSR0C          | -      | UMSEL0 | UPM01  | UPM00           | USBS0            | UCSZ01  | UCSZ00  | UCPOL0  | 182  |

| (0xC1)           | UCSR0B          | RXCIE0 | TXCIE0 | UDRIE0 | RXEN0           | TXEN0            | UCSZ02  | RXB80   | TXB80   | 181  |

| (0xC0)           | UCSR0A          | RXC0   | TXC0   | UDRE0  | FE0             | DOR0             | UPE0    | U2X0    | MPCM0   | 180  |

| (0xBF)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xBE)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xBD)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xBC)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xBB)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xBA)           | USIDR           |        |        |        | USI Data        | a Register       |         |         |         | 192  |

| (0xB9)           | USISR           | USISIF | USIOIF | USIPF  | USIDC           | USICNT3          | USICNT2 | USICNT1 | USICNT0 | 193  |

| (0xB8)           | USICR           | USISIE | USIOIE | USIWM1 | USIWM0          | USICS1           | USICS0  | USICLK  | USITC   | 194  |

| (0xB7)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xB6)           | ASSR            | -      | -      | -      | EXCLK           | AS2              | TCN2UB  | OCR2UB  | TCR2UB  | 145  |

| . ,              | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xB5)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xB4)           | OCR2A           | -      |        |        |                 |                  |         | -       |         | 145  |

| (0xB3)           |                 |        |        | 11/11  |                 | ut Compare Regis | er A    |         |         | 145  |

| (0xB2)           | TCNT2           |        |        |        |                 | Counter2         |         |         |         | 145  |

| (0xB1)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xB0)           | TCCR2A          | FOC2A  | WGM20  | COM2A1 | COM2A0          | WGM21            | CS22    | CS21    | CS20    | 143  |

| (0xAF)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xAE)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xAD)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xAC)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xAB)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xAA)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA9)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA8)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA0)<br>(0xA7) | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| . ,              | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA6)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA5)           |                 |        |        |        |                 |                  |         |         |         |      |

| (0xA4)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA3)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA2)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA1)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0xA0)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9F)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9E)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9D)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9C)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9B)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x9A)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x99)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x99)<br>(0x98) | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| . ,              | Reserved        | -      | _      | -      | -               | _                | _       | -       | -       |      |

| (0x97)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x96)           | Reserved        | -      | -      |        |                 |                  |         |         | -       |      |

| (0x95)           |                 |        |        | -      | -               | -                | -       | -       |         |      |

| (0x94)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x93)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x92)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x91)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x90)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x8F)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x8E)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x8D)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x8C)           | Reserved        | -      | -      | -      | -               | -                | -       | -       | -       |      |

| (0x8B)           | OCR1BH          |        |        |        | Counter1 Output | Compare Register |         |         |         | 127  |

| (0x8A)           | OCR1BL          |        |        |        |                 | Compare Register |         |         |         | 127  |

|                  | OCR1AH          |        |        |        |                 | Compare Register |         |         |         | 127  |

| (0x89)           | OCR1AL          |        |        |        |                 | Compare Register | -       |         |         | 127  |

| (0x88)           |                 |        |        |        |                 |                  |         |         |         |      |

| (0x87)           | ICR1H           |        |        |        |                 | Capture Register | -       |         |         | 127  |

| (0x86)           | ICR1L<br>TCNT1H |        |        | Tin    |                 | Capture Register | LOW     |         |         | 127  |

|                  |                 |        |        |        |                 | unter1 High      |         |         |         | 127  |

| Mnemonics        | Operands     | Description                        | Operation                                                          | Flags   | #Clocks |

|------------------|--------------|------------------------------------|--------------------------------------------------------------------|---------|---------|

| BRTC             | k            | Branch if T Flag Cleared           | if (T = 0) then PC $\leftarrow$ PC + k + 1                         | None    | 1/2     |

| BRVS             | k            | Branch if Overflow Flag is Set     | if (V = 1) then PC $\leftarrow$ PC + k + 1                         | None    | 1/2     |

| BRVC             | k            | Branch if Overflow Flag is Cleared | if (V = 0) then PC $\leftarrow$ PC + k + 1                         | None    | 1/2     |

| BRIE             | k            | Branch if Interrupt Enabled        | if $(I = 1)$ then PC $\leftarrow$ PC + k + 1                       | None    | 1/2     |

| BRID             | k            | Branch if Interrupt Disabled       | if (I = 0) then PC $\leftarrow$ PC + k + 1                         | None    | 1/2     |

| BIT AND BIT-TEST | INSTRUCTIONS | · ·                                |                                                                    |         |         |

| SBI              | P,b          | Set Bit in I/O Register            | I/O(P,b) ← 1                                                       | None    | 2       |

| CBI              | P,b          | Clear Bit in I/O Register          | I/O(P,b) ← 0                                                       | None    | 2       |

| LSL              | Rd           | Logical Shift Left                 | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z,C,N,V | 1       |

| LSR              | Rd           | Logical Shift Right                | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z,C,N,V | 1       |

| ROL              | Rd           | Rotate Left Through Carry          | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z,C,N,V | 1       |

| ROR              | Rd           | Rotate Right Through Carry         | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z,C,N,V | 1       |

| ASR              | Rd           | Arithmetic Shift Right             | Rd(n) ← Rd(n+1), n=06                                              | Z,C,N,V | 1       |

| SWAP             | Rd           | Swap Nibbles                       | Rd(30)←Rd(74),Rd(74)←Rd(30)                                        | None    | 1       |

| BSET             | s            | Flag Set                           | $SREG(s) \leftarrow 1$                                             | SREG(s) | 1       |

| BCLR             | s            | Flag Clear                         | $SREG(s) \leftarrow 0$                                             | SREG(s) | 1       |

| BST              | Rr, b        | Bit Store from Register to T       | $T \leftarrow Rr(b)$                                               | т       | 1       |

| BLD              | Rd, b        | Bit load from T to Register        | Rd(b) ← T                                                          | None    | 1       |

| SEC              |              | Set Carry                          | C ← 1                                                              | С       | 1       |

| CLC              |              | Clear Carry                        | C ← 0                                                              | С       | 1       |

| SEN              |              | Set Negative Flag                  | N ← 1                                                              | Ν       | 1       |

| CLN              |              | Clear Negative Flag                | N ← 0                                                              | N       | 1       |

| SEZ              |              | Set Zero Flag                      | Z ← 1                                                              | Z       | 1       |

| CLZ              |              | Clear Zero Flag                    | Z ← 0                                                              | Z       | 1       |

| SEI              |              | Global Interrupt Enable            | l ← 1                                                              | 1       | 1       |

| CLI              |              | Global Interrupt Disable           | l ← 0                                                              | 1       | 1       |

| SES              |              | Set Signed Test Flag               | S ← 1                                                              | S       | 1       |

| CLS              |              | Clear Signed Test Flag             | S ← 0                                                              | S       | 1       |

| SEV              |              | Set Twos Complement Overflow.      | V ← 1                                                              | V       | 1       |

| CLV              |              | Clear Twos Complement Overflow     | V ← 0                                                              | V       | 1       |

| SET              |              | Set T in SREG                      | T ← 1                                                              | Т       | 1       |

| CLT              |              | Clear T in SREG                    | T ← 0                                                              | Т       | 1       |

| SEH              |              | Set Half Carry Flag in SREG        | H ← 1                                                              | Н       | 1       |

| CLH              |              | Clear Half Carry Flag in SREG      | H ← 0                                                              | Н       | 1       |

| DATA TRANSFER I  | NSTRUCTIONS  |                                    |                                                                    |         | -       |

| MOV              | Rd, Rr       | Move Between Registers             | $Rd \leftarrow Rr$                                                 | None    | 1       |

| MOVW             | Rd, Rr       | Copy Register Word                 | $Rd+1:Rd \leftarrow Rr+1:Rr$                                       | None    | 1       |

| LDI              | Rd, K        | Load Immediate                     | Rd ← K                                                             | None    | 1       |

| LD               | Rd, X        | Load Indirect                      | $Rd \leftarrow (X)$                                                | None    | 2       |

| LD               | Rd, X+       | Load Indirect and Post-Inc.        | $Rd \leftarrow (X), X \leftarrow X + 1$                            | None    | 2       |

| LD               | Rd, - X      | Load Indirect and Pre-Dec.         | $X \leftarrow X - 1, Rd \leftarrow (X)$                            | None    | 2       |

| LD               | Rd, Y        | Load Indirect                      | $Rd \leftarrow (Y)$                                                | None    | 2       |

| LD               | Rd, Y+       | Load Indirect and Post-Inc.        | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                            | None    | 2       |

| LD               | Rd, - Y      | Load Indirect and Pre-Dec.         | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                            | None    | 2       |

| LDD              | Rd,Y+q       | Load Indirect with Displacement    | $Rd \leftarrow (Y + q)$                                            | None    | 2       |

| LD               | Rd, Z        | Load Indirect                      | $Rd \leftarrow (Z)$                                                | None    | 2       |

| LD               | Rd, Z+       | Load Indirect and Post-Inc.        | $Rd \leftarrow (Z), Z \leftarrow Z+1$                              | None    | 2       |

| LD               | Rd, -Z       | Load Indirect and Pre-Dec.         | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                            | None    | 2       |

| LDD              | Rd, Z+q      | Load Indirect with Displacement    | $Rd \leftarrow (Z + q)$                                            | None    | 2       |

| LDS              | Rd, k        | Load Direct from SRAM              | $Rd \leftarrow (k)$                                                | None    | 2       |

| ST               | X, Rr        | Store Indirect                     | $(X) \leftarrow Rr$                                                | None    | 2       |

| ST               | X+, Rr       | Store Indirect and Post-Inc.       | $(X) \leftarrow Rr, X \leftarrow X + 1$                            | None    | 2       |

| ST               | - X, Rr      | Store Indirect and Pre-Dec.        | $X \leftarrow X - 1, (X) \leftarrow Rr$                            | None    | 2       |

| ST               | Y, Rr        | Store Indirect                     | $(Y) \leftarrow Rr$                                                | None    | 2       |

| ST               | Y+, Rr       | Store Indirect and Post-Inc.       | $(Y) \leftarrow Rr,  Y \leftarrow Y + 1$                           | None    | 2       |

| ST               | - Y, Rr      | Store Indirect and Pre-Dec.        | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                            | None    | 2       |

| STD              | Y+q,Rr       | Store Indirect with Displacement   | $(Y + q) \leftarrow Rr$                                            | None    | 2       |

| ST               | Z, Rr        | Store Indirect                     | $(Z) \leftarrow Rr$                                                | None    | 2       |

| ST               | Z+, Rr       | Store Indirect and Post-Inc.       | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                            | None    | 2       |

| ST               | -Z, Rr       | Store Indirect and Pre-Dec.        | $Z \leftarrow Z - 1$ , (Z) $\leftarrow Rr$                         | None    | 2       |

| STD              | Z+q,Rr       | Store Indirect with Displacement   | $(Z + q) \leftarrow Rr$                                            | None    | 2       |

| STS              | k, Rr        | Store Direct to SRAM               | (k) ← Rr                                                           | None    | 2       |

| LPM              |              | Load Program Memory                | $R0 \leftarrow (Z)$                                                | None    | 3       |

| LPM              | Rd, Z        | Load Program Memory                | $Rd \leftarrow (Z)$                                                | None    | 3       |

|                  |              |                                    |                                                                    |         |         |

| LPM              | Rd, Z+       | Load Program Memory and Post-Inc   | $Rd \leftarrow (Z), Z \leftarrow Z+1$                              | None    | 3       |

# 9. Ordering Information

# 9.1 ATmega325

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                                                                         | Package Type <sup>(1)</sup> | Operational Range |

|----------------------------|--------------|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|

| 8                          | 1.8 - 5.5V   | ATmega325V-8AU<br>ATmega325V-8AUR <sup>(4)</sup><br>ATmega325V-8MU<br>ATmega325V-8MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial        |

| 16                         | 2.7 - 5.5V   | ATmega325-16AU<br>ATmega325-16AUR <sup>(4)</sup><br>ATmega325-16MU<br>ATmega325-16MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | (-40°C to 85°C)   |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For Speed Grades see Figure 28-1 on page 299 and Figure 28-2 on page 299.

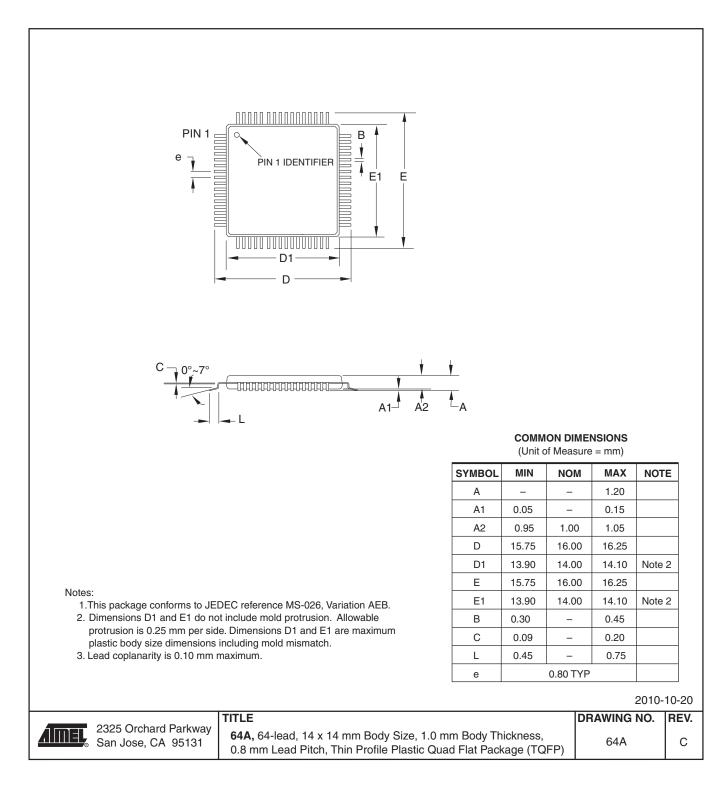

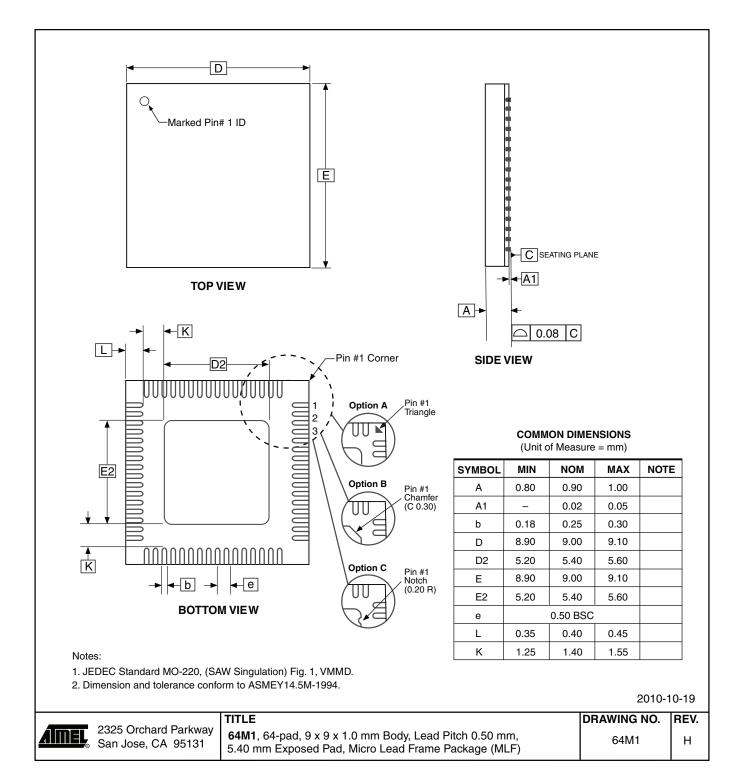

|      | Package Type                                                                |  |  |  |  |

|------|-----------------------------------------------------------------------------|--|--|--|--|

| 64A  | 64-lead, 14 x 14 x 1.0mm, Thin Profile Plastic Quad Flat Package (TQFP)     |  |  |  |  |

| 64M1 | 64-pad, 9 x 9 x 1.0mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF) |  |  |  |  |

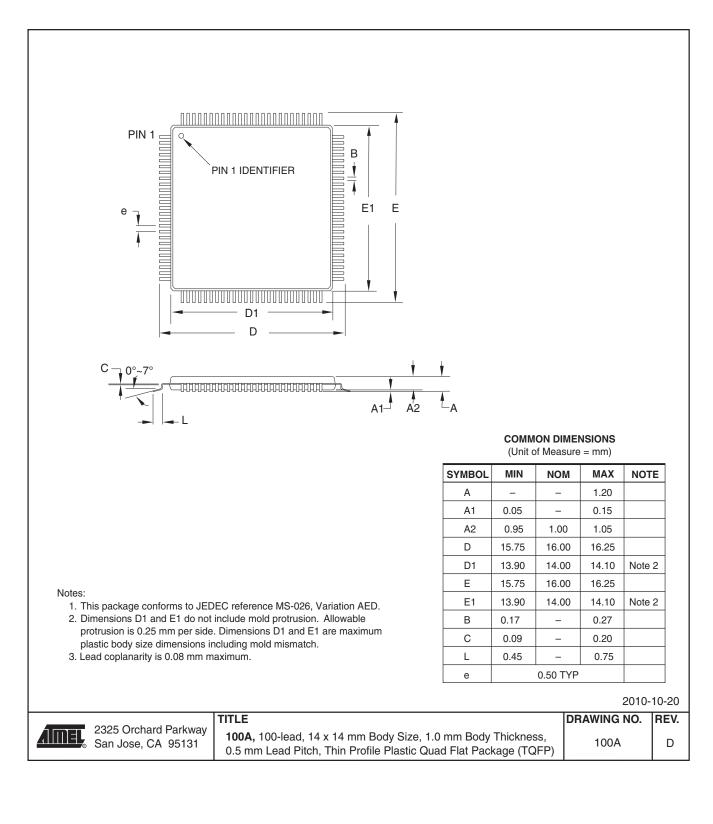

# 9.2 ATmega3250

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                       | Package Type <sup>(1)</sup> | Operational Range |

|----------------------------|--------------|----------------------------------------------------|-----------------------------|-------------------|

| 8                          | 1.8 - 5.5V   | ATmega3250V-8AU<br>ATmega3250V-8AUR <sup>(4)</sup> | 100A<br>100A                | Industrial        |

| 16                         | 2.7 - 5.5V   | ATmega3250-16AU<br>ATmega3250-16AUR <sup>(4)</sup> | 100A<br>100A                | (-40°C to 85°C)   |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For Speed Grades see Figure 28-1 on page 299 and Figure 28-2 on page 299.

|      | Package Type                                                                               |  |

|------|--------------------------------------------------------------------------------------------|--|

| 100A | 100-lead, 14 x 14 x 1.0mm, 0.5mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |

# 9.3 ATmega645

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                                                                         | Package Type <sup>(1)</sup> | <b>Operational Range</b>      |  |

|----------------------------|--------------|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|--|

| 8                          | 1.8 - 5.5V   | ATmega645V-8AU<br>ATmega645V-8AUR <sup>(4)</sup><br>ATmega645V-8MU<br>ATmega645V-8MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial<br>(-40°C to 85°C) |  |

| 16                         | 2.7 - 5.5V   | ATmega645-16AU<br>ATmega645-16AUR <sup>(4)</sup><br>ATmega645-16MU<br>ATmega645-16MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  |                               |  |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For Speed Grades see Figure 28-1 on page 299 and Figure 28-2 on page 299.

| Package Type |                                                                             |  |  |  |

|--------------|-----------------------------------------------------------------------------|--|--|--|

| 64A          | 64-lead, 14 x 14 x 1.0mm, Thin Profile Plastic Quad Flat Package (TQFP)     |  |  |  |

| 64M1         | 64-pad, 9 x 9 x 1.0mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF) |  |  |  |

# 9.4 ATmega6450

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                       | Package Type <sup>(1)</sup> | <b>Operational Range</b>      |

|----------------------------|--------------|----------------------------------------------------|-----------------------------|-------------------------------|

| 8                          | 1.8 - 5.5V   | ATmega6450V-8AU<br>ATmega6450V-8AUR <sup>(4)</sup> | 100A<br>100A                | Industrial<br>(-40°C to 85°C) |

| 16                         | 2.7 - 5.5V   | ATmega6450-16AU<br>ATmega6450-16AUR <sup>(4)</sup> | 100A<br>100A                |                               |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For Speed Grades see Figure 28-1 on page 299 and Figure 28-2 on page 299.

| Package Type                                         |  |  |  |

|------------------------------------------------------|--|--|--|

| Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |  |

|                                                      |  |  |  |

# 10. Packaging Information

# 10.1 64A

10.2 64M1

## 10.3 100A

# 11. Errata

# 11.1 Errata ATmega325

The revision letter in this section refers to the revision of the ATmega325 device.

#### 11.1.1 ATmega325 Rev. C

• Interrupts may be lost when writing the timer registers in the asynchronous timer

1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

#### 11.1.2 ATmega325 Rev. B

Not sampled.

#### 11.1.3 ATmega325 Rev. A

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- 1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

## Problem Fix/ Workaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 11.2 Errata ATmega3250

The revision letter in this section refers to the revision of the ATmega3250 device.

## 11.2.1 ATmega3250 Rev. C

• Interrupts may be lost when writing the timer registers in the asynchronous timer

1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

## 11.2.2 ATmega3250 Rev. B

Not sampled.

#### 11.2.3 ATmega3250 Rev. A

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- 1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

#### 11.3 Errata ATmega645

The revision letter in this section refers to the revision of the ATmega645 device.

#### 11.3.1 ATmega645 Rev. A

Interrupts may be lost when writing the timer registers in the asynchronous timer

#### 1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

#### 11.4 Errata ATmega6450

The revision letter in this section refers to the revision of the ATmega6450 device.

#### 11.4.1 ATmega6450 Rev. A

• Interrupts may be lost when writing the timer registers in the asynchronous timer

1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# **12. Datasheet Revision History**

Please note that the referring page numbers in this section are referring to this document. The referring revision in this section are referring to the document revision.

## 12.1 Rev. 2570N - 05/11

- 1. Added Atmel QTouch Library Support and QTouch Sensing Capablity Features.

- 2. Updated the last page with Atmel<sup>®</sup> trademarks and Microsft Windows<sup>®</sup> trademarks.

## 12.2 Rev. 2570M - 04/11

- 1. Removed "Preliminary" from the front page

- 2. Removed "Disclaimer" section from the datasheet

- 3. Updated Table 28-5 on page 301 "BODLEVEL Fuse Coding(1)"

- 4. Updated "Ordering Information" on page 17 to include the "Tape & Reel" devices. Removed "AI" and "MI" devices.

- 5. Updated "Errata" on page 24.

- 6. Updated the datasheet according to the Atmel new drand style guide, including the last page.

# 12.3 Rev. 2570L - 08/07

- 1. Updated "Features" on page 1.

- 2. Added "Data Retention" on page 9

- 3. Updated "Serial Programming Algorithm" on page 281.

- 4. Updated "Speed Grades" on page 299.

- 5. Updated "System and Reset Characteristics" on page 301.

- 6. Updated the Register Description at the end of each chapter.

## 12.4 Rev. 2570K - 04/07

1. Updated "Errata" on page 24.

## 12.5 Rev. 2570J - 11/06

- 1. Updated Table 28-7 on page 304.

- 2. Updated note in Table 28-7 on page 304.

## 12.6 Rev. 2570I - 07/06

- 1. Updated Table 15-6 on page 92.

- 2. Updated Table 15-2 on page 97, Table 15-4 on page 97, Table 17-3 on page 124, Table 17-5 on page 125, Table 18-2 on page 143 and Table 18-4 on page 144.

- 3. Updated "Fast PWM Mode" on page 115.

- 4. Updated Features in "USI Universal Serial Interface" on page 185.

- 5. Added "Clock speed considerations." on page 191.

- 6. Updated "Errata" on page 24.

#### 12.7 Rev. 2570H - 06/06

- 1. Updated "Calibrated Internal RC Oscillator" on page 29.

- 2. Updated "OSCCAL Oscillator Calibration Register" on page 32.

- 3. Added Table 28-2 on page 300.

#### 12.8 Rev. 2570G - 04/06

- 1. Updated "Calibrated Internal RC Oscillator" on page 29.

- 12.9 Rev. 2570F 03/06

- 1. Updated "Errata" on page 24.

# 12.10 Rev. 2570E - 03/06

- 1. Added Addresses in Register Descriptions.

- 2. Updated number of Genearl Purpose I/O pins.

- 3. Correction of Bitnames in "Register Summary" on page 10.

- 4. Added "Resources" on page 9.

- 5. Updated "Power Management and Sleep Modes" on page 35.

- 6. Updated "Bit 0 IVCE: Interrupt Vector Change Enable" on page 54.

- 7. Updated Introduction in "I/O-Ports" on page 60.

- 8. Updated 19. "SPI Serial Peripheral Interface" on page 148.

- 9. Updated "Bit 6 ACBG: Analog Comparator Bandgap Select" on page 199.

- 10 Updated Features in "Analog to Digital Converter" on page 201.

- 11. Updated "Prescaling and Conversion Timing" on page 204.

- 12. Updated "Atmel ATmega325/3250/645/6450 Boot Loader Parameters" on page 262.

- 13. Updated "DC Characteristics" on page 297.

# 12.11 Rev. 2570D - 05/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Added "Pin Change Interrupt Timing" on page 55.

- 3. Updated "Signature Bytes" on page 268.

- 4. Updated Table 27-15 on page 282.

- 5. Added Figure 27-12 on page 284.

- 6. Updated Figure 23-9 on page 209 and Figure 27-5 on page 276.

- 7. Updated algorithm "Enter Programming Mode" on page 271.

- 8. Added "Supply Current of I/O modules" on page 311.

- 9. Updated "Ordering Information" on page 17.

# 12.12 Rev. 2570C - 11/04

- 1. "0 8MHz @ 2.7 5.5V; 0 16MHz @ 4.5 5.5V" on page 1 updated.

- 2. Table 9-8 on page 30 updated.

- COM01:0 renamed COM0A1:0 in "8-bit Timer/Counter0 with PWM" on page 85.

- 4. PRR-bit descripton added to "16-bit Timer/Counter1" on page 102, "SPI Serial Peripheral Interface" on page 148, and "USART0" on page 157.

- 5. "Part Number" on page 225 updated.

- 6. "Typical Characteristics" on page 306 updated.

- 7. "DC Characteristics" on page 297 updated.

- 8. "Alternate Functions of Port G" on page 76 updated.

## 12.13 Rev. 2570B - 09/04

1. Updated "Ordering Information" on page 17.

## 12.14 Rev. 2570A - 09/04

1. Initial revision.