# E·) ( Frenesas Electronics America Inc - <u>UPD70F3913GC(R)-UEU-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                    |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | V850E1                                                                                 |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 100MHz                                                                                 |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                                |

| Number of I/O              | 55                                                                                     |

| Program Memory Size        | 256КВ (256К х 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 24K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.35V ~ 1.65V                                                                          |

| Data Converters            | A/D 12x10b, 7x12b                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 100-LQFP                                                                               |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3913gc-r-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

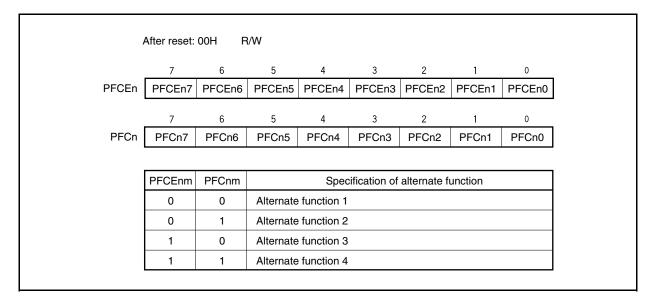

#### (5) Port n function control expansion register (PFCEn)

The PFCEn register specifies the alternate function of a port pin to be used if the pin has three or more alternate functions.

Each bit of this register corresponds to one pin of port n, and the alternate function of a port pin can be specified in 1-bit units.

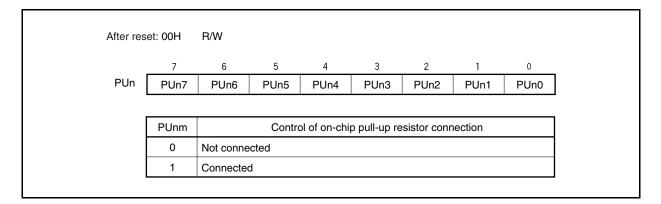

### (6) Pull-up resistor option register (PUn)

PUn is a register that specifies the connection of an on-chip pull-up resistor.

Each bit of the pull-up resistor option register corresponds to one pin of port n and can be specified in 1-bit units.

| Port Name           | Function    | PMCmn             | PFCEmn | PFCmn           | PMmn      | Output Data        | Pmn Read Value | Remark                         |

|---------------------|-------------|-------------------|--------|-----------------|-----------|--------------------|----------------|--------------------------------|

| P40 <sup>Note</sup> | Output port | 0                 | ×      | ×               | 0         | Port latch         | Port latch     |                                |

|                     | Input port  |                   |        |                 | 1         | -                  | Pin level      |                                |

|                     | SIF0        | 1                 | 0      | 0               | 0         | _                  | Port latch     | Alternate input (serial input) |

|                     |             |                   |        |                 | 1         |                    | Pin level      |                                |

|                     | RXDA0       | 1                 | 0      | 1               | 0         | _                  | Port latch     | Alternate input (serial input) |

|                     |             |                   |        |                 | 1         |                    | Pin level      |                                |

|                     | TOA00       | 1                 | 1      | 1               | 0         | Alternate output   | Port latch     |                                |

|                     |             | 1 (timer output   |        | (timer output)  | Pin level |                    |                |                                |

| P41                 | Output port | 0                 | None   | ×               | 0         | Port latch         | Port latch     |                                |

|                     | Input port  |                   |        |                 | 1         | _                  | Pin level      |                                |

|                     | SOF0        | 1                 | None   | 0               | 0         | Alternate output 1 | Port latch     |                                |

|                     |             | 1 (serial output) |        | (serial output) | Pin level |                    |                |                                |

|                     | TXDA0       | 1                 | None   | 1               | 0         | Alternate output 2 | Port latch     |                                |

|                     |             |                   |        |                 | 1         | (serial output)    | Pin level      |                                |

#### Table 4-15. Output Data and Port Read Value for Each Setting (7/10)

Note The P40 pin is also used for on-chip debugging. Switching between the on-chip debug function and port function (including the alternate function) can be done by using the DRST pin level. The following shows the setting method.

| Port 4 Functions            |                              |  |  |  |  |  |

|-----------------------------|------------------------------|--|--|--|--|--|

| Low-Level Input to DRST Pin | High-Level Input to DRST Pin |  |  |  |  |  |

| P40/SIF0/RXDA0/TOA00        | DDI                          |  |  |  |  |  |

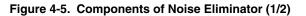

The components of the noise eliminator are shown below.

(1/2)

## (2) TAAn control register 1 (TAAnCTL1)

The TAAnCTL1 register is an 8-bit register that controls the TAAn operation.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

|                            | 7                                                                                                                                                                                                                                                              | 6                                                                       | 5                                              | 4                                         | 3                                           | 2          | 1       | 0       |  |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|---------------------------------------------|------------|---------|---------|--|--|--|--|--|

| TAAnCTL1                   | TAAaSYE <sup>Note 1</sup>                                                                                                                                                                                                                                      | TAAnEST                                                                 | TAA2EEENote 2                                  | 0                                         | 0                                           | TAAnMD2    | TAAnMD1 | TAAnMD0 |  |  |  |  |  |

| $\int n = 0 \text{ to } 2$ |                                                                                                                                                                                                                                                                |                                                                         |                                                |                                           |                                             |            |         |         |  |  |  |  |  |

| [a = 0, 1 ]                | TAAaSYE <sup>Note 1</sup>                                                                                                                                                                                                                                      |                                                                         | Operation mode selection                       |                                           |                                             |            |         |         |  |  |  |  |  |

|                            | 0                                                                                                                                                                                                                                                              | TAAa sing                                                               | le mode                                        |                                           |                                             |            |         |         |  |  |  |  |  |

|                            | 1                                                                                                                                                                                                                                                              | Tuning op                                                               | eration mode                                   | e (see <b>10.</b> 4                       | <b>1.5</b> )                                |            |         |         |  |  |  |  |  |

| an                         | 1       Tuning operation mode (see 10.4.5)         TAAa can be used only as an A/D conversion start trigger factor of A/D converters 0 and 1 during the tuning operation. In the tuning operation mode, this bit always operates in synchronization with TABa. |                                                                         |                                                |                                           |                                             |            |         |         |  |  |  |  |  |

|                            |                                                                                                                                                                                                                                                                |                                                                         |                                                |                                           |                                             |            |         |         |  |  |  |  |  |

|                            | TAAnEST                                                                                                                                                                                                                                                        |                                                                         |                                                | Softwa                                    | are trigge                                  | er control |         |         |  |  |  |  |  |

|                            | TAAnEST<br>0                                                                                                                                                                                                                                                   |                                                                         |                                                | Softwa                                    | are trigge<br>-                             | r control  |         |         |  |  |  |  |  |

|                            |                                                                                                                                                                                                                                                                |                                                                         | s a valid sig                                  | nal for exte                              | –<br>ernal trig                             |            |         |         |  |  |  |  |  |

|                            | 0                                                                                                                                                                                                                                                              | <ul> <li>In one-s<br/>A one-s<br/>trigger.</li> <li>In exter</li> </ul> | shot pulse of<br>hot pulse is<br>nal trigger p | nal for extend<br>utput mod<br>output wit | ernal trigg<br>e:<br>th writing<br>ut mode: |            |         |         |  |  |  |  |  |

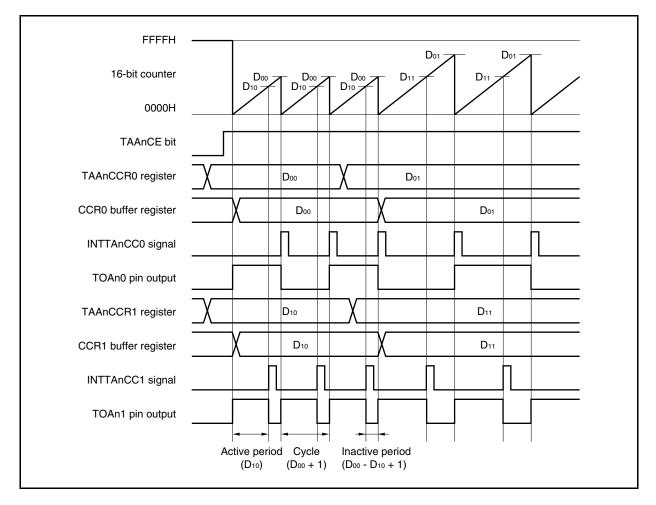

Figure 6-34. Basic Timing in PWM Output Mode

When the TAAnCE bit is set to 1, the 16-bit counter is cleared from FFFFH to 0000H, starts counting, and outputs a PWM waveform from the TOAn1 pin.

The active level width, cycle, and duty factor of the PWM waveform can be calculated as follows.

Active level width = (Set value of TAAnCCR1 register) × Count clock cycle Cycle = (Set value of TAAnCCR0 register + 1) × Count clock cycle Duty factor = (Set value of TAAnCCR1 register)/(Set value of TAAnCCR0 register + 1)

The PWM waveform can be changed by rewriting the TAAnCCRa register while the counter is operating. The newly written value is reflected when the count value of the 16-bit counter matches the value of the CCR0 buffer register and the 16-bit counter is cleared to 0000H.

The compare match interrupt request signal INTTAnCC0 is generated when the 16-bit counter counts next time after its count value matches the value of the CCR0 buffer register, and the 16-bit counter is cleared to 0000H. The compare match interrupt request signal INTTAnCC1 is generated when the count value of the 16-bit counter matches the value of the CCR1 buffer register.

The value set to the TAAnCCRa register is transferred to the CCRa buffer register when the count value of the 16-bit counter matches the value of the CCRa buffer register and the 16-bit counter is cleared to 0000H.

**Remark** n = 0 to 2 a = 0, 1

# Figure 6-35. Register Setting in PWM Output Mode (2/2)

| (d)     | TAA2 I/O c                | control reg               | gister 2 (1            | FAA2IOC    | 2)          |                       |           |            |                                                                    |

|---------|---------------------------|---------------------------|------------------------|------------|-------------|-----------------------|-----------|------------|--------------------------------------------------------------------|

|         |                           |                           |                        |            | TAA2EES1    | TAA2EES0              | TAA2ETS1  | TAA2ETS0   | )                                                                  |

| TAA2IOC | 2 0                       | 0                         | 0                      | 0          | 0/1         | 0/1                   | 0         | 0          |                                                                    |

|         |                           |                           |                        |            |             |                       |           |            |                                                                    |

|         |                           |                           |                        |            |             |                       |           |            | Select valid edge<br>of external event<br>count input (TIA20 pin). |

| (e)     | TAAn cour<br>The value of |                           |                        |            |             | ading the 1           | ſAAnCNT   | register.  |                                                                    |

| (f)     | TAAn capt                 | ure/comp                  | are regis              | ters 0 an  | nd 1 (TAAı  | nCCR0 ar              | nd TAAnC  | CR1)       |                                                                    |

|         | If D <sub>0</sub> is set  | to the TA                 | AnCCR0                 | register a | and D1 to t | he TAAnC              | CR1 regi  | ster, the  | cycle and active level of                                          |

|         | the PWM v                 | vaveform a                | are as follo           | ows.       |             |                       |           |            |                                                                    |

|         | -                         | (D₀ + 1) ×<br>vel width = |                        | •          | cycle       |                       |           |            |                                                                    |

|         | Remarks                   |                           | /O contro<br>n the PWN | •          |             | OC1) and <sup>-</sup> | TAAn opti | on registe | er 0 (TAAnOPT0) are not                                            |

|         |                           | <b>2.</b> n = 0 to        | o 2                    |            |             |                       |           |            |                                                                    |

|         |                           | a = 0,                    | 1                      |            |             |                       |           |            |                                                                    |

|         |                           |                           |                        |            |             |                       |           |            |                                                                    |

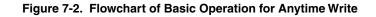

#### (2) Anytime write and batch write

The TABnCCR0 to TABnCCR3 registers can be rewritten in the TABn during timer operation (TABnCTL0.TABnCE bit = 1), but the write method (anytime write, batch write) of the CCR0 to CCR3 buffer registers differs depending on the mode.

#### (a) Anytime write

In this mode, data is transferred at any time from the TABnCCR0 to TABnCCR3 registers to the CCR0 to CCR3 buffer registers during the timer operation.

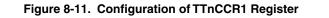

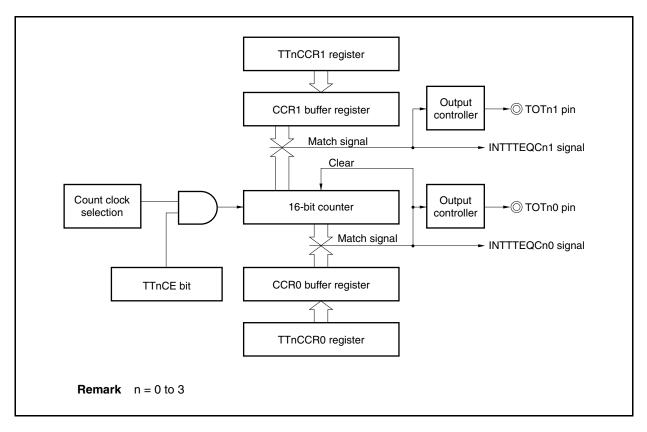

## (d) Operation of TTnCCR1 register

Figure 8-47. Register Setting in Pulse Width Measurement Mode (1/2)

#### (5) D/A converter

The D/A converter is connected between AV<sub>DD2</sub> and AV<sub>SS2</sub> and generates a voltage to be compared with an input analog signal.

#### (6) ANI2n pin

The ANI2n pin is an analog input pin for A/D converter 2. This pin inputs the analog signals to be A/D converted. Pins other than the one that is selected by the AD2S register as analog signal input pins can be used as input port pins.

- Cautions 1. Make sure that the voltages input to the ANI2n pin do not exceed the rated values. If a voltage higher than or equal to AV<sub>DD2</sub> or lower than or equal to AV<sub>SS2</sub> is input to a channel, the conversion value of the channel is undefined, and the conversion values of the other channels may also be affected.

- 2. The analog input pin (ANI2n) is alternately used as input port pin (P7n). If an instruction to input a signal to port 7 is executed during conversion when one of ANI2n is selected for A/D conversion, the resolution for conversion may drop.

#### (7) AVDD2 pin

The AV<sub>DD2</sub> pin alternately functions as the pin for inputting the positive power supply and reference voltage of A/D converter 2. This pin converts signals input to the ANI2n pin to digital signals based on the voltage applied between AV<sub>DD2</sub> and AV<sub>SS2</sub>.

Always make the potential at this pin the same as that at the EVDD0, EVDD1, EVDD2, and EVDD3 pins (V850E/IH4 only) even when A/D converter 2 is not used.

The operating voltage range of the AV<sub>DD2</sub> pin is  $EV_{DD0} = EV_{DD1} = EV_{DD2} = EV_{DD3}$  (V850E/IH4 only) = AV<sub>DD2</sub> = 4.0 to 5.5 V.

#### (8) AVss2 pin

This is the ground pin of A/D converter 2. Always make the potential at this pin the same as that at the EVsso, EVss1, EVss2, EVss3 (V850E/IH4 only) and EVss4 (V850E/IH4 only) pins even when A/D converter 2 is not used.

**Remark** n = 0 to 11

## CHAPTER 16 CLOCKED SERIAL INTERFACE F (CSIF)

#### 16.1 Features

- O Transfer rate: 6.25 Mbps (using internal clock)

- O Master mode and slave mode selectable

- O Interrupt request signals: 3

- Reception end interrupt request signal (INTCFnR): This signal is generated when reception is enabled and receive data is transferred from the shift register to the CSIFn receive data register (CFnRX) after completion of a serial transfer.

Transmission enable interrupt request signal (INTCFnT): This signal is generated when transmission is enabled in the continuous transmission or continuous transmission/reception mode and transmission data is transferred from the CSIFn transmit data register (CFnTX) to the shift register.

Reception error interrupt request signal (INTCFnRE): Reception error interrupt request signal (INTCFnRE):

- O Serial clock and data phase switchable

- O 3-wire serial interface, transfer data length selectable in 1-bit units between 8 and 16 bits

- O Transfer data MSB-first/LSB-first switchable

- O 3-wire transfer SOFn: Serial data output

SIFn: Serial data input

SCKFn: Serial clock I/O

Transmission mode, reception mode, and transmission/reception mode specifiable

- O Double buffer for both transmission and reception

- O Overrun error detection

**Remark** n = 0 to 2

# 17.7 I<sup>2</sup>C Interrupt Request Signals (INTIIC)

The following shows the value of the IICS0 register at the INTIIC interrupt request signal generation timing and at the INTIIC signal timing.

| Remark | ST:         | Start condition                  |

|--------|-------------|----------------------------------|

|        | AD6 to AD0: | Address                          |

|        | R/W:        | Transfer direction specification |

|        | ACK:        | Acknowledge                      |

|        | D7 to D0:   | Data                             |

|        | SP:         | Stop condition                   |

# CHAPTER 18 DMA (DMA CONTROLLER)

The V850E/IG4 and V850E/IH4 include a direct memory access (DMA) controller (DMAC) that executes and controls DMA transfer.

The DMAC controls data transfer between the internal RAM and on-chip peripheral I/O based on interrupt requests issued by the peripheral I/O (serial interface, timer, A/D converter, interrupts from an external input pin), or DMA transfer requests triggered by software.

## 18.1 Features

- 7 independent DMA channels

- Transfer unit: 8/16/32 bits

- Maximum transfer count: 4096

- Transfer type: Two-cycle transfer

- Two transfer modes

- Single transfer mode

- Single-step transfer mode

- Transfer request

- Request by interrupts from on-chip peripheral I/O (serial interface, timer, A/D converter) or interrupts from an external input pin

- Requests triggered by software

- Transfer sources and destinations

- Internal RAM ↔ on-chip peripheral I/O

- Next address setting function

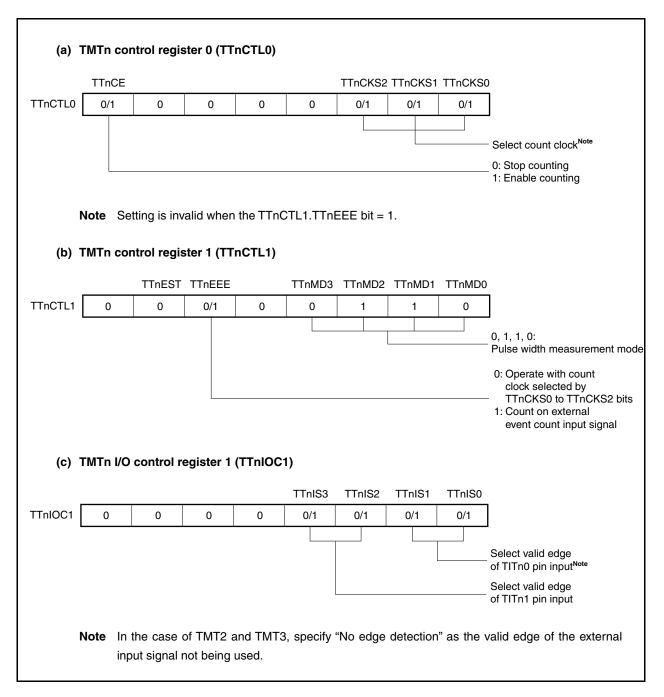

## 19.3.2 Return processing

Execution is returned from non-maskable interrupt servicing by using the RETI instruction.

When the RETI instruction is executed, the CPU performs the following processing and transfers control to the address of the return PC.

- <1> Loads the values of the PC and the PSW from EIPC and EIPSW, respectively, because the PSW.EP bit is 0 and the PSW.NP bit is 0.

- <2> Transfers control back to the address of the return PC and PSW.

The processing of the RETI instruction is shown below.

Figure 19-5. RETI Instruction Processing

## (2) Releasing HALT mode by RESET pin input or by WDTRES, LVIRES, or POCRES signal generation The same operation as the normal reset operation is performed.

| Setting of HALT Mode         |                  | Operation Status                                                                                                                                                |  |  |  |  |  |  |

|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Item                         |                  |                                                                                                                                                                 |  |  |  |  |  |  |

| Clock generator, F           | PLL              | Operates                                                                                                                                                        |  |  |  |  |  |  |

| System clock (fxx)           | )                | Supply                                                                                                                                                          |  |  |  |  |  |  |

| CPU                          |                  | Stops operation                                                                                                                                                 |  |  |  |  |  |  |

| DMA                          |                  | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Interrupt controlle          | r                | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Timer                        | TAA0 to TAA2     | Operable                                                                                                                                                        |  |  |  |  |  |  |

|                              | TAB0, TAB1       | Operable                                                                                                                                                        |  |  |  |  |  |  |

| TMT0 to TMT3<br>TMM0 to TMM3 |                  | Operable                                                                                                                                                        |  |  |  |  |  |  |

|                              |                  | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Watchdog timer               |                  | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Serial interface             | CSIF0 to CSIF2   | Operable                                                                                                                                                        |  |  |  |  |  |  |

|                              | UARTA0 to UARTA2 | Operable                                                                                                                                                        |  |  |  |  |  |  |

|                              | UARTB            | Operable                                                                                                                                                        |  |  |  |  |  |  |

|                              | I <sup>2</sup> C | Operable                                                                                                                                                        |  |  |  |  |  |  |

| A/D converters 0             | to 2             | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Clock monitor                |                  | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Low-voltage detect           | ctor             | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Power-on-clear ci            | rcuit            | Operable                                                                                                                                                        |  |  |  |  |  |  |

| Port function                |                  | Retains status before HALT mode was set.                                                                                                                        |  |  |  |  |  |  |

| Internal data                |                  | The CPU registers, statuses, data, and all other internal data such as the contents of the internal RAM are retained as they were before the HALT mode was set. |  |  |  |  |  |  |

#### Table 20-3. Operation Status in HALT Mode

## 21.2 Control Register

#### (1) Reset source flag register (RESF)

The RESF register is an 8-bit register that indicates occurrence of a reset request from the watchdog timer (WDT) or low-voltage detector (LVI).

The WDTRF or LVIRF bit of this register is set to 1 when the internal reset source signal from WDT or LVI is asserted. The WDTRF or LVIRF bit is cleared by a reset signal (the one generated by inputting the RESET pin, the POCRES signal generated by the power-on-clear circuit (POC), or the forced reset signal generated by the on-chip debug function), a bit manipulation instruction, or a store instruction (writing 0 to the WDTRF or LVIRF bit).

The RESF register is a special register and can be written only in a combination of specific sequences (see **3.4.8 Special registers**).

This register can be read or written in 8-bit or 1-bit units. However, bits 0 and 4 can only be cleared (0) by writing.

This register is set to 00H by RESET pin input and reset by the power-on-clear circuit (POC). This register is set to 00H by RESET pin input, a reset by the power-on-clear circuit (POC), or a forced reset by the on-chip debug function. For details on reset conflict, see **Cautions** on the next page.

## CHAPTER 23 POWER-ON CLEAR CIRCUIT

## 23.1 Function

Functions of the power-on-clear circuit (POC) are shown below.

- Generates a reset signal (POCRES) upon power application.

- Compares the supply voltage (V850E/IG4: EVDD0, EVDD1, EVDD2, V850E/IH4: FVDD) and detection voltage (VPOC0), and generates a reset signal when the supply voltage drops below the detection voltage (detection voltage (VPOC0): 3.7 V ±0.2 V).

- **Remark** The V850E/IG4 and V850E/IH4 have the reset source flag register (RESF) that indicates generation of a reset signal (WDTRES) by watchdog timer overflow and a reset signal (LVIRES) by low-voltage detector (LVI).

The RESF register is not cleared to 00H when a reset signal (WDTRES or LVIRES) is generated, and its flag corresponding to the reset source is set to 1.

The RESF register is cleared (00H) when a reset signal (POCRES) by power-on-clear circuit (POC) is generated.

For details of the RESF register, see CHAPTER 21 RESET FUNCTIONS.

| Symbol   | Name                                        | Unit  | Page |

|----------|---------------------------------------------|-------|------|

| DSAR2    | DMA source address register 2               | DMAC  | 954  |

| DSAR2H   | DMA source address register 2H              | DMAC  | 954  |

| DSAR2L   | DMA source address register 2L              | DMAC  | 954  |

| DSAR3    | DMA source address register 3               | DMAC  | 954  |

| DSAR3H   | DMA source address register 3H              | DMAC  | 954  |

| DSAR3L   | DMA source address register 3L              | DMAC  | 954  |

| DSAR4    | DMA source address register 4               | DMAC  | 954  |

| DSAR4H   | DMA source address register 4H              | DMAC  | 954  |

| DSAR4L   | DMA source address register 4L              | DMAC  | 954  |

| DSAR5    | DMA source address register 5               | DMAC  | 954  |

| DSAR5H   | DMA source address register 5H              | DMAC  | 954  |

| DSAR5L   | DMA source address register 5L              | DMAC  | 954  |

| DSAR6    | DMA source address register 6               | DMAC  | 954  |

| DSAR6H   | DMA source address register 6H              | DMAC  | 954  |

| DSAR6L   | DMA source address register 6L              | DMAC  | 954  |

| DTCR0    | DMA transfer times specification register 0 | DMAC  | 957  |

| DTCR1    | DMA transfer times specification register 1 | DMAC  | 957  |

| DTCR2    | DMA transfer times specification register 2 | DMAC  | 957  |

| DTCR3    | DMA transfer times specification register 3 | DMAC  | 957  |

| DTCR4    | DMA transfer times specification register 4 | DMAC  | 957  |

| DTCR5    | DMA transfer times specification register 5 | DMAC  | 957  |

| DTCR6    | DMA transfer times specification register 6 | DMAC  | 957  |

| DTFR0    | DMA trigger factor register 0               | DMAC  | 965  |

| DTFR0H   | DMA trigger factor register 0H              | DMAC  | 965  |

| DTFR0L   | DMA trigger factor register 0L              | DMAC  | 965  |

| DTFR1    | DMA trigger factor register 1               | DMAC  | 965  |

| DTFR1H   | DMA trigger factor register 1H              | DMAC  | 965  |

| DTFR1L   | DMA trigger factor register 1L              | DMAC  | 965  |

| DTFR2    | DMA trigger factor register 2               | DMAC  | 965  |

| DTFR2H   | DMA trigger factor register 2H              | DMAC  | 965  |

| DTFR2L   | DMA trigger factor register 2L              | DMAC  | 965  |

| DTFR3    | DMA trigger factor register 3               | DMAC  | 965  |

| DTFR3H   | DMA trigger factor register 3H              | DMAC  | 965  |

| DTFR3L   | DMA trigger factor register 3L              | DMAC  | 965  |

| DTFR4    | DMA trigger factor register 4               | DMAC  | 965  |

| DTFR4H   | DMA trigger factor register 4H              | DMAC  | 965  |

| DTFR4L   | DMA trigger factor register 4L              | DMAC  | 965  |

| DTFR5    | DMA trigger factor register 5               | DMAC  | 965  |

| DTFR5H   | DMA trigger factor register 5H              | DMAC  | 965  |

| DTFR5L   | DMA trigger factor register 5L              | DMAC  | 965  |

| DTFR6    | DMA trigger factor register 6               | DMAC  | 965  |

| DTFR6H   | DMA trigger factor register 6H              | DMAC  | 965  |

| DTFR6L   | DMA trigger factor register 6L              | DMAC  | 965  |

| HZA0CTL0 | High-impedance output control register 00   | Timer | 571  |

|                         |                    |                                                |                                                                                     |                               |             |              |             |    |    |       | (3/ | 6)  |

|-------------------------|--------------------|------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------|-------------|--------------|-------------|----|----|-------|-----|-----|

| Mnemonic                | Operand            | Opcode                                         | Operation                                                                           |                               |             | ecut<br>Cloc |             |    | I  | Flags |     |     |

|                         |                    |                                                |                                                                                     |                               | i           | r            | Ι           | СҮ | ov | S     | Z   | SAT |

| LD.H                    | disp16[reg1],reg2  | rrrrr111001RRRRR<br>dddddddddddddddd<br>Note 8 | adr←GR[reg1]+sign-extend(disp16)<br>GR[reg2]←sign-extend(Load-memory(adr,Halfword)) |                               |             | 1            | Note<br>11  |    |    |       |     |     |

| LDSR                    | reg2,regID         | rrrrr111111RRRRR                               | SR[regID]←GR[reg2]                                                                  | Other than regID = PSW        | 1           | 1            | 1           |    |    |       |     |     |

|                         |                    | 000000000100000<br>Note 12                     |                                                                                     | regID = PSW                   | 1           | 1            | 1           | ×  | ×  | ×     | ×   | ×   |

| LD.HU                   | disp16[reg1],reg2  | rrrrr111111RRRRR<br>dddddddddddddd             | adr-GR[reg1]+sign-extend(disp16)<br>GR[reg2]-zero-extend(Load-memory(adr,Halfword)  |                               |             | 1            | Note<br>11  |    |    |       |     |     |

|                         |                    | Note 8                                         |                                                                                     |                               |             |              |             |    |    |       |     |     |

| LD.W                    | disp16[reg1],reg2  | rrrrr111001RRRRR<br>ddddddddddddddd<br>Note 8  | adr←GR[reg1]+sign-exten<br>GR[reg2]←Load-memory(                                    |                               | 1           | 1            | Note<br>11  |    |    |       |     |     |

| MOV                     | reg1,reg2          | rrrr000000RRRRR                                | GR[reg2]←GR[reg1]                                                                   |                               | 1           | 1            | 1           |    |    |       |     |     |

|                         | imm5,reg2          | rrrrr010000iiiii                               | GR[reg2]←sign-extend(im                                                             | m5)                           | 1           | 1            | 1           |    |    |       |     |     |

|                         | imm32,reg1         | 00000110001RRRRR                               | GR[reg1]←imm32                                                                      |                               |             |              | 2           |    |    |       |     |     |

| MOVEA                   | imm16,reg1,reg2    | rrrrr110001RRRRR                               | GR[reg2]←GR[reg1]+sign                                                              | -extend(imm16)                | 1           | 1            | 1           |    |    |       |     |     |

| MOVHI                   | imm16,reg1,reg2    | rrrr110010RRRRR                                | GR[reg2]←GR[reg1]+(imr                                                              | n16    0 <sup>16</sup> )      | 1           | 1            | 1           |    |    |       |     |     |

| MUL <sup>Note 22</sup>  | reg1,reg2,reg3     | rrrr111111RRRRR<br>wwww01000100000             | GR[reg3] ∥ GR[reg2]←GR                                                              | [reg2]xGR[reg1]               | 1           | 2<br>Note14  | 2           |    |    |       |     |     |

|                         | imm9,reg2,reg3     | rrrrr111111iiii<br>wwww01001IIII00<br>Note 13  | GR[reg3] II GR[reg2]←GR[reg2]xsign-extend(imm9)                                     |                               |             |              | 2           |    |    |       |     |     |

| MULH                    | reg1,reg2          | rrrr000111RRRRR                                | GR[reg2]←GR[reg2] <sup>№™ 6</sup> xG                                                | GR[reg1] <sup>Note 6</sup>    | 1           | 1            | 2           |    |    |       |     |     |

|                         | imm5,reg2          | rrrrr010111iiiii                               | GR[reg2]←GR[reg2] <sup>№te 6</sup> xs                                               |                               | 1           | 1            | 2           |    |    |       |     |     |

| MULHI                   | imm16,reg1,reg2    | rrrrr110111RRRRR                               | GR[reg2]←GR[reg1] <sup>Mos s</sup> ximm16                                           |                               |             |              | 2           |    |    |       |     |     |

| MULU <sup>Note 22</sup> | reg1,reg2,reg3     | rrrrr111111RRRRR<br>wwwww01000100010           | GR[reg3] ∥ GR[reg2]←GR                                                              | [reg2]xGR[reg1]               | 1           | 2<br>Note 14 | 2           |    |    |       |     |     |

|                         | imm9,reg2,reg3     | rrrrr111111iiii<br>wwww01001IIII10<br>Note 13  | GR[reg3] II GR[reg2]←GR[reg2]xzero-extend(imm9)                                     |                               |             |              | 2           |    |    |       |     |     |

| NOP                     |                    | 000000000000000000000000000000000000000        | Pass at least one clock cy                                                          | cle doing nothing.            | 1           | 1            | 1           |    |    |       |     |     |

| NOT                     | reg1,reg2          | rrrr000001RRRRR                                | GR[reg2]←NOT(GR[reg1]]                                                              |                               | 1           | 1            | 1           |    | 0  | ×     | ×   |     |

| NOT1                    | bit#3,disp16[reg1] | 01bbb111110RRRR<br>ddddddddddddddddd           | adr←GR[reg1]+sign-exten<br>Z flag←Not(Load-memory<br>Store-memory-bit(adr,bit#3     | d(disp16)<br>-bit(adr,bit#3)) | 3           | 3            | 3<br>Note 3 |    |    |       | ×   |     |

|                         | reg2,[reg1]        | rrrrr111111RRRRR<br>0000000011100010           | adr←GR[reg1]<br>Z flag←Not(Load-memory<br>Store-memory-bit(adr,reg2                 | -bit(adr,reg2))               | 3<br>Note 3 | 3<br>Note 3  | 3<br>Note 3 |    |    |       | ×   |     |