Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | SCI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 23                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                              |

| Supplier Device Package    | 28-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08rd32cdwe |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Pins and Connections**

### Table 2-2. Signal Properties

| Pin<br>Name     | Dir <sup>(1)</sup> | High Current<br>Pin | Pullup <sup>(2)</sup> | Comments <sup>(3)</sup>                                                                     |

|-----------------|--------------------|---------------------|-----------------------|---------------------------------------------------------------------------------------------|

| V <sub>DD</sub> |                    | _                   | —                     |                                                                                             |

| V <sub>SS</sub> |                    | —                   |                       |                                                                                             |

| XTAL            | 0                  | —                   | _                     | Crystal oscillator output                                                                   |

| EXTAL           | I                  | —                   | _                     | Crystal oscillator input                                                                    |

| IRO             | 0                  | Y                   | _                     | Infrared output                                                                             |

| PTA0/KBI1P0     | I                  | N                   | SWC                   | PTA0 does not have a clamp diode to $V_{DD}\!.$ PTA0 should not be driven above $V_{DD}\!.$ |

| PTA1/KBI1P1     | I/O                | N                   | SWC                   |                                                                                             |

| PTA2/KBI1P2     | I/O                | N                   | SWC                   |                                                                                             |

| PTA3/KBI1P3     | I/O                | N                   | SWC                   |                                                                                             |

| PTA4/KBI1P4     | I/O                | N                   | SWC                   |                                                                                             |

| PTA5/KBI1P5     | I/O                | N                   | SWC                   |                                                                                             |

| PTA6/KBI1P6     | I/O                | N                   | SWC                   |                                                                                             |

| PTA7/KBI1P7     | I/O                | N                   | SWC                   |                                                                                             |

| PTB0/TxD1       | I/O                | Y                   | SWC                   |                                                                                             |

| PTB1/RxD1       | I/O                | Y                   | SWC                   |                                                                                             |

| PTB2            | I/O                | Y                   | SWC                   |                                                                                             |

| PTB3            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                   |

| PTB4            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                   |

| PTB5            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                   |

| PTB6            | I/O                | Y                   | SWC                   | Available only in 32-, 44-, and 48-pin packagess                                            |

| PTB7/TPM1CH1    | I/O                | Y                   | SWC                   |                                                                                             |

| PTC0/KBI2P0     | I/O                | N                   | SWC                   |                                                                                             |

| PTC1/KBI2P1     | I/O                | N                   | SWC                   |                                                                                             |

| PTC2/KBI2P2     | I/O                | N                   | SWC                   |                                                                                             |

| PTC3/KBI2P3     | I/O                | N                   | SWC                   |                                                                                             |

| PTC4/MOSI1      | I/O                | N                   | SWC                   |                                                                                             |

| PTC5/MISO1      | I/O                | N                   | SWC                   |                                                                                             |

| PTC6/SPSCK1     | I/O                | N                   | SWC                   |                                                                                             |

| PTC7/SS1        | I/O                | N                   | SWC                   |                                                                                             |

| PTD0/BKGD/MS    | I/O                | N                   | SWC <sup>(4)</sup>    | Output-only when configured as PTD0 pin. Pullup enabled.                                    |

| PTD1/RESET      | I/O                | N                   | SWC <sup>(3)</sup>    | Output-only when configured as PTD1 pin.                                                    |

#### Memory

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the FLASH if needed (normally through the background debug interface) and verifying that FLASH is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC01:SEC00) to the unsecured state (1:0).

### 4.3 RAM

The MC9S08RC/RD/RE/RG includes static RAM. The locations in RAM below \$0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit-manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on or after wakeup from stop1, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HCS08 resets the stack pointer to \$00FF. In the MC9S08RC/RD/RE/RG, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security," for a detailed description of the security feature.

### 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

Resets, Interrupts, and System Configuration

# 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts based on a multiple of the source clock's period. The RTI has two source clock choices, the external clock input or the RTI's own internal clock. The RTI can be used in run, wait, stop2, and stop3 modes. It is not available in stop1 mode.

In run and wait modes, only the external clock can be used as the RTI's clock source. In stop2 mode, only the internal RTI clock can be used. In stop3, either the external clock or internal RTI clock can be used. When using the external oscillator in stop3 mode, it must be enabled in stop (OSCSTEN = 1) and configured for low bandwidth operation (RANGE = 0).

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS2:RTIS1:RTIS0) used to select one of seven RTI periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The module can be disabled by writing 0:0:0 to RTIS2:RTIS1:RTIS0 in which case the clock source input is disabled and no interrupts will be generated. See Section 5.8.6, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

# 5.8 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and five 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

### 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes two unimplemented bits that always read 0, four read/write bits, one read-only status bit, and one write-only bit. These bits are used to configure the IRQ function, report status, and acknowledge IRQ events.

#### Parallel Input/Output

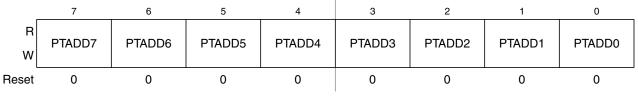

### Figure 6-8. Data Direction for Port A (PTADD)

#### Table 6-3. PTADD Field Descriptions

| Field             | Description                                                                                                                                                                     |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0<br>PTADD[7:0] | ata Direction for Port A Bits — These read/write bits control the direction of port A pins and what is read for TAD reads.                                                      |  |  |  |  |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port A bit n and PTAD reads return the contents of PTADn.</li> </ol> |  |  |  |  |

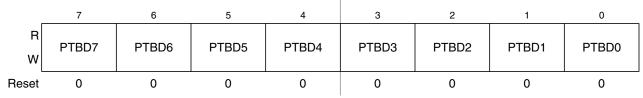

### 6.6.2 Port B Registers (PTBD, PTBPE, and PTBDD)

Port B pins used as general-purpose I/O pins are controlled by the port B data (PTBD), data direction (PTBDD), and pullup enable (PTBPE) registers.

Figure 6-9. Port B Data Register (PTBD)

### Table 6-4. PTBD Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out on the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

## 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

### 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at \$FFFE and \$FFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

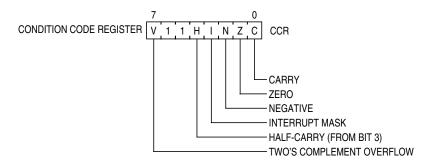

### 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1/D.

Figure 7-2. Condition Code Register

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

- IX = 16-bit indexed no offset

- IX+ = 16-bit indexed no offset, post increment (CBEQ and MOV only)

- IX1 = 16-bit indexed with 8-bit offset from H:X

- IX1+ = 16-bit indexed with 8-bit offset, post increment (CBEQ only)

- IX2 = 16-bit indexed with 16-bit offset from H:X

- REL = 8-bit relative offset

- SP1 = Stack pointer with 8-bit offset

- SP2 = Stack pointer with 16-bit offset

### Table 7-2. HCS08 Instruction Set Summary (Sheet 1 of 7)

| Source                                                                                                               | Operation                                                  | Description                                                          |   |   | Eff<br>on ( |   | - |   | 'ess<br>de                                          | ode                                | and                                 | ycles <sup>1</sup>      |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|---|---|-------------|---|---|---|-----------------------------------------------------|------------------------------------|-------------------------------------|-------------------------|

| Form                                                                                                                 | Operation                                                  | Description                                                          | v | н | I           | N | z | с | Address<br>Mode                                     | Opcode                             | Operand                             | Bus Cycles <sup>1</sup> |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC oprx8,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry                                             | A ← (A) + (M) + (C)                                                  |   |   | _           |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D9<br>E9<br>F9<br>9ED9<br>9EE9     | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP      | Add without Carry                                          | A ← (A) + (M)                                                        |   |   | -           |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | BB<br>CB                           | hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 3 5 4         |

| AIS # <i>opr8i</i>                                                                                                   | Add Immediate Value<br>(Signed) to Stack Pointer           | $SP \leftarrow (SP) + (M)$<br>M is sign extended to a 16-bit value   | - | - | -           | - | - | - | IMM                                                 | A7                                 | ii                                  | 2                       |

| AIX #opr8i                                                                                                           | Add Immediate Value<br>(Signed) to Index<br>Register (H:X) | $H:X \leftarrow (H:X) + (M)$<br>M is sign extended to a 16-bit value | - | - | -           | - | - | - | IMM                                                 | AF                                 | ii                                  | 2                       |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP      | Logical AND                                                | A ← (A) & (M)                                                        | 0 | _ | _           |   |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D4                                 | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL ,X<br>ASL oprx8,SP                                         | Arithmetic Shift Left<br>(Same as LSL)                     | C - 0 b7 b0                                                          |   | _ | _           |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68 | ff                                  | 5<br>1<br>5<br>4<br>6   |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                                   | Arithmetic Shift Right                                     |                                                                      |   | _ | _           |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37<br>47<br>57<br>67<br>77<br>9E67 | ff<br>ff                            | 5<br>1<br>5<br>4<br>6   |

| BCC rel                                                                                                              | Branch if Carry Bit Clear                                  | Branch if (C) = 0                                                    | - | - | -           | - | - | - | REL                                                 | 24                                 | rr                                  | 3                       |

Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

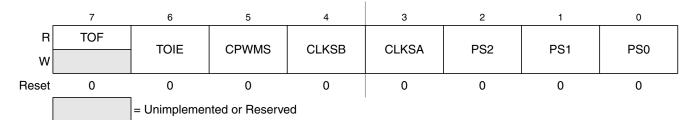

### 10.7.1 Timer Status and Control Register (TPM1SC)

TPM1SC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

### Figure 10-5. Timer Status and Control Register (TPM1SC)

#### Table 10-1. TPM1SC Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to \$0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.         0 TOF interrupts inhibited (use software polling)         1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All TPM1 channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPM1 channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table 10-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 10-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Timer/PWM (TPM)

In input capture mode, reading either byte (TPM1CnVH or TPM1CnVL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This latching mechanism also resets (becomes unlatched) when the TPM1CnSC register is written.

In output compare or PWM modes, writing to either byte (TPM1CnVH or TPM1CnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPM1CnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

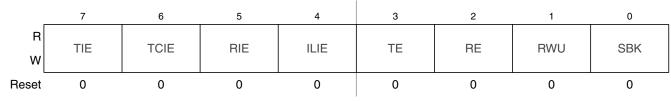

## 12.2.3 SCI Control Register 2 (SCI1C2)

This register can be read or written at any time.

### Figure 12-6. SCI Control Register 2 (SCI1C2)

### Table 12-4. SCI1C2 Register Field Descriptions

| Field     | Description                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)         0       Hardware interrupts from TDRE disabled (use polling).         1       Hardware interrupt requested when TDRE flag is 1.        |

| 6<br>TCIE | Transmission Complete Interrupt Enable (for TC)         0       Hardware interrupt requested when TC flag is 1.         1       Hardware interrupts from TC disabled (use polling). |

| 5<br>RIE  | Receiver Interrupt Enable (for RDRF)         0       Hardware interrupts from RDRF disabled (use polling).         1       Hardware interrupt requested when RDRF flag is 1.        |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)         0       Hardware interrupts from IDLE disabled (use polling).         1       Hardware interrupt requested when IDLE flag is 1.       |

| 3<br>TE   | Transmitter Enable001111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                                       |

| 2<br>RE   | <ul> <li>Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin.</li> <li>Receiver off.</li> <li>Receiver on.</li> </ul>       |

#### Table 12-4. SCI1C2 Register Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWU | <ul> <li>Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 12.3.3.2, "Receiver Wakeup Operation," for more details.</li> <li>0 Normal SCI receiver operation.</li> <li>1 SCI receiver in standby waiting for wakeup condition.</li> </ul> |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 12.3.2.1, "Send Break and Queued Idle," for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                     |

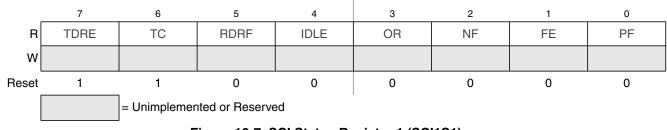

### 12.2.4 SCI Status Register 1 (SCI1S1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

### Figure 12-7. SCI Status Register 1 (SCI1S1)

#### Table 12-5. SCI1S1 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set immediately after reset and when a transmit data value<br>transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To<br>clear TDRE, read SCI1S1 with TDRE = 1 and then write to the SCI data register (SCI1D).0Transmit data register (buffer) full.<br>11Transmit data register (buffer) empty.                                                                                                                                                                                                                          |

| 6<br>TC   | <ul> <li>Transmission Complete Flag — TC is set immediately after reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.</li> <li>0 Transmitter active (sending data, a preamble, or a break).</li> <li>1 Transmitter idle (transmission activity complete).</li> <li>TC is cleared automatically by reading SCI1S1 with TC = 1 and then doing one of the following three things: <ul> <li>Write to the SCI data register (SCI1D) to transmit new data</li> <li>Queue a preamble by changing TE from 0 to 1</li> <li>Queue a break character by writing 1 to SBK in SCI1C2</li> </ul> </li> </ul> |

has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCI1D. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 12.3.4, "Interrupts and Status Flags," for more details about flag clearing.

### 12.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD1 serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

### 12.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCI1C2. When RWU = 1, it inhibits setting of the status flags associated with the receiver, thus eliminating the software overhead for handling the unimportant message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

## 14.4 Functional Description

The analog comparator can be used to compare two analog input voltages applied to ACMP1– and ACMP1+; or it can be used to compare an analog input voltage applied to ACMP1– with an internal bandgap reference voltage. The ACBGS bit is used to select the mode of operation. The comparator output is high when the non-inverting input is greater than the inverting input, and is low when the non-inverting input is less than the inverting input. The ACMOD0 and ACMOD1 bits are used to select the condition that will cause the ACF bit to be set. The ACF bit can be set on a rising edge of the comparator output, a falling edge of the comparator output, or either a rising or a falling edge. The comparator output can be read directly through the ACO bit.

### 14.4.1 Interrupts

The ACMP module is capable of generating an interrupt on a compare event. The interrupt request is asserted when both the ACIE bit and the ACF bit are set. The interrupt is deasserted by clearing either the ACIE bit or the ACF bit. The ACIE bit is cleared by writing a 0 and the ACF bit is cleared by writing a 1.

### 14.4.2 Wait Mode Operation

During wait mode the ACMP, if enabled, will continue to operate normally. Also, if enabled, the interrupt can wake up the MCU.

### 14.4.3 Stop Mode Operation

During stop mode, clocks to the ACMP module are halted. The ACMP comparator circuit will enter a low power state. No compare operation will occur while in stop mode.

In stop1 and stop2 modes, the ACMP module will be in its reset state when the MCU recovers from the stop condition and must be re-initialized.

In stop3 mode, control and status register information is maintained and upon recovery normal ACMP function is available to the user.

### 14.4.4 Background Mode Operation

When the microcontroller is in active background mode, the ACMP will continue to operate normally.

### 15.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 15-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 15-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

the host must perform ((8 - CNT) - 1) dummy reads of the FIFO to advance it to the first significant entry in the FIFO.

In most trigger modes, the information stored in the FIFO consists of 16-bit change-of-flow addresses. In these cases, read DBGFH then DBGFL to get one coherent word of information out of the FIFO. Reading DBGFL (the low-order byte of the FIFO data port) causes the FIFO to shift so the next word of information is available at the FIFO data port. In the event-only trigger modes (see Section 15.3.5, "Trigger Modes"), 8-bit data information is stored into the FIFO. In these cases, the high-order half of the FIFO (DBGFH) is not used and data is read out of the FIFO by simply reading DBGFL. Each time DBGFL is read, the FIFO is shifted so the next data value is available through the FIFO data port at DBGFL.

In trigger modes where the FIFO is storing change-of-flow addresses, there is a delay between CPU addresses and the input side of the FIFO. Because of this delay, if the trigger event itself is a change-of-flow address or a change-of-flow address appears during the next two bus cycles after a trigger event starts the FIFO, it will not be saved into the FIFO. In the case of an end-trace, if the trigger event is a change-of-flow, it will be saved as the last change-of-flow entry for that debug run.

The FIFO can also be used to generate a profile of executed instruction addresses when the debugger is not armed. When ARM = 0, reading DBGFL causes the address of the most-recently fetched opcode to be saved in the FIFO. To use the profiling feature, a host debugger would read addresses out of the FIFO by reading DBGFH then DBGFL at regular periodic intervals. The first eight values would be discarded because they correspond to the eight DBGFL reads needed to initially fill the FIFO. Additional periodic reads of DBGFH and DBGFL return delayed information about executed instructions so the host debugger can develop a profile of executed instruction addresses.

### 15.3.3 Change-of-Flow Information

To minimize the amount of information stored in the FIFO, only information related to instructions that cause a change to the normal sequential execution of instructions is stored. With knowledge of the source and object code program stored in the target system, an external debugger system can reconstruct the path of execution through many instructions from the change-of-flow information stored in the FIFO.

For conditional branch instructions where the branch is taken (branch condition was true), the source address is stored (the address of the conditional branch opcode). Because BRA and BRN instructions are not conditional, these events do not cause change-of-flow information to be stored in the FIFO.

Indirect JMP and JSR instructions use the current contents of the H:X index register pair to determine the destination address, so the debug system stores the run-time destination address for any indirect JMP or JSR. For interrupts, RTI, or RTS, the destination address is stored in the FIFO as change-of-flow information.

### 15.3.4 Tag vs. Force Breakpoints and Triggers

Tagging is a term that refers to identifying an instruction opcode as it is fetched into the instruction queue, but not taking any other action until and unless that instruction is actually executed by the CPU. This distinction is important because any change-of-flow from a jump, branch, subroutine call, or interrupt causes some instructions that have been fetched into the instruction queue to be thrown away without being executed.

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

**Development Support**

## A.4 Electrostatic Discharge (ESD) Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the applicable device data sheet at room temperature followed by hot temperature, unless specified otherwise in the device data sheet.

| Table A-3. ESD Prote | ection Chara | acteristics |

|----------------------|--------------|-------------|

| Paramatar            | Symbol       | Value       |

| Parameter                                                        | Symbol             | Value | Unit |

|------------------------------------------------------------------|--------------------|-------|------|

| ESD Target for Machine Model (MM)<br>MM circuit description      | V <sub>THMM</sub>  | 200   | V    |

| ESD Target for Human Body Model (HBM)<br>HBM circuit description | V <sub>THHBM</sub> | 2000  | V    |

## A.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Table A-4. DC Characteristics (Te | emperature Range = 0 to 70°C Ambient) |

|-----------------------------------|---------------------------------------|

|-----------------------------------|---------------------------------------|

| Parameter                                            | Symbol             | Min  | Typical | Max  | Unit |

|------------------------------------------------------|--------------------|------|---------|------|------|

| Low-voltage detection threshold                      | V <sub>LVD</sub>   | 1.82 | 1.875   | 1.90 | V    |

| Power on reset (POR) voltage                         | V <sub>POR</sub>   | 0.8  | 0.9     | 1.1  | V    |

| Maximum low-voltage safe state re-arm <sup>(1)</sup> | V <sub>REARM</sub> | 1.90 | 2.24    | 2.60 | V    |

1. If SAFE bit is set, V<sub>DD</sub> must be above re-arm voltage to allow MCU to accept interrupts, refer to Section 5.6, "Low-Voltage Detect (LVD) System."

| Parameter                                                                                | Symbol           | Min                                  | Typical      | Max          | Unit |

|------------------------------------------------------------------------------------------|------------------|--------------------------------------|--------------|--------------|------|

| Supply voltage (run, wait and stop modes.) $0 < f_{Bus} < 8 MHz$                         | V <sub>DD</sub>  | 1.8                                  |              | 3.6          | V    |

| Minimum RAM retention supply voltage applied to $V_{DD}$                                 | V <sub>RAM</sub> | V <sub>POR</sub> <sup>(1), (2)</sup> |              | —            | V    |

| Low-voltage detection threshold<br>(V <sub>DD</sub> falling)<br>(V <sub>DD</sub> rising) | V <sub>LVD</sub> | 1.82<br>1.92                         | 1.88<br>1.96 | 1.93<br>2.01 | V    |

| Low-voltage warning threshold<br>(V <sub>DD</sub> falling)<br>(V <sub>DD</sub> rising)   | V <sub>LVW</sub> | 2.07<br>2.16                         | 2.13<br>2.21 | 2.18<br>2.26 | V    |

| Power on reset (POR) voltage                                                             | V <sub>POR</sub> | 0.85                                 | 1.0          | 1.2          | V    |

#### How to Reach Us:

#### USA/Europe/Locations not listed:

Freescale Semiconductor Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor H.K. Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong 852-26668334

Learn More: For more information about Freescale Semiconductor products, please visit http://www.freescale.com

MC9S08RG60/D Rev. 1.11 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.