Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI                                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                              |

| Supplier Device Package    | 28-PDIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08rd32cpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Section Number |           | mber Title                                             | Page |

|----------------|-----------|--------------------------------------------------------|------|

|                |           | Chapter 9<br>Keyboard Interrupt (S08KBIV1)             |      |

| 9.1            | Introduct | ion                                                    | 123  |

| 9.2            | KBI Bloo  | ck Diagram                                             | 125  |

| 9.3            | Keyboard  | d Interrupt (KBI) Module                               | 125  |

|                | 9.3.1     | Pin Enables                                            | 125  |

|                | 9.3.2     | Edge and Level Sensitivity                             | 125  |

|                | 9.3.3     | KBI Interrupt Controls                                 | 126  |

| 9.4            | KBI Reg   | isters and Control Bits                                | 126  |

|                | 9.4.1     | KBI x Status and Control Register (KBIxSC)             | 127  |

|                | 9.4.2     | KBI x Pin Enable Register (KBIxPE)                     | 128  |

|                |           | Chapter 10                                             |      |

| 10.1           | T., 4.,   | Timer/PWM Module (S08TPMV1)                            | 120  |

|                |           | ion                                                    |      |

|                |           | oals Diagram                                           |      |

|                |           | ock Diagram                                            |      |

| 10.4           | 10.4.1    | riptionsExternal TPM Clock Sources                     |      |

|                |           | TPM1CHn — TPM1 Channel n I/O Pins                      |      |

| 10.5           |           | al Description                                         |      |

| 10.5           | 10.5.1    | Counter                                                |      |

|                | 10.5.1    | Channel Mode Selection                                 |      |

|                | 10.5.2    | 10.5.2.1 Input Capture Mode                            |      |

|                |           | 10.5.2.2 Output Compare Mode                           |      |

|                |           | 10.5.2.3 Edge-Aligned PWM Mode                         |      |

|                | 10.5.3    | Center-Aligned PWM Mode                                |      |

| 10.6           |           | errupts                                                |      |

| 10.0           | 10.6.1    | Clearing Timer Interrupt Flags                         |      |

|                | 10.6.2    | Timer Overflow Interrupt Description                   |      |

|                | 10.6.3    | Channel Event Interrupt Description                    |      |

|                | 10.6.4    | PWM End-of-Duty-Cycle Events                           |      |

| 10.7           |           | gisters and Control Bits                               |      |

|                | 10.7.1    | Timer Status and Control Register (TPM1SC)             |      |

|                | 10.7.2    | Timer Counter Registers (TPM1CNTH:TPM1CNTL)            |      |

|                | 10.7.3    | Timer Counter Modulo Registers (TPM1MODH:TPM1MODL)     | 141  |

|                | 10.7.4    | Timer Channel n Status and Control Register (TPM1CnSC) |      |

|                | 10.7.5    | Timer Channel Value Registers (TPM1CnVH:TPM1CnVL)      |      |

| Section Number |                  | imber Title                                           | Page |

|----------------|------------------|-------------------------------------------------------|------|

|                |                  | Chapter 11 Serial Communications Interface (S08SCIV1) |      |

| 11.1           | Introduc         | tion                                                  | 145  |

|                |                  |                                                       |      |

|                |                  | Chapter 12                                            |      |

| 10.1           | T., 4.,          | Serial Communications Interface (S08SCIV1)            | 1.47 |

| 12.1           |                  | tion                                                  |      |

|                | 12.1.1<br>12.1.2 | Features                                              |      |

|                | 12.1.2           | Block Diagram                                         |      |

| 12.2           |                  | Definition                                            |      |

| 12,2           | 12.2.1           | SCI Baud Rate Registers (SCI1BDH, SCI1BHL)            |      |

|                | 12.2.2           | SCI Control Register 1 (SCI1C1)                       |      |

|                | 12.2.3           | SCI Control Register 2 (SCI1C2)                       |      |

|                | 12.2.4           | SCI Status Register 1 (SCI1S1)                        |      |

|                | 12.2.5           | SCI Status Register 2 (SCI1S2)                        |      |

|                | 12.2.6           | SCI Control Register 3 (SCI1C3)                       |      |

|                | 12.2.7           | SCI Data Register (SCI1D)                             |      |

| 12.3           | Function         | al Description                                        |      |

|                | 12.3.1           | Baud Rate Generation                                  |      |

|                | 12.3.2           | Transmitter Functional Description                    | 157  |

|                |                  | 12.3.2.1 Send Break and Queued Idle                   | 158  |

|                | 12.3.3           | Receiver Functional Description                       |      |

|                |                  | 12.3.3.1 Data Sampling Technique                      |      |

|                |                  | 12.3.3.2 Receiver Wakeup Operation                    | 159  |

|                | 12.3.4           | Interrupts and Status Flags                           |      |

|                | 12.3.5           | Additional SCI Functions                              |      |

|                |                  | 12.3.5.1 8- and 9-Bit Data Modes                      |      |

|                |                  | 12.3.5.2 Stop Mode Operation                          |      |

|                |                  | 12.3.5.3 Loop Mode                                    |      |

|                |                  | 12.3.5.4 Single-Wire Operation                        | 162  |

|                |                  | Chapter 13                                            |      |

|                |                  | Serial Peripheral Interface (S08SPIV3)                |      |

| 13 1           | Fanturas         | Serial Peripheral Interface (3003F1V3)                | 164  |

|                |                  | iagrams                                               |      |

| 13.4           | 13.2.1           |                                                       |      |

|                | 13.2.1           | SPI Module Block Diagram                              |      |

|                | 13.2.3           | SPI Baud Rate Generation                              |      |

| 13.3           |                  | al Description                                        |      |

| 10.0           | 13.3.1           | SPI Clock Formats                                     |      |

|                | 13.3.2           |                                                       |      |

|                |                  | 13.3.2.1 SPSCK1 — SPI Serial Clock                    |      |

|                |                  | 13.3.2.2 MOSI1 — Master Data Out, Slave Data In       |      |

|                |                  |                                                       |      |

|                |                  | MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11               |      |

#### **Table 2-2. Signal Properties (continued)**

| Pin<br>Name  | Dir <sup>(1)</sup> | High Current<br>Pin | Pullup <sup>(2)</sup> | Comments <sup>(3)</sup>                          |

|--------------|--------------------|---------------------|-----------------------|--------------------------------------------------|

| PTD2/IRQ     | I/O                | N                   | SWC <sup>(5)</sup>    | Available only in 32-, 44-, and 48-pin packagess |

| PTD3         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTD4/ACMP1-  | I/O                | N                   | SWC                   | Available only in 32-, 44-, and 48-pin packagess |

| PTD5/ACMP1+  | I/O                | N                   | SWC                   | Available only in 32-, 44-, and 48-pin packagess |

| PTD6/TPM1CH0 | I/O                | N                   | SWC                   |                                                  |

| PTE0         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE1         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE2         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE3         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE4         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE5         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE6         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

| PTE7         | I/O                | N                   | SWC                   | Available only in 44- and 48-pin packages        |

- 1. Unless otherwise indicated, all digital inputs have input hysteresis.

- 2. SWC is software-controlled pullup resistor, the register is associated with the respective port.

- 3. Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unconnected pins to outputs so the pins do not float.

- 4. When these pins are configured as RESET or BKGD/MS pullup device is enabled.

- 5. When configured for the IRQ function, this pin will have a pullup device enabled when the IRQ is set for falling edge detection and a pulldown device enabled when the IRQ is set for rising edge detection.

Resets, Interrupts, and System Configuration

## 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts based on a multiple of the source clock's period. The RTI has two source clock choices, the external clock input or the RTI's own internal clock. The RTI can be used in run, wait, stop2, and stop3 modes. It is not available in stop1 mode.

In run and wait modes, only the external clock can be used as the RTI's clock source. In stop2 mode, only the internal RTI clock can be used. In stop3, either the external clock or internal RTI clock can be used. When using the external oscillator in stop3 mode, it must be enabled in stop (OSCSTEN = 1) and configured for low bandwidth operation (RANGE = 0).

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS2:RTIS1:RTIS0) used to select one of seven RTI periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The module can be disabled by writing 0:0:0 to RTIS2:RTIS1:RTIS0 in which case the clock source input is disabled and no interrupts will be generated. See Section 5.8.6, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

# 5.8 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and five 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

## 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes two unimplemented bits that always read 0, four read/write bits, one read-only status bit, and one write-only bit. These bits are used to configure the IRQ function, report status, and acknowledge IRQ events.

Parallel Input/Output

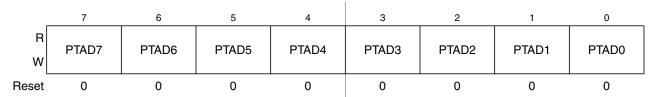

# 6.6.1 Port A Registers (PTAD, PTAPE, and PTADD)

Port A pins used as general-purpose I/O pins are controlled by the port A data (PTAD), data direction (PTADD), and pullup enable (PTAPE) registers.

Figure 6-6. Port A Data Register (PTAD)

**Table 6-1. PTAD Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTAD[7:0] | Port A Data Register Bits — For port A pins that are inputs, reads of this register return the logic level on the pin. For port A pins that are configured as outputs, reads of this register return the last value written to this register.  Writes are latched into all bits of this register. For port A pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.  Reset forces PTAD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

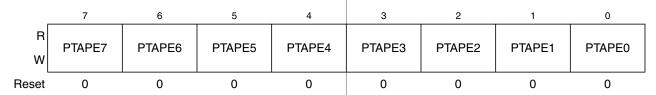

Figure 6-7. Pullup Enable for Port A (PTAPE)

**Table 6-2. PTAPE Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTAPE[7:0] | Pullup Enable for Port A Bits — For port A pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled provided the corresponding PTADDn is a logic 0. For port A pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled. When any of bits 7 through 4 of port A are enabled as KBI inputs and are configured to detect rising edges/high levels, the pullup enable bits enable pulldown rather than pullup devices.  0 Internal pullup device disabled.  1 Internal pullup device enabled. |

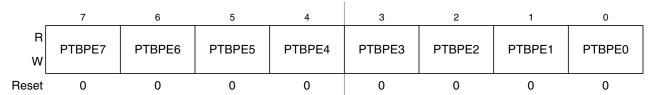

#### Parallel Input/Output

Figure 6-10. Pullup Enable for Port B (PTBPE)

### **Table 6-5. PTBPE Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBPE[7:0] | Pullup Enable for Port B Bits — For port B pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port B pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.  0 Internal pullup device disabled.  1 Internal pullup device enabled. |

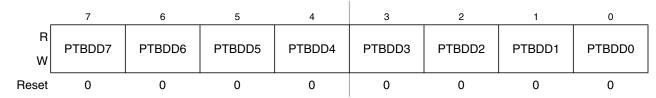

Figure 6-11. Data Direction for Port B (PTBDD)

### **Table 6-6. PTBDD Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDD[7:0] | Data Direction for Port B Bits — These read/write bits control the direction of port B pins and what is read for PTBD reads.  0 Input (output driver disabled) and reads return the pin value.  1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn. |

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

80

Freescale Semiconductor

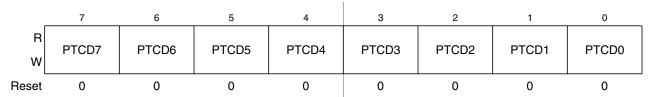

# 6.6.3 Port C Registers (PTCD, PTCPE, and PTCDD)

Port C pins used as general-purpose I/O pins are controlled by the port C data (PTCD), data direction (PTCDD), and pullup enable (PTCPE) registers.

Figure 6-12. Port C Data Register (PTCD)

**Table 6-7. PTCD Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCD[7:0] | Port C Data Register Bits — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register.  Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.  Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

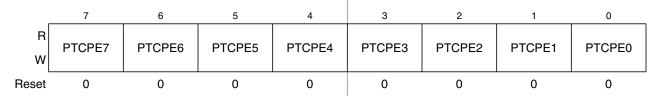

Figure 6-13. Pullup Enable for Port C (PTCPE)

**Table 6-8. PTCPE Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCPE[7:0] | Pullup Enable for Port C Bits — For port C pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port C pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.  0 Internal pullup device disabled.  1 Internal pullup device enabled. |

Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

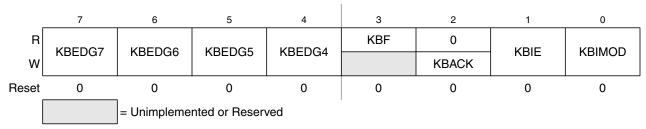

# 9.4.1 KBI x Status and Control Register (KBIxSC)

Figure 9-3. KBI x Status and Control Register (KBIxSC)

Table 9-1. KBIxSC Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4<br>KBEDG[7:4] | Keyboard Edge Select for KBI Port Bits — Each of these read/write bits selects the polarity of the edges and/or levels that are recognized as trigger events on the corresponding KBI port pin when it is configured as a keyboard interrupt input (KBIPEn = 1). Also see the KBIMOD control bit, which determines whether the pin is sensitive to edges-only or edges and levels.  0 Falling edges/low levels.  1 Rising edges/high levels.                                                                                                                                                       |

| 3<br>KBF          | Keyboard Interrupt Flag — This read-only status flag is set whenever the selected edge event has been detected on any of the enabled KBI port pins. This flag is cleared by writing a logic 1 to the KBACK control bit. The flag will remain set if KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level.  0 No KBI interrupt pending.  1 KBI interrupt pending.  KBF can be used as a software pollable flag (KBIE = 0) or it can generate a hardware interrupt request to the CPU (KBIE = 1). KBF must be cleared before entering stop mode. |

| 2<br>KBACK        | <b>Keyboard Interrupt Acknowledge</b> — This write-only bit (reads always return 0) is used to clear the KBF status flag by writing a logic 1 to KBACK. When KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level, KBF is being continuously set so writing 1 to KBACK does not clear the KBF flag.                                                                                                                                                                                                                                            |

| 1<br>KBIE         | Keyboard Interrupt Enable — This read/write control bit determines whether hardware interrupts are generated when the KBF status flag equals 1. When KBIE = 0, no hardware interrupts are generated, but KBF can still be used for software polling.  0 KBF does not generate hardware interrupts (use polling).  1 KBI hardware interrupt requested when KBF = 1.                                                                                                                                                                                                                                 |

| 0<br>KBIMOD       | Keyboard Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. KBI port bits 3 through 0 can detect falling edges-only or falling edges and low levels.  KBI port bits 7 through 4 can be configured to detect either:  Rising edges-only or rising edges and high levels (KBEDGn = 1)  Falling edges-only or falling edges and low levels (KBEDGn = 0)  Edge-only detection.                                                                                                                                                               |

# Chapter 10 Timer/PWM Module (S08TPMV1)

### 10.1 Introduction

The MC9S08RC/RD/RE/RG includes a timer/PWM (TPM) module that supports traditional input capture, output compare, or buffered edge-aligned pulse-width modulation (PWM) on each channel. A control bit in the TPM configures both channels in the timer to operate as center-aligned PWM functions. Timing functions in the TPM are based on a 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications. The MC9S08RC/RD/RE/RG devices do not have a separate fixed internal clock source (XCLK). If the XCLK source is selected using the CLKSA and CLKSB control bits (see Table 10-2), the TPM will use the BUSCLK.

#### 10.2 Features

Timer system features include:

- Two separate channels:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- The TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on both channels

- Clock source to prescaler for the TPM is selectable between the bus clock or an external pin:

- Prescale taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- External clock input shared with TPM1CH0 timer channel pin

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus terminal count interrupt

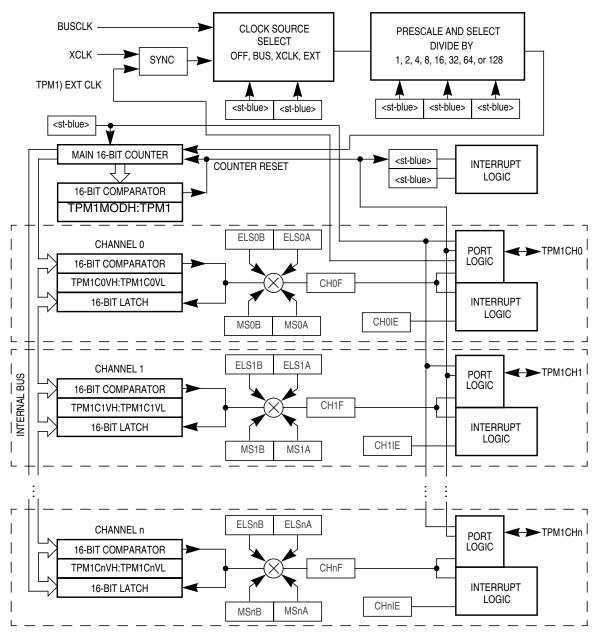

## 10.3 TPM Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPM1CHn where n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information). Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture,

has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCI1D. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 12.3.4, "Interrupts and Status Flags," for more details about flag clearing.

### 12.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD1 serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

## 12.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCI1C2. When RWU = 1, it inhibits setting of the status flags associated with the receiver, thus eliminating the software overhead for handling the unimportant message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

Serial Peripheral Interface (SPI) Module

#### 13.1 **Features**

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

#### 13.2 **Block Diagrams**

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

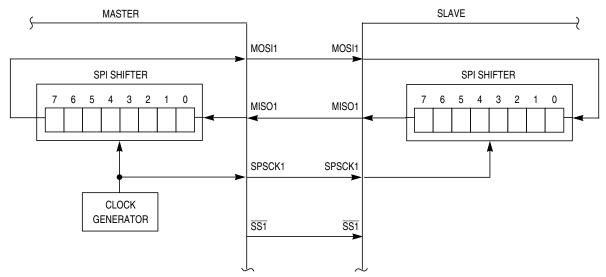

#### 13.2.1 **SPI System Block Diagram**

Figure 13-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI1 pin) to the slave while simultaneously shifting data in (on the MISO1 pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK1 signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS1}$  pin). In this system, the master device has configured its  $\overline{SS1}$  pin as an optional slave select output.

Figure 13-2. SPI System Connections

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11 164 Freescale Semiconductor

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS1}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

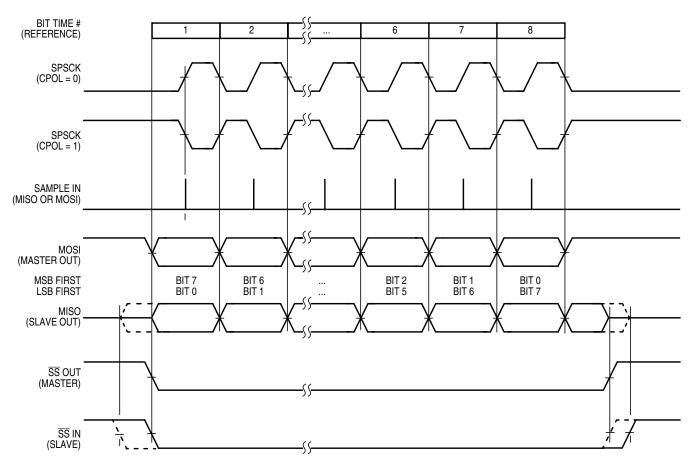

Figure 13-6 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 13-6. SPI Clock Formats (CPHA = 0)

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Analog Comparator (ACMP) Block Description

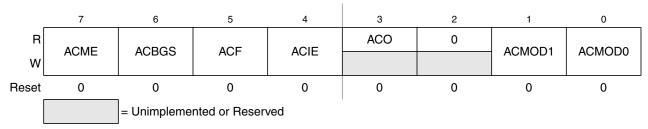

# 14.5 ACMP Status and Control Register (ACMP1SC)

Figure 14-3. ACMP Status and Control Register (ACMP1SC)

**Table 14-1. ACMP1SC Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACME         | Analog Comparator Module Enable — The ACME bit enables the analog comparator module. When the module is not enabled, it remains in a low-power state.  O Analog comparator disabled  1 Analog comparator enabled                                                                                             |

| 6<br>ACBGS        | Analog Comparator Bandgap Select — The ACBGS bit is used to select the internal bandgap as the comparator reference.  0 External pin ACMP1+ selected as comparator non-inverting input 1 Internal bandgap reference selected as comparator non-inverting input                                               |

| 5<br>ACF          | Analog Comparator Flag — The ACF bit is set when a compare event occurs. Compare events are defined by the ACMOD0 and ACMOD1 bits. The ACF bit is cleared by writing a 1 to the bit.  O Compare event has not occurred.  Compare event has occurred.                                                         |

| 4<br>ACIE         | Analog Comparator Interrupt Enable — The ACIE bit enables the interrupt from the ACMP. When this bit is set, an interrupt will be asserted when the ACF bit is set.  0 Interrupt disabled  1 Interrupt enabled                                                                                               |

| 3<br>ACO          | Analog Comparator Output — Reading the ACO bit will return the current value of the analog comparator output. The register bit is reset to 0 and will read as 0 when the analog comparator module is disabled (ACME = 0).                                                                                    |

| 1:0<br>ACMOD[1:0] | Analog Comparator Modes — The ACMOD1 and ACMOD0 bits select the flag setting mode that controls the type of compare event that sets the ACF bit.  O0 Comparator output falling edge  O1 Comparator output rising edge  10 Comparator output falling edge  11 Comparator output either rising or falling edge |

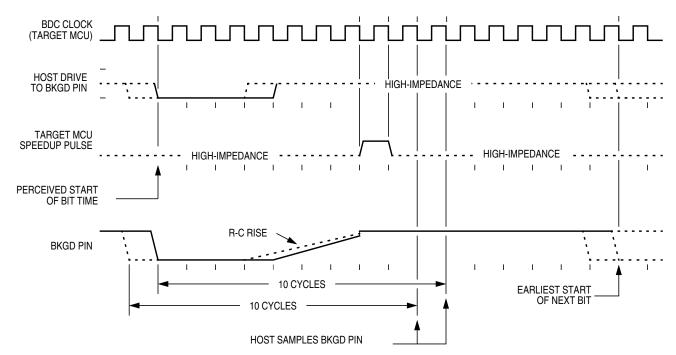

Figure 15-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host should sample the bit level about 10 cycles after it started the bit time.

Figure 15-3. BDC Target-to-Host Serial Bit Timing (Logic 1)

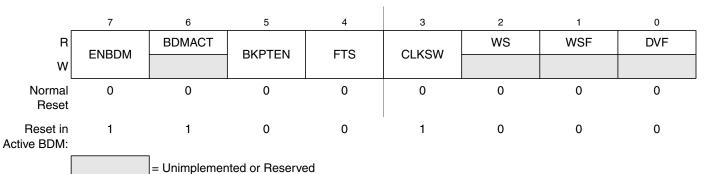

#### **BDC Status and Control Register (BDCSCR)** 15.4.1.1

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

Figure 15-5. BDC Status and Control Register (BDCSCR)

Table 15-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.  0 BDM cannot be made active (non-intrusive commands still allowed)  1 BDM can be made active to allow active background mode commands                                                                                                                                                                                                                                              |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.  0 BDM not active (user application program running)  1 BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5<br>BKPTEN | BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.  0 BDC breakpoint disabled  1 BDC breakpoint enabled                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4<br>FTS    | Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.  O Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction  Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode) |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.  O Alternate BDC clock source  1 MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11 197 Freescale Semiconductor

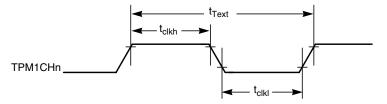

| Function                  | Symbol              | Min | Max                 | Unit             |

|---------------------------|---------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

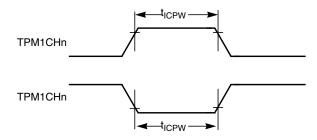

| Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

Figure A-9. Timer External Clock

Figure A-10. Timer Input Capture Pulse

# A.9.3 SPI Timing

Table A-11 and Figure A-11 through Figure A-14 describe the timing requirements for the SPI system.

# MECHANICAL DUTLINES DICTIONARY

| DOCUMENT | ND: 98ASH70 | 029A |

|----------|-------------|------|

| PAGE:    | 873A        |      |

| REV:     | С           |      |

DO NOT SCALE THIS DRAWING

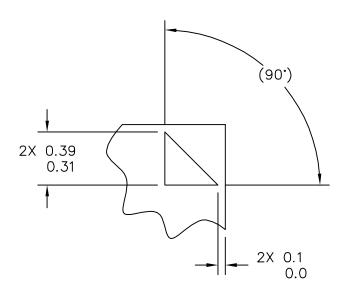

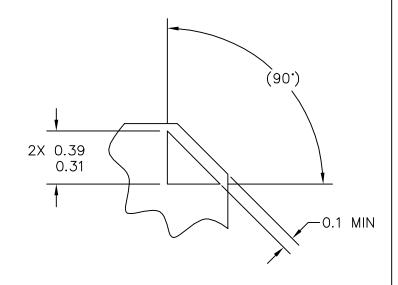

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

3 Datums A, B, and D to be determined at datum plane H.

4. Dimensions to be determined at seating plane datum c.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS

0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING

MOLD MISMATCH.

$\triangle$  exact shape of each corner is optional.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

TITLE:

LOW PROFILE QUAD FLAT PACK (LQFP)

)W PROFILE QUAD FLAT PACK (LQFP) 32 LEAD, 0.8 PITCH (7 X 7 X 1.4) CASE NUMBER: 873A-04

STANDARD: JEDEC MS-026 BBA

PACKAGE CODE: 6300

SHEET:

3 DF **3**

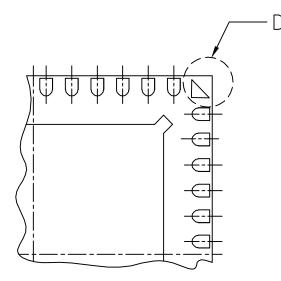

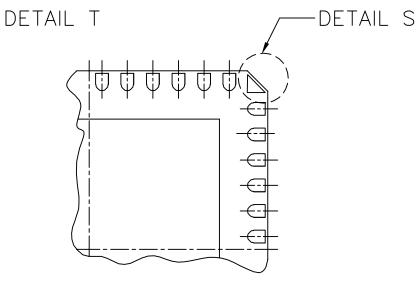

#### MECHANICAL OUTLINES **DICTIONARY**

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARH99048A

PAGE: 1314

REV: D

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION2 PIN 1 BACKSIDE IDENTIFIER OPTION3

DETAIL M

DETAIL T PIN 1 BACKSIDE IDENTIFIER OPTION2

DETAIL S PIN 1 BACKSIDE IDENTIFIER OPTION3

TITLE: THERMALLY ENHANCED QUAD FLAT NON-LEADED PACKAGE (QFN) 48 TERMINAL, 0.5 PITCH (7 X 7 X 1) CASE NUMBER: 1314-03

STANDARD: JEDEC-MO-220 VKKD-2

PACKAGE CODE: 6152 SHEET: 4 OF 5