Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | S08                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                        |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 60KB (60K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 28-PDIP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08rd60pe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pins and Connections**

**Table 2-2. Signal Properties**

| Pin<br>Name     | Dir <sup>(1)</sup> | High Current<br>Pin | Pullup <sup>(2)</sup> | Comments <sup>(3)</sup>                                                                                   |

|-----------------|--------------------|---------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> |                    | _                   | _                     |                                                                                                           |

| V <sub>SS</sub> |                    | _                   | _                     |                                                                                                           |

| XTAL            | 0                  | _                   | _                     | Crystal oscillator output                                                                                 |

| EXTAL           | I                  | _                   | _                     | Crystal oscillator input                                                                                  |

| IRO             | 0                  | Y                   | _                     | Infrared output                                                                                           |

| PTA0/KBI1P0     | I                  | N                   | SWC                   | PTA0 does not have a clamp diode to $\rm V_{\rm DD}$ . PTA0 should not be driven above $\rm V_{\rm DD}$ . |

| PTA1/KBI1P1     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA2/KBI1P2     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA3/KBI1P3     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA4/KBI1P4     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA5/KBI1P5     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA6/KBI1P6     | I/O                | N                   | SWC                   |                                                                                                           |

| PTA7/KBI1P7     | I/O                | N                   | SWC                   |                                                                                                           |

| PTB0/TxD1       | I/O                | Y                   | SWC                   |                                                                                                           |

| PTB1/RxD1       | I/O                | Y                   | SWC                   |                                                                                                           |

| PTB2            | I/O                | Y                   | SWC                   |                                                                                                           |

| PTB3            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                                 |

| PTB4            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                                 |

| PTB5            | I/O                | Y                   | SWC                   | Available only in 44- and 48-pin packages                                                                 |

| PTB6            | I/O                | Y                   | SWC                   | Available only in 32-, 44-, and 48-pin packagess                                                          |

| PTB7/TPM1CH1    | I/O                | Y                   | SWC                   |                                                                                                           |

| PTC0/KBI2P0     | I/O                | N                   | SWC                   |                                                                                                           |

| PTC1/KBI2P1     | I/O                | N                   | SWC                   |                                                                                                           |

| PTC2/KBI2P2     | I/O                | N                   | SWC                   |                                                                                                           |

| PTC3/KBI2P3     | I/O                | N                   | SWC                   |                                                                                                           |

| PTC4/MOSI1      | I/O                | N                   | SWC                   |                                                                                                           |

| PTC5/MISO1      | I/O                | N                   | SWC                   |                                                                                                           |

| PTC6/SPSCK1     | I/O                | N                   | SWC                   |                                                                                                           |

| PTC7/SS1        | I/O                | N                   | SWC                   |                                                                                                           |

| PTD0/BKGD/MS    | I/O                | N                   | SWC <sup>(4)</sup>    | Output-only when configured as PTD0 pin. Pullup enabled.                                                  |

| PTD1/RESET      | I/O                | N                   | SWC <sup>(3)</sup>    | Output-only when configured as PTD1 pin.                                                                  |

# **Chapter 3 Modes of Operation**

#### 3.1 Introduction

The operating modes of the MC9S08RC/RD/RE/RG are described in this section. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

#### 3.2 Features

- Active background mode for code development

- Wait mode:

- CPU shuts down to conserve power

- System clocks running

- Full voltage regulation maintained

- Stop modes:

- System clocks stopped; voltage regulator in standby

- Stop1 Full power down of internal circuits for maximum power savings

- Stop2 Partial power down of internal circuits, RAM remains operational

- Stop3 All internal circuits powered for fast recovery

#### 3.3 Run Mode

This is the normal operating mode for the MC9S08RC/RD/RE/RG. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at \$FFFE:\$FFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip debug module (DBG), provide the means for analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

- When the BKGD/MS pin is low at the rising edge of reset

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

#### Memory

Figure 4-7. FLASH Configuration Register (FCNFG)

**Table 4-8. FCNFG Field Descriptions**

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 5<br>KEYACC | Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."  0 Writes to \$FFB0-\$FFB7 are interpreted as the start of a FLASH programming or erase command.  1 Writes to NVBACKKEY (\$FFB0-\$FFB7) are interpreted as comparison key writes.  Reads of the FLASH return invalid data. |  |  |  |  |  |

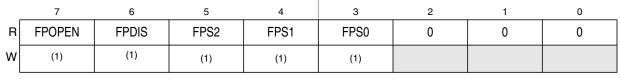

## 4.6.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT is copied from FLASH into FPROT. Bits 0, 1, and 2 are not used and each always reads as 0. This register may be read at any time, but user program writes have no meaning or effect. Background debug commands can write to FPROT at \$1824.

Reset This register is loaded from Unimplemented or Reserved

This register is loaded from nonvolatile location NVPROT during reset.

Figure 4-8. FLASH Protection Register (FPROT)

#### 1. Background commands can be used to change the contents of these bits in FPROT.

**Table 4-9. FPROT Field Descriptions**

| Field           | Description  Open Unprotected FLASH for Program/Erase  0 Entire FLASH memory is block protected (no program or erase allowed).  1 Any FLASH location, not otherwise block protected or secured, may be erased or programmed.                                     |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>FPOPEN     |                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 6<br>FPDIS      | FLASH Protection Disable  0 FLASH block specified by FPS2:FPS0 is block protected (program and erase not allowed).  1 No FLASH block is protected.                                                                                                               |  |  |  |  |  |

| 5:3<br>FPS[2:0] | <b>FLASH Protect Size Selects</b> — When FPDIS = 0, this 3-bit field determines the size of a protected block of FLASH locations at the high address end of the FLASH (see Table 4-10 and Table 4-11). Protected FLASH locations cannot be erased or programmed. |  |  |  |  |  |

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Resets, Interrupts, and System Configuration

The MC9S08RC/RD/RE/RG has these sources for reset:

- Power-on reset (POR)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect

- Illegal address (16K and 8K devices only)

- · Background debug forced reset

- The reset pin ( $\overline{RESET}$ )

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the reset pin is driven low for 34 internal bus cycles where the internal bus frequency is one-half the OSC frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.8.4, "System Options Register (SOPT)," for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>20</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user must write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer must not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it was before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such

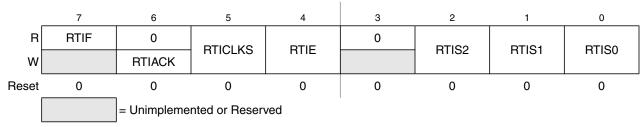

# 5.8.6 System Real-Time Interrupt Status and Control Register (SRTISC)

This register contains one read-only status flag, one write-only acknowledge bit, three read/write delay selects, and three unimplemented bits, which always read 0.

Figure 5-8. System RTI Status and Control Register (SRTISC)

**Table 5-8. SRTISC Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>RTIF        | Real-Time Interrupt Flag — This read-only status bit indicates the periodic wakeup timer has timed out.  O Periodic wakeup timer not timed out.  Periodic wakeup timer timed out.                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 6<br>RTIACK      | Real-Time Interrupt Acknowledge — This write-only bit is used to acknowledge real-time interrupt request (write 1 to clear RTIF). Writing 0 has no meaning or effect. Reads always return 0.                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 5<br>RTICLKS     | Real-Time Interrupt Clock Select — This read/write bit selects the clock source for the real-time interrupt.  O Real-time interrupt request clock source is internal 1-kHz oscillator.  Real-time interrupt request clock source is external clock.                                                                                                                                                                       |  |  |  |  |  |  |

| 4<br>RTIE        | Real-Time Interrupt Enable — This read-write bit enables real-time interrupts.  O Real-time interrupts disabled.  1 Real-time interrupts enabled.                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 2:0<br>RTIS[2:0] | Real-Time Interrupt Period Selects — These read/write bits select the wakeup period for the RTI. One clock source for the real-time interrupt is its own internal clock source, which oscillates with a period of approximately t <sub>RTI</sub> and is independent of other MCU clock sources. Using an external clock source the delays will be crystal frequency divided by value in RTIS2:RTIS1:RTIS0. See Table 5-9. |  |  |  |  |  |  |

Table 5-9. Real-Time Interrupt Period

| RTIS2:RTIS1:RTIS0 | Internal Clock Source <sup>(1)</sup><br>(t <sub>RTI</sub> = 1 ms, Nominal) | External Clock Source <sup>(2)</sup><br>Period = t <sub>ext</sub> |

|-------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|

| 0:0:0             | Disable periodic wakeup timer                                              | Disable periodic wakeup timer                                     |

| 0:0:1             | 8 ms                                                                       | t <sub>ext</sub> x 256                                            |

| 0:1:0             | 32 ms                                                                      | t <sub>ex</sub> x 1024                                            |

| 0:1:1             | 64 ms                                                                      | t <sub>ex</sub> x 2048                                            |

| 1:0:0             | 128 ms                                                                     | t <sub>ex</sub> x 4096                                            |

| 1:0:1             | 256 ms                                                                     | t <sub>ext</sub> x 8192                                           |

| 1:1:0             | 512 ms                                                                     | t <sub>ext</sub> x 16384                                          |

| 1:1:1             | 1.024 s                                                                    | t <sub>ex</sub> x 32768                                           |

<sup>1.</sup> See Table A-9  $t_{\mbox{RTI}}$  in Appendix A, "Electrical Characteristics," for the tolerance on these values.

#### MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

$<sup>2.\</sup> t_{ext}$  is based on the external clock source, resonator, or crystal selected by the ICG configuration. See Table A-9 for details.

of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

# 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

## 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

# 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

# 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

# 7.3.5 Extended Addressing Mode (EXT)

In extended addressing mode, the full 16-bit address of the operand is located in the next two bytes of program memory after the opcode (high byte first).

# 7.3.6 Indexed Addressing Mode

Indexed addressing mode has seven variations including five that use the 16-bit H:X index register pair and two that use the stack pointer as the base reference.

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Table 7-2. HCS08 Instruction Set Summary (Sheet 3 of 7)

| Source                                                                                                           | Onovetter                                 | Description                                                                                                                                                                                                                                                                                                       |   | Effect<br>on CCR |   |   |   |   | ess<br>de                                                                                    | əpc                                      | and                                                                  | /cles <sup>1</sup>                    |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|---|---|---|---|----------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------|---------------------------------------|

| Form                                                                                                             | Operation                                 |                                                                                                                                                                                                                                                                                                                   |   | Н                | I | N | z | С | Address                                                                                      | Opcode                                   | Operand                                                              | Bus Cycle                             |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Clear | Branch if (Mn) = 0                                                                                                                                                                                                                                                                                                |   | _                | _ | _ | _ |   | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 03<br>05<br>07<br>09<br>0B<br>0D         | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 555555555                             |

| BRN rel                                                                                                          | Branch Never                              | Uses 3 Bus Cycles                                                                                                                                                                                                                                                                                                 | - | _                | - | - | - | - | REL                                                                                          | 21                                       | rr                                                                   | 3                                     |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Set   | Branch if (Mn) = 1                                                                                                                                                                                                                                                                                                | _ | _                | _ | - | _ |   | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b6) DIR (b7)             | 02<br>04<br>06<br>08<br>0A<br>0C         | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5555555<br>5555                       |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory                | Mn ← 1                                                                                                                                                                                                                                                                                                            | _ | _                | _ | _ | _ | _ | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b6)                      |                                          | dd<br>dd<br>dd<br>dd<br>dd<br>dd                                     | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |

| BSR rel                                                                                                          | Branch to Subroutine                      | $\begin{array}{c} PC \leftarrow (PC) + 0x0002 \\ push \ (PCL); SP \leftarrow (SP) - 0x0001 \\ push \ (PCH); SP \leftarrow (SP) - 0x0001 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                         | - | -                | - | - | - | - | REL                                                                                          | AD                                       | rr                                                                   | 5                                     |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if Equal               | Branch if (A) = (M) Branch if (A) = (M) Branch if (X) = (M) Branch if (A) = (M) Branch if (A) = (M) Branch if (A) = (M)                                                                                                                                                                                           | _ | _                | _ | _ | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 41<br>51                                 | ii rr<br>ff rr<br>rr                                                 | 5<br>4<br>4<br>5<br>5<br>6            |

| CLC                                                                                                              | Clear Carry Bit                           | C ← 0                                                                                                                                                                                                                                                                                                             | - | _                | - | - | - | 0 | INH                                                                                          | 98                                       |                                                                      | 1                                     |

| CLI                                                                                                              | Clear Interrupt Mask Bit                  | I ← 0                                                                                                                                                                                                                                                                                                             | Ŀ | -                | 0 | - | _ | Ŀ | INH                                                                                          | 9A                                       |                                                                      | 1                                     |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear                                     | $\begin{array}{l} M \leftarrow 0x00 \\ A \leftarrow 0x00 \\ X \leftarrow 0x00 \\ H \leftarrow 0x00 \\ M \leftarrow 0x00 \end{array}$                                                                                          | 0 | _                | _ | 0 | 1 | _ | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                 | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F |                                                                      | 5<br>1<br>1<br>5<br>4<br>6            |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP  | Compare Accumulator with Memory           | (A) – (M)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                                            |   | _                | _ |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                          |                                          | dd<br>hh II<br>ee ff<br>ff                                           | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4  |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                               | Complement<br>(One's Complement)          | $\begin{array}{l} M \leftarrow (\overline{M}) = 0 x FF - (M) \\ A \leftarrow (\underline{A}) = 0 x FF - (A) \\ X \leftarrow (\overline{X}) = 0 x FF - (X) \\ M \leftarrow (\underline{M}) = 0 x FF - (M) \\ M \leftarrow (\overline{M}) = 0 x FF - (M) \\ M \leftarrow (\overline{M}) = 0 x FF - (M) \end{array}$ | 0 | _                | _ |   |   | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 43<br>53<br>63<br>73<br>9E63             | ff<br>ff                                                             | 5<br>1<br>1<br>5<br>4<br>6            |

| CPHX opr16a<br>CPHX #opr16i<br>CPHX opr8a<br>CPHX oprx8,SP                                                       | Compare Index Register (H:X) with Memory  | (H:X) – (M:M + 0x0001)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                               |   | _                | - |   |   |   | EXT<br>IMM<br>DIR<br>SP1                                                                     | 65                                       | dd                                                                   | 6<br>3<br>5<br>6                      |

Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

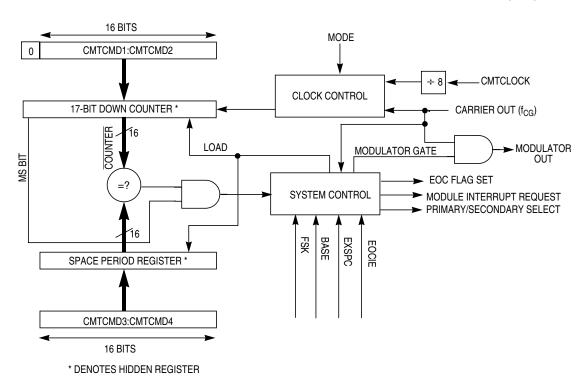

Figure 8-4. Modulator Block Diagram

#### 8.5.2.1 Time Mode

When the modulator operates in time mode (MCGEN bit is set, BASE bit is clear, and FSK bit is clear), the modulation mark period consists of an integer number of CMTCLK  $\div$  8 clock periods. The modulation space period consists of zero or an integer number of CMTCLK  $\div$  8 clock periods. With an 8 MHz bus and CMTDIV1:CMTDIV0 = 00, the modulator resolution is 1  $\mu$ s and has a maximum mark and space period of about 65.535 ms each. See Figure 8-5 for an example of the time mode and baseband mode outputs.

The mark and space time equations for time and baseband mode are:

$$\mathbf{t_{mark}} = (\mathsf{CMTCMD1} : \mathsf{CMTCMD2} + 1) \div (\mathbf{f_{\mathsf{CMTCLK}}} \div 8)$$

Eqn. 8-5

$$\mathbf{t_{space}} = \mathsf{CMTCMD3} : \mathsf{CMTCMD4} \div (\mathbf{f_{\mathsf{CMTCLK}}} \div 8)$$

Eqn. 8-6

where CMTCMD1:CMTCMD2 and CMTCMD3:CMTCMD4 are the decimal values of the concatenated registers.

#### NOTE

If the modulator is disabled while the  $t_{mark}$  time is less than the programmed carrier high time ( $t_{mark}$  < CMTCGH1/ $f_{CMTCLK}$ ), the modulator can enter into an illegal state and end the curent cycle before the programmed value. Make sure to program  $t_{mark}$  greater than the carrier high time to avoid this illegal state.

## 8.5.5 CMT Interrupts

The end of cycle flag (EOCF) is set when:

- The modulator is not currently active and the MCGEN bit is set to begin the initial CMT transmission

- At the end of each modulation cycle (when the counter is reloaded from CMTCMD1:CMTCMD2) while the MCGEN bit is set

In the case where the MCGEN bit is cleared and then set before the end of the modulation cycle, the EOCF bit will not be set when the MCGEN is set, but will become set at the end of the current modulation cycle.

When the MCGEN becomes disabled, the CMT module does not set the EOC flag at the end of the last modulation cycle.

The EOCF bit is cleared by reading the CMT modulator status and control register (CMTMSC) followed by an access of CMTCMD2 or CMTCMD4.

If the EOC interrupt enable (EOCIE) bit is high when the EOCF bit is set, the CMT module will generate an interrupt request. The EOCF bit must be cleared within the interrupt service routine to prevent another interrupt from being generated after exiting the interrupt service routine.

The EOC interrupt is coincident with loading the down-counter with the contents of CMTCMD1:CMTCMD2 and loading the space period register with the contents of CMTCMD3:CMTCMD4. The EOC interrupt provides a means for the user to reload new mark/space values into the modulator data registers. Modulator data register updates will take effect at the end of the current modulation cycle. Note that the down-counter and space period register are updated at the end of every modulation cycle, regardless of interrupt handling and the state of the EOCF flag.

# 8.5.6 Wait Mode Operation

During wait mode the CMT, if enabled, will continue to operate normally. However, there will be no new codes or changes of pattern mode while in wait mode, because the CPU is not operating.

# 8.5.7 Stop Mode Operation

During all stop modes, clocks to the CMT module are halted.

In stop1 and stop2 modes, all CMT register data is lost and must be re-initialized upon recovery from these two stop modes.

No CMT module registers are affected in stop3 mode.

Note, because the clocks are halted, the CMT will resume upon exit from stop (only in stop3 mode). Software should ensure stop2 or stop3 mode is not entered while the modulator is in operation to prevent the IRO pin from being asserted while in stop mode. This may require a time-out period from the time that the MCGEN bit is cleared to allow the last modulator cycle to complete.

**Carrier Modulator Transmitter (CMT) Block Description**

## 8.5.8 Background Mode Operation

When the microcontroller is in active background mode, the CMT temporarily suspends all counting until the microcontroller returns to normal user mode.

# 8.6 CMT Registers and Control Bits

The following registers control and monitor CMT operation:

- CMT carrier generator data registers (CMTCGH1, CMTCGL1, CMTCGH2, CMTCGL2)

- CMT output control register (CMTOC)

- CMT modulator status and control register (CMTMSC)

- CMT modulator period data registers (CMTCMD1, CMTCMD2, CMTCMD3, CMTCMD4)

# 8.6.1 Carrier Generator Data Registers (CMTCGH1, CMTCGL1, CMTCGH2, and CMTCGL2)

The carrier generator data registers contain the primary and secondary high and low values for generating the carrier output.

Figure 8-8. Carrier Generator Data Register High 1(CMTCGH1)

**Table 8-3. CMTCGH1 Field Descriptions**

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

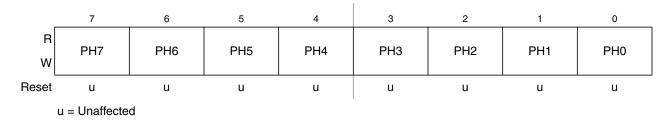

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0<br>PH[7:0] | Primary Carrier High Time Data Values — When selected, these bits contain the number of input clocks required to generate the carrier high and low time periods. When operating in time mode (see Section 8.5.2.1, "Time Mode"), this register pair is always selected. When operating in FSK mode (see Section 8.5.2.3, "FSK Mode"), this register pair and the secondary register pair are alternatively selected under control of the modulator. The primary carrier high and low time values are unaffected out of reset. These bits must be written to nonzero values before the carrier generator is enabled to avoid spurious results. |  |  |  |  |  |

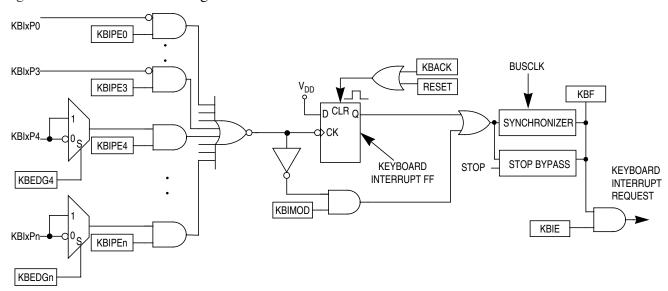

# 9.2 KBI Block Diagram

Figure 9-2 shows the block diagram for a KBI module.

Figure 9-2. KBI Block Diagram

The KBI module allows up to eight pins to act as additional interrupt sources. Four of these pins allow falling-edge sensing while the other four can be configured for either rising-edge sensing or falling-edge sensing. The sensing mode for all eight pins can also be modified to detect edges and levels instead of only edges.

# 9.3 Keyboard Interrupt (KBI) Module

This on-chip peripheral module is called a keyboard interrupt (KBI) module because originally it was designed to simplify the connection and use of row-column matrices of keyboard switches. However, these inputs are also useful as extra external interrupt inputs and as an external means of waking up the MCU from stop or wait low-power modes.

#### 9.3.1 Pin Enables

The KBIPEn control bits in the KBIxPE register allow a user to enable (KBIPEn = 1) any combination of KBI-related port pins to be connected to the KBI module. Pins corresponding to 0s in KBIxPE are general-purpose I/O pins that are not associated with the KBI module.

# 9.3.2 Edge and Level Sensitivity

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled keyboard inputs in a KBI module must be at the deasserted logic level.

A falling edge is detected when an enabled keyboard input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle.

Freescale Semiconductor

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

Serial Peripheral Interface (SPI) Module

#### 13.1 **Features**

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

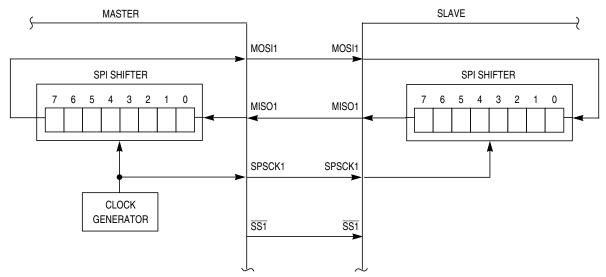

#### 13.2 **Block Diagrams**

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

#### 13.2.1 **SPI System Block Diagram**

Figure 13-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI1 pin) to the slave while simultaneously shifting data in (on the MISO1 pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK1 signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS1}$  pin). In this system, the master device has configured its  $\overline{SS1}$  pin as an optional slave select output.

Figure 13-2. SPI System Connections

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11 164 Freescale Semiconductor

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 13-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

## 13.2.2 SPI Module Block Diagram

Figure 13-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPI1D) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPI1D). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK1 pin, the shifter output is routed to MOSI1, and the shifter input is routed from the MISO1 pin.

When the SPI is configured as a slave, the SPSCK1 pin is routed to the clock input of the SPI, the shifter output is routed to MISO1, and the shifter input is routed from the MOSI1 pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 15.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 15.2.2, "Communication Details," for more detail.

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a development system is connected, it can pull both BKGD and RESET low, release RESET to select active background mode rather than normal operating mode, then release BKGD. It is not necessary to reset the target MCU to communicate with it through the background debug interface.

#### 15.2.2 Communication Details

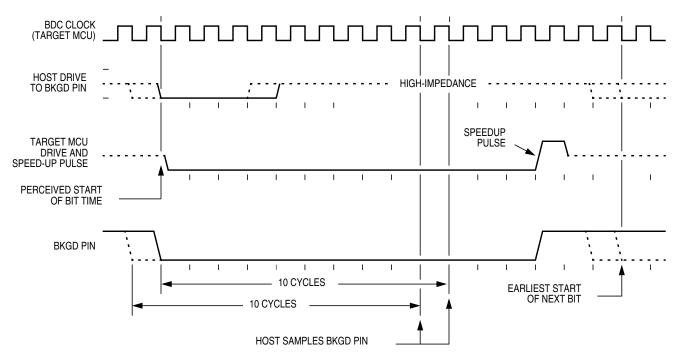

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

#### **Development Support**

Figure 15-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 15-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

#### **Development Support**

Table 15-2. BDCSCR Register Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |  |  |  |  |  |  |

| 1<br>WSF | Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)  0 Memory access did not conflict with a wait or stop instruction 1 Memory access command failed because the CPU entered wait or stop mode                                                                                                                |  |  |  |  |  |  |

| 0<br>DVF | Data Valid Failure Status — This status bit is not used in the MC9S08RC/RD/RE/RG because it does not have any slow access memory.  O Memory access did not conflict with a slow memory access  Memory access command failed because CPU was not finished with a slow memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

#### 15.4.1.2 **BDC Breakpoint Match Register (BDCBKPT)**

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ BKPT and WRITE BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 15.2.4, "BDC Hardware Breakpoint."

#### 15.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial active background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11 198 Freescale Semiconductor

**Development Support**

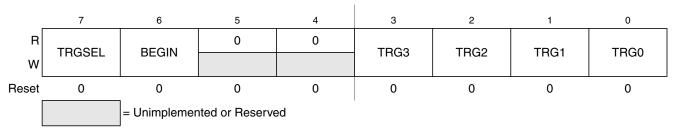

## 15.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

Figure 15-8. Debug Trigger Register (DBGT)

**Table 15-5. DBGT Register Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TRGSEL     | Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.  O Trigger on access to compare address (force)  1 Trigger if opcode at compare address is executed (tag) |  |  |  |  |  |

| 6<br>BEGIN      | Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.  0 Data stored in FIFO until trigger (end trace)  1 Trigger initiates data storage (begin trace)                                                                                                             |  |  |  |  |  |

| 3:0<br>TRG[3:0] | Select Trigger Mode — Selects one of nine triggering modes, as described below.  0000 A-only  0001 A OR B  0010 A Then B  0011 Event-only B (store data)  0100 A then event-only B (store data)  0101 A AND B data (full mode)  0110 A AND NOT B data (full mode)  0111 Inside range: A ≤ address ≤ B  1000 Outside range: address < A or address > B  1001 – 1111 (No trigger)                                                                                                  |  |  |  |  |  |

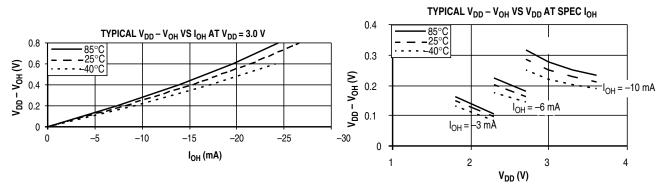

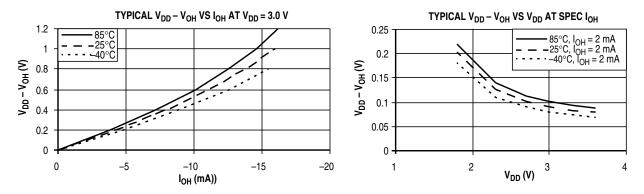

#### **Electrical Characteristics**

Figure A-4. Typical High-Side Driver (Source) Characteristics (Port B and IRO)

Figure A-5. Typical High-Side (Source) Characteristics (Ports A, C, D and E)

Semiconductor Products Sector

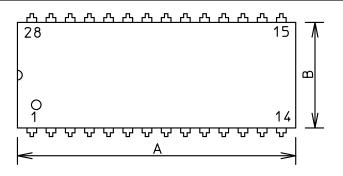

MECHANICAL OUTLINES DICTIONARY

98ASB42390B

**PAGE** 710

В

DATE 08/18/78

COPYRIGHT 1978-95 MOTOROLA ALL RIGHTS RESERVED DO NOT SCALE THIS DRAWING

ISSUE

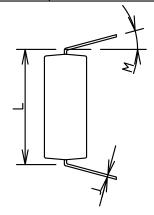

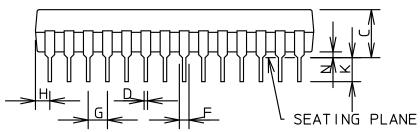

| DIM          | MIL                  | LIMETERS                                                            | IN                      | CHES                            |

|--------------|----------------------|---------------------------------------------------------------------|-------------------------|---------------------------------|

| וווט         | MIN                  | MAX                                                                 | MIN                     | MAX                             |

| くめしひにのエーメーをと | 1.65<br>0.20<br>2.92 | 14.22<br>5.08<br>0.56<br>1.52<br>54 BSC<br>0.38<br>3.43<br>5.24 BSC | 0.065<br>0.008<br>0.115 | 0.022<br>0.060<br>0BSC<br>0.085 |

| CASE         | NO .                 | 710-02                                                              |                         |                                 |

MOT STD

STANDARD

REFERENCE

28 LD PDIP

TITLE

- POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- DIMENSION L TO CENTER OF LEADS 2. WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- 710-01 OBSOLETE, NEW STD 710-02. CONTROLLING DIMENSION: INCH

SHEET 1 OF 1

5.