Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | SCI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 23                                                         |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                             |

| Supplier Device Package    | 28-SOIC                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08rd8cdwe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Section Nu    | mber Title                                      | Page |

|---------------|-------------------------------------------------|------|

|               | 13.3.2.3 MISO1 — Master Data In, Slave Data Out |      |

|               | 13.3.2.4 $\overline{SS1}$ — Slave Select        |      |

| 13.3.3        | SPI Interrupts                                  |      |

| 13.3.4        | Mode Fault Detection                            |      |

| 13.4 SPI Regi | sters and Control Bits                          |      |

| 13.4.1        | SPI Control Register 1 (SPI1C1)                 |      |

| 13.4.2        | SPI Control Register 2 (SPI1C2)                 |      |

| 13.4.3        | SPI Baud Rate Register (SPI1BR)                 |      |

|               | SPI Status Register (SPI1S)                     |      |

| 13.4.5        | SPI Data Register (SPI1D)                       |      |

# Chapter 14 Analog Comparator (S08ACMPV1)

| 14.1 | Features  |                                     |  |

|------|-----------|-------------------------------------|--|

| 14.2 | Block Dia | agram                               |  |

|      |           | iption                              |  |

|      |           | d Description                       |  |

|      |           | Interrupts                          |  |

|      |           | Wait Mode Operation                 |  |

|      |           | Stop Mode Operation                 |  |

|      |           | Background Mode Operation           |  |

| 14.5 |           | atus and Control Register (ACMP1SC) |  |

|      |           |                                     |  |

# Chapter 15 Development Support

| 15.1 | Introduct | tion                                                 | 183 |

|------|-----------|------------------------------------------------------|-----|

|      | 15.1.1    | ion<br>Features                                      | 183 |

| 15.2 | Backgrou  | und Debug Controller (BDC)                           | 184 |

|      | 15.2.1    | BKGD Pin Description                                 | 184 |

|      | 15.2.2    | Communication Details                                | 185 |

|      | 15.2.3    | BDC Commands                                         | 189 |

|      | 15.2.4    | BDC Hardware Breakpoint                              | 191 |

| 15.3 | On-Chip   | Debug System (DBG)                                   | 192 |

|      | 15.3.1    | Comparators A and B                                  | 192 |

|      | 15.3.2    | Bus Capture Information and FIFO Operation           | 192 |

|      | 15.3.3    | Change-of-Flow Information                           | 193 |

|      | 15.3.4    | Tag vs. Force Breakpoints and Triggers               | 193 |

|      | 15.3.5    | Trigger Modes                                        | 194 |

|      | 15.3.6    | Hardware Breakpoints                                 | 196 |

| 15.4 | Register  | Definition                                           | 196 |

|      | 15.4.1    | BDC Registers and Control Bits                       | 196 |

|      |           | 15.4.1.1 BDC Status and Control Register (BDCSCR)    | 197 |

|      |           | 15.4.1.2 BDC Breakpoint Match Register (BDCBKPT)     | 198 |

|      | 15.4.2    | System Background Debug Force Reset Register (SBDFR) |     |

|      |           | -                                                    |     |

#### MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

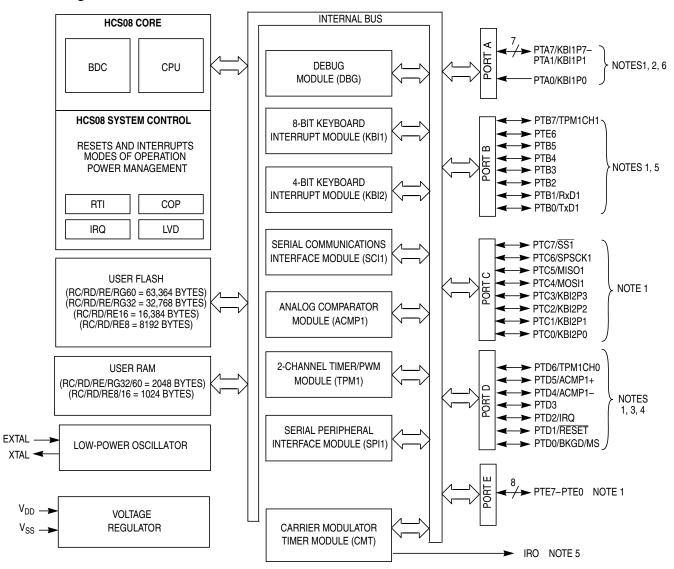

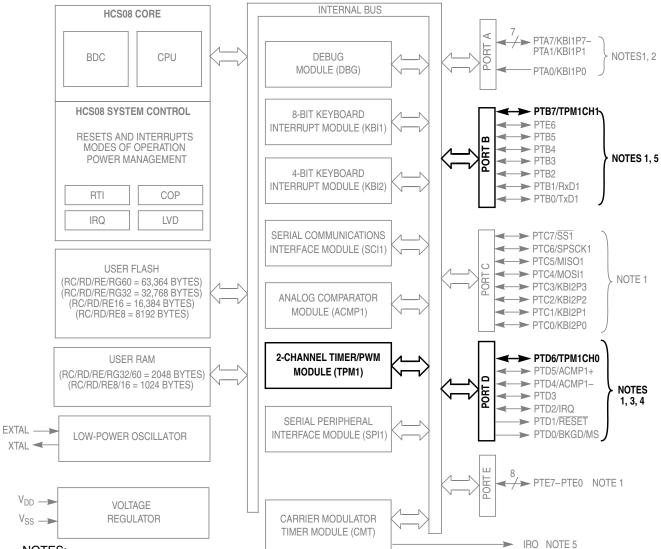

## 1.3 MCU Block Diagram

This block diagram shows the structure of the MC9S08RC/RD/RE/RG MCUs

NOTES:

- 1. Port pins are software configurable with pullup device if input port

- 2. PTA0 does not have a clamp diode to  $V_{DD}$ . PTA0 should not be driven above  $V_{DD}$ . Also, PTA0 does not pullup to  $V_{DD}$  when internal pullup is enabled.

- 3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1)

- 4. The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

#### Figure 1-1. MC9S08RC/RD/RE/RG Block Diagram

Table 1-2 lists the functional versions of the on-chip modules.

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

**Pins and Connections**

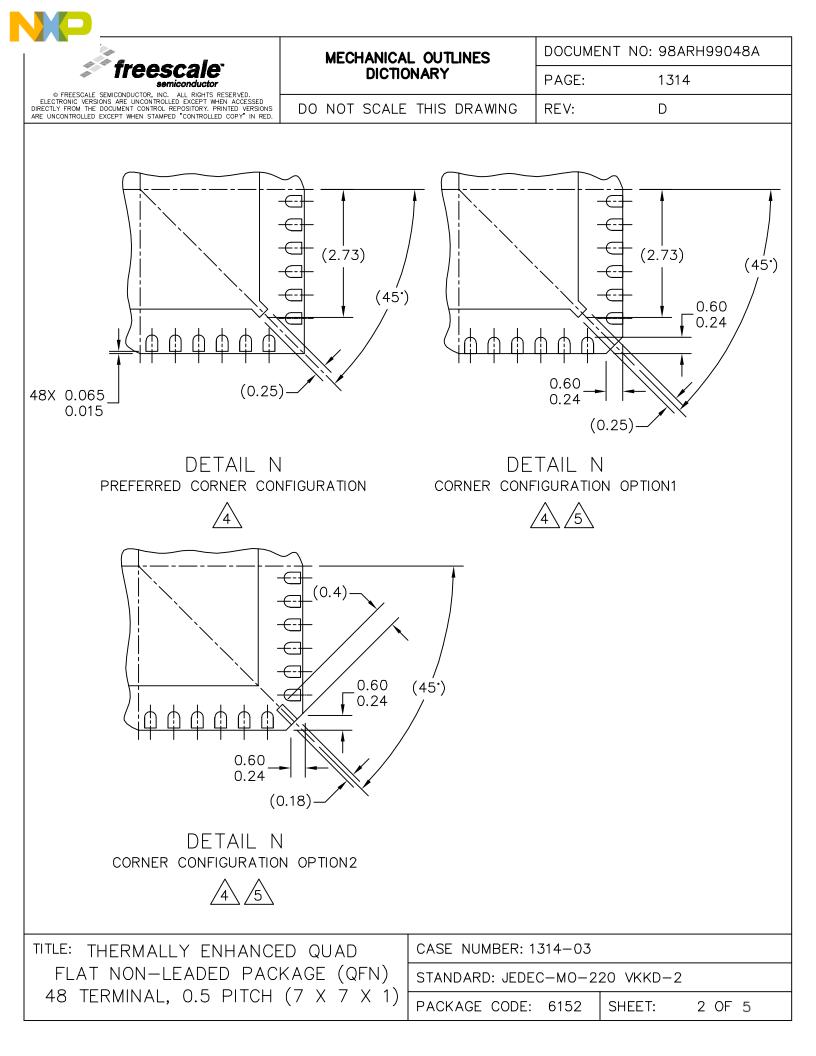

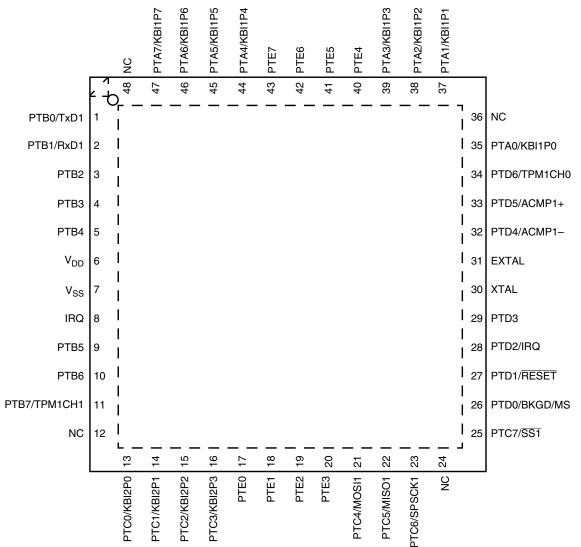

Figure 2-4. MC9S08RC/RD/RE/RG in 48-Pin QFN Package

## 2.3 Recommended System Connections

Figure 2-5 shows pin connections that are common to almost all MC9S08RC/RD/RE/RG application systems. A more detailed discussion of system connections follows.

#### Modes of Operation

into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and after exiting stop2 mode until a 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting any of the wakeup pins: RESET, IRQ, or KBI1 that have been enabled, or through the real-time interrupt. IRQ and KBI1 pins are always active-low when used as wakeup pins in stop2 regardless of how they were configured before entering stop2. (KBI2 will not wake the MCU from stop2.)

Upon wakeup from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

After waking up from stop2, the PPDF bit in SPMSC2 is set. This flag may be used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

For pins that were configured as general-purpose I/O, the user must copy the contents of the I/O port registers, which have been saved in RAM, back to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the register bits will be in their reset states when the I/O pin latches are opened and the I/O pins will switch to their reset states.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

## 3.6.3 Stop3 Mode

Upon entering stop3 mode, all of the clocks in the MCU, including the oscillator itself, are halted. The OSC is turned off, the ACMP is disabled, and the voltage regulator is put in standby. The states of all of the internal registers and logic, as well as the RAM content, are maintained. The I/O pin states are not latched at the pin as in stop2. Instead they are maintained by virtue of the states of the internal logic driving the pins being maintained.

Exit from stop3 is done by asserting  $\overline{\text{RESET}}$ , any asynchronous interrupt pin that has been enabled, or through the real-time interrupt. The asynchronous interrupt pins are the IRQ or KBI1 and KBI2 pins.

If stop3 is exited by means of the RESET pin, then the MCU will be reset and operation will resume after taking the reset vector. Exit by means of an asynchronous interrupt or the real-time interrupt will result in the MCU taking the appropriate interrupt vector.

A separate self-clocked source ( $\approx 1 \text{ kHz}$ ) for the real-time interrupt allows a wakeup from stop2 or stop3 mode with no external components. When RTIS2:RTIS1:RTIS0 = 0:0:0, the real-time interrupt function and this 1-kHz source are disabled. Power consumption is lower when the 1-kHz source is disabled, but in that case the real-time interrupt cannot wake the MCU from stop.

Memory

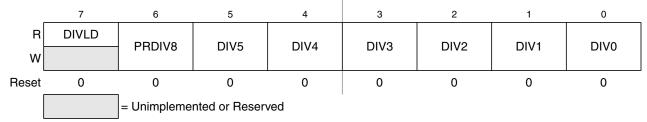

| Figure 4-5. FLASH Clock Divider Register (FCDI) | /) |

|-------------------------------------------------|----|

|-------------------------------------------------|----|

#### Table 4-5. FCDIV Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD      | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH.</li> </ul>                                                                                                                                           |

| 6<br>PRDIV8     | <ul> <li>Prescale (Divide) FLASH Clock by 8</li> <li>0 Clock input to the FLASH clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:0<br>DIV[5:0] | <b>Divisor for FLASH Clock Divider</b> — The FLASH clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV5:DIV0 field plus one. The resulting frequency of the internal FLASH clock must fall within the range of 200 kHz to 150 kHz for proper FLASH operations. Program/erase timing pulses are one cycle of this internal FLASH clock, which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |

## if PRDIV8 = 0 — $f_{FCLK} = f_{Bus} \div ([DIV5:DIV0] + 1)$

Eqn. 4-1

## if PRDIV8 = 1 — $f_{FCLK} = f_{Bus} \div (8 \times ([DIV5:DIV0] + 1))$

Eqn. 4-2

Table 4-6 shows the appropriate values for PRDIV8 and DIV5:DIV0 for selected bus frequencies.

#### Table 4-6. FLASH Clock Divider Settings

| f <sub>Bus</sub> | PRDIV8<br>(Binary) | DIV5:DIV0<br>(Decimal) | ffclk   | Program/Erase Timing Pulse<br>(5 μs Min, 6.7 μs Max) |

|------------------|--------------------|------------------------|---------|------------------------------------------------------|

| 8 MHz            | 0                  | 39                     | 200 kHz | 5 µs                                                 |

| 4 MHz            | 0                  | 19                     | 200 kHz | 5 μs                                                 |

| 2 MHz            | 0                  | 9                      | 200 kHz | 5 µs                                                 |

| 1 MHz            | 0                  | 4                      | 200 kHz | 5 µs                                                 |

| 200 kHz          | 0                  | 0                      | 200 kHz | 5 μs                                                 |

| 150 kHz          | 0                  | 0                      | 150 kHz | 6.7 μs                                               |

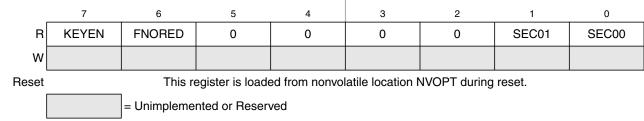

## 4.6.2 FLASH Options Register (FOPT and NVOPT)

During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into FOPT. Bits 5 through 2 are not used and always read 0. This register may be read at any time, but writes have no meaning or effect. To change the value in this register, erase and reprogram the NVOPT location in FLASH memory as usual and then issue a new MCU reset.

#### Figure 4-6. FLASH Options Register (FOPT)

| Table | 4-7. | FOPT | Field  | Descriptions |

|-------|------|------|--------|--------------|

| labio |      |      | 1 1010 | Booonphono   |

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>KEYEN       | <ul> <li>Backdoor Key Mechanism Enable — When this bit is 0, the backdoor key mechanism cannot be used to disengage security. The backdoor key mechanism is accessible only from user (secured) firmware. BDM commands cannot be used to write key comparison values that would unlock the backdoor key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."</li> <li>No backdoor key access allowed.</li> <li>If user firmware writes an 8-byte value that matches the nonvolatile backdoor key (NVBACKKEY through NVBACKKEY+7 in that order), security is temporarily disengaged until the next MCU reset.</li> </ul> |

| 6<br>FNORED      | <ul> <li>Vector Redirection Disable — When this bit is 1, then vector redirection is disabled.</li> <li>0 Vector redirection enabled.</li> <li>1 Vector redirection disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1:0<br>SEC0[1:0] | Security State Code — This 2-bit field determines the security state of the MCU as shown below. When the MCU is secure, the contents of RAM and FLASH memory cannot be accessed by instructions from any unsecured source including the background debug interface. For more detailed information about security, refer to Section 4.5, "Security."<br>00 Secure<br>01 Secure<br>10 Unsecured<br>11 Secure<br>SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.                                                                                                                                                    |

# 4.6.3 FLASH Configuration Register (FCNFG)

Bits 7 through 5 may be read or written at any time. Bits 4 through 0 always read 0 and cannot be written.

#### Parallel Input/Output

|                                                | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| R<br>W                                         | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |  |  |

| Reset                                          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| Figure 6-20. Data Direction for Port E (PTEDD) |        |        |        |        |        |        |        |        |  |  |

#### **5**

#### Table 6-15. PTEDD Field Descriptions

| Field             | Description                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDD(7:0) | <b>Data Direction for Port E Bits</b> — These read/write bits control the direction of port E pins and what is read for PTED reads.                                                 |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.</li> </ul> |

## 7.5 HCS08 Instruction Set Summary

#### **Instruction Set Summary Nomenclature**

The nomenclature listed here is used in the instruction descriptions in Table 7-2.

#### **Operators**

- () = Contents of register or memory location shown inside parentheses

- $\leftarrow$  = Is loaded with (read: "gets")

- **&** = Boolean AND

- $\mid$  = Boolean OR

- $\oplus$  = Boolean exclusive-OR

- $\times$  = Multiply

- $\div$  = Divide

- : = Concatenate

- + = Add

- = Negate (two's complement)

#### **CPU registers**

- A = Accumulator

- CCR = Condition code register

- H = Index register, higher order (most significant) 8 bits

- X = Index register, lower order (least significant) 8 bits

- PC = Program counter

- PCH = Program counter, higher order (most significant) 8 bits

- PCL = Program counter, lower order (least significant) 8 bits

- SP = Stack pointer

#### Memory and addressing

- M = A memory location or absolute data, depending on addressing mode

- M:M + 0x0001= A 16-bit value in two consecutive memory locations. The higher-order (most significant) 8 bits are located at the address of M, and the lower-order (least significant) 8 bits are located at the next higher sequential address.

#### Condition code register (CCR) bits

- V = Two's complement overflow indicator, bit 7

- H = Half carry, bit 4

- I = Interrupt mask, bit 3

- N = Negative indicator, bit 2

- Z = Zero indicator, bit 1

- **C** = Carry/borrow, bit 0 (carry out of bit 7)

#### CCR activity notation

- = Bit not affected

- IX = 16-bit indexed no offset

- IX+ = 16-bit indexed no offset, post increment (CBEQ and MOV only)

- IX1 = 16-bit indexed with 8-bit offset from H:X

- IX1+ = 16-bit indexed with 8-bit offset, post increment (CBEQ only)

- IX2 = 16-bit indexed with 16-bit offset from H:X

- REL = 8-bit relative offset

- SP1 = Stack pointer with 8-bit offset

- SP2 = Stack pointer with 16-bit offset

#### Table 7-2. HCS08 Instruction Set Summary (Sheet 1 of 7)

| Source                                                                                                               | Operation                                                  | Description                                                          |   | Effect<br>on CCR |   |   |   |   | Address<br>Mode                                     | Opcode                             | and                                 | /cles <sup>1</sup>      |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|---|------------------|---|---|---|---|-----------------------------------------------------|------------------------------------|-------------------------------------|-------------------------|

| Form                                                                                                                 | Operation                                                  |                                                                      |   | н                | I | N | z | с | Addi<br>Mo                                          | Opc                                | Operand                             | Bus Cycles <sup>1</sup> |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC oprx8,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry                                             | A ← (A) + (M) + (C)                                                  |   |                  | _ |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D9<br>E9<br>F9<br>9ED9<br>9EE9     | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP      | Add without Carry                                          | A ← (A) + (M)                                                        |   |                  | - |   |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | BB<br>CB                           | hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 3 5 4         |

| AIS # <i>opr8i</i>                                                                                                   | Add Immediate Value<br>(Signed) to Stack Pointer           | $SP \leftarrow (SP) + (M)$<br>M is sign extended to a 16-bit value   | - | -                | - | - | - | - | IMM                                                 | A7                                 | ii                                  | 2                       |

| AIX #opr8i                                                                                                           | Add Immediate Value<br>(Signed) to Index<br>Register (H:X) | $H:X \leftarrow (H:X) + (M)$<br>M is sign extended to a 16-bit value | - | -                | - | - | - | - | IMM                                                 | AF                                 | ii                                  | 2                       |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP      | Logical AND                                                | A ← (A) & (M)                                                        | 0 | _                | _ |   |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D4                                 | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL ,X<br>ASL oprx8,SP                                         | Arithmetic Shift Left<br>(Same as LSL)                     | C - 0 b7 b0                                                          |   | _                | _ |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68 | ff                                  | 5<br>1<br>5<br>4<br>6   |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                                   | Arithmetic Shift Right                                     |                                                                      |   | _                | _ |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37<br>47<br>57<br>67<br>77<br>9E67 | ff<br>ff                            | 5<br>1<br>5<br>4<br>6   |

| BCC rel                                                                                                              | Branch if Carry Bit Clear                                  | Branch if (C) = 0                                                    | - | -                | - | - | - | - | REL                                                 | 24                                 | rr                                  | 3                       |

| Mode              | MCGEN<br>Bit <sup>(1)</sup> | BASE<br>Bit <sup>(2)</sup> | FSK<br>Bit <sup>(2)</sup> | EXSPC<br>Bit | Comment                                                                                                                                                                   |  |

|-------------------|-----------------------------|----------------------------|---------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Time              | 1                           | 0                          | 0                         | 0            | $\rm f_{CG}$ controlled by primary high and low registers. $\rm f_{CG}$ transmitted to IRO pin when modulator gate is open.                                               |  |

| Baseband          | 1                           | 1                          | х                         | 0            | ${\rm f}_{\rm CG}$ is always high. IRO pin high when modulator gate is open.                                                                                              |  |

| FSK               | 1                           | 0                          | 1                         | 0            | $\rm f_{CG}$ control alternates between primary high/low registers and secondary high/low registers. $\rm f_{CG}$ transmitted to IRO pin when modulator gate is open.     |  |

| Extended<br>Space | 1                           | x                          | x                         | 1            | Setting the EXSPC bit causes subsequent modulator cycles<br>to be spaces (modulator out not asserted) for the duration of<br>the modulator period (mark and space times). |  |

| IRO Latch         | 0                           | х                          | х                         | x            | IROL bit controls state of IRO pin.                                                                                                                                       |  |

#### Table 8-2. CMT Modes of Operation

1. To prevent spurious operation, initialize all data and control registers before beginning a transmission (MCGEN=1).

2. These bits are not double buffered and should not be changed during a transmission (while MCGEN=1).

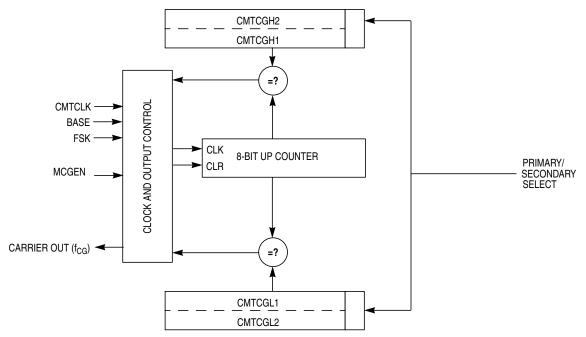

## 8.5.1 Carrier Generator

The carrier signal is generated by counting a register-selected number of input clocks (125 ns for an 8 MHz bus) for both the carrier high time and the carrier low time. The period is determined by the total number of clocks counted. The duty cycle is determined by the ratio of high time clocks to total clocks counted. The high and low time values are user programmable and are held in two registers.

An alternate set of high/low count values is held in another set of registers to allow the generation of dual frequency FSK (frequency shift keying) protocols without CPU intervention.

#### NOTE

Only non-zero data values are allowed. The carrier generator will not work if any of the count values are equal to zero.

The MCGEN bit in the CMTMSC register must be set and the BASE bit must be cleared to enable carrier generator clocks. When the BASE bit is set, the carrier output to the modulator is held high continuously. The block diagram is shown in Figure 8-3.

Figure 8-3. Carrier Generator Block Diagram

The high/low time counter is an 8-bit up counter. After each increment, the contents of the counter are compared with the appropriate high or low count value register. When the compare value is reached, the counter is reset to a value of \$01, and the compare is redirected to the other count value register.

Assuming that the high time count compare register is currently active, a valid compare will cause the carrier output to be driven low. The counter will continue to increment (starting at reset value of \$01). When the value stored in the selected low count value register is reached, the counter will again be reset and the carrier output will be driven high.

The cycle repeats, automatically generating a periodic signal that is directed to the modulator. The lowest frequency (maximum period) and highest frequency (minimum period) that can be generated are defined as:

$$f_{max} = f_{CMTCLK} \div (2 x 1) Hz$$

Eqn. 8-1

$$f_{min} = f_{CMTCLK} \div (2 \times (2^8 - 1)) Hz$$

Eqn. 8-2

In the general case, the carrier generator output frequency is:

$$f_{CG} = f_{CMTCLK} \div$$

(Highcount + Lowcount) Hz Eqn. 8-3

Where: 0 < Highcount < 256 and 0 < Lowcount < 256

#### Keyboard Interrupt (KBI) Block Description

A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

The KBIMOD control bit can be set to reconfigure the detection logic so that it detects edges and levels. In KBIMOD = 1 mode, the KBF status flag becomes set when an edge is detected (when one or more enabled pins change from the deasserted to the asserted level while all other enabled pins remain at their deasserted levels), but the flag is continuously set (and cannot be cleared) as long as any enabled keyboard input pin remains at the asserted level. When the MCU enters stop mode, the synchronous edge-detection logic is bypassed (because clocks are stopped). In stop mode, KBI inputs act as asynchronous level-sensitive inputs so they can wake the MCU from stop mode.

## 9.3.3 KBI Interrupt Controls

The KBF status flag becomes set (1) when an edge event has been detected on any KBI input pin. If KBIE = 1 in the KBIxSC register, a hardware interrupt will be requested whenever KBF = 1. The KBF flag is cleared by writing a 1 to the keyboard acknowledge (KBACK) bit.

When KBIMOD = 0 (selecting edge-only operation), KBF is always cleared by writing 1 to KBACK. When KBIMOD = 1 (selecting edge-and-level operation), KBF cannot be cleared as long as any keyboard input is at its asserted level.

## 9.4 KBI Registers and Control Bits

This section provides information about all registers and control bits associated with the KBI modules.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all KBI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some MCU systems have more than one KBI, so register names include placeholder characters to identify which KBI is being referenced. For example, KBIxSC refers to the KBIx status and control register and KBI2SC is the status and control register for KBI2.

#### Timer/PWM Module (S08TPMV1)

#### NOTES:

13.Port pins are software configurable with pullup device if input port

14.PTA0 does not have a clamp diode to VDD. PTA0 should not be driven above VDD. Also, PTA0 does not pullup to VDD when interna pullup is enabled.

15.IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1) 16.The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

17.High current drive

18.Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

#### Figure 10-1. MC9S08RC/RD/RE/RG Block Diagram Highlighting TPM Block and Pins

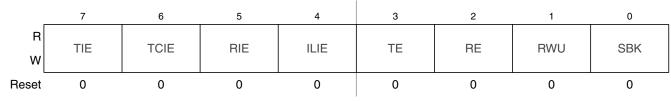

# 12.2.3 SCI Control Register 2 (SCI1C2)

This register can be read or written at any time.

## Figure 12-6. SCI Control Register 2 (SCI1C2)

#### Table 12-4. SCI1C2 Register Field Descriptions

| Field     | Description                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)         0       Hardware interrupts from TDRE disabled (use polling).         1       Hardware interrupt requested when TDRE flag is 1.        |

| 6<br>TCIE | Transmission Complete Interrupt Enable (for TC)         0       Hardware interrupt requested when TC flag is 1.         1       Hardware interrupts from TC disabled (use polling). |

| 5<br>RIE  | Receiver Interrupt Enable (for RDRF)         0       Hardware interrupts from RDRF disabled (use polling).         1       Hardware interrupt requested when RDRF flag is 1.        |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)         0       Hardware interrupts from IDLE disabled (use polling).         1       Hardware interrupt requested when IDLE flag is 1.       |

| 3<br>TE   | Transmitter Enable001111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                                       |

| 2<br>RE   | <ul> <li>Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin.</li> <li>Receiver off.</li> <li>Receiver on.</li> </ul>       |

Serial Peripheral Interface (SPI) Module

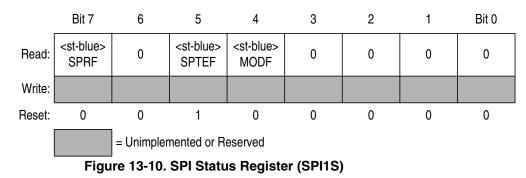

# 13.4.4 SPI Status Register (SPI1S)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0s. Writes have no meaning or effect.

### SPRF — SPI Read Buffer Full Flag

SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPI1D). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.

1 = Data available in the receive data buffer.

0 = No data available in the receive data buffer.

### SPTEF — SPI Transmit Buffer Empty Flag

This bit is set when there is room in the transmit data buffer. It is cleared by reading SPI1S with SPTEF set, followed by writing a data value to the transmit buffer at SPI1D. SPI1S must be read with SPTEF = 1 before writing data to SPI1D or the SPI1D write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPI1C1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPI1D is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter.

1 = SPI transmit buffer empty.

0 = SPI transmit buffer not empty.

MODF — Master Mode Fault Flag

MODF is set if the SPI is configured as a master and the slave select input goes low, indicating some other SPI device is also configured as a master. The  $\overline{SS1}$  pin acts as a mode fault error input only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by reading MODF while it is 1, then writing to SPI control register 1 (SPI1C1).

1 = Mode fault error detected.

0 = No mode fault error.

Development Support

- Inside range (A  $\leq$  address  $\leq$  B)

- Outside range (address < A or address > B)

# 15.2 Background Debug Controller (BDC)

All MCUs in the HCS08 Family contain a single-wire background debug interface that supports in-circuit programming of on-chip nonvolatile memory and sophisticated non-intrusive debug capabilities. Unlike debug interfaces on earlier 8-bit MCUs, this system does not interfere with normal application resources. It does not use any user memory or locations in the memory map and does not share any on-chip peripherals.

BDC commands are divided into two groups:

- Active background mode commands require that the target MCU is in active background mode (the user program is not running). Active background mode commands allow the CPU registers to be read or written, and allow the user to trace one user instruction at a time, or GO to the user program from active background mode.

- Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

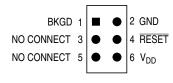

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 15-1. BDM Tool Connector

## 15.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

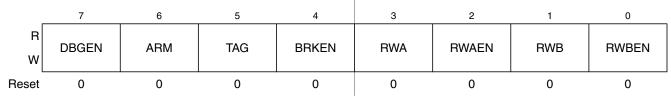

## 15.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 15-7. Debug Control Register (DBGC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DBGEN | <ul> <li>Debug Module Enable — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.</li> <li>0 DBG disabled</li> <li>1 DBG enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>ARM   | <ul> <li>Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                       |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If         BRKEN = 0, this bit has no meaning or effect.         0 CPU breaks requested as force type requests         1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                                                     |

| 4<br>BRKEN | <ul> <li>Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests.</li> <li>0 CPU break requests not enabled</li> <li>1 Triggers cause a break request to the CPU</li> </ul> |

| 3<br>RWA   | <ul> <li>R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A.</li> <li>0 Comparator A can only match on a write cycle</li> <li>1 Comparator A can only match on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 2<br>RWAEN | <ul> <li>Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.</li> <li>0 R/W is not used in comparison A</li> <li>1 R/W is used in comparison A</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

| 1<br>RWB   | <ul> <li>R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.</li> <li>0 Comparator B can match only on a write cycle</li> <li>1 Comparator B can match only on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 0<br>RWBEN | <ul> <li>Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.</li> <li>0 R/W is not used in comparison B</li> <li>1 R/W is used in comparison B</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

# Appendix A Electrical Characteristics

# A.1 Introduction

This section contains electrical and timing specifications.

# A.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-1 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                                                        | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                                                | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                                                          | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                                                         | V <sub>In</sub>  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>(1)</sup> , <sup>(2)</sup> , <sup>(3)</sup> | ۱ <sub>D</sub>   | ± 25                          | mA   |

| Storage temperature range                                                                                                     | T <sub>stg</sub> | –55 to 150                    | °C   |

| Table A-1. Absolut | e Maximum Ratings |

|--------------------|-------------------|

|--------------------|-------------------|

1. Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

2. All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$ .

3. Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

**Electrical Characteristics**

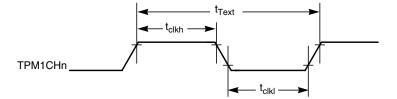

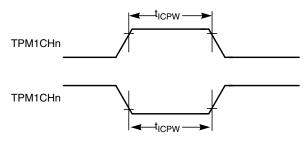

| Function                  | Symbol              | Min | Мах                 | Unit             |

|---------------------------|---------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

Figure A-9. Timer External Clock

Figure A-10. Timer Input Capture Pulse

## A.9.3 SPI Timing

Table A-11 and Figure A-11 through Figure A-14 describe the timing requirements for the SPI system.