Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI                                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 23                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                             |

| Supplier Device Package    | 28-PDIP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08rd8cpe |

**Pins and Connections**

### 2.3.4 Background/Mode Select (PTD0/BKGD/MS)

The background/mode select function is shared with an output-only port function on the PTD0/BKDG/MS pin. While in reset, the pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background/mode select pin, this pin has an internal pullup device enabled. To use as an output-only port, BKGDPE in SOPT must be cleared.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during the rising edge of reset, which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

### 2.3.5 IRO Pin Description

The IRO pin is the output of the CMT. See the Carrier Modulator Timer (CMT) Module Chapter for a detailed description of this pin function.

### 2.3.6 General-Purpose I/O and Peripheral Ports

The remaining pins are shared among general-purpose I/O and on-chip peripheral functions such as timers and serial I/O systems. (Not all pins are available in all packages. See Table 2-2.) Immediately after reset, all 37 of these pins are configured as high-impedance general-purpose inputs with internal pullup devices disabled.

#### **NOTE**

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

For information about controlling these pins as general-purpose I/O pins, see the Chapter 6, "Parallel Input/Output." For information about how and when on-chip peripheral systems use these pins, refer to the appropriate chapter from Table 2-1.

**Pins and Connections**

### 3.6 Stop Modes

One of three stop modes is entered upon execution of a STOP instruction when the STOPE bit in the system option register is set. In all stop modes, all internal clocks are halted. If the STOPE bit is not set when the CPU executes a STOP instruction, the MCU will not enter any of the stop modes and an illegal opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

| Mode  | PDC | PPDC       | CPU, Digital<br>Peripherals,<br>FLASH | RAM     | osc | АСМР    | Regulator | I/O Pins       | RTI           |

|-------|-----|------------|---------------------------------------|---------|-----|---------|-----------|----------------|---------------|

| Stop1 | 1   | 0          | Off                                   | Off     | Off | Standby | Standby   | Reset          | Off           |

| Stop2 | 1   | 1          | Off                                   | Standby | Off | Standby | Standby   | States<br>held | Optionally on |

| Stop3 | 0   | Don't care | Standby                               | Standby | Off | Standby | Standby   | States<br>held | Optionally on |

**Table 3-1. Stop Mode Behavior**

### 3.6.1 Stop1 Mode

Stop1 mode provides the lowest possible standby power consumption by causing the internal circuitry of the MCU to be powered down. To enter stop1, the user must execute a STOP instruction with the PDC bit in SPMSC2 set and the PPDC bit clear. Stop1 can be entered only if the LVD reset is disabled (LVDRE = 0).

When the MCU is in stop1 mode, all internal circuits that are powered from the voltage regulator are turned off. The voltage regulator is in a low-power standby state, as are the OSC and ACMP.

Exit from stop1 is done by asserting any of the wakeup pins on the MCU: RESET, IRQ, or KBI1, which have been enabled. IRQ and KBI pins are always active-low when used as wakeup pins in stop1 regardless of how they were configured before entering stop1.

Upon wakeup from stop1 mode, the MCU will start up as from a power-on reset (POR). The CPU will take the reset vector.

## 3.6.2 Stop2 Mode

Stop2 mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. To select entry into stop2 upon execution of a STOP instruction, the user must execute a STOP instruction with the PPDC and PDC bits in SPMSC2 set. Stop2 can be entered only if LVDRE = 0.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers that they want to restore after exit of stop2, to locations in RAM. Upon exit from stop2, these values can be restored by user software.

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ACMP. Upon entry

Table 4-1. Direct-Page Register Summary

| Address                          | Register Name          | Bit 7    | 6        | 5        | 4        | 3        | 2        | 1      | Bit 0      |

|----------------------------------|------------------------|----------|----------|----------|----------|----------|----------|--------|------------|

| \$00 <b>00</b>                   | PTAD                   | PTAD7    | PTAD6    | PTAD5    | PTAD4    | PTAD3    | PTAD2    | PTAD1  | PTAD0      |

| \$00 <b>00</b><br>\$00 <b>01</b> | PTAPE                  | PTAPE7   | PTAPE6   | PTAPE5   | PTAPE4   | PTAPE3   | PTAPE2   | PTAPE1 | PTAPE0     |

| \$00 <b>01</b>                   | Reserved               | I IAI L7 | I IAI LO | I IAI LS | 1 IAI L4 | 1 IAI L3 |          |        | I IAI LU   |

| \$00 <b>02</b>                   | PTADD                  | PTADD7   | PTADD6   | PTADD5   | PTADD4   | PTADD3   | PTADD2   | PTADD1 | PTADD0     |

| \$00 <b>03</b><br>\$00 <b>04</b> | PTBD                   | PTBD7    | PTBD6    | PTBD5    | PTBD4    | PTBD3    | PTBD2    | PTBD1  | PTBD0      |

| \$00 <b>04</b><br>\$00 <b>05</b> | PTBPE                  | PTBPE7   | PTBPE6   | PTBPE5   | PTBPE4   | PTBPE3   | PTBPE2   | PTBPE1 | PTBPE0     |

| \$00 <b>05</b>                   | Reserved               |          |          |          | - FIDEL4 |          |          |        | FIBEE0     |

| \$00 <b>07</b>                   | PTBDD                  | PTBDD7   | PTBDD6   | PTBDD5   | PTBDD4   | PTBDD3   | PTBDD2   | PTBDD1 | PTBDD0     |

| \$00 <b>07</b>                   | PTCD                   | PTCD7    | PTCD6    | PTCD5    | PTCD4    | PTCD3    | PTCD2    | PTCD1  | PTCD0      |

| \$00 <b>09</b>                   | PTCPE                  | PTCPE7   | PTCPE6   | PTCPE5   | PTCPE4   | PTCPE3   | PTCPE2   | PTCPE1 | PTCPE0     |

| \$00 <b>03</b>                   | Reserved               | 1 101 L7 | —        | 1 101 L3 | —        |          | 1 101 LZ |        | —          |

| \$00 <b>0A</b>                   | PTCDD                  | PTCDD7   | PTCDD6   | PTCDD5   | PTCDD4   | PTCDD3   | PTCDD2   | PTCDD1 | PTCDD0     |

| \$00 <b>0C</b>                   | PTDD                   | 0        | PTDD6    | PTDD5    | PTDD4    | PTDD3    | PTDD2    | PTDD1  | PTDD0      |

| \$00 <b>0D</b>                   | PTDPE                  | 0        | PTDPE6   | PTDPE5   | PTDPE4   | PTDPE3   | PTDPE2   | PTDPE1 | PTDPE0     |

| \$00 <b>0</b> E                  | Reserved               |          |          | 1 1D1 L3 | 1 1D1 L4 | 1 1D1 L3 | 1 1D1 L2 |        | - I IDI LO |

| \$00 <b>0</b> E                  | PTDDD                  | 0        | PTDDD6   | PTDDD5   | PTDDD4   | PTDDD3   | PTDDD2   | PTDDD1 | PTDDD0     |

| \$00 <b>01</b>                   | PTED                   | PTED7    | PTED6    | PTED5    | PTED4    | PTED3    | PTED2    | PTED1  | PTED0      |

| \$00 <b>10</b>                   | PTEPE                  | PTEPE7   | PTEPE6   | PTEPE5   | PTEPE4   | PTEPE3   | PTEPE2   | PTEPE1 | PTEPE0     |

| \$00 <b>11</b>                   | Reserved               |          |          |          |          |          |          |        |            |

| \$00 <b>12</b>                   | PTEDD                  | PTEDD7   | PTEDD6   | PTEDD5   | PTEDD4   | PTEDD3   | PTEDD2   | PTEDD1 | PTEDD0     |

| \$0014                           | KBI1SC                 | KBEDG7   | KBEDG6   | KBEDG5   | KBEDG4   | KBF      | KBACK    | KBIE   | KBIMOD     |

| \$00 <b>15</b>                   | KBI1PE                 | KBIPE7   | KBIPE6   | KBIPE5   | KBIPE4   | KBIPE3   | KBIPE2   | KBIPE1 | KBIPE0     |

| \$00 <b>16</b>                   | KBI2SC                 | 0        | 0        | 0        | 0        | KBF      | KBACK    | KBIE   | KBIMOD     |

| \$00 <b>17</b>                   | KBI2PE                 | 0        | 0        | 0        | 0        | KBIPE3   | KBIPE2   | KBIPE1 | KBIPE0     |

| \$00 <b>18</b>                   | SCI1BDH <sup>(1)</sup> | 0        | 0        | 0        | SBR12    | SBR11    | SBR10    | SBR9   | SBR8       |

| \$00 <b>19</b>                   | SCI1BDL <sup>(1)</sup> | SBR7     | SBR6     | SBR5     | SBR4     | SBR3     | SBR2     | SBR1   | SBR0       |

| \$00 <b>1A</b>                   | SCI1C1 <sup>(1)</sup>  | LOOPS    | SCISWAI  | RSRC     | M        | WAKE     | ILT      | PE     | PT         |

| \$00 <b>1B</b>                   | SCI1C2 <sup>(1)</sup>  | TIE      | TCIE     | RIE      | ILIE     | TE       | RE       | RWU    | SBK        |

| \$00 <b>1C</b>                   | SCI1S1 <sup>(1)</sup>  | TDRE     | TC       | RDRF     | IDLE     | OR       | NF       | FE     | PF         |

| \$00 <b>1D</b>                   | SCI1S2 <sup>(1)</sup>  | 0        | 0        | 0        | 0        | 0        | 0        | 0      | RAF        |

| \$00 <b>1E</b>                   | SCI1C3 <sup>(1)</sup>  | R8       | T8       | TXDIR    | 0        | ORIE     | NEIE     | FEIE   | PEIE       |

| \$00 <b>1F</b>                   | SCI1D <sup>(1)</sup>   | R7/T7    | R6/T6    | R5/T5    | R4/T4    | R3/T3    | R2/T2    | R1/T1  | R0/T0      |

| \$00 <b>20</b>                   | CMTCGH1                | PH7      | PH6      | PH5      | PH4      | PH3      | PH2      | PH1    | PH0        |

| \$00 <b>21</b>                   | CMTCGL1                | PL7      | PL6      | PL5      | PL4      | PL3      | PL2      | PL1    | PL0        |

| \$00 <b>22</b>                   | CMTCGH2                | SH7      | SH6      | SH5      | SH4      | SH3      | SH2      | SH1    | SH0        |

| \$00 <b>23</b>                   | CMTCGL2                | SL7      | SL6      | SL5      | SL4      | SL3      | SL2      | SL1    | SL0        |

| \$00 <b>24</b>                   | CMTOC                  | IROL     | CMTPOL   | IROPEN   | 0        | 0        | 0        | 0      | 0          |

| \$00 <b>25</b>                   | CMTMSC                 | EOCF     | CMTDIV1  | CMTDIV0  | EXSPC    | BASE     | FSK      | EOCIE  | MCGEN      |

| \$00 <b>26</b>                   | CMTCMD1                | MB15     | MB14     | MB13     | MB12     | MB11     | MB10     | MB9    | MB8        |

| \$00 <b>27</b>                   | CMTCMD2                | MB7      | MB6      | MB5      | MB4      | MB3      | MB2      | MB1    | MB0        |

| \$00 <b>28</b>                   | CMTCMD3                | SB15     | SB14     | SB13     | SB12     | SB11     | SB10     | SB9    | SB8        |

| \$00 <b>29</b>                   | CMTCMD4                | SB7      | SB6      | SB5      | SB4      | SB3      | SB2      | SB1    | SB0        |

Parallel Input/Output

#### **Pin Descriptions** 6.3

The MC9S08RC/RD/RE/RG has a total of 39 parallel I/O pins distributed between four 8-bit ports and one 7-bit port. Not all pins are bonded out in all packages. Consult the pin assignment in Chapter 2, "Pins and Connections," for available parallel I/O pins. All of these pins are available for general-purpose I/O when they are not used by other on-chip peripheral systems.

The following paragraphs discuss each port and the software controls that determine each pin's use.

#### 6.3.1 Port A

| Port A |          | Bit 7           | 6               | 5               | 4               | 3               | 2               | 1               | Bit 0           |

|--------|----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|        | MCU Pin: | PTA7/<br>KBI1P7 | PTA6/<br>KBI1P6 | PTA5/<br>KBI1P5 | PTA4/<br>KBI1P4 | PTA3/<br>KBI1P3 | PTA2/<br>KBI1P2 | PTA1/<br>KBI1P1 | PTA0/<br>KBI1P0 |

Figure 6-1. Port A Pin Names

Port A is an 8-bit general-purpose I/O port shared with the KBI1 keyboard interrupt inputs. Bit 0 of port A is an input-only pin.

Port A pins are available as general-purpose I/O pins controlled by the port A data (PTAD), data direction (PTADD), and pullup enable (PTAPE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

Any of the port A pins can be configured as a KBI1 keyboard interrupt pin. Refer to the Keyboard Interrupt (KBI) Module chapter for more information about using port A pins as keyboard interrupt pins.

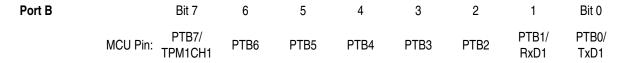

#### 6.3.2 Port B

Figure 6-2. Port B Pin Names

Port B is an 8-bit general-purpose I/O port with two pins shared with the SCI and one pin shared with the TPM. The port B output drivers are capable of high current drive.

Port B pins are available as general-purpose I/O pins controlled by the port B data (PTBD), data direction (PTBDD), and pullup enable (PTBPE) registers. Refer to Section 6.4, "Parallel I/O Controls," for more information about general-purpose I/O control.

When the SCI module is enabled, PTB0 and PTB1 function as the transmit (TxD1) and receive (RxD1) pins of the SCI. Refer to the Serial Communications Interface (SCI) Module chapter for more information about using PTB0 and PTB1 as SCI pins.

The TPM can be configured to use PTB7 as either an input capture, output compare, or PWM pin. Refer to the Timer/PWM Module (TPM) Module chapter for more information about using PTB7 as a timer pin.

### Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

### Table 7-2. HCS08 Instruction Set Summary (Sheet 2 of 7)

| Source                                                                                                          | Operation                                                  | December                                                              |   | ( |   | ec<br>CC |   |   | ess<br>de                                                               | Opcode | and                              | /cles <sup>1</sup>                   |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|---|---|---|----------|---|---|-------------------------------------------------------------------------|--------|----------------------------------|--------------------------------------|

| Form                                                                                                            | Operation                                                  | Description                                                           | v | н | ı | N        | z | С | Address                                                                 | Opc    | Oper                             | Bus Cycles <sup>1</sup>              |

| BCLR n,opr8a                                                                                                    | Clear Bit n in Memory                                      | Mn ← 0                                                                | _ | _ | _ | _        | _ | _ | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b6) |        | dd<br>dd<br>dd<br>dd<br>dd<br>dd | 55555555                             |

| BCS rel                                                                                                         | Branch if Carry Bit Set (Same as BLO)                      | Branch if (C) = 1                                                     | - | - | - | -        | - | - | REL                                                                     | 25     | rr                               | 3                                    |

| BEQ rel                                                                                                         | Branch if Equal                                            | Branch if (Z) = 1                                                     | - | _ | - | -        | - | - | REL                                                                     | 27     | rr                               | 3                                    |

| BGE rel                                                                                                         | Branch if Greater Than or<br>Equal To<br>(Signed Operands) | Branch if $(N \oplus V) = 0$                                          | - | - | - | _        | - | - | REL                                                                     | 90     | rr                               | 3                                    |

| BGND                                                                                                            | Enter Active Background if ENBDM = 1                       | Waits For and Processes BDM<br>Commands Until GO, TRACE1, or<br>TAGGO | - | - | - | -        | - | - | INH                                                                     | 82     |                                  | 5+                                   |

| BGT rel                                                                                                         | Branch if Greater Than (Signed Operands)                   | Branch if (Z)   (N $\oplus$ V) = 0                                    | - | - | - | -        | - | - | REL                                                                     | 92     | rr                               | 3                                    |

| BHCC rel                                                                                                        | Branch if Half Carry Bit<br>Clear                          | Branch if (H) = 0                                                     | - | - | - | -        | - | - | REL                                                                     | 28     | rr                               | 3                                    |

| BHCS rel                                                                                                        | Branch if Half Carry Bit<br>Set                            | Branch if (H) = 1                                                     | - | - | - | -        | - | - | REL                                                                     | 29     | rr                               | 3                                    |

| BHI rel                                                                                                         | Branch if Higher                                           | Branch if (C)   (Z) = 0                                               | - | _ | - | -        | - | - | REL                                                                     | 22     | rr                               | 3                                    |

| BHS rel                                                                                                         | Branch if Higher or Same (Same as BCC)                     | Branch if (C) = 0                                                     | - | - | - | -        | - | - | REL                                                                     | 24     | rr                               | 3                                    |

| BIH rel                                                                                                         | Branch if IRQ Pin High                                     | Branch if IRQ pin = 1                                                 | - | _ | - | -        | - | - | REL                                                                     | 2F     | rr                               | 3                                    |

| BIL rel                                                                                                         | Branch if IRQ Pin Low                                      | Branch if IRQ pin = 0                                                 | - | _ | - | -        | - | - | REL                                                                     | 2E     | rr                               | 3                                    |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test                                                   | (A) & (M)<br>(CCR Updated but Operands<br>Not Changed)                | 0 | _ | _ |          |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                     |        | dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 |

| BLE rel                                                                                                         | Branch if Less Than<br>or Equal To<br>(Signed Operands)    | Branch if (Z)   $(N \oplus V) = 1$                                    | - | - | _ | _        | - | - | REL                                                                     | 93     | rr                               | 3                                    |

| BLO rel                                                                                                         | Branch if Lower<br>(Same as BCS)                           | Branch if (C) = 1                                                     | - | - | - | -        | - | - | REL                                                                     | 25     | rr                               | 3                                    |

| BLS rel                                                                                                         | Branch if Lower or Same                                    | Branch if (C)   (Z) = 1                                               | - | _ | - | -        | - | - | REL                                                                     | 23     | rr                               | 3                                    |

| BLT rel                                                                                                         | Branch if Less Than<br>(Signed Operands)                   | Branch if $(N \oplus V) = 1$                                          | - | - | - | -        | - | - | REL                                                                     | 91     | rr                               | 3                                    |

| BMC rel                                                                                                         | Branch if Interrupt Mask<br>Clear                          | Branch if (I) = 0                                                     | - | - | - | -        | - | - | REL                                                                     | 2C     | rr                               | 3                                    |

| BMI rel                                                                                                         | Branch if Minus                                            | Branch if (N) = 1                                                     | - | - | - | -        | - | - | REL                                                                     | 2B     | rr                               | 3                                    |

| BMS rel                                                                                                         | Branch if Interrupt Mask<br>Set                            | Branch if (I) = 1                                                     | - | - | - | -        | - | - | REL                                                                     | 2D     | rr                               | 3                                    |

| BNE rel                                                                                                         | Branch if Not Equal                                        | Branch if (Z) = 0                                                     | - | _ | - | -        | - | - | REL                                                                     | 26     | rr                               | 3                                    |

| BPL rel                                                                                                         | Branch if Plus                                             | Branch if (N) = 0                                                     | - | _ | - | -        | _ | - | REL                                                                     | 2A     | rr                               | 3                                    |

| BRA rel                                                                                                         | Branch Always                                              | No Test                                                               | - | _ | - | -        | - | - | REL                                                                     | 20     | rr                               | 3                                    |

### Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

Table 7-3. Opcode Map (Sheet 2 of 2)

| Bit-Manipulation | Branch | Read | I-Modify-Write                   | Control |                        |                         | Register                | /Memory                |                        |                                  |

|------------------|--------|------|----------------------------------|---------|------------------------|-------------------------|-------------------------|------------------------|------------------------|----------------------------------|

|                  |        |      | 9E60 6<br>NEG<br>3 SP1           |         |                        |                         |                         | 4 SP2                  | SUB<br>3 SP1           |                                  |

|                  |        |      | 9E61 6<br>CBEQ<br>4 SP1          |         |                        |                         |                         | 4 SP2                  | CMP<br>3 SP1           |                                  |

|                  |        |      |                                  |         |                        |                         |                         | 4 SP2                  | SBC<br>3 SP1           |                                  |

|                  |        |      | 9E63 6<br>COM<br>3 SP1           |         |                        |                         |                         | 9ED3 5<br>CPX<br>4 SP2 | 9EE3 4<br>CPX<br>3 SP1 | 9EF3 6<br>CPHX<br>3 SP1          |

|                  |        |      | 9E64 6<br>LSR<br>3 SP1           |         |                        |                         |                         | 9ED4 5<br>AND<br>4 SP2 | 9EE4 4<br>AND<br>3 SP1 |                                  |

|                  |        |      |                                  |         |                        |                         |                         | 9ED5 5<br>BIT<br>4 SP2 | 9EE5 4<br>BIT<br>3 SP1 |                                  |

|                  |        |      | 9E66 6<br>ROR<br>3 SP1           |         |                        |                         |                         | 9ED6 5<br>LDA<br>4 SP2 | 9EE6 4<br>LDA<br>3 SP1 |                                  |

|                  |        |      | 9E67 6<br>ASR<br>3 SP1           |         |                        |                         |                         | 4 SP2                  | STA<br>3 SP1           |                                  |

|                  |        |      | 9E68 6<br>LSL<br>3 SP1           |         |                        |                         |                         | 9ED8 5<br>EOR<br>4 SP2 | 9EE8 4<br>EOR<br>3 SP1 |                                  |

|                  |        |      | 9E69 6<br>ROL<br>3 SP1           |         |                        |                         |                         | 9ED9 5<br>ADC<br>4 SP2 | 9EE9 4<br>ADC<br>3 SP1 |                                  |

|                  |        |      | 9E6A 6<br>DEC<br>3 SP1<br>9E6B 8 |         |                        |                         |                         | 9EDA 5<br>ORA<br>4 SP2 | ORA<br>3 SP1           |                                  |

|                  |        |      | DBNZ  <br>4 SP1                  |         |                        |                         |                         | 9EDB 5<br>ADD<br>4 SP2 | ADD                    |                                  |

|                  |        |      | 9E6C 6<br>INC<br>3 SP1           |         |                        |                         |                         |                        |                        |                                  |

|                  |        |      | 9E6D 5<br>TST<br>3 SP1           |         |                        |                         |                         |                        |                        |                                  |

|                  |        |      |                                  |         | 9EAE 5<br>LDHX<br>2 IX | 9EBE 6<br>LDHX<br>4 IX2 | 9ECE 5<br>LDHX<br>3 IX1 | 9EDE 5<br>LDX<br>4 SP2 | 9EEE 4<br>LDX<br>3 SP1 | 9EFE 5<br>LDHX<br>3 SP1          |

|                  |        |      | 9E6F 6<br>CLR<br>3 SP1           |         |                        |                         |                         | 9EDF 5<br>STX<br>4 SP2 | 9EEF 4<br>STX<br>3 SP1 | 3 SP1<br>9EFF 5<br>STHX<br>3 SP1 |

| INH  | Inherent   | REL  | Relative               | SP1  | Stack Pointer, 8-Bit Offset  |

|------|------------|------|------------------------|------|------------------------------|

| IMM  | Immediate  | IX   | Indexed, No Offset     | SP2  | Stack Pointer, 16-Bit Offset |

| DIR  | Direct     | IX1  | Indexed, 8-Bit Offset  | IX+  | Indexed, No Offset with      |

| EXT  | Extended   | IX2  | Indexed, 16-Bit Offset |      | Post Increment               |

| DD   | DIR to DIR | IMD  | IMM to DIR             | IX1+ | Indexed, 1-Byte Offset with  |

| IX+D | IX+ to DIR | DIX+ | DIR to IX+             |      | Post Increment               |

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal NEG Number of Bytes SP1 HCS08 Cycles Instruction Mnemonic Addressing Mode

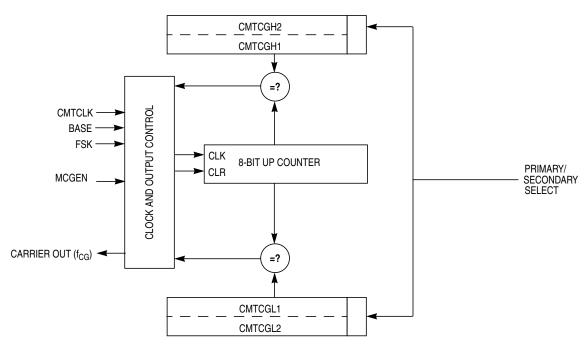

Figure 8-3. Carrier Generator Block Diagram

The high/low time counter is an 8-bit up counter. After each increment, the contents of the counter are compared with the appropriate high or low count value register. When the compare value is reached, the counter is reset to a value of \$01, and the compare is redirected to the other count value register.

Assuming that the high time count compare register is currently active, a valid compare will cause the carrier output to be driven low. The counter will continue to increment (starting at reset value of \$01). When the value stored in the selected low count value register is reached, the counter will again be reset and the carrier output will be driven high.

The cycle repeats, automatically generating a periodic signal that is directed to the modulator. The lowest frequency (maximum period) and highest frequency (minimum period) that can be generated are defined as:

$$f_{\text{max}} = f_{\text{CMTCLK}} \div (2 \text{ x 1}) \text{ Hz}$$

Eqn. 8-1

111

$$f_{min} = f_{CMTCLK} \div (2 \times (2^8 - 1)) Hz$$

Eqn. 8-2

In the general case, the carrier generator output frequency is:

$$f_{CG} = f_{CMTCLK} \div (Highcount + Lowcount) Hz$$

Eqn. 8-3

Where: 0 < High count < 256 and

0 < Lowcount < 256

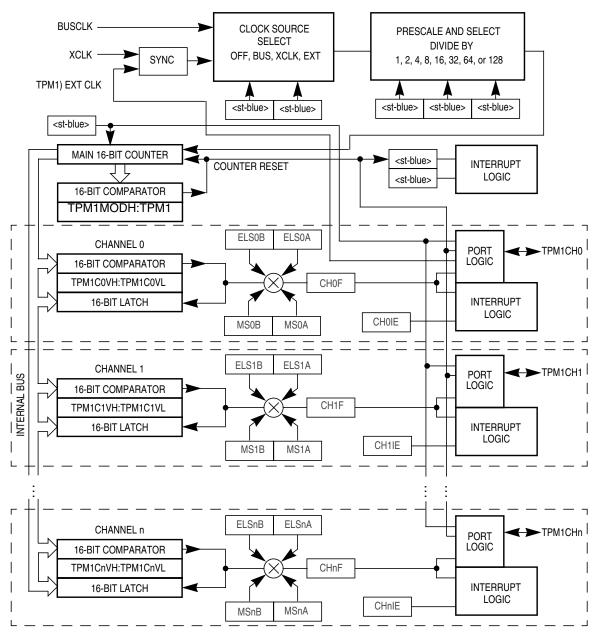

# Chapter 10 Timer/PWM Module (S08TPMV1)

### 10.1 Introduction

The MC9S08RC/RD/RE/RG includes a timer/PWM (TPM) module that supports traditional input capture, output compare, or buffered edge-aligned pulse-width modulation (PWM) on each channel. A control bit in the TPM configures both channels in the timer to operate as center-aligned PWM functions. Timing functions in the TPM are based on a 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications. The MC9S08RC/RD/RE/RG devices do not have a separate fixed internal clock source (XCLK). If the XCLK source is selected using the CLKSA and CLKSB control bits (see Table 10-2), the TPM will use the BUSCLK.

### 10.2 Features

Timer system features include:

- Two separate channels:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- The TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on both channels

- Clock source to prescaler for the TPM is selectable between the bus clock or an external pin:

- Prescale taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- External clock input shared with TPM1CH0 timer channel pin

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus terminal count interrupt

### 10.3 TPM Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPM1CHn where n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information). Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture,

#### Timer/PWM (TPM)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPM1CNTH or TPM1CNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPM1CNTH or TPM1CNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

### 10.5.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

### 10.5.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPM1CnVH:TPM1CnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPM1CnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

### 10.5.2.2 Output Compare Mode

With the output compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel value registers of an output compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel value registers only after both 8-bit bytes of a 16-bit register have been written. This coherency sequence can be manually reset by writing to the channel status/control register (TPM1CnSC).

An output compare event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

### 10.5.2.3 Edge-Aligned PWM Mode

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS = 0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the setting in the modulus register (TPM1MODH:TPM1MODL). The duty cycle is determined by the setting in the timer channel value

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

### 10.7.3 Timer Counter Modulo Registers (TPM1MODH:TPM1MODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from \$0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPM1MODH or TPM1MODL inhibits the TOF bit and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to \$0000, which results in a free-running timer counter (modulo disabled).

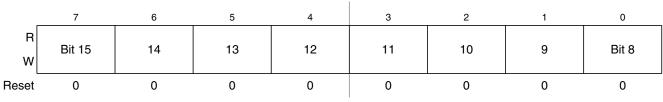

Figure 10-8. Timer Counter Modulo Register High (TPM1MODH)

Figure 10-9. Timer Counter Modulo Register Low (TPM1MODL)

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

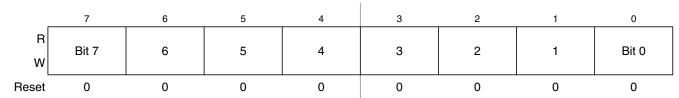

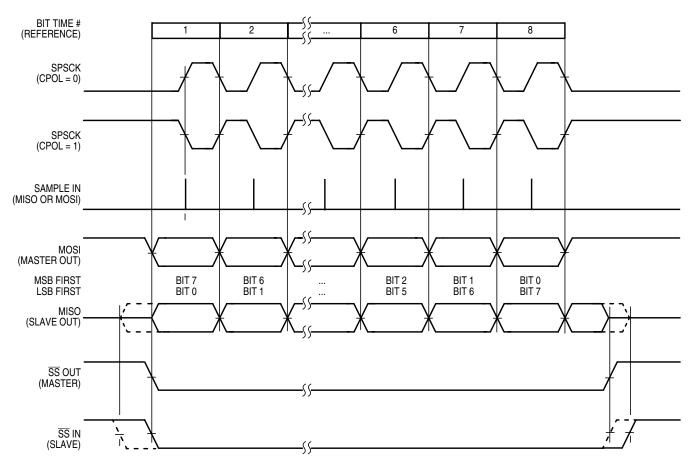

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS1}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 13-6 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 13-6. SPI Clock Formats (CPHA = 0)

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Serial Peripheral Interface (SPI) Module

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS1}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

### 13.3.2 SPI Pin Controls

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

### 13.3.2.1 SPSCK1 — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

### 13.3.2.2 MOSI1 — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

### 13.3.2.3 MISO1 — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

### 13.3.2.4 SS1 — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

Serial Peripheral Interface (SPI) Module

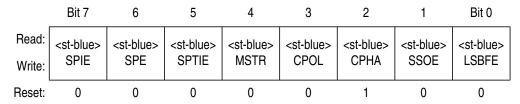

### 13.4.1 SPI Control Register 1 (SPI1C1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 13-7. SPI Control Register 1 (SPI1C1)

SPIE — SPI Interrupt Enable (for SPRF and MODF)

This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.

- 1 = When SPRF or MODF is 1, request a hardware interrupt.

- 0 = Interrupts from SPRF and MODF inhibited (use polling).

### SPE — SPI System Enable

Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.

- 1 = SPI system enabled.

- 0 = SPI system inactive.

### SPTIE — SPI Transmit Interrupt Enable

This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).

- 1 = When SPTEF is 1, hardware interrupt requested.

- 0 = Interrupts from SPTEF inhibited (use polling).

#### MSTR — Master/Slave Mode Select

- 1 = SPI module configured as a master SPI device.

- 0 = SPI module configured as a slave SPI device.

#### CPOL — Clock Polarity

This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 13.3.1, "SPI Clock Formats," for more details.

- 1 = Active-low SPI clock (idles high).

- 0 = Active-high SPI clock (idles low).

### CPHA — Clock Phase

This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 13.3.1, "SPI Clock Formats," for more details.

- 1 = First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer.

- 0 = First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer.

#### **Electrical Characteristics**

Table A-5. DC Characteristics (Temperature Range = -40 to 85°C Ambient) (continued)

| Parameter                                                                                                                                                                                            | Symbol              | Min                   | Typical | Max                       | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------|---------------------------|----------|

| Maximum low-voltage safe state re-arm <sup>(3)</sup>                                                                                                                                                 | V <sub>REARM</sub>  | _                     | _       | 3.0                       | V        |

| Input high voltage (V <sub>DD</sub> > 2.3 V) (all digital inputs)                                                                                                                                    | V <sub>IH</sub>     | $0.70 \times V_{DD}$  |         | _                         | V        |

| Input high voltage (1.8 V ≤ V <sub>DD</sub> ≤ 2.3 V) (all digital inputs)                                                                                                                            | V <sub>IH</sub>     | $0.85 \times V_{DD}$  |         | _                         | V        |

| Input low voltage (V <sub>DD</sub> > 2.3 V) (all digital inputs)                                                                                                                                     | V <sub>IL</sub>     | _                     |         | 0.35 ×<br>V <sub>DD</sub> | V        |

| Input low voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                                   | V <sub>IL</sub>     | _                     |         | 0.30 ×<br>V <sub>DD</sub> | V        |

| Input hysteresis (all digital inputs)                                                                                                                                                                | V <sub>hys</sub>    | $0.06 \times V_{DD}$  |         | _                         | V        |

| Input leakage current (Per pin) $V_{In} = V_{DD}$ or $V_{SS}$ , all input only pins                                                                                                                  | II <sub>In</sub> I  | _                     | 0.025   | 1.0                       | μА       |

| High impedance (off-state) leakage current (per pin) $V_{In} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                                | ll <sub>OZ</sub> l  | _                     | 0.025   | 1.0                       | μА       |

| Internal pullup resistors <sup>(4) (5)</sup>                                                                                                                                                         | R <sub>PU</sub>     | 17.5                  |         | 52.5                      | κW       |

| Internal pulldown resistor (IRQ)                                                                                                                                                                     | R <sub>PD</sub>     | 17.5                  |         | 52.5                      | κW       |

| Output high voltage (V <sub>DD</sub> ≥ 1.8 V)<br>I <sub>OH</sub> = −2 mA (ports A, C, D and E)                                                                                                       | V <sub>OH</sub>     | V <sub>DD</sub> - 0.5 |         | _                         | V        |

| Output high voltage (port B and IRO) $I_{OH} = -10 \text{ mA } (V_{DD} \ge 2.7 \text{ V})$ $I_{OH} = -6 \text{ mA } (V_{DD} \ge 2.3 \text{ V})$ $I_{OH} = -3 \text{ mA } (V_{DD} \ge 1.8 \text{ V})$ |                     | V <sub>DD</sub> – 0.5 |         | _<br>_<br>_               |          |

| Maximum total I <sub>OH</sub> for all port pins                                                                                                                                                      | II <sub>OHT</sub> I | _                     |         | 60                        | mA       |

| Output low voltage ( $V_{DD} \ge 1.8 \text{ V}$ )<br>$I_{OL} = 2.0 \text{ mA (ports A, C, D and E)}$                                                                                                 | V <sub>OL</sub>     | _                     |         | 0.5                       | V        |

| Output low voltage (port B) $I_{OL} = 10.0 \text{ mA } (V_{DD} \ge 2.7 \text{ V})$ $I_{OL} = 6 \text{ mA } (V_{DD} \ge 2.3 \text{ V})$ $I_{OL} = 3 \text{ mA } (V_{DD} \ge 1.8 \text{ V})$           |                     | _<br>_<br>_           |         | 0.5<br>0.5<br>0.5         |          |

| Output low voltage (IRO) $I_{OL} = 16 \text{ mA } (V_{DD} \ge 2.7 \text{ V})$ $I_{OL} = 6 \text{ mA } (V_{DD} \ge 2.3 \text{ V})$ $I_{OL} = 3 \text{ mA } (V_{DD} \ge 1.8 \text{ V})$                |                     | _<br>_<br>_           |         | 1.2<br>1.2<br>1.2         |          |

| Maximum total I <sub>OL</sub> for all port pins                                                                                                                                                      | I <sub>OLT</sub>    | _                     |         | 60                        | mA       |

| dc injection current <sup>(2), (6), (7), (8),, (9)</sup> $V_{IN} < V_{SS}, V_{IN} > V_{DD}$ Single pin limit Total MCU limit, includes sum of all stressed pins                                      | II <sub>IC</sub> I  |                       |         | 0.2<br>5                  | mA<br>mA |

| Input capacitance (all non-supply pins)                                                                                                                                                              | C <sub>In</sub>     | _                     |         | 7                         | pF       |

- 1. RAM will retain data down to POR voltage. RAM data not guaranteed to be valid following a POR.

- 2. This parameter is characterized and not tested on each device.

- If SAFE bit is set, V<sub>DD</sub> must be above re-arm voltage to allow MCU to accept interrupts, refer to Section 5.6, "Low-Voltage Detect (LVD) System."

- 4. Measurement condition for pull resistors:  $V_{In} = V_{SS}$  for pullup and  $V_{In} = V_{DD}$  for pulldown.

- 5. The PTA0 pullup resistor may not pull up to the specified minimum  $V_{IH}$ . However, all ports are functionally tested to guarantee that a logic 1 will be read on any port input when the pullup is enabled and no dc load is present on the pin.

- 6. All functional non-supply pins are internally clamped to  $\rm V_{SS}$  and  $\rm V_{DD}$

#### **Electrical Characteristics**

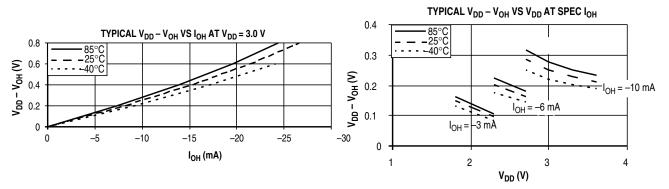

Figure A-4. Typical High-Side Driver (Source) Characteristics (Port B and IRO)

Figure A-5. Typical High-Side (Source) Characteristics (Ports A, C, D and E)

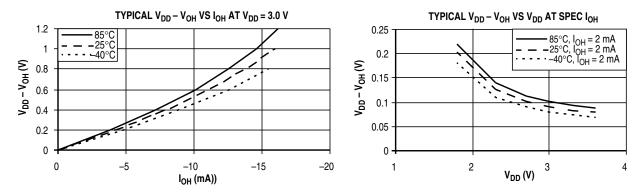

### A.8 Oscillator Characteristics

Table A-8. OSC Electrical Specifications (Temperature Range = -40 to 85°C Ambient)

| Characteristic    | Symbol                           | Min                 | Typ <sup>(1)</sup> | Max | Unit |  |

|-------------------|----------------------------------|---------------------|--------------------|-----|------|--|

| Frequency         | f <sub>osc</sub>                 | 1                   | _                  | 16  | MHz  |  |

| Load Capacitors   | C <sub>1</sub><br>C <sub>2</sub> | Note <sup>(2)</sup> |                    |     |      |  |

| Feedback resistor | R <sub>F</sub>                   |                     | 1                  |     | ΜΩ   |  |

<sup>1.</sup> Data in typical column was characterized at 3.0 V, 25°C or is typical recommended value.

### A.9 AC Characteristics

This section describes ac timing characteristics for each peripheral system.

## A.9.1 Control Timing

**Table A-9. Control Timing**

| Parameter                                              | Symbol                                | Min                  | Typical | Max  | Unit |

|--------------------------------------------------------|---------------------------------------|----------------------|---------|------|------|

| Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> ) | f <sub>Bus</sub>                      | dc                   | _       | 8    | MHz  |

| Real time interrupt internal oscillator period         | t <sub>RTI</sub>                      | 400                  |         | 1600 | μs   |

| External reset pulse width <sup>(1)</sup>              | t <sub>extrst</sub>                   | 1.5 t <sub>cyc</sub> |         | _    | ns   |

| Reset low drive <sup>(2)</sup>                         | t <sub>rstdrv</sub>                   | 34 t <sub>cyc</sub>  |         | _    | ns   |

| Active background debug mode latch setup time          | t <sub>MSSU</sub>                     | 25                   |         | _    | ns   |

| Active background debug mode latch hold time           | t <sub>MSH</sub>                      | 25                   |         | _    | ns   |

| IRQ pulse width <sup>(3)</sup>                         | t <sub>ILIH</sub>                     | 1.5 t <sub>cyc</sub> |         | _    | ns   |

| Port rise and fall time (load = 50 pF) <sup>(4)</sup>  | t <sub>Rise</sub> , t <sub>Fall</sub> | _                    | 3       |      | ns   |

<sup>1.</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>2.</sup> See crystal or resonator manufacturer's recommendation.

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DICOMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

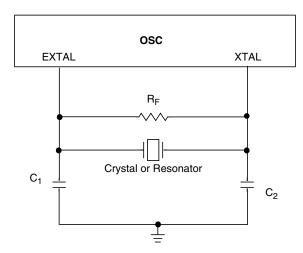

# MECHANICAL DUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASS23225W

PAGE: 824D

REV: B

TITLE:

44 LD TQFP, 10 X 10 PKG, 0.8 PITCH, 1.4 THICK CASE NUMBER: 824D-03

STANDARD: JEDEC MS-026-BCB

PACKAGE CODE: 8256

SHEET:

1 DF 3

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS

ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED.

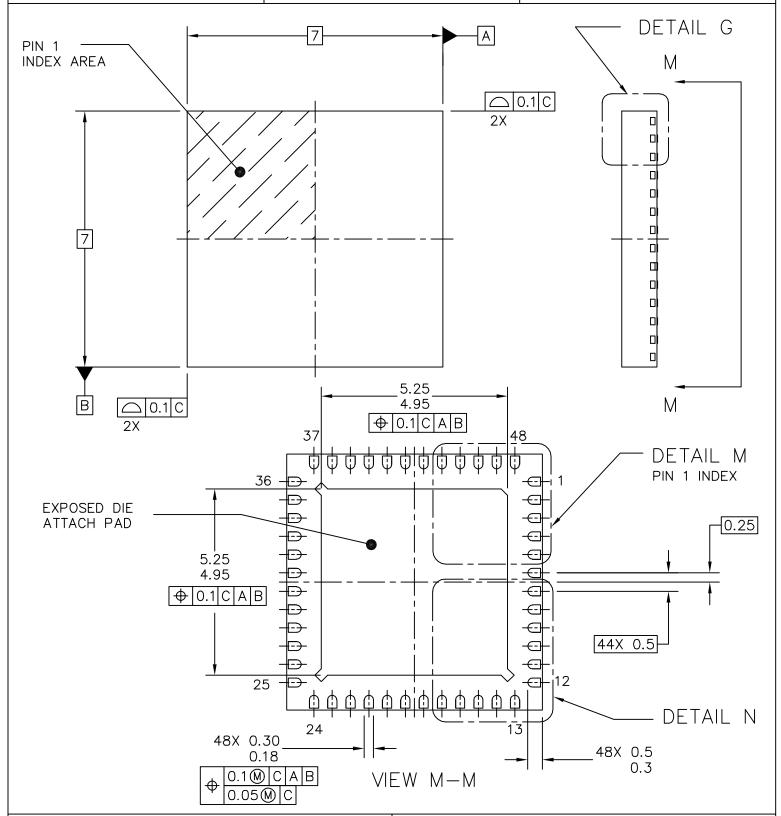

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARH99048A

PAGE: 1314

REV: D

TITLE: THERMALLY ENHANCED QUAD FLAT NON-LEADED PACKAGE (QFN) 48 TERMINAL, 0.5 PITCH (7 X 7 X 1) CASE NUMBER: 1314-03

STANDARD: JEDEC-MO-220 VKKD-2

PACKAGE CODE: 6152 | SHEET: 1 OF 5