Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI                                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08re16fde |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List of Chapters**

| Chapter 1  | Introduction                                 | 15  |

|------------|----------------------------------------------|-----|

| Chapter 2  | Pins and Connections                         | 19  |

| Chapter 3  | Modes of Operation                           | 29  |

| Chapter 4  | Memory                                       | 35  |

| Chapter 5  | Resets, Interrupts, and System Configuration | 57  |

| Chapter 6  | Parallel Input/Output                        | 73  |

| Chapter 7  | Central Processor Unit (S08CPUV2)            | 87  |

| Chapter 8  | Carrier Modulator Timer (S08CMTV1)           | 107 |

| Chapter 9  | Keyboard Interrupt (S08KBIV1)                | 123 |

| Chapter 10 | Timer/PWM Module (S08TPMV1)                  | 129 |

| Chapter 11 | Serial Communications Interface (S08SCIV1)   | 145 |

| Chapter 12 | Serial Communications Interface (S08SCIV1)   | 147 |

| Chapter 13 | Serial Peripheral Interface (S08SPIV3)       | 163 |

| Chapter 14 | Analog Comparator (S08ACMPV1)                | 179 |

| Chapter 15 | Development Support                          | 183 |

| Appendix A | Electrical Characteristics                   | 205 |

| Appendix B | Ordering Information and Mechanical Drawings | 219 |

Freescale Semiconductor 5

| Section Number |                  | imber Title                                           | Page |

|----------------|------------------|-------------------------------------------------------|------|

|                |                  | Chapter 11 Serial Communications Interface (S08SCIV1) |      |

| 11.1           | Introduc         | tion                                                  | 145  |

|                |                  |                                                       |      |

|                |                  | Chapter 12                                            |      |

| 10.1           | T., 4.,          | Serial Communications Interface (S08SCIV1)            | 1.47 |

| 12.1           |                  | tion                                                  |      |

|                | 12.1.1<br>12.1.2 | Features                                              |      |

|                | 12.1.2           | Block Diagram                                         |      |

| 12.2           |                  | Definition                                            |      |

| 12,2           | 12.2.1           | SCI Baud Rate Registers (SCI1BDH, SCI1BHL)            |      |

|                | 12.2.2           | SCI Control Register 1 (SCI1C1)                       |      |

|                | 12.2.3           | SCI Control Register 2 (SCI1C2)                       |      |

|                | 12.2.4           | SCI Status Register 1 (SCI1S1)                        |      |

|                | 12.2.5           | SCI Status Register 2 (SCI1S2)                        |      |

|                | 12.2.6           | SCI Control Register 3 (SCI1C3)                       |      |

|                | 12.2.7           | SCI Data Register (SCI1D)                             |      |

| 12.3           | Function         | al Description                                        |      |

|                | 12.3.1           | Baud Rate Generation                                  |      |

|                | 12.3.2           | Transmitter Functional Description                    | 157  |

|                |                  | 12.3.2.1 Send Break and Queued Idle                   | 158  |

|                | 12.3.3           | Receiver Functional Description                       |      |

|                |                  | 12.3.3.1 Data Sampling Technique                      |      |

|                |                  | 12.3.3.2 Receiver Wakeup Operation                    | 159  |

|                | 12.3.4           | Interrupts and Status Flags                           |      |

|                | 12.3.5           | Additional SCI Functions                              |      |

|                |                  | 12.3.5.1 8- and 9-Bit Data Modes                      |      |

|                |                  | 12.3.5.2 Stop Mode Operation                          |      |

|                |                  | 12.3.5.3 Loop Mode                                    |      |

|                |                  | 12.3.5.4 Single-Wire Operation                        | 162  |

|                |                  | Chapter 13                                            |      |

|                |                  | Serial Peripheral Interface (S08SPIV3)                |      |

| 13 1           | Fanturas         | Serial Peripheral Interface (3003F1V3)                | 164  |

|                |                  | iagrams                                               |      |

| 13.4           | 13.2.1           |                                                       |      |

|                | 13.2.1           | SPI Module Block Diagram                              |      |

|                | 13.2.3           | SPI Baud Rate Generation                              |      |

| 13.3           |                  | al Description                                        |      |

| 10.0           | 13.3.1           | SPI Clock Formats                                     |      |

|                | 13.3.2           |                                                       |      |

|                |                  | 13.3.2.1 SPSCK1 — SPI Serial Clock                    |      |

|                |                  | 13.3.2.2 MOSI1 — Master Data Out, Slave Data In       |      |

|                |                  |                                                       |      |

|                |                  | MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11               |      |

12 Freescale Semiconductor

| Section  | Number      | Title                                     | Page |

|----------|-------------|-------------------------------------------|------|

| 15.      | .4.3 DBG Re | egisters and Control Bits                 | 199  |

|          | 15.4.3.1    | Debug Comparator A High Register (DBGCAH) | 199  |

|          |             | Debug Comparator A Low Register (DBGCAL)  |      |

|          |             | Debug Comparator B High Register (DBGCBH) |      |

|          |             | Debug Comparator B Low Register (DBGCBL)  |      |

|          |             | Debug FIFO High Register (DBGFH)          |      |

|          |             | Debug FIFO Low Register (DBGFL)           |      |

|          |             | Debug Control Register (DBGC)             |      |

|          |             | Debug Trigger Register (DBGT)             |      |

|          | 15.4.3.9    | Debug Status Register (DBGS)              | 203  |

|          |             | Appendix A                                |      |

|          |             | Electrical Characteristics                |      |

|          |             |                                           |      |

|          |             | n Ratings                                 |      |

|          |             | istics                                    |      |

|          |             | arge (ESD) Protection Characteristics     |      |

|          |             | S                                         |      |

|          | . •         | aracteristics                             |      |

|          | -           | or (ACMP) Electricals                     |      |

|          |             | 5                                         |      |

|          |             | iming                                     |      |

|          |             | VM (TPM) Module Timing                    |      |

|          |             | ng                                        |      |

|          |             | ions                                      |      |

|          | •           | Appendix B                                |      |

|          | Ord         | ering Information and Mechanical Drawings |      |

| B.1 Orde |             | ion                                       | 210  |

|          | _           | ngs                                       |      |

|          |             |                                           |      |

# **Chapter 4 Memory**

#### 4.1 MC9S08RC/RD/RE/RG Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08RC/RD/RE/RG series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (\$0000 through \$0045 for 32K and 60K parts, and \$0000 through \$003F for 16K and 8K parts)

- High-page registers (\$1800 through \$182B)

- Nonvolatile registers (\$FFB0 through \$FFBF)

# Chapter 6 Parallel Input/Output

#### 6.1 Introduction

This section explains software controls related to parallel input/output (I/O). The MC9S08RC/RD/RE/RG has five I/O ports that include a total of 39 general-purpose I/O pins (two of these pins are output only and one pin is input only). Not all of the ports are available in all packages. See Chapter 2, "Pins and Connections," for more information about the logic and hardware aspects of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, external interrupts, or keyboard interrupts. When these other modules are not controlling the port pins, they revert to general-purpose I/O control. For each I/O pin, a port data bit provides access to input (read) and output (write) data. A data direction bit controls the direction of the pin and a pullup enable bit enables an internal pullup device (if the pin is configured as an input).

#### NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unconnected pins to outputs so the pins do not float.

#### 6.2 Features

Parallel I/O features for the MC9S08RC/RD/RE/RG MCUs, depending on specific device and package choice, include:

- A total of 39 general-purpose I/O pins in five ports (two pins are output only, one is input only)

- High-current drivers on port B pins

- Hysteresis input buffers on all inputs

- Software-controlled pullups on each input pin

- Eight port A pins shared with KBI1

- Eight port B pins shared with SCI and TPMCH1

- Eight port C pins shared with KBI2 and SPI

- Seven port D pins shared with TPMCH0, ACMP, IRQ, RESET, and BKGD/MS

- Eight port E pins

of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

#### 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

#### 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

#### 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

### 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

#### 7.3.5 Extended Addressing Mode (EXT)

In extended addressing mode, the full 16-bit address of the operand is located in the next two bytes of program memory after the opcode (high byte first).

#### 7.3.6 Indexed Addressing Mode

Indexed addressing mode has seven variations including five that use the 16-bit H:X index register pair and two that use the stack pointer as the base reference.

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Table 7-2. HCS08 Instruction Set Summary (Sheet 5 of 7)

| Source                                                                                                          | 2                                          | Description                                                                                                                                                                                                                                                     |    | Effect on CCR |   |   |   |   | de<br>de                                            | and                                              | and                                       | /cles <sup>1</sup>                   |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|---|---|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                                            | Operation                                  |                                                                                                                                                                                                                                                                 |    | Н             | I | N | z | С | Address                                             | Орсоде                                           | Operand                                   | Bus Cycles <sup>1</sup>              |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX ,X<br>LDX oprx16,SP<br>LDX oprx8,SP | Load X (Index Register<br>Low) from Memory | $X \leftarrow (M)$                                                                                                                                                                                                                                              | 0  | _             | _ |   |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | DE<br>EE<br>FE<br>9EDE<br>9EEE                   | dd<br>hh II<br>ee ff<br>ff<br>ee ff<br>ff | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 |

| LSL opr8a<br>LSLA<br>LSLX<br>LSL oprx8,X<br>LSL ,X<br>LSL oprx8,SP                                              | Logical Shift Left<br>(Same as ASL)        | © → 0 b0                                                                                                                                                                                                                                                        |    | _             | _ |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | ff                                        | 5<br>1<br>1<br>5<br>4<br>6           |

| LSR opr8a<br>LSRA<br>LSRX<br>LSR oprx8,X<br>LSR ,X<br>LSR oprx8,SP                                              | Logical Shift Right                        | 0 - C<br>b7 b0                                                                                                                                                                                                                                                  |    | _             | _ | 0 |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               |                                           | 5<br>1<br>1<br>5<br>4<br>6           |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                            | Move                                       | $(M)_{destination} \leftarrow (M)_{source}$<br>$H:X \leftarrow (H:X) + 0x0001 \text{ in}$<br>IX+/DIR  and  DIR/IX+  Modes                                                                                                                                       | 0  | _             | _ |   |   | _ | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR            | 5E                                               | ii dd                                     | 5<br>5<br>4<br>5                     |

| MUL                                                                                                             | Unsigned multiply                          | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                                                                                 | -  | 0             | - | _ | - | 0 | INH                                                 | 42                                               |                                           | 5                                    |

| NEG opr8a<br>NEGA<br>NEGX<br>NEG oprx8,X<br>NEG oprx8,SP                                                        | Negate<br>(Two's Complement)               | $\begin{array}{l} M \longleftarrow -(M) = 0x00 - (M) \\ A \longleftarrow -(A) = 0x00 - (A) \\ X \longleftarrow -(X) = 0x00 - (X) \\ M \longleftarrow -(M) = 0x00 - (M) \\ M \longleftarrow -(M) = 0x00 - (M) \\ M \longleftarrow -(M) = 0x00 - (M) \end{array}$ |    | -             | _ |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               |                                           | 5<br>1<br>5<br>4<br>6                |

| NOP                                                                                                             | No Operation                               | Uses 1 Bus Cycle                                                                                                                                                                                                                                                | 1- | -             | _ | _ | - | - | INH                                                 | 9D                                               |                                           | 1                                    |

| NSA                                                                                                             | Nibble Swap<br>Accumulator                 | $A \leftarrow (A \text{\texttt{\texttt{[3:0]:}A}} \text{\texttt{\texttt{\texttt{[7:4]})}}$                                                                                                                                                                      | -  | -             | - | _ | - | - | INH                                                 | 62                                               |                                           | 1                                    |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator and Memory        | $A \leftarrow (A) \mid (M)$                                                                                                                                                                                                                                     | 0  | _             | _ |   |   | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EDA<br>9EEA | dd<br>hh II<br>ee ff<br>ff                | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 |

| PSHA                                                                                                            | Push Accumulator onto Stack                | Push (A); SP $\leftarrow$ (SP) – 0x0001                                                                                                                                                                                                                         | -  | -             | - | _ | - | _ | INH                                                 | 87                                               |                                           | 2                                    |

| PSHH                                                                                                            | Push H (Index Register<br>High) onto Stack | Push (H); SP ← (SP) – 0x0001                                                                                                                                                                                                                                    | -  | -             | - | - | - | - | INH                                                 | 8B                                               |                                           | 2                                    |

| PSHX                                                                                                            | Push X (Index Register Low) onto Stack     | Push (X); SP $\leftarrow$ (SP) – 0x0001                                                                                                                                                                                                                         | _  |               |   |   | _ |   | INH                                                 | 89                                               |                                           | 2                                    |

| PULA                                                                                                            | Pull Accumulator from<br>Stack             | $SP \leftarrow (SP + 0x0001);  Pull  (A)$                                                                                                                                                                                                                       | _  | _             | - | _ | _ | _ | INH                                                 | 86                                               |                                           | 3                                    |

| PULH                                                                                                            | Pull H (Index Register<br>High) from Stack | $SP \leftarrow (SP + 0x0001);  Pull  (H)$                                                                                                                                                                                                                       | _  |               | _ | _ | _ |   | INH                                                 | 8A                                               |                                           | 3                                    |

| PULX                                                                                                            | Pull X (Index Register<br>Low) from Stack  | $SP \leftarrow (SP + 0x0001);  Pull  (X)$                                                                                                                                                                                                                       |    | _             | _ | _ | _ | _ | INH                                                 | 88                                               |                                           | 3                                    |

| ROL opr8a<br>ROLA<br>ROLX<br>ROL oprx8,X<br>ROL ,X<br>ROL oprx8,SP                                              | Rotate Left through Carry                  | b7 b0                                                                                                                                                                                                                                                           |    | _             | _ |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | ff                                        | 5<br>1<br>1<br>5<br>4<br>6           |

Freescale Semiconductor \_ \_ 101

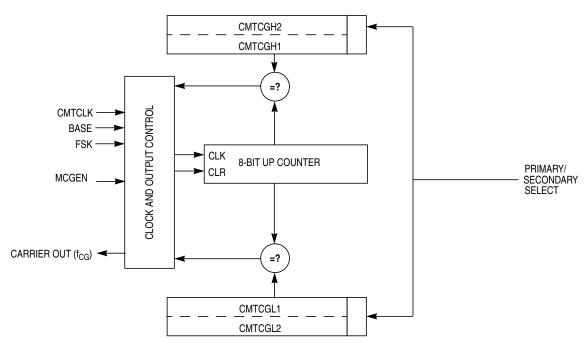

Figure 8-3. Carrier Generator Block Diagram

The high/low time counter is an 8-bit up counter. After each increment, the contents of the counter are compared with the appropriate high or low count value register. When the compare value is reached, the counter is reset to a value of \$01, and the compare is redirected to the other count value register.

Assuming that the high time count compare register is currently active, a valid compare will cause the carrier output to be driven low. The counter will continue to increment (starting at reset value of \$01). When the value stored in the selected low count value register is reached, the counter will again be reset and the carrier output will be driven high.

The cycle repeats, automatically generating a periodic signal that is directed to the modulator. The lowest frequency (maximum period) and highest frequency (minimum period) that can be generated are defined as:

$$f_{\text{max}} = f_{\text{CMTCLK}} \div (2 \text{ x 1}) \text{ Hz}$$

Eqn. 8-1

111

$$f_{min} = f_{CMTCLK} \div (2 \times (2^8 - 1)) Hz$$

Eqn. 8-2

In the general case, the carrier generator output frequency is:

$$f_{CG} = f_{CMTCLK} \div (Highcount + Lowcount) Hz$$

Eqn. 8-3

Where: 0 < High count < 256 and

0 < Lowcount < 256

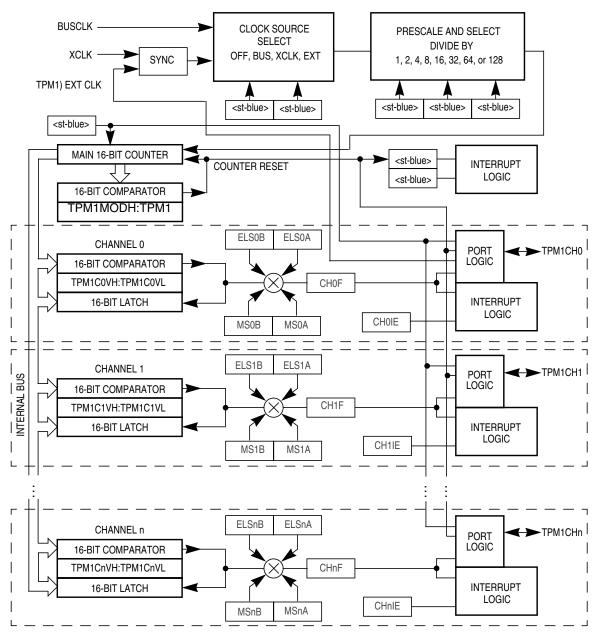

### Chapter 10 Timer/PWM Module (S08TPMV1)

#### 10.1 Introduction

The MC9S08RC/RD/RE/RG includes a timer/PWM (TPM) module that supports traditional input capture, output compare, or buffered edge-aligned pulse-width modulation (PWM) on each channel. A control bit in the TPM configures both channels in the timer to operate as center-aligned PWM functions. Timing functions in the TPM are based on a 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications. The MC9S08RC/RD/RE/RG devices do not have a separate fixed internal clock source (XCLK). If the XCLK source is selected using the CLKSA and CLKSB control bits (see Table 10-2), the TPM will use the BUSCLK.

#### 10.2 Features

Timer system features include:

- Two separate channels:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- The TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on both channels

- Clock source to prescaler for the TPM is selectable between the bus clock or an external pin:

- Prescale taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- External clock input shared with TPM1CH0 timer channel pin

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus terminal count interrupt

#### 10.3 TPM Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPM1CHn where n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information). Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture,

Freescale Semiconductor

# **Chapter 12 Serial Communications Interface (S08SCIV1)**

#### 12.1 Introduction

#### 12.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

#### 12.1.2 Modes of Operation

See Section 12.3, "Functional Description," for a detailed description of SCI operation in the different modes.

- 8- and 9- bit data modes

- Stop modes SCI is halted during all stop modes

- Loop modes

Serial Peripheral Interface (SPI) Module

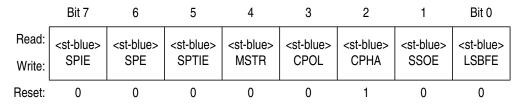

#### 13.4.1 SPI Control Register 1 (SPI1C1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 13-7. SPI Control Register 1 (SPI1C1)

SPIE — SPI Interrupt Enable (for SPRF and MODF)

This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.

- 1 = When SPRF or MODF is 1, request a hardware interrupt.

- 0 = Interrupts from SPRF and MODF inhibited (use polling).

#### SPE — SPI System Enable

Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.

- 1 = SPI system enabled.

- 0 = SPI system inactive.

#### SPTIE — SPI Transmit Interrupt Enable

This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).

- 1 = When SPTEF is 1, hardware interrupt requested.

- 0 = Interrupts from SPTEF inhibited (use polling).

#### MSTR — Master/Slave Mode Select

- 1 = SPI module configured as a master SPI device.

- 0 = SPI module configured as a slave SPI device.

#### CPOL — Clock Polarity

This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 13.3.1, "SPI Clock Formats," for more details.

- 1 = Active-low SPI clock (idles high).

- 0 = Active-high SPI clock (idles low).

#### CPHA — Clock Phase

This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 13.3.1, "SPI Clock Formats," for more details.

- 1 = First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer.

- 0 = First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer.

**Development Support**

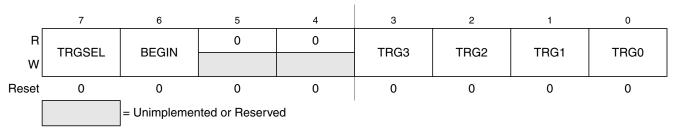

#### 15.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

Figure 15-8. Debug Trigger Register (DBGT)

**Table 15-5. DBGT Register Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TRGSEL     | Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.  O Trigger on access to compare address (force)  1 Trigger if opcode at compare address is executed (tag) |  |  |  |  |  |

| 6<br>BEGIN      | Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.  0 Data stored in FIFO until trigger (end trace)  1 Trigger initiates data storage (begin trace)                                                                                                             |  |  |  |  |  |

| 3:0<br>TRG[3:0] | Select Trigger Mode — Selects one of nine triggering modes, as described below.  0000 A-only  0001 A OR B  0010 A Then B  0011 Event-only B (store data)  0100 A then event-only B (store data)  0101 A AND B data (full mode)  0110 A AND NOT B data (full mode)  0111 Inside range: A ≤ address ≤ B  1000 Outside range: address < A or address > B  1001 – 1111 (No trigger)                                                                                                  |  |  |  |  |  |

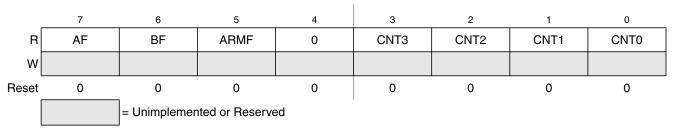

#### 15.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

Figure 15-9. Debug Status Register (DBGS)

**Table 15-6. DBGS Register Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>AF         | Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.  0 Comparator A has not matched  1 Comparator A match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 6<br>BF         | Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.  0 Comparator B has not matched 1 Comparator B match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 5<br>ARMF       | Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.  0 Debugger not armed 1 Debugger armed                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |  |  |  |  |  |

**Development Support**

1. Not defined but normally MSB of character just received

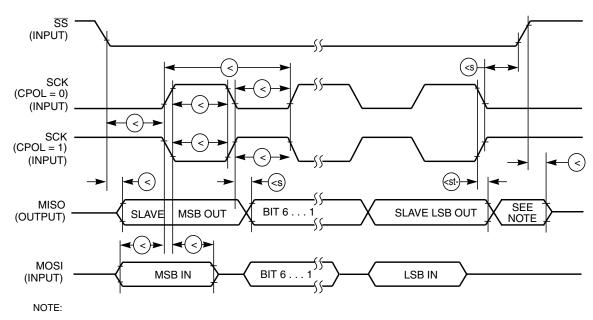

Figure A-13. SPI Slave Timing (CPHA = 0)

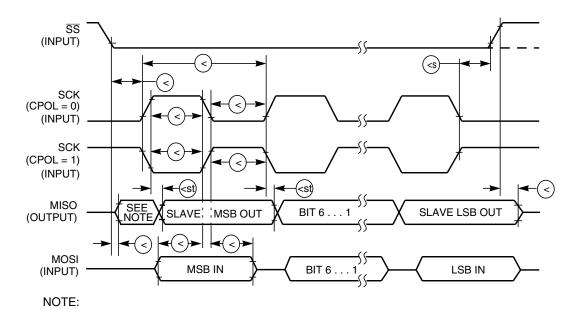

1. Not defined but normally LSB of character just received

Figure A-14. SPI Slave Timing (CPHA = 1)

Semiconductor Products Sector

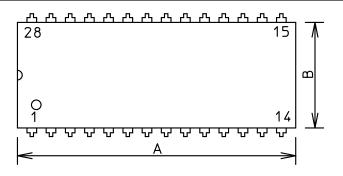

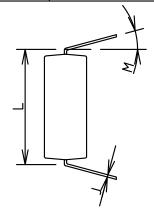

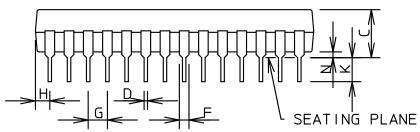

MECHANICAL OUTLINES DICTIONARY

98ASB42390B

**PAGE** 710

В

DATE 08/18/78

COPYRIGHT 1978-95 MOTOROLA ALL RIGHTS RESERVED DO NOT SCALE THIS DRAWING

ISSUE

| DIM          | MIL                  | LIMETERS                                                            | INCHES                  |                                 |  |  |  |  |

|--------------|----------------------|---------------------------------------------------------------------|-------------------------|---------------------------------|--|--|--|--|

| וווט         | MIN                  | MAX                                                                 | MIN                     | MAX                             |  |  |  |  |

| くめしひにのエーメーをと | 1.65<br>0.20<br>2.92 | 14.22<br>5.08<br>0.56<br>1.52<br>54 BSC<br>0.38<br>3.43<br>5.24 BSC | 0.065<br>0.008<br>0.115 | 0.022<br>0.060<br>0BSC<br>0.085 |  |  |  |  |

| CASE         | NO .                 | 710-02                                                              |                         |                                 |  |  |  |  |

MOT STD

STANDARD

REFERENCE

28 LD PDIP

TITLE

- POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- DIMENSION L TO CENTER OF LEADS 2. WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- 710-01 OBSOLETE, NEW STD 710-02. CONTROLLING DIMENSION: INCH

SHEET 1 OF 1

5.

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

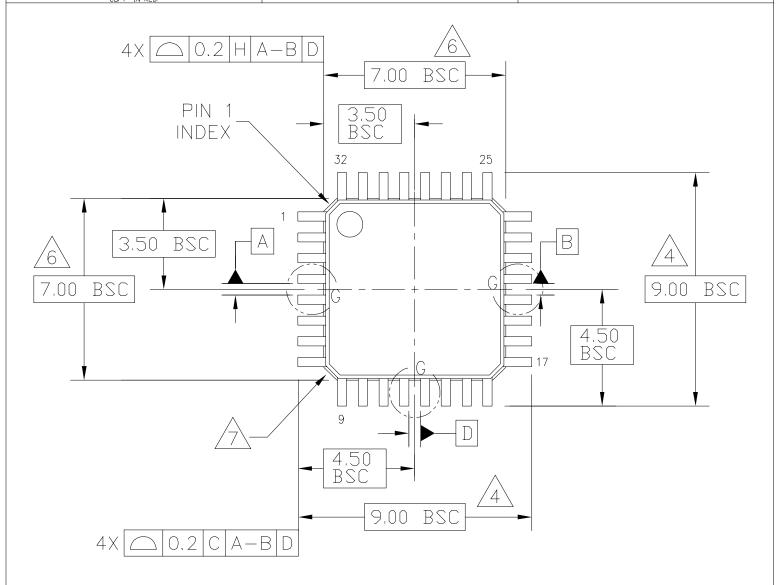

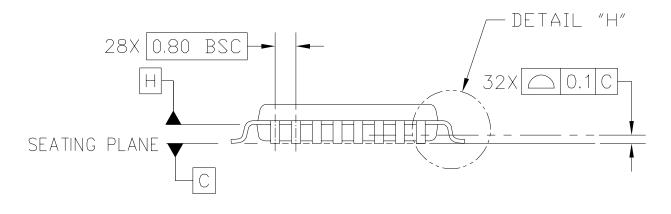

## MECHANICAL DUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASH70029A

PAGE: 873A

REV: C

TITLE:

LOW PROFILE QUAD FLAT PACK (LQFP) 32 LEAD, 0.8 PITCH (7 X 7 X 1.4)

CASE NUMBER: 873A-04

STANDARD: JEDEC MS-026 BBA

PACKAGE CDDE: 6300

SHEET:

1 DF 3

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DISCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

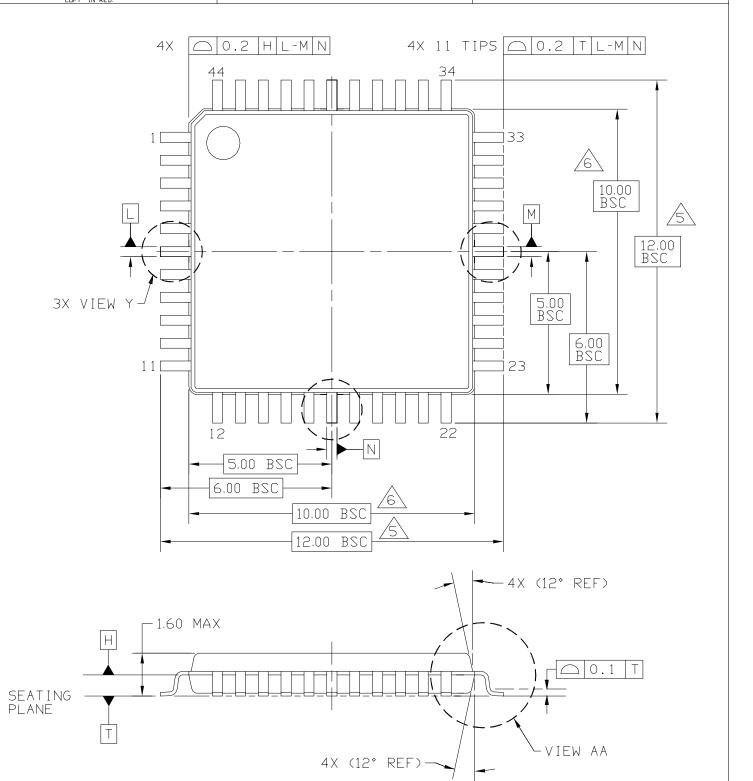

## MECHANICAL DUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASS23225W

PAGE: 824D

REV: B

TITLE:

44 LD TQFP, 10 X 10 PKG, 0.8 PITCH, 1.4 THICK CASE NUMBER: 824D-03

STANDARD: JEDEC MS-026-BCB

PACKAGE CODE: 8256

SHEET:

1 DF 3

### MECHANICAL OUTLINES DICTIONARY

PAGE: 824D

REV: B

DO NOT SCALE THIS DRAWING

#### NOTES

- 1. DIMENSIONS AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE [-H-] IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS -L-, -M- AND -N- TO BE DETERMINED AT DATUM PLANE -H-.

DIMENSIONS TO BE DETERMINED AT SEATING PLANE [-T-].

DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE [-H-].

7). DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE DIMENSION TO EXCEED 0.53. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

TITLE:

44 LD TQFP, 10 X 10 PKG, 0.8 PITCH, 1.4 THICK CASE NUMBER: 824D-03

STANDARD: JEDEC MS-026 BCB

PACKAGE CODE: 8256 | SHEET:

3 DF **3**