#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 25                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08rg32cfjer |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

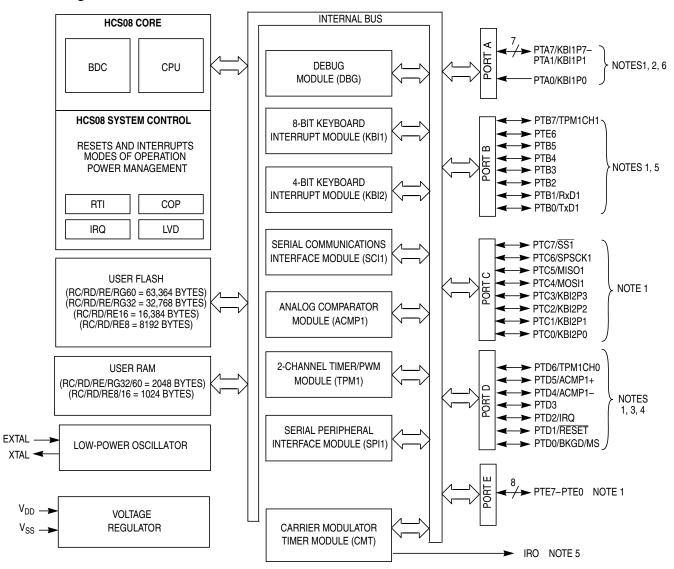

## 1.3 MCU Block Diagram

This block diagram shows the structure of the MC9S08RC/RD/RE/RG MCUs

NOTES:

- 1. Port pins are software configurable with pullup device if input port

- 2. PTA0 does not have a clamp diode to  $V_{DD}$ . PTA0 should not be driven above  $V_{DD}$ . Also, PTA0 does not pullup to  $V_{DD}$  when internal pullup is enabled.

- 3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1)

- 4. The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

#### Figure 1-1. MC9S08RC/RD/RE/RG Block Diagram

Table 1-2 lists the functional versions of the on-chip modules.

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Memory

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the FLASH if needed (normally through the background debug interface) and verifying that FLASH is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC01:SEC00) to the unsecured state (1:0).

## 4.3 RAM

The MC9S08RC/RD/RE/RG includes static RAM. The locations in RAM below \$0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit-manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on or after wakeup from stop1, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HCS08 resets the stack pointer to \$00FF. In the MC9S08RC/RD/RE/RG, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security," for a detailed description of the security feature.

## 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

## 4.4.1 Features

Features of the FLASH memory include:

- FLASH Size

- MC9S08RC/RD/RE/RG60 63374 bytes (124 pages of 512 bytes each)

- MC9S08RC/RD/RE/RG32 32768 bytes (64 pages of 512 bytes each)

- MC9S08RC/RD/RE16 16384 bytes (32 pages of 512 bytes each)

- MC9S08RC/RD/RE8 8192 bytes (16 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

## 4.4.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.6.1, "FLASH Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses are used by the command processor to complete a program or erase command.

Table 4-4 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \mu s$ . Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |  |  |  |  |  |

|----------------------|----------------|------------------------|--|--|--|--|--|

| Byte program         | 9              | 45 μs                  |  |  |  |  |  |

| Byte program (burst) | 4              | 20 μs <sup>(1)</sup>   |  |  |  |  |  |

| Page erase           | 4000           | 20 ms                  |  |  |  |  |  |

| Mass erase           | 20,000         | 100 ms                 |  |  |  |  |  |

### Table 4-4. Program and Erase Times

1. Excluding start/end overhead

Memory

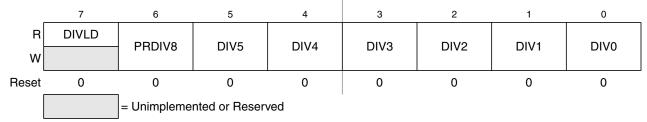

| Figure 4-5. FLASH Clock Divider Register (FCDI) | /) |

|-------------------------------------------------|----|

|-------------------------------------------------|----|

### Table 4-5. FCDIV Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD      | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH.</li> </ul>                                                                                                                                           |

| 6<br>PRDIV8     | <ul> <li>Prescale (Divide) FLASH Clock by 8</li> <li>0 Clock input to the FLASH clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:0<br>DIV[5:0] | <b>Divisor for FLASH Clock Divider</b> — The FLASH clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV5:DIV0 field plus one. The resulting frequency of the internal FLASH clock must fall within the range of 200 kHz to 150 kHz for proper FLASH operations. Program/erase timing pulses are one cycle of this internal FLASH clock, which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |

### if PRDIV8 = 0 — $f_{FCLK} = f_{Bus} \div ([DIV5:DIV0] + 1)$

Eqn. 4-1

## if PRDIV8 = 1 — $f_{FCLK} = f_{Bus} \div (8 \times ([DIV5:DIV0] + 1))$

Eqn. 4-2

Table 4-6 shows the appropriate values for PRDIV8 and DIV5:DIV0 for selected bus frequencies.

### Table 4-6. FLASH Clock Divider Settings

| f <sub>Bus</sub> | PRDIV8<br>(Binary) | DIV5:DIV0<br>(Decimal) | ffclk   | Program/Erase Timing Pulse<br>(5 μs Min, 6.7 μs Max) |

|------------------|--------------------|------------------------|---------|------------------------------------------------------|

| 8 MHz            | 0                  | 39                     | 200 kHz | 5 µs                                                 |

| 4 MHz            | 0                  | 19                     | 200 kHz | 5 μs                                                 |

| 2 MHz            | 0                  | 9                      | 200 kHz | 5 µs                                                 |

| 1 MHz            | 0                  | 4                      | 200 kHz | 5 µs                                                 |

| 200 kHz          | 0                  | 0                      | 200 kHz | 5 µs                                                 |

| 150 kHz          | 0                  | 0                      | 150 kHz | 6.7 μs                                               |

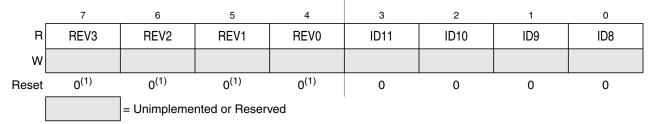

## 5.8.5 System Device Identification Register (SDIDH, SDIDL)

This read-only register is included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

#### Figure 5-6. System Device Identification Register — High (SDIDH)

1. The revision number that is hard coded into these bits reflects the current silicon revision level.

|   | Field           |                             | Description                                                                                                                                                                                                                                                                               |     |     |     |     |     |     |  |  |  |  |

|---|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

|   | 7:4<br>REV[3:0] |                             | <b>Revision Number</b> — The high-order 4 bits of address \$1806 are hard coded to reflect the current mask set evision number (0–F).                                                                                                                                                     |     |     |     |     |     |     |  |  |  |  |

|   | 3:0<br>ID[11:8] | MC9S08RC/                   | Part Identification Number — Each derivative in the HCS08 Family has a unique identification number. The MC9S08RC/RD/RE/RG32/60 is hard coded to the value \$004 and the MC9S08RC/RD/RE8/16 is hard coded to the value \$004 and the MC9S08RC/RD/RE8/16 is hard coded to the value \$004. |     |     |     |     |     |     |  |  |  |  |

|   |                 | 7                           | 6                                                                                                                                                                                                                                                                                         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|   | R               | ID7                         | ID6                                                                                                                                                                                                                                                                                       | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |  |  |  |  |

|   | w               |                             |                                                                                                                                                                                                                                                                                           |     |     |     |     |     |     |  |  |  |  |

| l | Reset, 8/16K:   | 0                           | 0                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 1   | 1   | 1   |  |  |  |  |

| R | eset, 32/60K:   | 0                           | 0                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 1   | 0   | 0   |  |  |  |  |

|   |                 | = Unimplemented or Reserved |                                                                                                                                                                                                                                                                                           |     |     |     |     |     |     |  |  |  |  |

#### Table 5-6. SDIDH Field Descriptions

### Figure 5-7. System Device Identification Register — Low (SDIDL)

#### Table 5-7. SDIDL Field Descriptions

| Field          | Description                                                                                                                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[7:0] | <b>Part Identification Number</b> — Each derivative in the HCS08 Family has a unique identification number. The MC9S08RC/RD/RE/RG32/60 is hard coded to the value \$004 and the MC9S08RC/RD/RE8/16 is hard coded to the value \$003. |

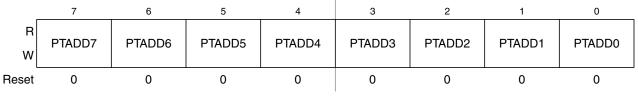

#### Parallel Input/Output

### Figure 6-8. Data Direction for Port A (PTADD)

#### Table 6-3. PTADD Field Descriptions

| Field             | Description                                                                                                                                                                     | read for |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7:0<br>PTADD[7:0] | <b>Data Direction for Port A Bits</b> — These read/write bits control the direction of port A pins and what is read for PTAD reads.                                             |          |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port A bit n and PTAD reads return the contents of PTADn.</li> </ol> |          |

## 6.6.2 Port B Registers (PTBD, PTBPE, and PTBDD)

Port B pins used as general-purpose I/O pins are controlled by the port B data (PTBD), data direction (PTBDD), and pullup enable (PTBPE) registers.

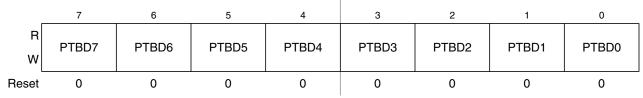

Figure 6-9. Port B Data Register (PTBD)

### Table 6-4. PTBD Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out on the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

#### Parallel Input/Output

|                                                | 7          | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|------------------------------------------------|------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| R<br>W                                         | PTEDD7     | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |  |  |

| Reset                                          | et 0 0 0 0 |        | 0      | 0      | 0      | 0      |        |        |  |  |

| Figure 6-20. Data Direction for Port E (PTEDD) |            |        |        |        |        |        |        |        |  |  |

#### **5**

### Table 6-15. PTEDD Field Descriptions

| Field             | Description                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDD(7:0) | <b>Data Direction for Port E Bits</b> — These read/write bits control the direction of port E pins and what is read for PTED reads.                                                 |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.</li> </ul> |

- IX = 16-bit indexed no offset

- IX+ = 16-bit indexed no offset, post increment (CBEQ and MOV only)

- IX1 = 16-bit indexed with 8-bit offset from H:X

- IX1+ = 16-bit indexed with 8-bit offset, post increment (CBEQ only)

- IX2 = 16-bit indexed with 16-bit offset from H:X

- REL = 8-bit relative offset

- SP1 = Stack pointer with 8-bit offset

- SP2 = Stack pointer with 16-bit offset

### Table 7-2. HCS08 Instruction Set Summary (Sheet 1 of 7)

| Source                                                                                                               | Operation                                                  | Description                                                          |   |   | Eff<br>on ( |   |       |   | Address<br>Mode                                     | Opcode                             | Operand                             | ycles <sup>1</sup>      |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|---|---|-------------|---|-------|---|-----------------------------------------------------|------------------------------------|-------------------------------------|-------------------------|

| Form                                                                                                                 | Operation                                                  |                                                                      |   | н | I           | N | v z c |   | Addi<br>Mo                                          |                                    |                                     | Bus Cycles <sup>1</sup> |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC oprx8,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry                                             | A ← (A) + (M) + (C)                                                  |   |   | _           |   |       |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D9<br>E9<br>F9<br>9ED9<br>9EE9     | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP      | Add without Carry                                          | A ← (A) + (M)                                                        |   |   | -           |   |       |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | BB<br>CB                           | hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 3 5 4         |

| AIS # <i>opr8i</i>                                                                                                   | Add Immediate Value<br>(Signed) to Stack Pointer           | $SP \leftarrow (SP) + (M)$<br>M is sign extended to a 16-bit value   | - | - | -           | - | -     | - | IMM                                                 | A7                                 | ii                                  | 2                       |

| AIX #opr8i                                                                                                           | Add Immediate Value<br>(Signed) to Index<br>Register (H:X) | $H:X \leftarrow (H:X) + (M)$<br>M is sign extended to a 16-bit value | - | - | -           | - | -     | - | IMM                                                 | AF                                 | ii                                  | 2                       |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP      | Logical AND                                                | A ← (A) & (M)                                                        | 0 | _ | _           |   |       | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D4                                 | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 23443354                |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL ,X<br>ASL oprx8,SP                                         | Arithmetic Shift Left<br>(Same as LSL)                     | C - 0 b7 b0                                                          |   | _ | _           |   |       |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68 | ff                                  | 5<br>1<br>5<br>4<br>6   |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                                   | Arithmetic Shift Right                                     |                                                                      |   | _ | _           |   |       |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37<br>47<br>57<br>67<br>77<br>9E67 | ff<br>ff                            | 5<br>1<br>5<br>4<br>6   |

| BCC rel                                                                                                              | Branch if Carry Bit Clear                                  | Branch if (C) = 0                                                    | - | - | -           | - | -     | - | REL                                                 | 24                                 | rr                                  | 3                       |

| Source                                                                                                          |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   | ieci<br>CC |   |   | sss                                                 | qe                                 | pui                                 | cles <sup>1</sup>               |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|------------|---|---|-----------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                            | Operation                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                               | v | н | I | N          | z | с | Address<br>Mode                                     | Opcode                             | Operand                             | Bus Cycles <sup>1</sup>         |

| ROR opr8a<br>RORA<br>RORX<br>ROR oprx8,X<br>ROR ,X<br>ROR oprx8,SP                                              | Rotate Right through<br>Carry                                          | b7 b0                                                                                                                                                                                                                                                                                                                                                                                                                     |   | _ | - |            |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66 | ff                                  | 5<br>1<br>5<br>4<br>6           |

| RSP                                                                                                             | Reset Stack Pointer                                                    | $SP \leftarrow 0xFF$<br>(High Byte Not Affected)                                                                                                                                                                                                                                                                                                                                                                          | - | - | - | -          | - | - | INH                                                 | 9C                                 |                                     | 1                               |

| RTI                                                                                                             | Return from Interrupt                                                  | $\begin{array}{l} SP \leftarrow (SP) + 0x0001; \ Pull \ (CCR) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (A) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (X) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (PCH) \\ SP \leftarrow (SP) + 0x0001; \ Pull \ (PCL) \end{array}$                                                                                                                                                        |   |   |   |            |   |   | INH                                                 | 80                                 |                                     | 9                               |

| RTS                                                                                                             | Return from Subroutine                                                 | $\begin{array}{l} SP \leftarrow SP + 0x0001; Pull \ (PCH) \\ SP \leftarrow SP + 0x0001; \ Pull \ (PCL) \end{array}$                                                                                                                                                                                                                                                                                                       | - | - | - | -          | - | - | INH                                                 | 81                                 |                                     | 6                               |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry                                                    | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                                                                                                                                                                                                            |   | - | - |            |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | D2                                 | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| SEC                                                                                                             | Set Carry Bit                                                          | C ← 1                                                                                                                                                                                                                                                                                                                                                                                                                     | - | - | - | -          | - | 1 | INH                                                 | 99                                 |                                     | 1                               |

| SEI                                                                                                             | Set Interrupt Mask Bit                                                 | l ← 1                                                                                                                                                                                                                                                                                                                                                                                                                     | - | - | 1 | -          | - | - | INH                                                 | 9B                                 |                                     | 1                               |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in<br>Memory                                         | M ← (A)                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | - | _ |            |   | - | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | D7                                 | hh II<br>ee ff<br>ff<br>ee ff       | 3<br>4<br>3<br>2<br>5<br>4      |

| STHX opr8a<br>STHX opr16a<br>STHX oprx8,SP                                                                      | Store H:X (Index Reg.)                                                 | (M:M + 0x0001) ← (H:X)                                                                                                                                                                                                                                                                                                                                                                                                    | 0 | - | - |            |   | - | DIR<br>EXT<br>SP1                                   | 35<br>96<br>9EFF                   | hh ll                               | 4<br>5<br>5                     |

| STOP                                                                                                            | Enable Interrupts:<br>Stop Processing<br>Refer to MCU<br>Documentation | I bit $\leftarrow$ 0; Stop Processing                                                                                                                                                                                                                                                                                                                                                                                     | - | - | 0 | -          | - | - | INH                                                 | 8E                                 |                                     | 2+                              |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of<br>Index Register)<br>in Memory                 | M ← (X)                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | - | _ |            |   | - | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        |                                    | hh II<br>ee ff<br>ff<br>ee ff       | 3<br>4<br>3<br>2<br>5<br>4      |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract                                                               | A ← (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                             |   | - | _ |            |   |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| SWI                                                                                                             | Software Interrupt                                                     | $\begin{array}{c} PC \leftarrow (PC) + 0x0001 \\ Push \ (PCL); \ SP \leftarrow (SP) - 0x0001 \\ Push \ (PCH); \ SP \leftarrow (SP) - 0x0001 \\ Push \ (X); \ SP \leftarrow (SP) - 0x0001 \\ Push \ (A); \ SP \leftarrow (SP) - 0x0001 \\ Push \ (CCR); \ SP \leftarrow (SP) - 0x0001 \\ I \leftarrow I; \\ PCH \leftarrow Interrupt \ Vector \ High \ Byte \\ PCL \leftarrow Interrupt \ Vector \ Low \ Byte \end{array}$ | - | - | 1 | _          | _ | - | INH                                                 | 83                                 |                                     | 11                              |

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

\_

#### Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

|                         |                        |                      |                       |                       |                       |                      | · · · ·               |                        |              |                      |                      |                      |                      |                      |                     |  |

|-------------------------|------------------------|----------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|------------------------|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|--|

| -                       | ipulation              | Branch               |                       |                       | ad-Modify-W           |                      |                       |                        | ntrol        | Register/Memory      |                      |                      |                      |                      |                     |  |

| 00 5<br>BRSET0<br>3 DIR | BSET0<br>2 DIR         | 20 3<br>BRA<br>2 REL | NEG<br>2 DIR          | 40 1<br>NEGA<br>1 INH | 50 1<br>NEGX<br>1 INH | NEG<br>2 IX1         | NEG<br>1 IX           | RTI<br>1 INH           | BGE<br>2 REL | SUB<br>2 IMM         | SUB<br>2 DIR         | SUB<br>3 EXT         | SUB<br>3 IX2         | SUB<br>2 IX1         | F0 3<br>SUB<br>1 IX |  |

| 01 5                    | 11 5                   | 21 3                 | 31 5                  | 41 4                  | 51 4                  | 61 5                 | 71 5                  | 81 6                   | 91 3         | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |  |

| BRCLR0                  | BCLR0                  | BRN                  | CBEQ                  | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                  | RTS                    | BLT          | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 3 DIR                 | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 02 5                    | 12 5                   | 22 3                 | 32 5                  | 42 5                  | 52 6                  | 62 1                 | 72 1                  | 82 5+                  | 92 3         | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |  |

| BRSET1                  | BSET1                  | BHI                  | LDHX                  | MUL                   | DIV                   | NSA                  | DAA                   | BGND                   | BGT          | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 3 EXT                 | 1 INH                 | 1 INH                 | 1 INH                | 1 INH                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 03 5                    | 13 5                   | 23 3                 | 33 5                  | 43 1                  | 53 1                  | 63 5                 | 73 4                  | 83 11                  | 93 3         | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |  |

| BRCLR1                  | BCLR1                  | BLS                  | COM                   | COMA                  | COMX                  | COM                  | COM                   | SWI                    | BLE          | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 04 5                    | 14 5                   | 24 3                 | 34 5                  | 44 1                  | 54 1                  | 64 5                 | 74 4                  | 84 1                   | 94 2         | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |  |

| BRSET2                  | BSET2                  | BCC                  | LSR                   | LSRA                  | LSRX                  | LSR                  | LSR                   | TAP                    | TXS          | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 05 5                    | 15 5                   | 25 3                 | 35 4                  | 45 3                  | 55 4                  | 65 3                 | 75 5                  | 85 1                   | 95 2         | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |  |

| BRCLR2                  | BCLR2                  | BCS                  | STHX                  | LDHX                  | LDHX                  | CPHX                 | CPHX                  | TPA                    | TSX          | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 06 5                    | 16 5                   | 26 3                 | 36 5                  | 46 1                  | 56 1                  | 66 5                 | 76 4                  | 86 3                   | 96 5         | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |  |

| BRSET3                  | BSET3                  | BNE                  | ROR                   | RORA                  | RORX                  | ROR                  | ROR                   | PULA                   | STHX         | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 07 5                    | 17 5                   | 27 3                 | 37 5                  | 47 1                  | 57 1                  | 67 5                 | 77 4                  | 87 2                   | 97 1         | A7 2                 | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |  |

| BRCLR3                  | BCLR3                  | BEQ                  | ASR                   | ASRA                  | ASRX                  | ASR                  | ASR                   | PSHA                   | TAX          | AIS                  | STA                  | STA                  | STA                  | STA                  | STA                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 08 5                    | 18 5                   | 28 3                 | 38 5                  | 48 1                  | 58 1                  | 68 5                 | 78 4                  | 88 3                   | 98 1         | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |  |

| BRSET4                  | BSET4                  | BHCC                 | LSL                   | LSLA                  | LSLX                  | LSL                  | LSL                   | PULX                   | CLC          | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 09 5                    | 19 5                   | 29 3                 | 39 5                  | 49 1                  | 59 1                  | 69 5                 | 79 4                  | 89 2                   | 99 1         | A9 2                 | B9 3                 | C9 4                 | D9 4                 | E9 3                 | F9 3                |  |

| BRCLR4                  | BCLR4                  | BHCS                 | ROL                   | ROLA                  | ROLX                  | ROL                  | ROL                   | PSHX                   | SEC          | ADC                  | ADC                  | ADC                  | ADC                  | ADC                  | ADC                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0A 5                    | 1A 5                   | 2A 3                 | 3A 5                  | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                  | 8A 3                   | 9A 1         | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |  |

| BRSET5                  | BSET5                  | BPL                  | DEC                   | DECA                  | DECX                  | DEC                  | DEC                   | PULH                   | CLI          | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0B 5                    | 1B 5                   | 2B 3                 | 3B 7                  | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                  | 8B 2                   | 9B 1         | AB 2                 | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |  |

| BRCLR5                  | BCLR5                  | BMI                  | DBNZ                  | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                  | PSHH                   | SEI          | ADD                  | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 3 DIR                 | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0C 5                    | 1C 5                   | 2C 3                 | 3C 5                  | 4C 1                  | 5C 1                  | 6C 5                 | <sup>7C</sup> 4       | 8C 1                   | 9C 1         |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |  |

| BRSET6                  | BSET6                  | BMC                  | INC                   | INCA                  | INCX                  | INC                  | INC                   | CLRH                   | RSP          |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0D 5                    | 1D 5                   | 2D 3                 | 3D 4                  | 4D 1                  | 5D 1                  | 6D 4                 | <sup>7D</sup> 3       |                        | 9D 1         | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |  |

| BRCLR6                  | BCLR6                  | BMS                  | TST                   | TSTA                  | TSTX                  | TST                  | TST                   |                        | NOP          | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  |                        | 1 INH        | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2 | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |  |

| 0F 5                    | 1F 5                   | 2F 3                 | 3F 5                  | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1         | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |  |

| BRCLR7                  | BCLR7                  | BIH                  | CLR                   | CLRA                  | CLRX                  | CLR                  | CLR                   | WAIT                   | TXA          | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |  |

| 3 DIR                   | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

|      |            |

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

SP1 SP2 IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment IX1+

Opcode in Hexadecimal F0 3 SUB 1 IX Addressing Mode Number of Bytes 1

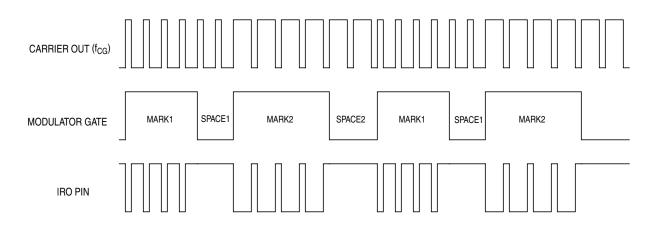

The space period provides an interpulse gap (no carrier). If CMTCMD3:CMTCMD4 = \$0000, then the modulator and carrier generator will switch between carrier frequencies without a gap or any carrier glitches (zero space).

Using timing data for carrier burst and interpulse gap length calculated by the CPU, FSK mode can automatically generate a phase-coherent, dual-frequency FSK signal with programmable burst and interburst gaps.

The mark and space time equations for FSK mode are:

### t<sub>space</sub> = CMTCMD3:CMTCMD4 ÷ f<sub>CG</sub> Eqn. 8-8

Where  $f_{CG}$  is the frequency output from the carrier generator. The example in Figure 8-6 shows what the IRO pin output looks like in FSK mode with the following values: CMTCMD1:CMTCMD2 = \$0003, CMTCMD3:CMTCMD4 = \$0002, primary carrier high count = \$01, primary carrier low count = \$02, secondary carrier high count = \$03, and secondary carrier low count = \$01.

## 8.5.3 Extended Space Operation

In time, baseband, or FSK mode, the space period can be made longer than the maximum possible value of the space period register. Setting the EXSPC bit in the CMTMSC register will force the modulator to treat the next modulation period (beginning with the next load of the counter and space period register) as a space period equal in length to the mark and space counts combined. Subsequent modulation periods will consist entirely of these extended space periods with no mark periods. Clearing EXSPC will return the modulator to standard operation at the beginning of the next modulation period.

## 8.5.3.1 EXSPC Operation in Time Mode

To calculate the length of an extended space in time or baseband modes, add the mark and space times and multiply by the number of modulation periods that EXSPC is set.

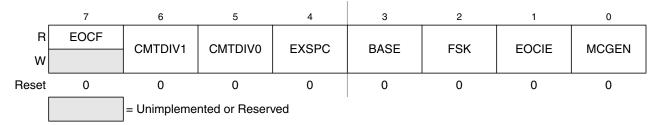

## 8.6.3 CMT Modulator Status and Control Register (CMTMSC)

The CMT modulator status and control register (CMTMSC) contains the modulator and carrier generator enable (MCGEN), end of cycle interrupt enable (EOCIE), FSK mode select (FSK), baseband enable (BASE), extended space (EXSPC), prescaler (CMTDIV1:CMTDIV0) bits, and the end of cycle (EOCF) status bit.

### Figure 8-13. CMT Modulator Status and Control Register (CMTMSC)

### Table 8-8. CMTMSC Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>EOCF          | <ul> <li>End of Cycle Status Flag — The EOCF bit is set when:</li> <li>The modulator is not currently active and the MCGEN bit is set to begin the initial CMT transmission.</li> <li>At the end of each modulation cycle while the MCGEN bit is set. This is recognized when a match occurs between the contents of the space period register and the down-counter. At this time, the counter is initialized with the (possibly new) contents of the mark period buffer, CMTCMD1 and CMTCMD2. The space period register is loaded with the (possibly new) contents of the space period buffer, CMTCMD1 and CMTCMD3 and CMTCMD4.</li> <li>This flag is cleared by a read of the CMTMSC register followed by an access of CMTCMD2 or CMTCMD4. In the case where the MCGEN bit is cleared and then set before the end of the modulation cycle, EOCF will not be set when MCGEN is set, but will be set at the end of the current modulation cycle.</li> <li>No end of modulator cycle has occurred</li> </ul> |

| 6:5<br>CMTDIV[1:0] | <ul> <li>CMT Clock Divide Prescaler — The CMT clock divide prescaler causes the CMT to be clocked at the BUS CLOCK frequency, or the BUS CLOCK frequency divided by 1, 2, 4, or 8. Because these bits are not double buffered, they should not be changed during a transmission.</li> <li>00 Bus clock ÷ 1</li> <li>01 Bus clock ÷ 2</li> <li>10 Bus clock ÷ 4</li> <li>11 Bus clock ÷ 8</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>EXSPC         | <ul> <li>Extended Space Enable — The EXSPC bit enables extended space operation.</li> <li>0 Extended space disabled</li> <li>1 Extended space enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3<br>BASE          | <ul> <li>Baseband Enable — When set, the BASE bit disables the carrier generator and forces the carrier output high for generation of baseband protocols. When BASE is clear, the carrier generator is enabled and the carrier output toggles at the frequency determined by values stored in the carrier data registers. See Section 8.5.2.2, "Baseband Mode." This bit is cleared by reset. This bit is not double buffered and should not be written to during a transmission.</li> <li>0 Baseband mode disabled</li> <li>1 Baseband mode enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2<br>FSK           | FSK Mode Select — The FSK bit enables FSK operation.         0       CMT operates in time or baseband mode         1       CMT operates in FSK mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

# Chapter 9 Keyboard Interrupt (S08KBIV1)

## 9.1 Introduction

The MC9S08RC/RD/RE/RG has two KBI modules. One has eight keyboard interrupt inputs that share port A pins. The other KBI module has four inputs that are shared on the upper four pins of port C. See the Pins and Connections chapter for more information about the logic and hardware aspects of these pins.

Port A is an 8-bit port that is shared between the KBI1 keyboard interrupt inputs and general-purpose I/O. The eight KBI1PEn control bits in the KBI1PE register allow selection of any combination of port A pins to be assigned as KBI1 inputs. Any pins that are enabled as KBI1 inputs will be forced to act as inputs and the remaining port A pins are available as general-purpose I/O pins controlled by the port A data (PTAD), data direction (PTADD) and pullup enable (PTAPE) registers. The eight PTAPEn control bits in the PTAPE register allow the user to select whether an internal pullup device is enabled on each port A pin that is configured as a port input or a KBI1 input.

KBI1 inputs can be configured for edge-only sensitivity or edge-and-level sensitivity. Bits 3 through 0 of port A are falling-edge/low-level sensitive and bits 7 through 4 can be configured for rising-edge/high-level or for falling-edge/low-level sensitivity.

Port C is an 8-bit port with its lower four pins shared between the KBI2 keyboard interrupt inputs and general-purpose I/O. The four KBI2PEn control bits in the KBI2PE register allow selection of any combination of the lower four port C pins to be assigned as KBI2 inputs. Any pins that are enabled as KBI2 inputs will be forced to act as inputs and the remaining port C pins are available as general-purpose I/O pins controlled by the port C data (PTCD), data direction (PTCDD) and pullup enable (PTCPE) registers. The eight PTCPEn control bits in the PTCPE register allow the user to select whether an internal pullup device is enabled on each port C pin that is configured as a port input or a KBI2 input.

Any enabled keyboard interrupt can be used to wake the MCU from wait, standby (stop3), partial power-down (stop2) or power-down modes (stop1). In either stop1 or stop2 mode, an input functions as a falling edge/low-level wakeup, therefore it should be configured to use falling-edge sensing if the MCU will be used in stop1 or stop2 modes.

Either KBI1 or KBI2 can be used to wake the MCU from wait or standby (stop3). Only KBI1 can be used to wake the MCU from partial power down (stop2) or power down (stop1). When using KBI1 to wake up from stop2 or stop1, the pins must be configured to use falling-edge/low-level sensing (KBEDG = 0). The KBF bits for both KBI modules must be cleared before entering stop mode, regardless of whether the interrupt is enabled.

### NOTE

The voltage measured on the pulled up PTA0 pin will be less than  $V_{DD}$ . The internal gates connected to this pin are pulled all the way to  $V_{DD}$ . All other pins with enabled pullup resistors will have an unloaded measurement of  $V_{DD}$ .

#### Table 12-4. SCI1C2 Register Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWU | <ul> <li>Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 12.3.3.2, "Receiver Wakeup Operation," for more details.</li> <li>0 Normal SCI receiver operation.</li> <li>1 SCI receiver in standby waiting for wakeup condition.</li> </ul> |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 12.3.2.1, "Send Break and Queued Idle," for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                     |

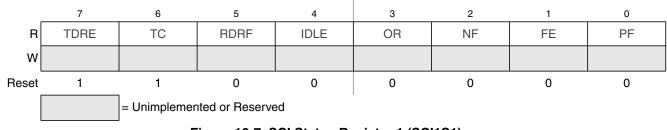

## 12.2.4 SCI Status Register 1 (SCI1S1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

### Figure 12-7. SCI Status Register 1 (SCI1S1)

#### Table 12-5. SCI1S1 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set immediately after reset and when a transmit data value<br>transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To<br>clear TDRE, read SCI1S1 with TDRE = 1 and then write to the SCI data register (SCI1D).0Transmit data register (buffer) full.<br>11Transmit data register (buffer) empty.                                                                                                                                                                                                                          |

| 6<br>TC   | <ul> <li>Transmission Complete Flag — TC is set immediately after reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.</li> <li>0 Transmitter active (sending data, a preamble, or a break).</li> <li>1 Transmitter idle (transmission activity complete).</li> <li>TC is cleared automatically by reading SCI1S1 with TC = 1 and then doing one of the following three things: <ul> <li>Write to the SCI data register (SCI1D) to transmit new data</li> <li>Queue a preamble by changing TE from 0 to 1</li> <li>Queue a break character by writing 1 to SBK in SCI1C2</li> </ul> </li> </ul> |

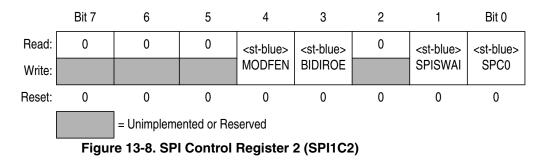

SSOE — Slave Select Output Enable

This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the  $\overline{SS1}$  pin as shown in Table 13-1.

| MODFEN | SSOE | Master Mode                   | Slave Mode         |  |  |

|--------|------|-------------------------------|--------------------|--|--|

| 0      | 0    | General-purpose I/O (not SPI) | Slave select input |  |  |