Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | 44-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08rg60cfg |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08RG60 Data Sheet

Covers: MC9S08RC8/16/32/60 MC9S08RD8/16/32/60 MC9S08RE8/16/32/60 MC9S08RG32/60

> MC9S08RG60/D Rev. 1.11 06/2005

#### Title Section Number Page 7.3.4 7.3.5 7.3.6 7.3.6.1 7.3.6.2 7.3.6.3 7.3.6.4 7.3.6.5 7.3.6.6 7.3.6.7 7.4 7.4.1 7.4.2 7.4.3 7.4.4 7.4.5 7.5

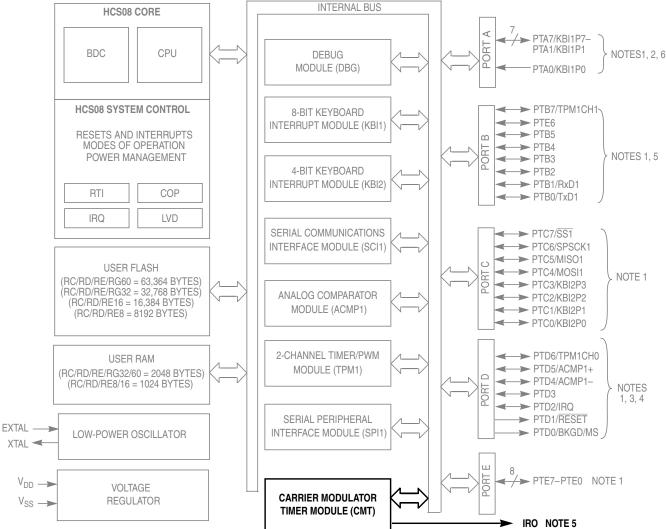

### Chapter 8 Carrier Modulator Timer (S08CMTV1)

| 8.1 | Introduct | 10n                                                              | 107 |

|-----|-----------|------------------------------------------------------------------|-----|

| 8.2 | Features  |                                                                  | 108 |

| 8.3 | CMT Blo   | ock Diagram                                                      | 108 |

| 8.4 | Pin Desci | ription                                                          | 108 |

| 8.5 | Function  | al Description                                                   | 109 |

|     | 8.5.1     | Carrier Generator                                                | 110 |

|     | 8.5.2     | Modulator                                                        | 112 |

|     |           | 8.5.2.1 Time Mode                                                | 113 |

|     |           | 8.5.2.2 Baseband Mode                                            | 114 |

|     |           | 8.5.2.3 FSK Mode                                                 | 114 |

|     | 8.5.3     | Extended Space Operation                                         | 115 |

|     |           | 8.5.3.1 EXSPC Operation in Time Mode                             | 115 |

|     |           | 8.5.3.2 EXSPC Operation in FSK Mode                              | 116 |

|     | 8.5.4     | Transmitter                                                      | 116 |

|     | 8.5.5     | CMT Interrupts                                                   | 117 |

|     | 8.5.6     | Wait Mode Operation                                              | 117 |

|     | 8.5.7     | Stop Mode Operation                                              | 117 |

|     | 8.5.8     | Background Mode Operation                                        | 118 |

| 8.6 | CMT Reg   | gisters and Control Bits                                         | 118 |

|     | 8.6.1     | Carrier Generator Data Registers (CMTCGH1, CMTCGL1, CMTCGH2, and |     |

|     |           | CMTCGL2)                                                         | 118 |

|     | 8.6.2     | CMT Output Control Register (CMTOC)                              | 120 |

|     | 8.6.3     | CMT Modulator Status and Control Register (CMTMSC)               | 121 |

|     | 8.6.4     | CMT Modulator Data Registers (CMTCMD1, CMTCMD2, CMTCMD3, and     |     |

|     |           | CMTCMD4)                                                         | 122 |

|     |           |                                                                  |     |

# Chapter 2 Pins and Connections

# 2.1 Introduction

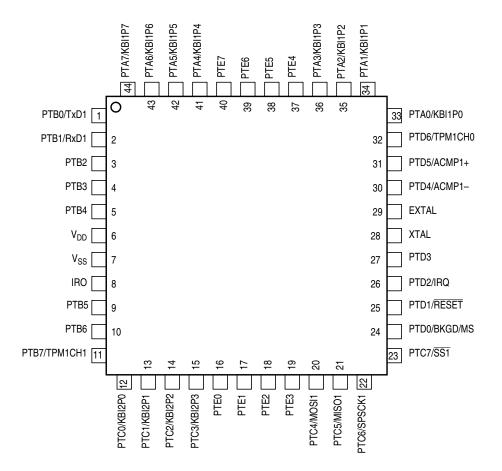

This section describes signals that connect to package pins. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals.

# 2.2 Device Pin Assignment

Figure 2-1. MC9S08RC/RD/RE/RG in 44-Pin LQFP Package

### 2.3.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a  $10-\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a  $0.1-\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise.

## 2.3.2 Oscillator

The oscillator in the MC9S08RC/RD/RE/RG is a traditional Pierce oscillator that can accommodate a crystal or ceramic resonator in the range of 1 MHz to 16 MHz.

Refer to Figure 2-5 for the following discussion.  $R_F$  should be a low-inductance resistor such as a carbon composition resistor. Wire-wound resistors, and some metal film resistors, have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup and its value is not generally critical. Typical systems use 1 M $\Omega$ . Higher values are sensitive to humidity and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance that is the series combination of C1 and C2, which are usually the same size. As a first-order approximation, use 5 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

## 2.3.3 PTD1/RESET

The external pin reset function is shared with an output-only port function on the PTD1/RESET pin. The reset function is enabled when RSTPE in SOPT is set. RSTPE is set following any reset of the MCU and must be cleared in order to use this pin as an output-only port.

Whenever any reset is initiated (whether from an external signal or from an internal system), the reset pin is driven low for about 34 cycles of  $f_{Self\_reset}$ , released, and sampled again about 38 cycles of  $f_{Self\_reset}$  later. If reset was caused by an internal source such as low-voltage reset or watchdog timeout, the circuitry expects the reset pin sample to return a logic 1. If the pin is still low at this sample point, the reset is assumed to be from an external source. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system control reset status register (SRS).

Never connect any significant capacitance to the reset pin because that would interfere with the circuit and sequence that detects the source of reset. If an external capacitance prevents the reset pin from rising to a valid logic 1 before the reset sample point, all resets will appear to be external resets.

| Vector<br>Number | Address<br>(High/Low) | Vector                                              | Vector Name |

|------------------|-----------------------|-----------------------------------------------------|-------------|

| 16<br>through    | \$FFC0:FFC1           | Unused Vector Space<br>(available for user program) |             |

| 31               | Ŧ                     |                                                     |             |

|                  | \$FFDE:FFDF           |                                                     |             |

| 15               | \$FFE0:FFE1           | SPI <sup>(1)</sup>                                  | Vspi1       |

| 14               | \$FFE2:FFE3           | RTI                                                 | Vrti        |

| 13               | \$FFE4:FFE5           | KBI2                                                | Vkeyboard2  |

| 12               | \$FFE6:FFE7           | KBI1                                                | Vkeyboard1  |

| 11               | \$FFE8:FFE9           | ACMP <sup>(2)</sup>                                 | Vacmp1      |

| 10               | \$FFEA:FFEB           | CMT                                                 | Vcmt        |

| 9                | \$FFEC:FFED           | SCI Transmit <sup>(3)</sup>                         | Vsci1tx     |

| 8                | \$FFEE:FFEF           | SCI Receive <sup>(3)</sup>                          | Vsci1rx     |

| 7                | \$FFF0:FFF1           | SCI Error <sup>(3)</sup>                            | Vsci1err    |

| 6                | \$FFF2:FFF3           | TPM Overflow                                        | Vtpm1ovf    |

| 5                | \$FFF4:FFF5           | TPM Channel 1                                       | Vtpm1ch1    |

| 4                | \$FFF6:FFF7           | TPM Channel 0                                       | Vtpm1ch0    |

| 3                | \$FFF8:FFF9           | IRQ                                                 | Virq        |

| 2                | \$FFFA:FFFB           | Low Voltage Detect                                  | Vlvd        |

| 1                | \$FFFC:FFFD           | SWI                                                 | Vswi        |

| 0                | \$FFFE:FFFF           | Reset                                               | Vreset      |

### Figure 4-2. Reset and Interrupt Vectors

1. The SPI module is not included on the MC9S08RC/RD/RE devices. This vector location is unused for those devices.

2. The analog comparator (ACMP) module is not included on the MC9S08RD devices. This vector location is unused for those devices.

3. The SCI module is not included on the MC9S08RC devices. This vector location is unused for those devices.

#### Memory

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the FLASH if needed (normally through the background debug interface) and verifying that FLASH is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC01:SEC00) to the unsecured state (1:0).

# 4.3 RAM

The MC9S08RC/RD/RE/RG includes static RAM. The locations in RAM below \$0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit-manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on or after wakeup from stop1, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HCS08 resets the stack pointer to \$00FF. In the MC9S08RC/RD/RE/RG, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security," for a detailed description of the security feature.

# 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

### 4.4.1 Features

Features of the FLASH memory include:

- FLASH Size

- MC9S08RC/RD/RE/RG60 63374 bytes (124 pages of 512 bytes each)

- MC9S08RC/RD/RE/RG32 32768 bytes (64 pages of 512 bytes each)

- MC9S08RC/RD/RE16 16384 bytes (32 pages of 512 bytes each)

- MC9S08RC/RD/RE8 8192 bytes (16 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

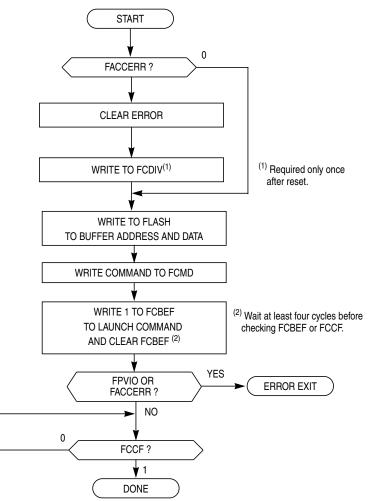

### 4.4.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.6.1, "FLASH Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses are used by the command processor to complete a program or erase command.

Table 4-4 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \mu s$ . Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |  |

|----------------------|----------------|------------------------|--|

| Byte program         | 9              | 45 μs                  |  |

| Byte program (burst) | 4              | 20 μs <sup>(1)</sup>   |  |

| Page erase           | 4000           | 20 ms                  |  |

| Mass erase           | 20,000         | 100 ms                 |  |

### Table 4-4. Program and Erase Times

1. Excluding start/end overhead

Figure 4-3. FLASH Program and Erase Flowchart

# 4.4.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and remains enabled after completion of the burst program operation if the following two conditions are met:

- The new burst program command has been queued before the current program operation completes.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst

= Unimplemented or Reserved

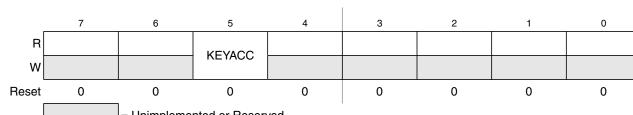

### Figure 4-7. FLASH Configuration Register (FCNFG)

### **Table 4-8. FCNFG Field Descriptions**

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5      | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."</li> <li>Writes to \$FFB0-\$FFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>Writes to NVBACKKEY (\$FFB0-\$FFB7) are interpreted as comparison key writes.</li></ul> |  |

| KEYACC | Reads of the FLASH return invalid data.                                                                                                                                                                                                                                                                                                                                                                    |  |

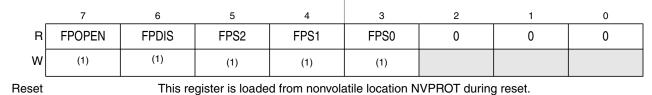

#### 4.6.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT is copied from FLASH into FPROT. Bits 0, 1, and 2 are not used and each always reads as 0. This register may be read at any time, but user program writes have no meaning or effect. Background debug commands can write to FPROT at \$1824.

= Unimplemented or Reserved

#### Figure 4-8. FLASH Protection Register (FPROT)

1. Background commands can be used to change the contents of these bits in FPROT.

### **Table 4-9. FPROT Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN     | Open Unprotected FLASH for Program/Erase0011Any FLASH location, not otherwise block protected or secured, may be erased or programmed.                                                                                                                           |

| 6<br>FPDIS      | FLASH Protection Disable0FLASH block specified by FPS2:FPS0 is block protected (program and erase not allowed).1No FLASH block is protected.                                                                                                                     |

| 5:3<br>FPS[2:0] | <b>FLASH Protect Size Selects</b> — When FPDIS = 0, this 3-bit field determines the size of a protected block of FLASH locations at the high address end of the FLASH (see Table 4-10 and Table 4-11). Protected FLASH locations cannot be erased or programmed. |

### 6.4.2 Internal Pullup Control

An internal pullup device can be enabled for each port pin that is configured as an input (PTxDDn = 0). The pullup device is available for a peripheral module to use, provided the peripheral is enabled and is an input function as long as the PTxDDn = 0.

### NOTE

The voltage measured on the pulled up PTA0 pin will be less than  $V_{DD}$ . The internal gates connected to this pin are pulled all the way to  $V_{DD}$ . All other pins with enabled pullup resistors will have an unloaded measurement of  $V_{DD}$ .

### 6.5 Stop Modes

Depending on the stop mode, I/O functions differently as the result of executing a STOP instruction. An explanation of I/O behavior for the various stop modes follows:

- When the MCU enters stop1 mode, all internal registers, including general-purpose I/O control and data registers, are powered down. All of the general-purpose I/O pins assume their reset state: output buffers and pullups turned off. Upon exit from stop1, all I/O must be initialized as if the MCU had been reset.

- When the MCU enters stop2 mode, the internal registers are powered down as in stop1 but the I/O pin states are latched and held. For example, a port pin that is an output driving low continues to function as an output driving low even though its associated data direction and output data registers are powered down internally. Upon exit from stop2, the pins continue to hold their states until a 1 is written to the PPDACK bit. To avoid discontinuity in the pin state following exit from stop2, the user must restore the port control and data registers to the values they held befor4e entering stop2. These values can be stored in RAM before entering stop2 because the RAM is maintained during stop2.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.6 Parallel I/O Registers and Control Bits

This section provides information about all registers and control bits associated with the parallel I/O ports.

Refer to tables in the Memory chapter for the absolute address assignments for all parallel I/O registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

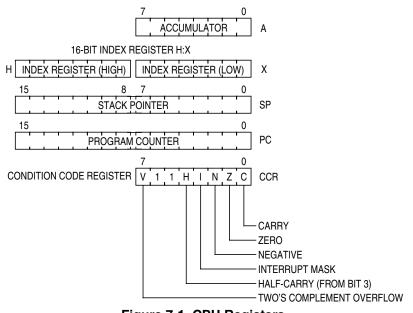

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

# 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where the specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

# 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>V | Two's Complement Overflow Flag — The CPU sets the overflow flag when a two's complement overflow occurs.         The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.         0       No overflow         1       Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4<br>H | <ul> <li>Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.</li> <li>0 No carry between bits 3 and 4</li> <li>1 Carry between bits 3 and 4</li> </ul>                                                                                                    |

| 3<br>  | Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.<br>Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.<br>0 Interrupts enabled<br>1 Interrupts disabled |

| 2<br>N | <ul> <li>Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.</li> <li>0 Non-negative result</li> <li>1 Negative result</li> </ul>                                                                                                                                                                                                                                                                                             |

| 1<br>Z | <ul> <li>Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.</li> <li>0 Non-zero result</li> <li>1 Zero result</li> </ul>                                                                                                                                                                                                                                                                                                                                                        |

| 0<br>C | Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.<br>0 No carry out of bit 7<br>1 Carry out of bit 7                                                                                                                                                                                                                                                                                                                                       |

### Table 7-1. CCR Register Field Descriptions

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location

Central Processor Unit (S08CPUV2)Central Processor Unit (S08CPUV2)

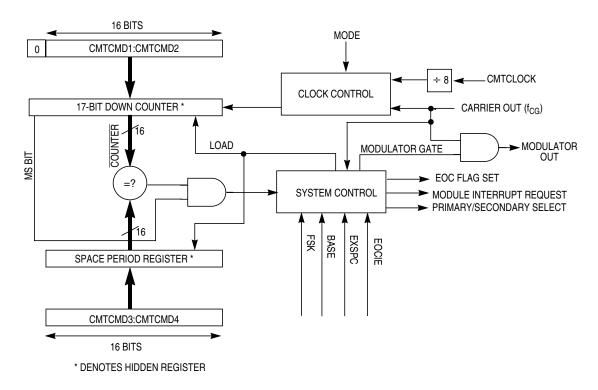

# **Chapter 8 Carrier Modulator Timer (S08CMTV1)**

#### 8.1 Introduction

#### NOTES:

- Port pins are software configurable with pullup device if input port

PTA0 does not have a clamp diode to VDD. PTA0 should not be driven above VDD. Also, PTA0 does not pullup to VDD when internal pullup is enabled.

- 3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1) The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

- 5. High current drive

- Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1). 6

### Figure 8-1. MC9S08RC/RD/RE/RG Block Diagram

Carrier Modulator Transmitter (CMT) Block Description

### Figure 8-4. Modulator Block Diagram

### 8.5.2.1 Time Mode

When the modulator operates in time mode (MCGEN bit is set, BASE bit is clear, and FSK bit is clear), the modulation mark period consists of an integer number of CMTCLK  $\div$  8 clock periods. The modulation space period consists of zero or an integer number of CMTCLK  $\div$  8 clock periods. With an 8 MHz bus and CMTDIV1:CMTDIV0 = 00, the modulator resolution is 1 µs and has a maximum mark and space period of about 65.535 ms each. See Figure 8-5 for an example of the time mode and baseband mode outputs.

The mark and space time equations for time and baseband mode are:

$$\mathbf{t}_{mark} = (CMTCMD1:CMTCMD2 + 1) \div (\mathbf{f}_{CMTCLK} \div 8)$$

Eqn. 8-5

$$t_{space} = CMTCMD3:CMTCMD4 \div (f_{CMTCLK} \div 8)$$

Eqn. 8-6

where CMTCMD1:CMTCMD2 and CMTCMD3:CMTCMD4 are the decimal values of the concatenated registers.

### NOTE

If the modulator is disabled while the  $t_{mark}$  time is less than the programmed carrier high time ( $t_{mark} < CMTCGH1/f_{CMTCLK}$ ), the modulator can enter into an illegal state and end the curent cycle before the programmed value. Make sure to program  $t_{mark}$  greater than the carrier high time to avoid this illegal state.

#### Carrier Modulator Transmitter (CMT) Block Description

$t_{exspace} = t_{space} + (t_{mark} + t_{space}) x$  (number of modulation periods)

Eqn. 8-9

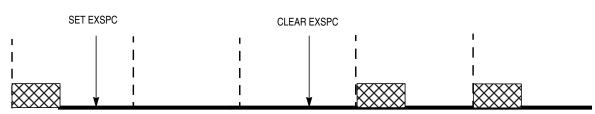

For an example of extended space operation, see Figure 8-7.

### NOTE

The EXSPC feature can be used to emulate a zero mark event.

Figure 8-7. Extended Space Operation

### 8.5.3.2 EXSPC Operation in FSK Mode

In FSK mode, the modulator continues to count carrier out clocks, alternating between the primary and secondary registers at the end of each modulation period.

To calculate the length of an extended space in FSK mode, the user must know whether the EXSPC bit was set on a primary or secondary modulation period, as well as the total number of both primary and secondary modulation periods completed while the EXSPC bit is high. A status bit for the current modulation is not accessible to the CPU. If necessary, software should maintain tracking of the current modulation cycle (primary or secondary). The extended space period ends at the completion of the space period time of the modulation period during which the EXSPC bit is cleared.

If the EXSPC bit was set during a primary modulation cycle, use the equation:

$$t_{exspace} = (t_{space})_{p} + (t_{mark} + t_{space})_{s} + (t_{mark} + t_{space})_{p} + \dots \qquad Eqn. 8-10$$

Where the subscripts p and s refer to mark and space times for the primary and secondary modulation cycles.

If the EXSPC bit was set during a secondary modulation cycle, use the equation:

$$t_{exspace} = (t_{space})_{s} + (t_{mark} + t_{space})_{p} + (t_{mark} + t_{space})_{s} + \dots \qquad Eqn. 8-11$$

### 8.5.4 Transmitter

The transmitter output block controls the state of the infrared out pin (IRO). The modulator output is gated on to the IRO pin when the modulator/carrier generator is enabled. When the modulator/carrier generator is disabled, the IRO pin is controlled by the state of the IRO latch.

A polarity bit in the CMTOC register enables the IRO pin to be high true or low true.

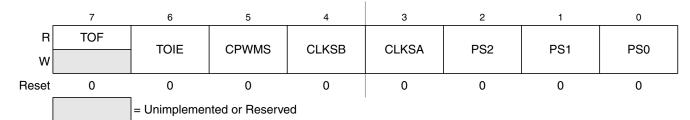

# 10.7.1 Timer Status and Control Register (TPM1SC)

TPM1SC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

### Figure 10-5. Timer Status and Control Register (TPM1SC)

#### Table 10-1. TPM1SC Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to \$0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.         0 TOF interrupts inhibited (use software polling)         1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All TPM1 channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPM1 channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table 10-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 10-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Timer/PWM (TPM)

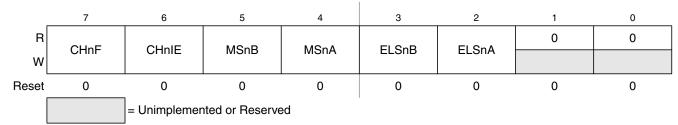

# 10.7.4 Timer Channel n Status and Control Register (TPM1CnSC)

TPM1CnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

### Figure 10-10. Timer Channel n Status and Control Register (TPM1CnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | <ul> <li>Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.</li> <li>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPM1CnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.</li> <li>No input capture or output compare event occurred on channel n</li> </ul> |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>0 Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 10-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 10-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 10-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin. This is also the setting required for channel 0 when the TPM1CH0 pin is used as an external clock input.                                                                                                                                                                                                                                                                                      |

### Table 10-4. TPM1CnSC Register Field Descriptions

Serial Peripheral Interface (SPI) Module

BIDIROE — Bidirectional Mode Output Enable

When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1, BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin. Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI1 (MOMI) or MISO1 (SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.

1 =SPI I/O pin enabled as an output.

0 = Output driver disabled so SPI data I/O pin acts as an input.

SPISWAI — SPI Stop in Wait Mode

1 =SPI clocks stop when the MCU enters wait mode.

0 = SPI clocks continue to operate in wait mode.

SPC0 — SPI Pin Control 0

The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO1 (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI1 (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.

1 = SPI configured for single-wire bidirectional operation.

0 = SPI uses separate pins for data input and data output.

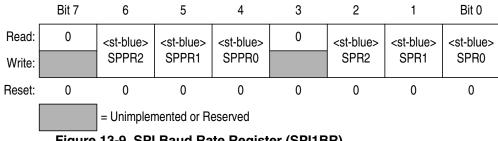

# 13.4.3 SPI Baud Rate Register (SPI1BR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

Figure 13-9. SPI Baud Rate Register (SPI1BR)

SPPR2:SPPR1:SPPR0 — SPI Baud Rate Prescale Divisor

This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 13-2. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 13-4).

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 15.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 15.2.2, "Communication Details," for more detail.

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a development system is connected, it can pull both BKGD and RESET low, release RESET to select active background mode rather than normal operating mode, then release BKGD. It is not necessary to reset the target MCU to communicate with it through the background debug interface.

# 15.2.2 Communication Details

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.