Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | SCI, SPI                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 25                                                         |

| Program Memory Size        | 60KB (60K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 2K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08rg60fje |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

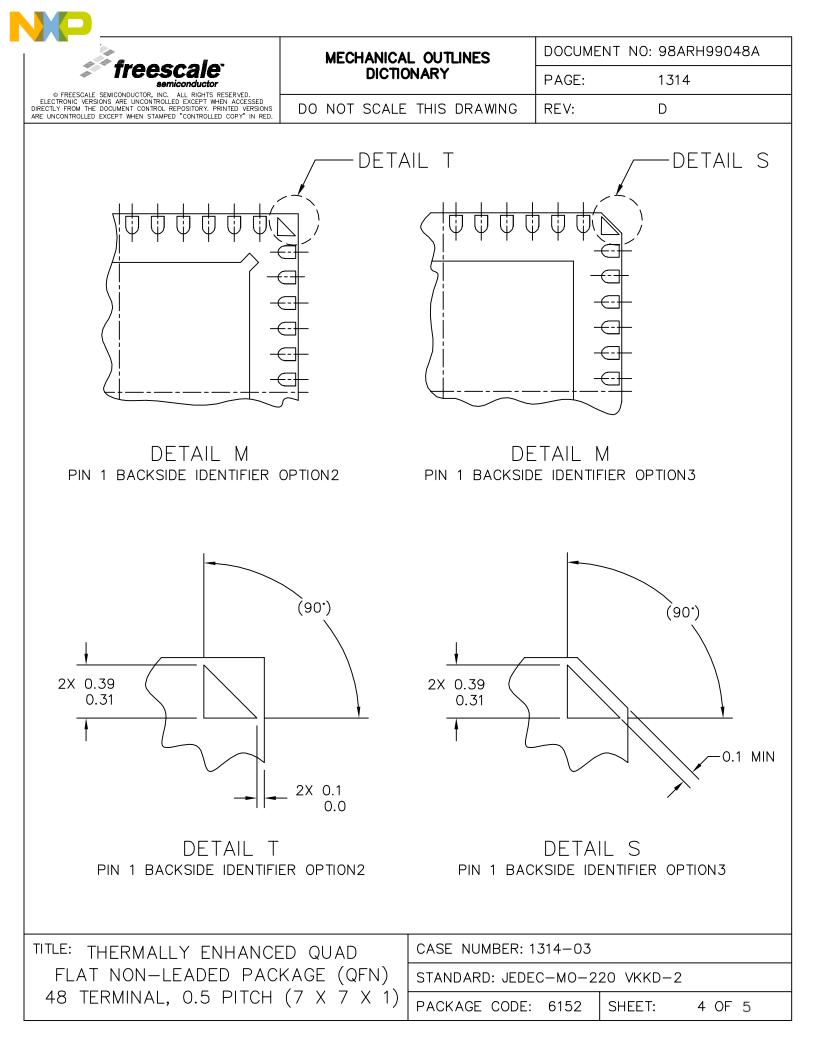

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |  |  |  |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|--|--|--|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |  |  |  |

| MC9S08AC16    |                     |                                                 |                                                  |  |  |  |

| MC9S908AC60   |                     |                                                 |                                                  |  |  |  |

| MC9S08AC128   |                     |                                                 |                                                  |  |  |  |

| MC9S08AW60    |                     |                                                 |                                                  |  |  |  |

| MC9S08GB60A   |                     |                                                 |                                                  |  |  |  |

| MC9S08GT16A   |                     |                                                 |                                                  |  |  |  |

| MC9S08JM16    |                     |                                                 |                                                  |  |  |  |

| MC9S08JM60    |                     |                                                 |                                                  |  |  |  |

| MC9S08LL16    |                     |                                                 |                                                  |  |  |  |

| MC9S08QE128   |                     |                                                 |                                                  |  |  |  |

| MC9S08QE32    |                     |                                                 |                                                  |  |  |  |

| MC9S08RG60    |                     |                                                 |                                                  |  |  |  |

| MCF51CN128    |                     |                                                 |                                                  |  |  |  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |  |  |  |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |  |  |  |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |  |  |  |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |  |  |  |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |  |  |  |

| MC9S08QB8     |                     |                                                 |                                                  |  |  |  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |  |  |  |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |  |  |  |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |  |  |  |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |  |  |  |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |  |  |  |

| MC9S08QG8     |                     |                                                 |                                                  |  |  |  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |  |  |  |

#### Resets, Interrupts, and System Configuration

The MC9S08RC/RD/RE/RG has these sources for reset:

- Power-on reset (POR)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect

- Illegal address (16K and 8K devices only)

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the reset pin is driven low for 34 internal bus cycles where the internal bus frequency is one-half the OSC frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.8.4, "System Options Register (SOPT)," for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods  $(2^{18} \text{ or } 2^{20} \text{ cycles of the bus rate clock})$ . Even if the application will use the reset default settings in COPE and COPT, the user must write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer must not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it was before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such

#### Resets, Interrupts, and System Configuration

| _                   | 7   | 6   | 5                | 4              | 3                   | 2               | 1   | 0 |  |  |  |  |  |

|---------------------|-----|-----|------------------|----------------|---------------------|-----------------|-----|---|--|--|--|--|--|

| R                   | POR | PIN | COP              | ILOP           | ILAD <sup>(1)</sup> | 0               | LVD | 0 |  |  |  |  |  |

| w                   |     | Wr  | riting any value | e to SRS addre | ess clears COF      | watchdog timer. |     |   |  |  |  |  |  |

| POR                 | 1   | 0   | 0                | 0              | 0                   | 0               | 1   | 0 |  |  |  |  |  |

| LVR                 | u   | 0   | 0                | 0              | 0                   | 0               | 1   | 0 |  |  |  |  |  |

| Any other<br>reset: | 0   | (2) | (2)              | (2)            | (2)                 | 0               | 0   | 0 |  |  |  |  |  |

u = Unaffected by reset

Т

### Figure 5-3. System Reset Status (SRS)

- 1. The ILAD bit is only present in 16K and 8K versions of the devices.

- 2. Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                                                                                                                                                                                                                                         |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out.</li> <li>This reset source may be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul>                                                                                                                                                                                                                     |

| 3<br>ILAD | <ul> <li>Illegal Address Access — Reset was caused by an attempt to access a designated illegal address.</li> <li>0 Reset not caused by an illegal address access</li> <li>1 Reset caused by an illegal address access</li> <li>Illegal address areas only exist in the 16K and 8K versions and are defined as: <ul> <li>\$0440-\$17FF — Gap from end of RAM to start of high-page registers</li> <li>\$1834-\$BFFF — Gap from end of high-page registers to start of FLASH memory</li> </ul> </li> <li>Unused and reserved locations in register areas are not considered designated illegal addresses and do not trigger illegal address resets.</li> </ul> |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset occurs. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR</li> <li>1 Reset caused by LVD trip or POR</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 5-3. SRS Field Descriptions

Parallel Input/Output

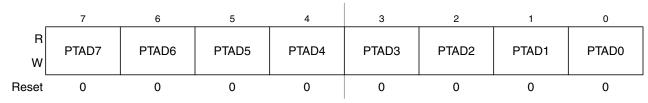

# 6.6.1 Port A Registers (PTAD, PTAPE, and PTADD)

Port A pins used as general-purpose I/O pins are controlled by the port A data (PTAD), data direction (PTADD), and pullup enable (PTAPE) registers.

Figure 6-6. Port A Data Register (PTAD)

## Table 6-1. PTAD Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTAD[7:0] | Port A Data Register Bits — For port A pins that are inputs, reads of this register return the logic level on the pin. For port A pins that are configured as outputs, reads of this register return the last value written to this register. Writes are latched into all bits of this register. For port A pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTAD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTAPE7 | PTAPE6 | PTAPE5 | PTAPE4 | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

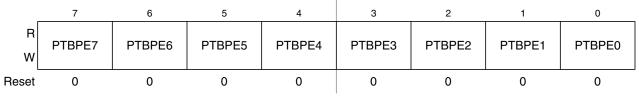

Figure 6-7. Pullup Enable for Port A (PTAPE)

### Table 6-2. PTAPE Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTAPE[7:0] | <ul> <li>Pullup Enable for Port A Bits — For port A pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled provided the corresponding PTADDn is a logic 0. For port A pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled. When any of bits 7 through 4 of port A are enabled as KBI inputs and are configured to detect rising edges/high levels, the pullup enable bits enable pulldown rather than pullup devices.</li> <li>0 Internal pullup device enabled.</li> <li>1 Internal pullup device enabled.</li> </ul> |

Parallel Input/Output

## Figure 6-10. Pullup Enable for Port B (PTBPE)

## Table 6-5. PTBPE Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBPE[7:0] | <ul> <li>Pullup Enable for Port B Bits — For port B pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port B pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled.</li> <li>1 Internal pullup device enabled.</li> </ul> |

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

## Figure 6-11. Data Direction for Port B (PTBDD)

## Table 6-6. PTBDD Field Descriptions

| Field             | Description                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDD[7:0] | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                             |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ol> |

| Source                                                                                                                    |                                            | Description                                                                                                                                                                                                                                   |   | C | Effect<br>on CCR |   |   |   | ess                                                 | Opcode<br>Operand                  | and                                 | rcles <sup>1</sup>              |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|---|---|---|-----------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                                      | Operation                                  | Description                                                                                                                                                                                                                                   |   |   | I                | N | z | с | Address<br>Mode                                     | Opc                                | Oper                                | Bus Cycles <sup>1</sup>         |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX ,X<br>LDX oprx16,SP<br>LDX oprx8,SP           | Load X (Index Register<br>Low) from Memory | $X \gets (M)$                                                                                                                                                                                                                                 | 0 | _ | _                |   |   | - | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | DE<br>EE<br>FE                     | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2 3 4 4 3 3 5 4                 |

| LSL opr8a<br>LSLA<br>LSLX<br>LSL oprx8,X<br>LSL ,X<br>LSL oprx8,SP                                                        | Logical Shift Left<br>(Same as ASL)        | C                                                                                                                                                                                                                                             |   | _ | _                |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68 |                                     | 511546                          |

| LSR opr8a<br>LSRA<br>LSRX<br>LSR oprx8,X<br>LSR ,X<br>LSR oprx8,SP                                                        | Logical Shift Right                        |                                                                                                                                                                                                                                               |   | _ | _                | 0 |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64 | ff                                  | 511546                          |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                                      | Move                                       | $(M)_{destination} \leftarrow (M)_{source}$<br>H:X $\leftarrow$ (H:X) + 0x0001 in<br>IX+/DIR and DIR/IX+ Modes                                                                                                                                | 0 | - | -                |   |   | - | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR            | 4E<br>5E<br>6E<br>7E               | ii dd                               | 554<br>5                        |

| MUL                                                                                                                       | Unsigned multiply                          | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                                                               | - | 0 | -                | - | - | 0 | INH                                                 | 42                                 |                                     | 5                               |

| NEG opr8a<br>NEGA<br>NEGX<br>NEG oprx8,X<br>NEG ,X<br>NEG oprx8,SP                                                        | Negate<br>(Two's Complement)               | $\begin{array}{l} M \leftarrow - (M) = 0x00 - (M) \\ A \leftarrow - (A) = 0x00 - (A) \\ X \leftarrow - (X) = 0x00 - (X) \\ M \leftarrow - (M) = 0x00 - (M) \\ M \leftarrow - (M) = 0x00 - (M) \\ M \leftarrow - (M) = 0x00 - (M) \end{array}$ |   | - | -                |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60 | ff                                  | 5<br>1<br>5<br>4<br>6           |

| NOP                                                                                                                       | No Operation                               | Uses 1 Bus Cycle                                                                                                                                                                                                                              | - | - | -                | - | - | - | INH                                                 | 9D                                 |                                     | 1                               |

| NSA                                                                                                                       | Nibble Swap<br>Accumulator                 | A ← (A[3:0]:A[7:4])                                                                                                                                                                                                                           | - | - | -                | - | - | - | INH                                                 | 62                                 |                                     | 1                               |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator<br>and Memory     | $A \gets (A) \mid (M)$                                                                                                                                                                                                                        | 0 | - | -                |   |   | - | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | DA<br>EA<br>FA                     | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| PSHA                                                                                                                      | Push Accumulator onto<br>Stack             | $Push\ (A);\ SP\leftarrow (SP)-0x0001$                                                                                                                                                                                                        | - | - | -                | - | - | - | INH                                                 | 87                                 |                                     | 2                               |

| PSHH                                                                                                                      | Push H (Index Register<br>High) onto Stack | $Push \text{ (H); SP} \leftarrow \text{(SP)} - 0x0001$                                                                                                                                                                                        | - | - | -                | - | - | - | INH                                                 | 8B                                 |                                     | 2                               |

| PSHX                                                                                                                      | Push X (Index Register<br>Low) onto Stack  | $Push \text{ (X); SP} \leftarrow \text{ (SP)} - 0x0001$                                                                                                                                                                                       | - | - | -                | - | - | - | INH                                                 | 89                                 |                                     | 2                               |

| PULA                                                                                                                      | Pull Accumulator from<br>Stack             | $SP \leftarrow (SP + 0x0001);  Pull  (A)$                                                                                                                                                                                                     | - | - | -                | - | - | - | INH                                                 | 86                                 |                                     | 3                               |

| PULH                                                                                                                      | Pull H (Index Register<br>High) from Stack | $SP \leftarrow (SP + 0x0001); Pull\ (H)$                                                                                                                                                                                                      | - | - | -                | - | - | - | INH                                                 | 8A                                 |                                     | 3                               |

| PULX                                                                                                                      | Pull X (Index Register<br>Low) from Stack  | $SP \gets (SP + 0x0001); Pull\ (X)$                                                                                                                                                                                                           | - | - | -                | - | - | - | INH                                                 | 88                                 | _                                   | 3                               |

| ROL <i>opr8a</i><br>ROLA<br>ROLX<br>ROL <i>oprx8</i> ,X<br>ROL ,X<br>ROL <i>oprx8</i> ,SP                                 | Rotate Left through Carry                  | b7 b0                                                                                                                                                                                                                                         |   | _ | _                |   |   |   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69 |                                     | 5<br>1<br>5<br>4<br>6           |

### MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

-

# **Chapter 8 Carrier Modulator Timer (S08CMTV1)**

#### 8.1 Introduction

#### NOTES:

- Port pins are software configurable with pullup device if input port

PTA0 does not have a clamp diode to VDD. PTA0 should not be driven above VDD. Also, PTA0 does not pullup to VDD when internal pullup is enabled.

- 3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1) The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

- 5. High current drive

- Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1). 6

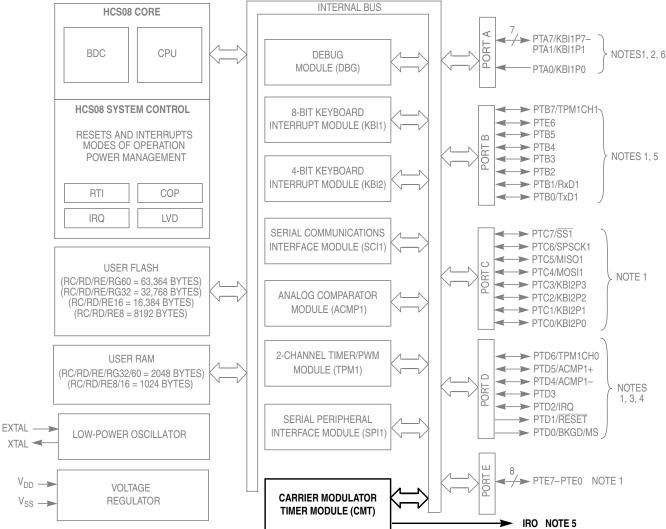

### Figure 8-1. MC9S08RC/RD/RE/RG Block Diagram

#### MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

#### Timer/PWM (TPM)

In input capture mode, reading either byte (TPM1CnVH or TPM1CnVL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This latching mechanism also resets (becomes unlatched) when the TPM1CnSC register is written.

In output compare or PWM modes, writing to either byte (TPM1CnVH or TPM1CnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPM1CnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

# Chapter 12 Serial Communications Interface (S08SCIV1)

# 12.1 Introduction

# 12.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

# 12.1.2 Modes of Operation

See Section 12.3, "Functional Description," for a detailed description of SCI operation in the different modes.

- 8- and 9- bit data modes

- Stop modes SCI is halted during all stop modes

- Loop modes

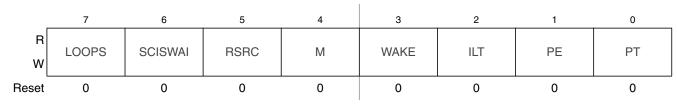

# 12.2.2 SCI Control Register 1 (SCI1C1)

This read/write register is used to control various optional features of the SCI system.

### Figure 12-5. SCI Control Register 1 (SCI1C1)

### Table 12-3. SCI1C1 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                     |  |  |  |  |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>0 Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>1 Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |  |  |  |  |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters<br/>start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                          |  |  |  |  |

| 3<br>WAKE    | <ul> <li>Receiver Wakeup Method Select — Refer to Section 12.3.3.2, "Receiver Wakeup Operation" for more information.</li> <li>0 Idle-line wakeup.</li> <li>1 Address-mark wakeup.</li> </ul>                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 2<br>ILT     | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of the logic high level by the idle line detection logic. Refer to Section 12.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit.                                                               |  |  |  |  |

| 1<br>PE      | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significan bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                                                                                   |  |  |  |  |

| 0<br>PT      | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                                                                               |  |  |  |  |

### Table 12-4. SCI1C2 Register Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1<br>RWU | <ul> <li>Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 12.3.3.2, "Receiver Wakeup Operation," for more details.</li> <li>0 Normal SCI receiver operation.</li> <li>1 SCI receiver in standby waiting for wakeup condition.</li> </ul> |  |  |  |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 12.3.2.1, "Send Break and Queued Idle," for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                     |  |  |  |

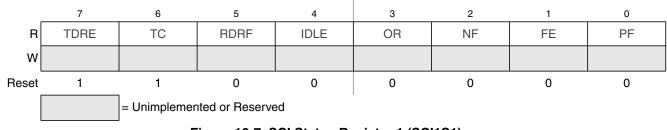

# 12.2.4 SCI Status Register 1 (SCI1S1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

## Figure 12-7. SCI Status Register 1 (SCI1S1)

### Table 12-5. SCI1S1 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set immediately after reset and when a transmit data value<br>transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To<br>clear TDRE, read SCI1S1 with TDRE = 1 and then write to the SCI data register (SCI1D).0Transmit data register (buffer) full.<br>11Transmit data register (buffer) empty.                                                                                                                                                                                                                          |  |  |  |

| 6<br>TC   | <ul> <li>Transmission Complete Flag — TC is set immediately after reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.</li> <li>0 Transmitter active (sending data, a preamble, or a break).</li> <li>1 Transmitter idle (transmission activity complete).</li> <li>TC is cleared automatically by reading SCI1S1 with TC = 1 and then doing one of the following three things: <ul> <li>Write to the SCI data register (SCI1D) to transmit new data</li> <li>Queue a preamble by changing TE from 0 to 1</li> <li>Queue a break character by writing 1 to SBK in SCI1C2</li> </ul> </li> </ul> |  |  |  |

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS1}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

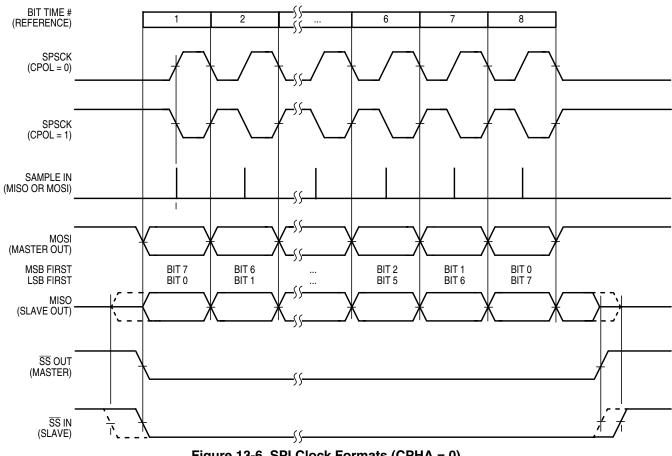

Figure 13-6 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 13-6. SPI Clock Formats (CPHA = 0)

MC9S08RC/RD/RE/RG Data Sheet, Rev. 1.11

# 13.3.3 SPI Interrupts

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

# 13.3.4 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS1}$  pin (provided the  $\overline{SS1}$  pin is configured as the mode fault input signal). The  $\overline{SS1}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS1}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK1, MOSI1, and MISO1 (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPI1C1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

# 13.4 SPI Registers and Control Bits

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Serial Peripheral Interface (SPI) Module

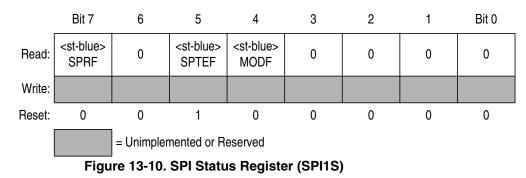

# 13.4.4 SPI Status Register (SPI1S)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0s. Writes have no meaning or effect.

## SPRF — SPI Read Buffer Full Flag

SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPI1D). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.

1 = Data available in the receive data buffer.

0 = No data available in the receive data buffer.

## SPTEF — SPI Transmit Buffer Empty Flag

This bit is set when there is room in the transmit data buffer. It is cleared by reading SPI1S with SPTEF set, followed by writing a data value to the transmit buffer at SPI1D. SPI1S must be read with SPTEF = 1 before writing data to SPI1D or the SPI1D write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPI1C1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPI1D is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter.

1 = SPI transmit buffer empty.

0 = SPI transmit buffer not empty.

MODF — Master Mode Fault Flag

MODF is set if the SPI is configured as a master and the slave select input goes low, indicating some other SPI device is also configured as a master. The  $\overline{SS1}$  pin acts as a mode fault error input only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by reading MODF while it is 1, then writing to SPI control register 1 (SPI1C1).

1 = Mode fault error detected.

0 = No mode fault error.

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte located at H:X                              |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |

|                     |                              |                     |                                                                                          |

## Table 15-1. BDC Command Summary

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

Development Support

# 15.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 15.3.6, "Hardware Breakpoints."

# 15.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

# 15.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

#### Development Support

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

# 15.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.