#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | A/D 5x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite05y0b6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

\_

| 10 I. | /O P0     | ORTS                                                                                         | 42  |

|-------|-----------|----------------------------------------------------------------------------------------------|-----|

| 1     | 10.1      |                                                                                              | 42  |

| 1     | 10.2      | FUNCTIONAL DESCRIPTION                                                                       | 42  |

| 1     | 10.3      | UNUSED I/O PINS                                                                              | 46  |

| 1     | 10.4      | LOW POWER MODES                                                                              | 46  |

| 1     | 10.5      | INTERRUPTS                                                                                   | 46  |

| 1     | 10.6      | I/O PORT IMPLEMENTATION                                                                      | 46  |

| 11 (  | ON-C      | HIP PERIPHERALS                                                                              | 48  |

| 1     | 11.1      | LITE TIMER (LT)                                                                              |     |

| 1     | 11.2      | 12-BIT AUTORELOAD TIMER (AT)                                                                 |     |

| 1     | 11.3      | SERIAL PERIPHERAL INTERFACE (SPI)                                                            | 59  |

|       |           | 8-BIT A/D CONVERTER (ADC)                                                                    |     |

| 12 I  | NSTE      |                                                                                              |     |

|       | 12.1      | ST7 ADDRESSING MODES                                                                         |     |

|       |           | INSTRUCTION GROUPS                                                                           |     |

| 13 E  | ELEC      |                                                                                              | -   |

| 1     | 13.1      | PARAMETER CONDITIONS                                                                         | -   |

| 1     | 13.2      | ABSOLUTE MAXIMUM RATINGS                                                                     |     |

| 1     | 13.3      | OPERATING CONDITIONS                                                                         |     |

| 1     | 13.4      | SUPPLY CURRENT CHARACTERISTICS                                                               |     |

| 1     | 13.5      | CLOCK AND TIMING CHARACTERISTICS                                                             |     |

| 1     | 13.6      | MEMORY CHARACTERISTICS                                                                       |     |

| 1     | 13.7      | EMC (ELECTROMAGNETIC COMPATIBILITY) CHARACTERISTICS                                          |     |

| 1     | 13.8      | I/O PORT PIN CHARACTERISTICS                                                                 | 95  |

| 1     | 13.9      | CONTROL PIN CHARACTERISTICS 10                                                               | 00  |

| 1     | 13.10     | COMMUNICATION INTERFACE CHARACTERISTICS                                                      | 02  |

| 1     | 13.11     | 8-BIT ADC CHARACTERISTICS 10                                                                 | 04  |

| 14 F  | PACK      | (AGE CHARACTERISTICS                                                                         |     |

|       | 14.1      |                                                                                              |     |

|       |           | THERMAL CHARACTERISTICS 1                                                                    |     |

|       |           | CE CONFIGURATION AND ORDERING INFORMATION                                                    |     |

|       | -         | OPTION BYTES 1                                                                               |     |

|       |           | DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE 1                                  |     |

|       |           | DEVELOPMENT TOOLS                                                                            |     |

|       |           | ST7 APPLICATION NOTES                                                                        |     |

|       |           | WN LIMITATIONS                                                                               |     |

|       |           | EXECUTION OF BTJX INSTRUCTION 12                                                             |     |

| 1     | 16.2<br>V | IN-CIRCUIT PROGRAMMING OF DEVICES PREVIOUSLY PROGRAMMED WITH HAF<br>WARE WATCHDOG OPTION 121 | ≀D- |

| 1     | 16.3      | IN-CIRCUIT DEBUGGING WITH HARDWARE WATCHDOG 12                                               | 21  |

| 1     | 16.4      | RECOMMENDATIONS WHEN LVD IS ENABLED                                                          | 21  |

| 1     | 16.5      | CLEARING ACTIVE INTERRUPTS OUTSIDE INTERRUPT ROUTINE 12                                      | 21  |

| 17 F  | REVIS     | SION HISTORY                                                                                 | 22  |

| Pin   | Pin n°  |            |      | Level |        | Port / Control |     |     |     | ol  |     |                  |                          |

|-------|---------|------------|------|-------|--------|----------------|-----|-----|-----|-----|-----|------------------|--------------------------|

| 0     | IP16    | Pin Name   | Type | L.    | ıt     |                | Inp | out |     | Out | put | Main<br>Function | Alternate Function       |

| QFN20 | SO16/DI |            | Ту   | Input | Output | float          | ndw | int | ana | OD  | ЬΡ  | (after reset)    | Alternate Function       |

| 15    | 14      | PA2/ATPWM0 | I/O  | $C_T$ | HS     | Х              | Х   |     |     | Х   | Х   | Port A2          | Auto-Reload Timer PWM0   |

| 16    | 15      | PA1        | I/O  | $C_T$ | HS     | Х              | Х   |     |     | х   | Х   | Port A1          |                          |

| 17    | 16      | PA0/LTIC   | I/O  | $C_T$ | HS     | X              | е   | i0  |     | Х   | Х   | Port A0          | Lite Timer Input Capture |

# Note:

In the interrupt input column, " $ei_x$ " defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

57

# DATA EEPROM (Cont'd)

# **5.7 REGISTER DESCRIPTION**

# EEPROM CONTROL/STATUS REGISTER (EEC-

SR) Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |       | 0     |

|---|---|---|---|---|---|-------|-------|

| 0 | 0 | 0 | 0 | 0 | 0 | E2LAT | E2PGM |

Bits 7:2 = Reserved, forced by hardware to 0.

## Bit 1 = E2LAT Latch Access Transfer

This bit is set by software. It is cleared by hardware at the end of the programming cycle. It can only be cleared by software if the E2PGM bit is cleared.

0: Read mode

1: Write mode

# Bit 0 = **E2PGM** *Programming control and status*

This bit is set by software to begin the programming cycle. At the end of the programming cycle, this bit is cleared by hardware.

0: Programming finished or not yet started

1: Programming cycle is in progress

**Note**: If the E2PGM bit is cleared during the programming cycle, the memory data is not guaranteed.

## Table 4. DATA EEPROM Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label    | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|-------------------|----------------------|---|---|---|---|---|---|------------|------------|

| 0030h             | EECSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | E2LAT<br>0 | E2PGM<br>0 |

<u>ل</u>حک

# POWER SAVING MODES (Cont'd)

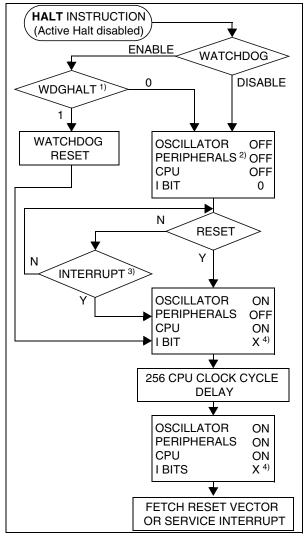

### 9.4.2 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when active halt mode is disabled.

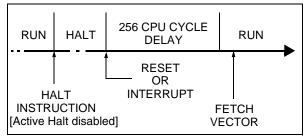

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 6, "Interrupt Mapping," on page 30) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 28).

When entering HALT mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see section 15.1 on page 112 for more details).

# Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 6, "Interrupt Mapping," on page 30 for more details.

**4.** Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

**5.** If the PLL is enabled by option byte, it outputs the clock after a delay of t<sub>STARTUP</sub> (see Figure 13).

# Figure 28. HALT Mode Flow-chart

### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING:** The analog input voltage level must be within the limits stated in the absolute maximum ratings.

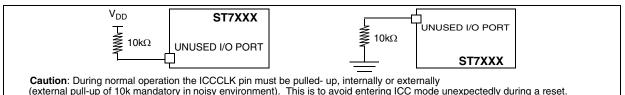

#### 10.3 UNUSED I/O PINS

Unused I/O pins must be connected to fixed voltage levels. Refer to Section 13.8.

#### **10.4 LOW POWER MODES**

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### **10.5 INTERRUPTS**

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |

#### **10.6 I/O PORT IMPLEMENTATION**

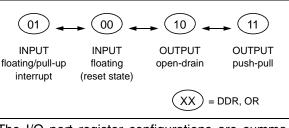

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 30 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 30. Interrupt I/O Port State Transitions

The I/O port register configurations are summarised as follows.

| Port   | Pin name     | Input (  | DDR=0)            | Output (DDR=1) |           |  |

|--------|--------------|----------|-------------------|----------------|-----------|--|

| POIL   | Fill fidilie | OR = 0   | OR = 1            | OR = 0         | OR = 1    |  |

|        | PA7          | floating | pull-up interrupt | open drain     | push-pull |  |

| Port A | PA6:1        | floating | pull-up           | open drain     | push-pull |  |

|        | PA0          | floating | pull-up interrupt | open drain     | push-pull |  |

|        | PB4          | floating | pull-up           | open drain     | push-pull |  |

| Port B | PB3          | floating | pull-up interrupt | open drain     | push-pull |  |

| TOILD  | PB2:1        | floating | pull-up           | open drain     | push-pull |  |

|        | PB0          | floating | pull-up interrupt | open drain     | push-pull |  |

#### **Table 11. Port Configuration**

# I/O PORTS (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label    | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|-------------------|----------------------|----------|---|---|---|---|---|---|----------|

| 0000h             | PADR<br>Reset Value  | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| 0001h             | PADDR<br>Reset Value | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| 0002h             | PAOR<br>Reset Value  | MSB<br>0 | 1 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| 0003h             | PBDR<br>Reset Value  | MSB<br>1 | 1 | 1 | 0 | 0 | 0 | 0 | LSB<br>0 |

| 0004h             | PBDDR<br>Reset Value | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| 0005h             | PBOR<br>Reset Value  | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

# Table 12. I/O Port Register Map and Reset Values

# **11 ON-CHIP PERIPHERALS**

# 11.1 LITE TIMER (LT)

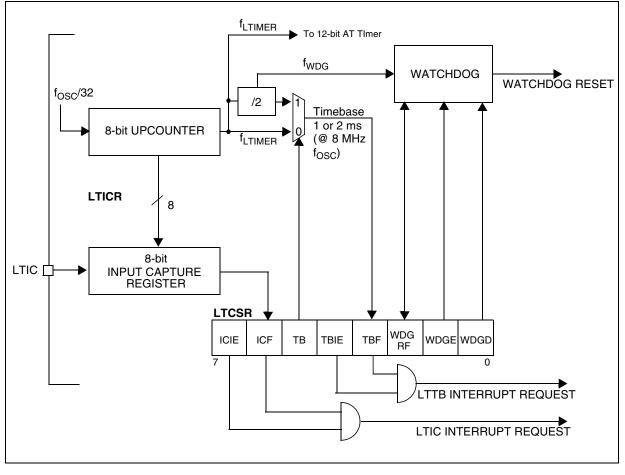

# 11.1.1 Introduction

The Lite Timer can be used for general-purpose timing functions. It is based on a free-running 8-bit upcounter with two software-selectable timebase periods, an 8-bit input capture register and watch-dog function.

## 11.1.2 Main Features

- Realtime Clock

- 8-bit upcounter

- 1 ms or 2 ms timebase period (@ 8 MHz f<sub>OSC</sub>)

- Maskable timebase interrupt

- Input Capture

- 8-bit input capture register (LTICR)

- Maskable interrupt with wakeup from Halt Mode capability

# Figure 31. Lite Timer Block Diagram

- Watchdog

- Enabled by hardware or software (configurable by option byte)

- Optional reset on HALT instruction (configurable by option byte)

- Automatically resets the device unless disable bit is refreshed

47/

- Software reset (Forced Watchdog reset)

- Watchdog reset status flag

# LITE TIMER (Cont'd)

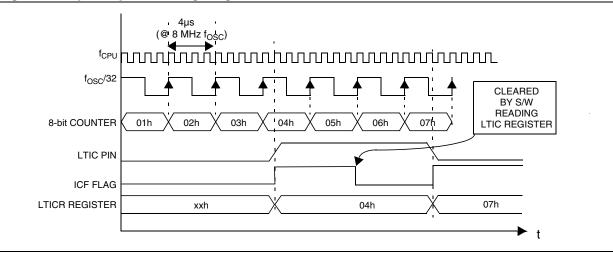

## Input Capture

The 8-bit input capture register is used to latch the free-running upcounter after a rising or falling edge is detected on the LTIC pin. When an input capture occurs, the ICF bit is set and the LTICR register contains the value of the free-running upcounter. An interrupt is generated if the ICIE bit is set. The ICF bit is cleared by reading the LTICR register.

The LTICR is a read only register and always contains the data from the last input capture. Input capture is inhibited if the ICF bit is set.

#### 11.1.4 Low Power Modes

5/

| Mode        | Description                            |

|-------------|----------------------------------------|

|             | No effect on Lite timer                |

| SLOW        | (this peripheral is driven directly by |

|             | f <sub>OSC</sub> /32)                  |

| WAIT        | No effect on Lite timer                |

| ACTIVE HALT | No effect on Lite timer                |

| HALT        | Lite timer stops counting              |

#### Figure 33. Input Capture Timing Diagram

#### 11.1.5 Interrupts

| Interrupt<br>Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt | Exit<br>from<br>Active-<br>Halt |

|--------------------|---------------|--------------------------|----------------------|----------------------|---------------------------------|

| Timebase<br>Event  | TBF           | TBIE                     | Yes                  | No                   | Yes                             |

| IC Event           | ICF           | ICIE                     | 1                    |                      | No                              |

**Note:** The TBF and ICF interrupt events are connected to separate interrupt vectors (see Interrupts chapter).

Timebase and IC events generate an interrupt if the enable bit is set in the LTCSR register and the interrupt mask in the CC register is reset (RIM instruction).

# LITE TIMER (Cont'd)

#### 11.1.6 Register Description

# LITE TIMER CONTROL/STATUS REGISTER (LTCSR)

Read / Write

Reset Value: 0x00 0000 (x0h)

| 7    |     |    |      |     |      |      | 0    |

|------|-----|----|------|-----|------|------|------|

| ICIE | ICF | тв | TBIE | TBF | WDGR | WDGE | WDGD |

### Bit 7 = ICIE Interrupt Enable

This bit is set and cleared by software. 0: Input Capture (IC) interrupt disabled 1: Input Capture (IC) interrupt enabled

## Bit 6 = **ICF** Input Capture Flag

This bit is set by hardware and cleared by software by reading the LTICR register. Writing to this bit does not change the bit value.

0: No input capture

1: An input capture has occurred

**Note:** After an MCU reset, software must initialise the ICF bit by reading the LTICR register

#### Bit 5 = **TB** Timebase period selection

This bit is set and cleared by software.

- 0: Timebase period =  $t_{OSC} * 8000 (1ms @ 8 MHz)$ 1: Timebase period =  $t_{OSC} * 16000 (2ms @ 8$

- 1: Timebase period = t<sub>OSC</sub> \* 16000 (2ms @ 8 MHz)

## Bit 4 = **TBIE** Timebase Interrupt enable

This bit is set and cleared by software.

- 0: Timebase (TB) interrupt disabled

- 1: Timebase (TB) interrupt enabled

#### Bit 3 = **TBF** Timebase Interrupt Flag

This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

#### Table 13. Lite Timer Register Map and Reset Values

- 0: No counter overflow

- 1: A counter overflow has occurred

### Bit 2 = **WDGRF** Force Reset/ Reset Status Flag

This bit is used in two ways: it is set by software to force a watchdog reset. It is set by hardware when a watchdog reset occurs and cleared by hardware or by software. It is cleared by hardware only when an LVD reset occurs. It can be cleared by software after a read access to the LTCSR register.

- 0: No watchdog reset occurred.

- 1: Force a watchdog reset (write), or, a watchdog reset occurred (read).

#### Bit 1 = WDGE Watchdog Enable

This bit is set and cleared by software.

0: Watchdog disabled

1: Watchdog enabled

### Bit 0 = WDGD Watchdog Reset Delay

This bit is set by software. It is cleared by hardware at the end of each t<sub>WDG</sub> period. 0: Watchdog reset not delayed 1: Watchdog reset delayed

LITE TIMER INPUT CAPTURE REGISTER

# (LTICR)

Read only Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |  |

|------|------|------|------|------|------|------|------|--|

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |  |

#### Bit 7:0 = ICR[7:0] Input Capture Value

These bits are read by software and cleared by hardware after a reset. If the ICF bit in the LTCSR is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2     | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|-------|------|------|

| 0B                | LTCSR             | ICIE | ICF  | ТВ   | TBIE | TBF  | WDGRF | WDGE | WDGD |

|                   | Reset Value       | 0    | x    | 0    | 0    | 0    | 0     | 0    | 0    |

| 0C                | LTICR             | ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2  | ICR1 | ICR0 |

|                   | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    |

# 12-BIT AUTORELOAD TIMER (Cont'd)

### 11.2.3 Functional Description

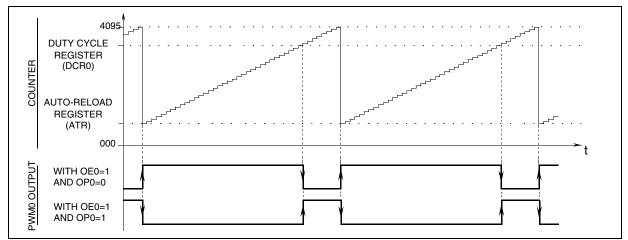

#### **PWM Mode**

This mode allows a Pulse Width Modulated signals to be generated on the PWM0 output pin with minimum core processing overhead. The PWM0 output signal can be enabled or disabled using the OE0 bit in the PWMCR register. When this bit is set the PWM I/O pin is configured as output pushpull alternate function.

**Note:** CMPF0 is available in PWM mode (see PWM0CSR description on page 57).

### **PWM Frequency and Duty Cycle**

The PWM signal frequency  $(f_{PWM})$  is controlled by the counter period and the ATR register value.

$f_{PWM} = f_{COUNTER} / (4096 - ATR)$

Following the above formula, if  $f_{CPU}$  is 8 MHz, the maximum value of  $f_{PWM}$  is 4 Mhz (ATR register value = 4094), and the minimum value is 2 kHz (ATR register value = 0).

**Note:** The maximum value of ATR is 4094 because it must be lower than the DCR value which must be 4095 in this case.

At reset, the counter starts counting from 0.

Software must write the duty cycle value in the DCR0H and DCR0L preload registers. The DCR0H register must be written first. See caution below.

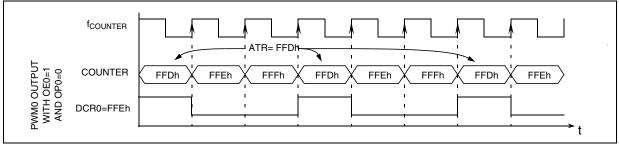

When a upcounter overflow occurs (OVF event), the ATR value is loaded in the upcounter, the preloaded Duty cycle value is transferred to the Duty Cycle register and the PWM0 signal is set to a high level. When the upcounter matches the DCRx value the PWM0 signals is set to a low level. To obtain a signal on the PWM0 pin, the contents of the DCR0 register must be greater than the contents of the ATR register.

The polarity bit can be used to invert the output signal.

The maximum available resolution for the PWM0 duty cycle is:

Resolution =

$$1 / (4096 - ATR)$$

**Note**: To get the maximum resolution (1/4096), the ATR register must be 0. With this maximum resolution and assuming that DCR=ATR, a 0% or 100% duty cycle can be obtained by changing the polarity.

**Caution:** As soon as the DCR0H is written, the compare function is disabled and will start only when the DCR0L value is written. If the DCR0H write occurs just before the compare event, the signal on the PWM output may not be set to a low level. In this case, the DCRx register should be updated just after an OVF event. If the DCR and ATR values are close, then the DCRx register shouldbe updated just before an OVF event, in order not to miss a compare event and to have the right signal applied on the PWM output.

47/

#### Figure 35. PWM Function

# 12-BIT AUTORELOAD TIMER (Cont'd)

## Figure 36. PWM Signal Example

## **Output Compare Mode**

To use this function, the OE bit must be 0, otherwise the compare is done with the shadow register instead of the DCRx register. Software must then write a 12-bit value in the DCR0H and DCR0L registers. This value will be loaded immediately (without waiting for an OVF event).

The DCR0H must be written first, the output compare function starts only when the DCR0L value is written.

When the 12-bit upcounter (CNTR) reaches the value stored in the DCR0H and DCR0L registers, the CMPF0 bit in the PWM0CSR register is set and an interrupt request is generated if the CMPIE bit is set.

**Note:** The output compare function is only available for DCRx values other than 0 (reset value).

**Caution:** At each OVF event, the DCRx value is written in a shadow register, even if the DCR0L value has not yet been written (in this case, the shadow register will contain the new DCR0H value and the old DCR0L value), then:

- If OE=1 (PWM mode): the compare is done between the timer counter and the shadow register (and not DCRx)

- if OE=0 (OCMP mode): the compare is done between the timer counter and DCRx. There is no PWM signal.

57

The compare between DCRx or the shadow register and the timer counter is locked until DCR0L is written.

#### 11.2.4 Low Power Modes

| Mode        | Description                                           |

|-------------|-------------------------------------------------------|

| SLOW        | The input frequency is divided by 32                  |

| WAIT        | No effect on AT timer                                 |

| ACTIVE-HALT | AT timer halted except if CK0=1,<br>CK1=0 and OVFIE=1 |

| HALT        | AT timer halted                                       |

#### 11.2.5 Interrupts

| Interrupt<br>Event <sup>1)</sup> | Event<br>Flag | Enable<br>Control<br>Bit |     | from | Exit<br>from<br>Active-<br>Halt |

|----------------------------------|---------------|--------------------------|-----|------|---------------------------------|

| Overflow<br>Event                | OVF           | OVFIE                    | Yes | No   | Yes <sup>2)</sup>               |

| CMP Event                        | CMPFx         | CMPIE                    | Yes | No   | No                              |

#### Notes:

**1.** The interrupt events are connected to separate interrupt vectors (see Interrupts chapter).

They generate an interrupt if the enable bit is set in the ATCSR register and the interrupt mask in the CC register is reset (RIM instruction).

2. only if CK0=1and CK1=0

# SERIAL PERIPHERAL INTERFACE (Cont'd) 11.3.8 Register Description CONTROL REGISTER (SPICR)

#### Read/Write

Reset Value: 0000 xxxx (0xh)

| 7    |     |      |      |      |      |      | 0    |

|------|-----|------|------|------|------|------|------|

| SPIE | SPE | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

# Bit 7 = **SPIE** Serial Peripheral Interrupt Enable. This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SPI interrupt is generated whenever SPIF=1, MODF=1 or OVR=1 in the SPICSR register

#### Bit 6 = **SPE** Serial Peripheral Output Enable.

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS}=0$  (see Section 11.3.5.1 Master Mode Fault (MODF)). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.

0: I/O pins free for general purpose I/O 1: SPI I/O pin alternate functions enabled

#### Bit 5 = SPR2 Divider Enable.

This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 15 SPI Master mode SCK Frequency.

0: Divider by 2 enabled

1: Divider by 2 disabled

Note: This bit has no effect in slave mode.

#### Bit 4 = MSTR Master Mode.

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS}=0$  (see Section 11.3.5.1 Master Mode Fault (MODF)).

0: Slave mode

5/

1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.

#### Bit 3 = **CPOL** Clock Polarity.

This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.

0: SCK pin has a low level idle state

1: SCK pin has a high level idle state

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Bit 2 = CPHA Clock Phase.

This bit is set and cleared by software.

- 0: The first clock transition is the first data capture edge.

- 1: The second clock transition is the first capture edge.

**Note:** The slave must have the same CPOL and CPHA settings as the master.

#### Bits 1:0 = SPR[1:0] Serial Clock Frequency.

These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.

Note: These 2 bits have no effect in slave mode.

#### Table 15. SPI Master mode SCK Frequency

| Serial Clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    | 0    | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |

# **13 ELECTRICAL CHARACTERISTICS**

# **13.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $\ensuremath{\mathsf{V}_{SS}}\xspace.$

#### 13.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

### 13.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25\,^\circ\text{C}, V_{DD}=5V$  (for the  $4.5V{\le}V_{DD}{\le}5.5V$  voltage range),  $V_{DD}=3.3V$  (for the  $3V{\le}V_{DD}{\le}3.6V$  voltage range) and  $V_{DD}=2.7V$  (for the  $2.4V{\le}V_{DD}{\le}3V$  voltage range). They are given only as design guidelines and are not tested.

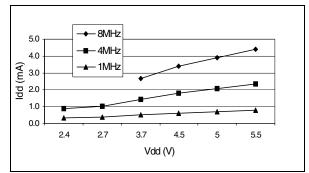

## 13.1.3 Typical curves

57

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 13.1.4 Loading capacitor

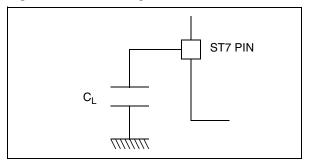

The loading conditions used for pin parameter measurement are shown in Figure 46.

## Figure 46. Pin loading conditions

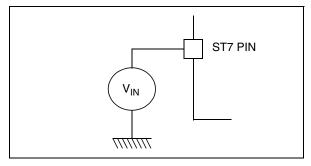

#### 13.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 47.

#### Figure 47. Pin input voltage

vice consumption, the two current values must be

added (except for HALT mode for which the clock

# **13.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total de-

### 13.4.1 Supply Current

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified

| Symbol          | Parameter                                                       |                  | Conditions                             | Тур  | Max  | Unit |

|-----------------|-----------------------------------------------------------------|------------------|----------------------------------------|------|------|------|

|                 | Supply current in RUN mode                                      |                  | f <sub>CPU</sub> =8MHz <sup>1)</sup>   | 4.50 | 7.00 |      |

|                 | Supply current in WAIT mode                                     |                  | f <sub>CPU</sub> =8MHz <sup>2)</sup>   | 1.75 | 2.70 | mA   |

|                 | Supply current in SLOW mode<br>Supply current in SLOW WAIT mode |                  | f <sub>CPU</sub> =250kHz <sup>3)</sup> | 0.75 | 1.13 | 3    |

| I <sub>DD</sub> |                                                                 |                  | f <sub>CPU</sub> =250kHz <sup>4)</sup> | 0.65 | 1    |      |

|                 | Supply current in HALT mode <sup>5)</sup>                       | V <sub>DD:</sub> | -40°C≤T <sub>A</sub> ≤+85°C            | 0.50 | 10   |      |

|                 |                                                                 |                  | -40°C≤T <sub>A</sub> ≤+105°C           | TBD  | TBD  | μA   |

|                 |                                                                 |                  | T <sub>A</sub> = +85°C                 | 5    | 100  |      |

is stopped).

#### Notes:

47/

1. CPU running with memory access, all I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

2. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

3. SLOW mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

**4.** SLOW-WAIT mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled. **5.** All I/O pins in output mode with a static value at  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max and  $f_{CPU}$  max.

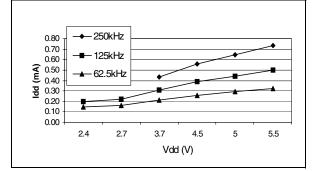

## Figure 56. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

# **13.6 MEMORY CHARACTERISTICS**

$T_A = -40^{\circ}C$  to 105°C, unless otherwise specified

## 13.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 13.6.2 FLASH Program Memory

| Symbol            | Parameter                                     | Conditions                                                                       | Min               | Тур  | Max               | Unit   |

|-------------------|-----------------------------------------------|----------------------------------------------------------------------------------|-------------------|------|-------------------|--------|

| V <sub>DD</sub>   | Operating voltage for Flash write/erase       |                                                                                  | 2.4               |      | 5.5               | V      |

| +                 | Programming time for 1~32 bytes <sup>2)</sup> | T <sub>A</sub> =-40 to +105°C                                                    |                   | 5    | 10                | ms     |

| t <sub>prog</sub> | Programming time for 1.5 kBytes               | T <sub>A</sub> =+25°C                                                            |                   | 0.24 | 0.48              | s      |

| t <sub>RET</sub>  | Data retention 4)                             | T <sub>A</sub> =+55°C <sup>3)</sup>                                              | 20                |      |                   | years  |

| N <sub>RW</sub>   | Write erase cycles                            | T <sub>A</sub> =+25°C                                                            | 10K <sup>7)</sup> |      |                   | cycles |

| I <sub>DD</sub>   | Supply current                                | Read / Write / Erase<br>modes<br>f <sub>CPU</sub> = 8MHz, V <sub>DD</sub> = 5.5V |                   |      | 2.6 <sup>6)</sup> | mA     |

|                   |                                               | No Read/No Write Mode                                                            |                   |      | 100               | μΑ     |

|                   |                                               | Power down mode / HALT                                                           |                   | 0    | 0.1               | μΑ     |

#### 13.6.3 EEPROM Data Memory

| Symbol            | Parameter                                | Conditions                          | Min                | Тур | Max | Unit   |

|-------------------|------------------------------------------|-------------------------------------|--------------------|-----|-----|--------|

| V <sub>DD</sub>   | Operating voltage for EEPROM write/erase |                                     | 2.4                |     | 5.5 | V      |

| t <sub>prog</sub> | Programming time for 1~32 bytes          | T <sub>A</sub> =-40 to +105°C       |                    | 5   | 10  | ms     |

| t <sub>ret</sub>  | Data retention <sup>4)</sup>             | T <sub>A</sub> =+55°C <sup>3)</sup> | 20                 |     |     | years  |

| N <sub>RW</sub>   | Write erase cycles                       | T <sub>A</sub> =+25°C               | 300K <sup>7)</sup> |     |     | cycles |

#### Notes:

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Guaranteed by construction, not tested in production.

2. Up to 32 bytes can be programmed at a time.

3. The data retention time increases when the  $\mathsf{T}_\mathsf{A}$  decreases.

4. Data based on reliability test results and monitored in production.

5. Data based on characterization results, not tested in production.

6. Guaranteed by Design. Not tested in production.

7. Design target value pending full product characterization.

# **13.8 I/O PORT PIN CHARACTERISTICS**

### **13.8.1 General Characteristics**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                | Parameter                                                                   |                                             | Conditions          |                                 | Тур | Max                             | Unit             |  |

|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------|---------------------|---------------------------------|-----|---------------------------------|------------------|--|

| VIL                   | Input low level voltage                                                     |                                             |                     |                                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V                |  |

| V <sub>IH</sub>       | Input high level voltage                                                    |                                             |                     | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     | V <sub>DD</sub> + 0.3           |                  |  |

| V <sub>hys</sub>      | Schmitt trigger voltage<br>hysteresis                                       |                                             |                     |                                 | 400 |                                 | mV               |  |

| ١L                    | Input leakage current                                                       | $V_{SS} \leq V_{IN} \leq V_{DD}$            |                     |                                 |     | ±1                              |                  |  |

| ۱ <sub>S</sub>        | Static current consumption induced by each floating input pin <sup>2)</sup> | Floatin                                     | Floating input mode |                                 | 400 |                                 | μΑ               |  |

| Р                     | Weak pull-up equivalent resistor <sup>3)</sup>                              | V <sub>IN</sub> =V                          | V <sub>DD</sub> =5V | 50                              | 120 | 250                             | kΩ               |  |

| R <sub>PU</sub>       | weak puil-up equivalent resistor?                                           | SS                                          | V <sub>DD</sub> =3V |                                 | 160 |                                 | KS 2             |  |

| CIO                   | I/O pin capacitance                                                         |                                             |                     |                                 | 5   |                                 | pF               |  |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>1)</sup>                            | C <sub>L</sub> =50pF<br>Between 10% and 90% |                     |                                 | 25  |                                 | ns               |  |

| t <sub>r(IO)out</sub> | Output low to high level rise time <sup>1)</sup>                            |                                             |                     |                                 | 25  |                                 |                  |  |

| t <sub>w(IT)in</sub>  | External interrupt pulse time 4)                                            |                                             |                     | 1                               |     |                                 | t <sub>CPU</sub> |  |

Notes:

1. Data based on characterization results, not tested in production.

2. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see Figure 66). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

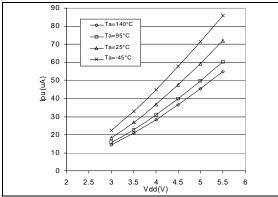

**3.** The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 63).

4. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

#### Figure 62. Two typical applications with unused I/O pin configured as input

(external pull-up of 10k mandatory in noisy environment). This is to avoid entering ICC mode unexpectedly during a reset. **Note:** I/O can be left unconnected if it is configured as output (0 or 1) by the software. This has the advantage of greater EMC robustness and lower cost.

## Figure 63. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

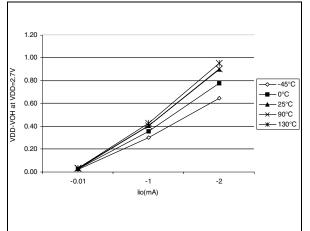

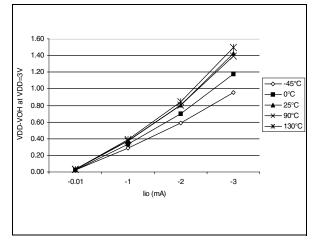

# Figure 69. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=2.7V

# Figure 70. Typical $V_{DD}$ - $V_{OH}$ at $V_{DD}$ =3V

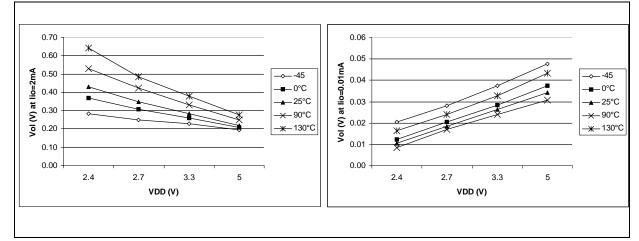

Figure 73. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard I/Os)

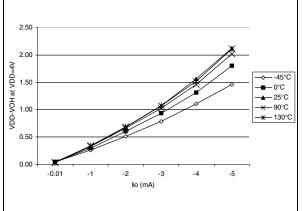

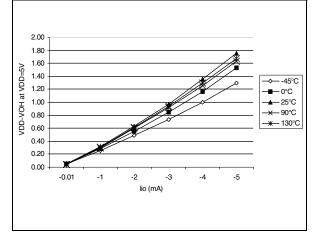

Figure 72. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=5V

57

| ST7LITE0xY0 AN                                                                                                                |                                                                                           | STROM MICR<br>e: November 2 | OCONTROLLER OPT<br>2007)                  | ION LIST                              |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|---------------------------------------|

| Customer<br>Address<br>Contact<br>Phone No<br>Reference/FASTROM Code*<br>*FASTROM code name is as<br>FASTROM code must be ser | signed by STMicroele                                                                      | ctronics.                   |                                           | · · · · · · · · · · · · · · · · · · · |

| Memory size (check only on                                                                                                    | e option): []1 K                                                                          |                             | []1.5 K                                   |                                       |

| Device type (check only one                                                                                                   |                                                                                           | LITES2Y0<br>LITE02Y0        | [] ST7PLITES5Y0<br>[] ST7PLITE05Y0        | [] ST7PLITE09Y0                       |

| Warning: Addresses 1000h<br>RCCR1 (see section 7.1 on                                                                         | , 1001h, FFDEh and I<br>page 24).                                                         | FDFh are re                 | served areas for ST to                    | program RCCR0 and                     |

| SO16 []                                                                                                                       | Tube<br> Tape & Reel<br> Tape & Reel<br>No<br>tters, digits, '.', '-', '/' an<br>PDIP16 ( | 15 char. max)               | ау                                        |                                       |

| Sector 0 size:                                                                                                                | []0.5K                                                                                    | [] 1K                       | <br>[ ] 1.5K                              |                                       |

| Readout Protection:<br>FLASH write Protection:                                                                                | [] Disabled<br>[] Disabled                                                                | [] Enable<br>[] Enable      | d                                         |                                       |

| Clock Source Selection:                                                                                                       | [] Internal RC                                                                            | [] Externa                  | al Clock                                  |                                       |

| PLL                                                                                                                           | [] Disabled                                                                               | [] PLLx4                    | [] PLLx8                                  |                                       |

| LVD Reset                                                                                                                     | [] Disabled                                                                               | [] Mediun                   | t threshold<br>n threshold<br>: threshold |                                       |

| Watchdog Selection:<br>Watchdog Reset on Halt:                                                                                | [ ] Software Activa<br>[ ] Disabled                                                       | tion                        | [] Hardware A<br>[] Enabled               | Activation                            |

| Supply Operating Range in the                                                                                                 | ne application:                                                                           |                             |                                           |                                       |

| Date:                                                                                                                         |                                                                                           |                             |                                           |                                       |

| Important note: Not all cont                                                                                                  |                                                                                           | le. See Table               |                                           |                                       |

| Please download the latest v<br>www.st.com                                                                                    | ersion of this option lis                                                                 | st from:                    |                                           |                                       |

57

# Table 24. ST7 Application Notes

| IDENTIFICATION        | DESCRIPTION                                                                 |

|-----------------------|-----------------------------------------------------------------------------|

| AN1947                | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                         |

| GENERAL PURPOSE       |                                                                             |

| AN1476                | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                   |

| AN1526                | ST7FLITE0 QUICK REFERENCE NOTE                                              |

| AN1709                | EMC DESIGN FOR ST MICROCONTROLLERS                                          |

| AN1752                | ST72324 QUICK REFERENCE NOTE                                                |

| PRODUCT EVALUATION    |                                                                             |

| AN 910                | PERFORMANCE BENCHMARKING                                                    |

| AN 990                | ST7 BENEFITS VS INDUSTRY STANDARD                                           |

| AN1077                | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                   |

| AN1086                | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                  |

| AN1103                | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141            |

| AN1150                | BENCHMARK ST72 VS PC16                                                      |

| AN1151                | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                           |

| AN1278                | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                  |

| PRODUCT MIGRATION     |                                                                             |

| AN1131                | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324          |

| AN1322                | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                       |

| AN1365                | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                  |

| AN1604                | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                      |

| AN2200                | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB              |

| PRODUCT OPTIMIZATION  |                                                                             |

| AN 982                | USING ST7 WITH CERAMIC RESONATOR                                            |

| AN1014                | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                   |

| AN1015                | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE           |

| AN1040                | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                     |

| AN1070                | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                       |

| AN1181                | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                               |

| AN1324                | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS          |

| AN1502                | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                |

| AN1529                | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY        |

| AN1530                | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLATOR |

| AN1605                | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE            |

| AN1636                | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                          |

| AN1828                | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE           |

| AN1946                | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC          |

| AN1953                | PFC FOR ST7MC STARTER KIT                                                   |

| AN1971                | ST7LITE0 MICROCONTROLLED BALLAST                                            |

| PROGRAMMING AND TOOLS |                                                                             |

| AN 978                | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                          |

| AN 983                | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                           |

| AN 985                | EXECUTING CODE IN ST7 RAM                                                   |

| AN 986                | USING THE INDIRECT ADDRESSING MODE WITH ST7                                 |

| AN 987                | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                      |

| AN 988                | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                       |

| AN1039                | ST7 MATH UTILITY ROUTINES                                                   |