Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | A/D 5x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 16-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite05y0m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

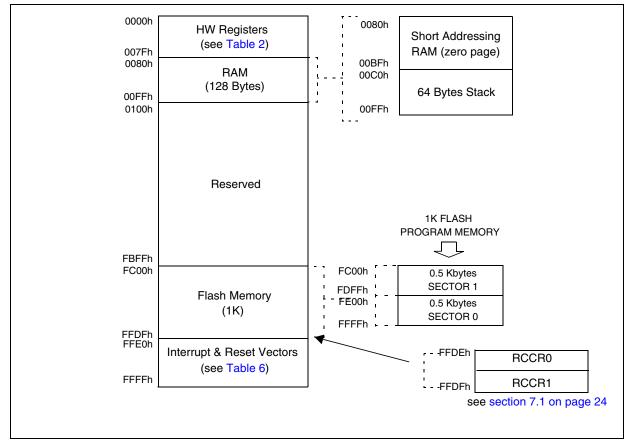

# REGISTER AND MEMORY MAP (Cont'd)

#### Figure 5. Memory Map (ST7SUPERLITE)

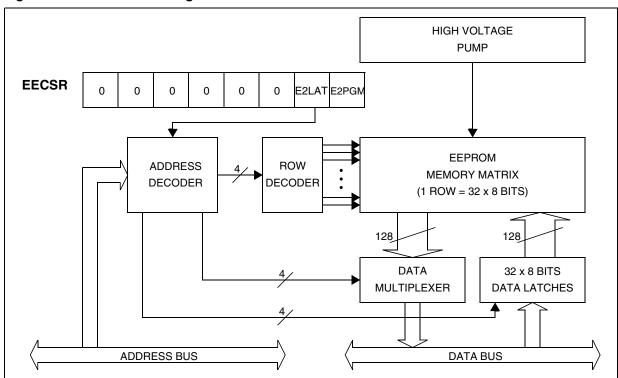

# **5 DATA EEPROM**

# **5.1 INTRODUCTION**

The Electrically Erasable Programmable Read Only Memory can be used as a non-volatile backup for storing data. Using the EEPROM requires a basic access protocol described in this chapter.

#### **5.2 MAIN FEATURES**

- Up to 32 bytes programmed in the same cycle

- EEPROM mono-voltage (charge pump)

- Chained erase and programming cycles

- Internal control of the global programming cycle duration

Δ7/

- WAIT mode management

- Read-out protection

# Figure 7. EEPROM Block Diagram

# DATA EEPROM (Cont'd)

#### **5.4 POWER SAVING MODES**

#### Wait mode

The DATA EEPROM can enter WAIT mode on execution of the WFI instruction of the microcontroller or when the microcontroller enters Active Halt mode. The DATA EEPROM will immediately enter this mode if there is no programming in progress, otherwise the DATA EEPROM will finish the cycle and then enter WAIT mode.

#### Active Halt mode

Refer to Wait mode.

#### Halt mode

5/

The DATA EEPROM immediately enters HALT mode if the microcontroller executes the HALT instruction. Therefore the EEPROM will stop the function in progress, and data may be corrupted.

### 5.5 ACCESS ERROR HANDLING

If a read access occurs while E2LAT = 1, then the data bus will not be driven.

If a write access occurs while E2LAT = 0, then the data on the bus will not be latched.

If a programming cycle is interrupted (by RESET action), the integrity of the data in memory will not be guaranteed.

#### 5.6 DATA EEPROM READ-OUT PROTECTION

The read-out protection is enabled through an option bit (see option byte section).

When this option is selected, the programs and data stored in the EEPROM memory are protected against read-out (including a re-write protection). In Flash devices, when this protection is removed by reprogramming the Option Byte, the entire Program memory and EEPROM is first automatically erased.

**Note:** Both Program Memory and data EEPROM are protected using the same option bit.

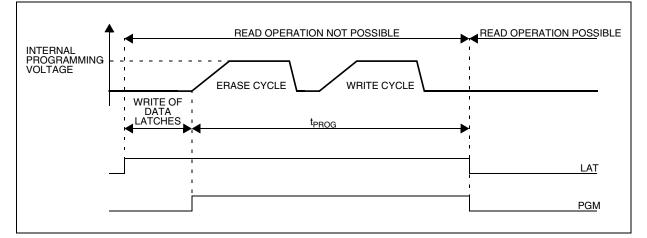

# Figure 10. Data EEPROM Programming Cycle

# DATA EEPROM (Cont'd)

# **5.7 REGISTER DESCRIPTION**

# EEPROM CONTROL/STATUS REGISTER (EEC-

SR) Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |       | 0     |

|---|---|---|---|---|---|-------|-------|

| 0 | 0 | 0 | 0 | 0 | 0 | E2LAT | E2PGM |

Bits 7:2 = Reserved, forced by hardware to 0.

### Bit 1 = E2LAT Latch Access Transfer

This bit is set by software. It is cleared by hardware at the end of the programming cycle. It can only be cleared by software if the E2PGM bit is cleared.

0: Read mode

1: Write mode

# Bit 0 = **E2PGM** *Programming control and status*

This bit is set by software to begin the programming cycle. At the end of the programming cycle, this bit is cleared by hardware.

0: Programming finished or not yet started

1: Programming cycle is in progress

**Note**: If the E2PGM bit is cleared during the programming cycle, the memory data is not guaranteed.

### Table 4. DATA EEPROM Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label    | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|-------------------|----------------------|---|---|---|---|---|---|------------|------------|

| 0030h             | EECSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | E2LAT<br>0 | E2PGM<br>0 |

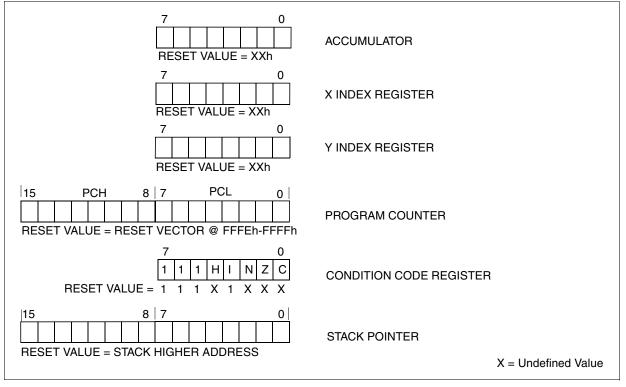

# **6 CENTRAL PROCESSING UNIT**

# 6.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

### **6.2 MAIN FEATURES**

- 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes

- Two 8-bit index registers

- 16-bit stack pointer

- Low power modes

- Maskable hardware interrupts

- Non-maskable software interrupt

#### 6.3 CPU REGISTERS

The six CPU registers shown in Figure 11 are not present in the memory mapping and are accessed by specific instructions.

#### Figure 11. CPU Registers

5/

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index Registers (X and Y)

In indexed addressing modes, these 8-bit registers are used to create either effective addresses or temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures (not pushed to and popped from the stack).

#### **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

# CPU REGISTERS (Cont'd) CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | н | Ι | Ν | Z | С |

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 3 = I Interrupt mask.

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except the TRAP software interrupt. This bit is cleared by software.

- 0: Interrupts are enabled.

- 1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

**Note:** Interrupts requested while I is set are latched and can be processed when I is cleared. By default an interrupt routine is not interruptible

because the I bit is set by hardware at the start of the routine and reset by the IRET instruction at the end of the routine. If the I bit is cleared by software in the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrupt routine.

#### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the 7<sup>th</sup> bit of the result.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative (that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = Z Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation. 0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

<u>ل</u>حک

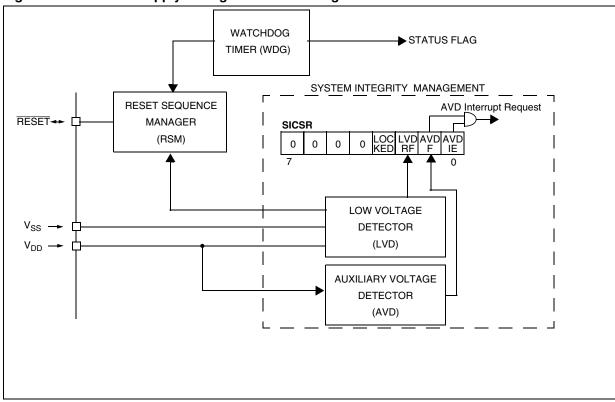

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

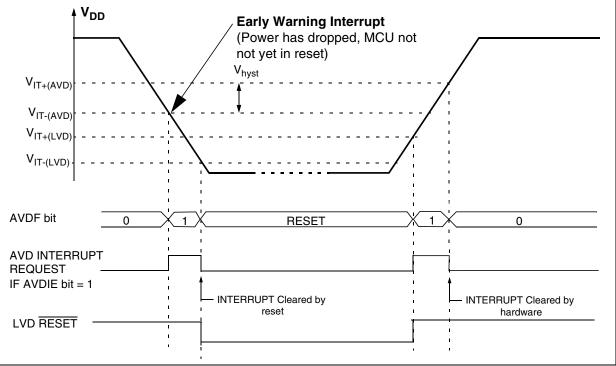

#### 8.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a  $V_{IT-(AVD)}$  and  $V_{IT+(AVD)}$  reference value and the  $V_{DD}$  main supply voltage ( $V_{AVD}$ ). The  $V_{IT-(AVD)}$  reference value for falling voltage is lower than the  $V_{IT+(AVD)}$  reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD functions only if the LVD is enabled through the option byte.

### 8.4.2.1 Monitoring the $V_{\mbox{\scriptsize DD}}$ Main Supply

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see section 15.1 on page 112).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{\text{IT+(LVD)}}$  or  $V_{\text{IT-(AVD)}}$  threshold (AVDF bit is set).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 21.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 8.4.3 Low Power Modes

| Mode | Description                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SI. AVD interrupts cause the device to exit from Wait mode.                                                  |

| HALT | The SICSR register is frozen.<br>The AVD remains active but the AVD inter-<br>rupt cannot be used to exit from Halt mode. |

#### 8.4.3.1 Interrupts

<u>ل</u>حک

The AVD interrupt event generates an interrupt if the corresponding Enable Control Bit (AVDIE) is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------|---------------|--------------------------|----------------------|----------------------|

| AVD event       | AVDF          | AVDIE                    | Yes                  | No                   |

# LITE TIMER (Cont'd)

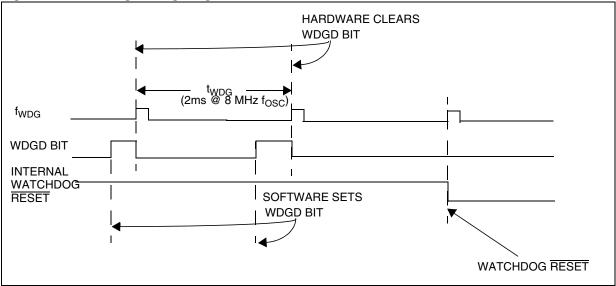

# Figure 32. Watchdog Timing Diagram

# SERIAL PERIPHERAL INTERFACE (Cont'd)

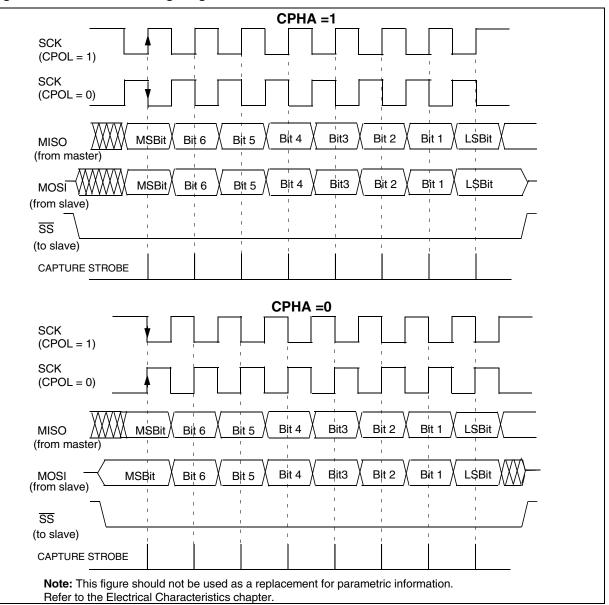

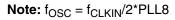

#### 11.3.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 41).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

Figure 41, shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin, the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

## Figure 41. Data Clock Timing Diagram

<u>/</u>۲/

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.3.5 Error Flags

#### 11.3.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device has its SS pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

#### 11.3.5.2 Overrun Condition (OVR)

An overrun condition occurs, when the master device has sent a data byte and the slave device has

not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 11.3.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 11.3.3.2 Slave Select Management.

**Note:** a "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

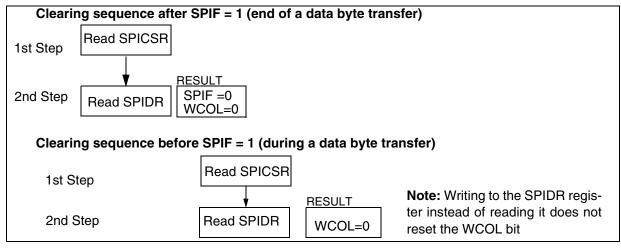

Clearing the WCOL bit is done through a software sequence (see Figure 42).

#### Figure 42. Clearing the WCOL bit (Write Collision Flag) Software Sequence

# SERIAL PERIPHERAL INTERFACE (Cont'd)

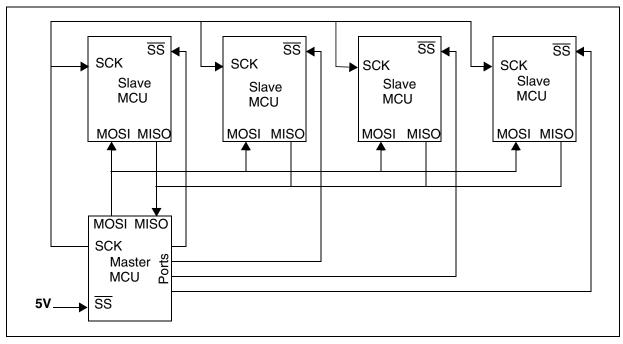

#### 11.3.5.4 Single Master Systems

47/

A typical single master system may be configured, using an MCU as the master and four MCUs as slaves (see Figure 43).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

# 8-BIT A/D CONVERTER (ADC) (Cont'd)

#### 11.4.6 Register Description

#### **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |   |     |     | 0   |

|-----|-------|------|---|---|-----|-----|-----|

| EOC | SPEED | ADON | 0 | 0 | CH2 | CH1 | CH0 |

### Bit 7 = **EOC** Conversion Complete

This bit is set by hardware. It is cleared by software reading the result in the DR register or writing to the CSR register.

0: Conversion is not complete

1: Conversion can be read from the DR register

#### Bit 6 = SPEED ADC clock selection

This bit is set and cleared by software. It is used together with the SLOW bit to configure the ADC clock speed. Refer to the table in the SLOW bit description.

Bit 5 = **ADON** *A/D Converter and Amplifier On* This bit is set and cleared by software.

0: A/D converter and amplifier are switched off 1: A/D converter and amplifier are switched on

**Note**: Amplifier not available on ST7LITES5 devices

Bits 4:3 = **Reserved.** *must always be cleared.*

#### Bits 2:0 = CH[2:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin <sup>1</sup> | CH2 | CH1 | CH0 |

|--------------------------|-----|-----|-----|

| AINO                     | 0   | 0   | 0   |

| AIN1                     | 0   | 0   | 1   |

| AIN2                     | 0   | 1   | 0   |

| AIN3                     | 0   | 1   | 1   |

| AIN4                     | 1   | 0   | 0   |

#### Notes:

1. The number of pins AND the channel selection varies according to the device. Refer to the device pinout.

2. A write to the ADCCSR register (with ADON set) aborts the current conversion, resets the EOC bit and starts a new conversion.

## DATA REGISTER (ADCDR)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

#### Bits 7:0 = D[7:0] Analog Converted Value

This register contains the converted analog value in the range 00h to FFh.

Note: Reading this register reset the EOC flag.

#### AMPLIFIER CONTROL REGISTER (ADCAMP)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |      |             |   | 0 |  |

|---|---|---|---|------|-------------|---|---|--|

| 0 | 0 | 0 | 0 | SLOW | AMP-<br>SEL | 0 | 0 |  |

Bit 7:4 = Reserved. Forced by hardware to 0.

#### Bit 3 = SLOW Slow mode

This bit is set and cleared by software. It is used together with the SPEED bit to configure the ADC clock speed as shown on the table below.

| f <sub>ADC</sub>    | SLOW | SPEED |

|---------------------|------|-------|

| f <sub>CPU</sub> /2 | 0    | 0     |

| f <sub>CPU</sub>    | 0    | 1     |

| f <sub>CPU</sub> /4 | 1    | х     |

Bit 2 = **AMPSEL** Amplifier Selection Bit

This bit is set and cleared by software. For ST7LITES5 devices, this bit must be kept at its reset value (0).

0: Amplifier is not selected

1: Amplifier is selected

**Note:** When AMPSEL=1 it is mandatory that  $f_{ADC}$  be less than or equal to 2 MHz.

Bits 1:0 = Reserved. Forced by hardware to 0.

**Note**: If ADC settings are changed by writing the ADCAMP register while the ADC is running, a dummy conversion is needed before obtaining results with the new settings.

57

# 13.3.2 Operating Conditions with Low Voltage Detector (LVD)

$T_A$  = -40 to 85°C, unless otherwise specified

| Symbol                | Parameter                                         | Conditions                                        | Min                                                            | Тур                  | Max                                                            | Unit |

|-----------------------|---------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------------------------------------------------|------|

| V <sub>IT+(LVD)</sub> | Reset release threshold<br>(V <sub>DD</sub> rise) | High Threshold<br>Med. Threshold<br>Low Threshold | 4.00 <sup>1)</sup><br>3.40 <sup>1)</sup><br>2.65 <sup>1)</sup> | 4.25<br>3.60<br>2.90 | 4.50<br>3.80<br>3.15                                           | V    |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall) | High Threshold<br>Med. Threshold<br>Low Threshold | 3.80<br>3.20<br>2.40                                           | 4.05<br>3.40<br>2.70 | 4.30 <sup>1)</sup><br>3.65 <sup>1)</sup><br>2.90 <sup>1)</sup> | v    |

| V <sub>hys</sub>      | LVD voltage threshold hysteresis                  | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>      |                                                                | 200                  |                                                                | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                                   | 20                                                             |                      | 20000                                                          | μs/V |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on V <sub>DD</sub>          | Not detected by the LVD                           |                                                                |                      | 150                                                            | ns   |

| I <sub>DD(LVD</sub> ) | LVD/AVD current consumption                       |                                                   |                                                                | 220                  |                                                                | μA   |

Notes:

**1.** Not tested in production.

**2.** Not tested in production. The  $V_{DD}$  rise time rate condition is needed to ensure a correct device power-on and LVD reset. When the  $V_{DD}$  slope is outside these values, the LVD may not ensure a proper reset of the MCU.

# 13.3.3 Auxiliary Voltage Detector (AVD) Thresholds

$T_A = -40$  to 85°C, unless otherwise specified

| Symbol                  | Parameter                                                  | Conditions                                   | Min  | Тур  | Max  | Unit |

|-------------------------|------------------------------------------------------------|----------------------------------------------|------|------|------|------|

|                         | 1=>0 AVDF flag toggle threshold<br>(V <sub>DD</sub> rise)  | High Threshold                               | 4.40 | 4.70 | 5.00 |      |

| V <sub>IT+(AVD)</sub>   |                                                            | Med. Threshold                               | 3.90 | 4.10 | 4.30 |      |

|                         |                                                            | Low Threshold                                | 3.20 | 3.40 | 3.60 | v    |

|                         | 0=>1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall)  | High Threshold                               | 4.30 | 4.60 | 4.90 | v    |

| V <sub>IT-(AVD)</sub>   |                                                            | Med. Threshold                               | 3.70 | 3.90 | 4.10 |      |

|                         |                                                            | Low Threshold                                | 2.90 | 3.20 | 3.40 |      |

| V <sub>hys</sub>        | AVD voltage threshold hysteresis                           | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |      | 150  |      | mV   |

| $\Delta V_{\text{IT-}}$ | Voltage drop between AVD flag set and LVD reset activation | V <sub>DD</sub> fall                         |      | 0.45 |      | V    |

47/

# **OPERATING CONDITIONS** (Cont'd)

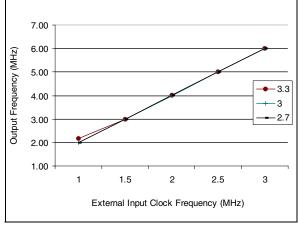

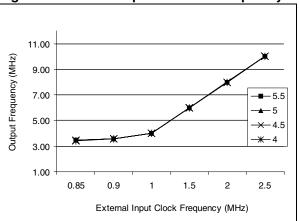

Note: f<sub>OSC</sub> = f<sub>CLKIN</sub>/2\*PLL4

Figure 55. PLLx8 Output vs CLKIN frequency

## **13.7 EMC (ELECTROMAGNETIC COMPATIBILITY) CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 13.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling two -+LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 13.7.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Level/<br>Class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD}$ =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2        | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | 3В              |

#### 13.7.2 EMI (Electromagnetic interference)

Based on a simple application running on the product (toggling two LEDs through the I/O ports), the product is monitored in terms of emission. This

emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

#### Table 20: EMI emissions

| Symbol           | Parameter  | Conditions                                  | Monitored       | Max vs. [f <sub>OSC</sub> /f <sub>CPU</sub> ] |        | Unit      |

|------------------|------------|---------------------------------------------|-----------------|-----------------------------------------------|--------|-----------|

|                  |            | Fre                                         | Frequency Band  | 1/4MHz                                        | 1/8MHz |           |

| S <sub>EMI</sub> | Peak level | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, | 0.1MHz to 30MHz | 8                                             | 14     |           |

|                  |            | SO16 package,                               | 30MHz to 130MHz | 27                                            | 32     | $dB\mu V$ |

|                  |            | conforming to SAE J 1752/3                  | 130MHz to 1GHz  | 26                                            | 28     |           |

|                  |            |                                             | SAE EMI Level   | 3.5                                           | 4      | -         |

Note:

1. Data based on characterization results, not tested in production.

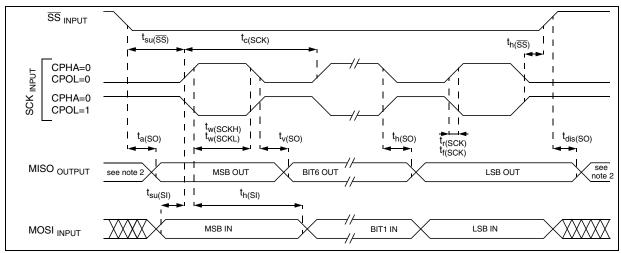

# **13.10 COMMUNICATION INTERFACE CHARACTERISTICS**

#### 13.10.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                                                                          | Parameter                    | Conditions                       | Min                               | Мах                        | Unit   |

|-------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|-----------------------------------|----------------------------|--------|

| f <sub>SCK =</sub>                                                                              | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128 =<br>0.0625 | f <sub>CPU</sub> /4 =<br>2 | MHz    |

| 1/t <sub>c(SCK)</sub>                                                                           | SFT Clock nequency           | Slave<br>f <sub>CPU</sub> =8MHz  | 0                                 | f <sub>CPU</sub> /2 =<br>4 | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                                      | SPI clock rise and fall time |                                  | see I/O port pin descriptio       |                            | otion  |

| t <sub>su(SS)</sub> 1)                                                                          | SS setup time <sup>4)</sup>  | Slave                            | T <sub>CPU</sub> + 50             |                            |        |

| t <sub>h(SS)</sub> <sup>1)</sup>                                                                | SS hold time                 | Slave                            | 120                               |                            |        |

| $ \begin{array}{c} t_{w(SCKH)} & 1) \\ t_{w(SCKL)} & 1) \\ \hline t_{out(MI)} & 1 \end{array} $ | SCK high and low time        | Master<br>Slave                  | 100<br>90                         |                            |        |

| $\begin{array}{c} t_{su(MI)} \\ t_{su(SI)} \\ t_{su(SI)} \end{array} $                          | Data input setup time        | Master<br>Slave                  | 100<br>100                        |                            |        |

| t <sub>h(MI)</sub> 1)<br>t <sub>h(SI)</sub> 1)                                                  | Data input hold time         | Master<br>Slave                  | 100<br>100                        |                            | ns     |

| t <sub>a(SO)</sub> <sup>1)</sup>                                                                | Data output access time      | Slave                            | 0                                 | 120                        |        |

| t <sub>dis(SO)</sub> <sup>1)</sup>                                                              | Data output disable time     | Slave                            |                                   | 240                        |        |

| t <sub>v(SO)</sub> <sup>1)</sup>                                                                | Data output valid time       | Slove (offer enable edge)        |                                   | 120                        |        |

| t <sub>h(SO)</sub> <sup>1)</sup>                                                                | Data output hold time        | - Slave (after enable edge)      | 0                                 |                            |        |

| t <sub>v(MO)</sub> <sup>1)</sup>                                                                | Data output valid time       | Master (offer enable edge)       |                                   | 120                        |        |

| t <sub>h(MO)</sub> <sup>1)</sup>                                                                | Data output hold time        | Master (after enable edge)       | 0                                 |                            |        |

### Figure 78. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

- 1. Data based on design simulation and/or characterisation results, not tested in production.

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

- 3. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

- **4.** Depends on  $f_{CPU}$ . For example, if  $f_{CPU}$ =8MHz, then  $T_{CPU}$  = 1/ $f_{CPU}$  =125ns and  $t_{su}(\overline{SS})$ =175ns

# Table 24. ST7 Application Notes

| IDENTIFICATION      | DESCRIPTION                                                                          |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|

| AN1071              | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER               |  |  |

| AN1106              | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |  |  |

| AN1179              | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |  |  |

| AN1446              | USING THE ST72521 EMULATOR TO DEBUG AN ST72324 TARGET APPLICATION                    |  |  |

| AN1477              | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |  |  |

| AN1527              | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |  |  |

| AN1575              | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |  |  |

| AN1576              | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS              |  |  |

| AN1577              | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS                |  |  |

| AN1601              | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1603              | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)                   |  |  |

| AN1635              | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                            |  |  |

| AN1754              | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                            |  |  |

| AN1796              | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT                  |  |  |

| AN1900              | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1904              | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                        |  |  |

| AN1905              | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                                |  |  |

| SYSTEM OPTIMIZATION |                                                                                      |  |  |

| AN1711              | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                                  |  |  |

| AN1827              | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                                 |  |  |

| AN2009              | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                        |  |  |

| AN2030              | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                       |  |  |

# **17 REVISION HISTORY**

# Table 25. Revision History

| Date       | Revision | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27-Oct-04  | 3        | Revision number incremented from 2.5 to 3.0 due to Internal Document Management System change<br>Changed all references of ADCDAT to ADCDR<br>Added EMU3 Emulator Programming Capability in Table 23<br>Clarification of read-out protection<br>Altered note 1 for section 13.2.3 on page 82 removing references to RESET<br>Alteration of $f_{CPU}$ for SLOW and SLOW-WAIT modes in Section 13.4.1 table and Figure 59<br>on page 90<br>Removed sentence relating to an effective change only after overflow for CK[1:0], page 56<br>Added illegal opcode detection to page 1, section 8.4 on page 32, section 12 on page 75<br>Clarification of Flash read-out protection, section 4.5.1 on page 15<br>$f_{PLL}$ value of 1MHz quoted as Typical instead of a Minimum in section 14.3.5.2 on page 92<br>Updated $F_{SCK}$ in section 13.10.1 on page 102 to $F_{CPU}/4$ and $F_{CPU}/2$<br>section 8.4.4 on page 36: Changed wording in AVDIE and AVDF bit descriptions to "when<br>the AVDF bit is set"<br>Socket Board development kit details added in Table 24 on page 115<br>PWM Signal diagram corrected, Figure 36 on page 55<br>Corrected count of reserved bits between 003Bh to 007Fh, Table 2 on page 11<br>Inserted note that RCCR0 and RCCR1 are erased if read-only flag is reset, section 7.1 on<br>page 24                                                                                                                                                                                                                                                                                                                                                                                    |

| 21-July-06 | 4        | Added QFN20 package<br>Modified section 2 on page 6<br>Changed Read operation paragraph in section 5.3 on page 17<br>Modified note below Figure 9 on page 18 and modified section 5.5 on page 19<br>Modified note to section 7.1 on page 24<br>Added note on illegal opcode reset to section 7.4.1 on page 27<br>Added note 2 to EICR description on page 31<br>Modified External Interrupt Function in section 10.2.1 on page 42<br>Changed text on input capture before section 11.1.4 on page 51<br>Modified text in section 11.1.5 on page 51<br>Added important note in section 11.3.3 on page 62<br>Changed note 1 in section 13.2.2 on page 82<br>Modified values in section 13.2.4.1 on page 55 and section 13.3.4.2 on page 86<br>Added note on clock stability and frequency accuracy to section 13.3.4.1 on page 85, section<br>13.3.4.2 on page 86, section 7.1 on page 24 and to OSC option bit in Section 15.1 on page<br>113<br>Changed I <sub>S</sub> value and note 2 in section 13.8.1 on page 95<br>Added note in Figure 62 on page 95<br>Changed Figure 76 on page 101 and removed EMC protection circuitry in Figure 77 on page<br>101 (device works correctly without these components)<br>Changed section 13.10.1 on page 102 (t <sub>su(SS)</sub> , t <sub>v(MO)</sub> and t <sub>h(MO)</sub> )<br>Modified Figure 79 (CPHA=1) and Figure 80 on page 103 (t <sub>v(MO)</sub> , t <sub>h(MO)</sub> )<br>Added ECOPACK information to section 14 on page 109<br>Modified Figure 88 on page 110 (A1 and A swapped in the diagram)<br>Modified Figure 88 on page 110<br>Modified Section 15.2 on page 117<br>Removed erratasheet section<br>Added Section 16.4 and section 16.5 on page 121 |