Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | A/D 5x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 16-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite09m6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3 REGISTER & MEMORY MAP**

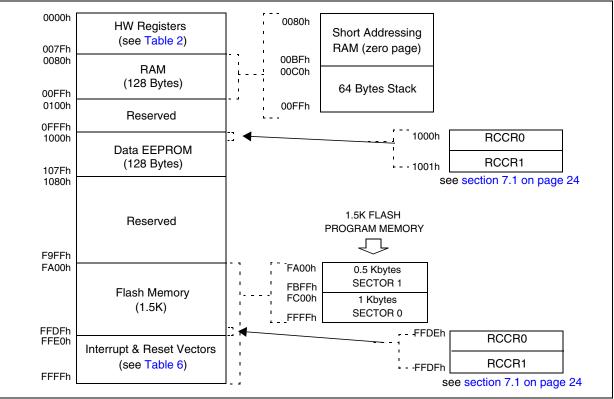

As shown in Figure 4 and Figure 5, the MCU is capable of addressing 64K bytes of memories and I/ O registers.

The available memory locations consist of up to 128 bytes of register locations, 128 bytes of RAM, 128 bytes of data EEPROM and up to 1.5 Kbytes of user program memory. The RAM space includes up to 64 bytes for the stack from 0C0h to 0FFh.

The highest address bytes contain the user reset and interrupt vectors.

The size of Flash Sector 0 is configurable by Option byte.

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

### Figure 4. Memory Map (ST7LITE0x)

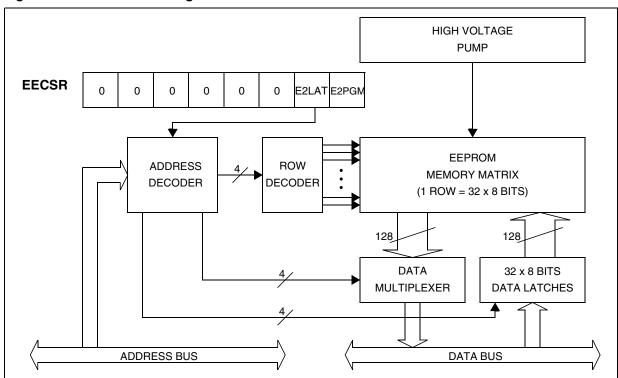

# **5 DATA EEPROM**

# **5.1 INTRODUCTION**

The Electrically Erasable Programmable Read Only Memory can be used as a non-volatile backup for storing data. Using the EEPROM requires a basic access protocol described in this chapter.

#### **5.2 MAIN FEATURES**

- Up to 32 bytes programmed in the same cycle

- EEPROM mono-voltage (charge pump)

- Chained erase and programming cycles

- Internal control of the global programming cycle duration

Δ7/

- WAIT mode management

- Read-out protection

# Figure 7. EEPROM Block Diagram

# CPU REGISTERS (Cont'd) CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | н | Ι | Ν | Z | С |

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 3 = I Interrupt mask.

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except the TRAP software interrupt. This bit is cleared by software.

- 0: Interrupts are enabled.

- 1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

**Note:** Interrupts requested while I is set are latched and can be processed when I is cleared. By default an interrupt routine is not interruptible

because the I bit is set by hardware at the start of the routine and reset by the IRET instruction at the end of the routine. If the I bit is cleared by software in the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrupt routine.

#### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the 7<sup>th</sup> bit of the result.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative (that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = Z Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation. 0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

# **11 ON-CHIP PERIPHERALS**

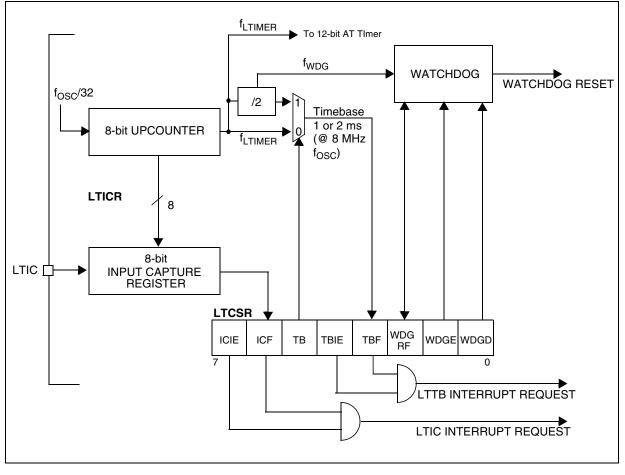

# 11.1 LITE TIMER (LT)

# 11.1.1 Introduction

The Lite Timer can be used for general-purpose timing functions. It is based on a free-running 8-bit upcounter with two software-selectable timebase periods, an 8-bit input capture register and watch-dog function.

### 11.1.2 Main Features

- Realtime Clock

- 8-bit upcounter

- 1 ms or 2 ms timebase period (@ 8 MHz f<sub>OSC</sub>)

- Maskable timebase interrupt

- Input Capture

- 8-bit input capture register (LTICR)

- Maskable interrupt with wakeup from Halt Mode capability

# Figure 31. Lite Timer Block Diagram

- Watchdog

- Enabled by hardware or software (configurable by option byte)

- Optional reset on HALT instruction (configurable by option byte)

- Automatically resets the device unless disable bit is refreshed

47/

- Software reset (Forced Watchdog reset)

- Watchdog reset status flag

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.3.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 11.3.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

**Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the

SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 11.3.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

11.3.7 Interrupts

| Interrupt Event                | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Trans-<br>fer Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event     | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                  | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# **12.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | CP   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a prebyte

The instructions are described with 1 to 4 bytes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC Opcode

- PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

- PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

- PIX 92 Replace an instruction using direct, direct bit or direct relative addressing mode to an instruction using the corresponding indirect addressing mode. It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

- PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

#### 12.2.1 Illegal Opcode Reset

In order to provide enhanced robustness to the device against unexpected behavior, a system of illegal opcode detection is implemented. If a code to be executed does not correspond to any opcode or prebyte value, a reset is generated. This, combined with the Watchdog, allows the detection and recovery from an unexpected fault or interference.

**Note:** A valid prebyte associated with a valid opcode forming an unauthorized combination does not generate a reset.

# INSTRUCTION GROUPS (cont'd)

| Mnemo | Description            | Function/Example    | Dst     | Src     | н | I | Ν | Z | С |

|-------|------------------------|---------------------|---------|---------|---|---|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |   |   |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |   |   | Ν | Z |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A | 0 |   |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |   |   | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |   |   |   |   |   |

| OR    | OR operation           | A = A + M           | А       | М       |   |   | Ν | Z |   |

| POP   | Pop from the Stack     | pop reg             | reg     | М       |   |   |   |   |   |

|       |                        | pop CC              | сс      | М       | Н | I | Ν | Z | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |   |   |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |   |   |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |   |   |   |   |   |

| RIM   | Enable Interrupts      | I = 0               |         |         |   | 0 |   |   |   |

| RLC   | Rotate left true C     | C <= Dst <= C       | reg, M  |         |   |   | Ν | Z | С |

| RRC   | Rotate right true C    | C => Dst => C       | reg, M  |         |   |   | Ν | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |   |   |   |   |   |

| SBC   | Subtract with Carry    | A = A - M - C       | А       | М       |   |   | Ν | Z | С |

| SCF   | Set carry flag         | C = 1               |         |         |   |   |   |   | 1 |

| SIM   | Disable Interrupts     | l = 1               |         |         |   | 1 |   |   |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SLL   | Shift left Logic       | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SRL   | Shift right Logic      | 0 => Dst => C       | reg, M  |         |   |   | 0 | Z | С |

| SRA   | Shift right Arithmetic | Dst7 => Dst => C    | reg, M  |         |   |   | Ν | Z | С |

| SUB   | Subtraction            | A = A - M           | А       | М       |   |   | Ν | Z | С |

| SWAP  | SWAP nibbles           | Dst[74] <=> Dst[30] | reg, M  |         |   |   | Ν | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |   |   | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         |   | 1 |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         |   | 0 |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | А       | М       |   |   | Ν | Z |   |

# **13.3 OPERATING CONDITIONS**

57

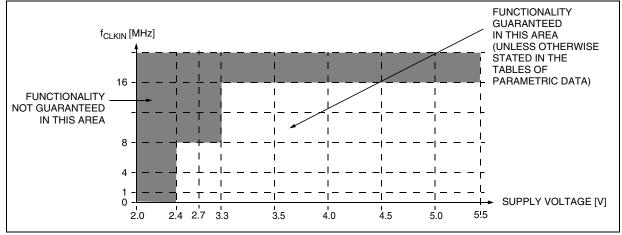

# 13.3.1 General Operating Conditions: Suffix 6 Devices

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified.

| Symbol | Parameter                       | Conditions                      | Min  | Max  | Unit   |

|--------|---------------------------------|---------------------------------|------|------|--------|

|        | f <sub>OSC</sub> = 8 MHz. max., | 2.4                             | 5.5  | V    |        |

| ♥ DD   | V <sub>DD</sub> Supply voltage  | f <sub>OSC</sub> = 16 MHz. max. | 3.3  | 5.5  | v      |

|        |                                 | $3.3V \le V_{DD} \le 5.5V$      | up t | o 16 | MHz    |

| CLKIN  | TCLKIN CLKIN pin                | $2.4V \le V_{DD} \le 3.3V$      | up   | to 8 | IVITIZ |

Note: For further information on clock management and  $f_{CLKIN}$  description, refer to Figure 14 in section 7 on page 24

# 13.3.2 Operating Conditions with Low Voltage Detector (LVD)

$T_A$  = -40 to 85°C, unless otherwise specified

| Symbol                | Parameter                                         | Conditions                                        | Min                                                            | Тур                  | Max                                                            | Unit |

|-----------------------|---------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------------------------------------------------|------|

| V <sub>IT+(LVD)</sub> | Reset release threshold<br>(V <sub>DD</sub> rise) | High Threshold<br>Med. Threshold<br>Low Threshold | 4.00 <sup>1)</sup><br>3.40 <sup>1)</sup><br>2.65 <sup>1)</sup> | 4.25<br>3.60<br>2.90 | 4.50<br>3.80<br>3.15                                           | V    |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall) | High Threshold<br>Med. Threshold<br>Low Threshold | 3.80<br>3.20<br>2.40                                           | 4.05<br>3.40<br>2.70 | 4.30 <sup>1)</sup><br>3.65 <sup>1)</sup><br>2.90 <sup>1)</sup> | v    |

| V <sub>hys</sub>      | LVD voltage threshold hysteresis                  | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>      |                                                                | 200                  |                                                                | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                                   | 20                                                             |                      | 20000                                                          | μs/V |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on V <sub>DD</sub>          | Not detected by the LVD                           |                                                                |                      | 150                                                            | ns   |

| I <sub>DD(LVD</sub> ) | LVD/AVD current consumption                       |                                                   |                                                                | 220                  |                                                                | μA   |

Notes:

**1.** Not tested in production.

**2.** Not tested in production. The  $V_{DD}$  rise time rate condition is needed to ensure a correct device power-on and LVD reset. When the  $V_{DD}$  slope is outside these values, the LVD may not ensure a proper reset of the MCU.

# 13.3.3 Auxiliary Voltage Detector (AVD) Thresholds

$T_A = -40$  to 85°C, unless otherwise specified

| Symbol                  | Parameter                                                  | Conditions                                   | Min  | Тур  | Max  | Unit |

|-------------------------|------------------------------------------------------------|----------------------------------------------|------|------|------|------|

|                         | 1=>0 AVDF flag toggle threshold                            | High Threshold                               | 4.40 | 4.70 | 5.00 |      |

| V <sub>IT+(AVD)</sub>   |                                                            | Med. Threshold                               | 3.90 | 4.10 | 4.30 |      |

|                         | (V <sub>DD</sub> rise)                                     | Low Threshold                                | 3.20 | 3.40 | 3.60 | V    |

|                         | 0=>1 AVDF flag toggle threshold                            | High Threshold                               | 4.30 | 4.60 | 4.90 | v    |

| V <sub>IT-(AVD)</sub>   |                                                            | Med. Threshold                               | 3.70 | 3.90 | 4.10 |      |

|                         | (V <sub>DD</sub> fall)                                     | Low Threshold                                | 2.90 | 3.20 | 3.40 |      |

| V <sub>hys</sub>        | AVD voltage threshold hysteresis                           | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |      | 150  |      | mV   |

| $\Delta V_{\text{IT-}}$ | Voltage drop between AVD flag set and LVD reset activation | V <sub>DD</sub> fall                         |      | 0.45 |      | V    |

47/

vice consumption, the two current values must be

added (except for HALT mode for which the clock

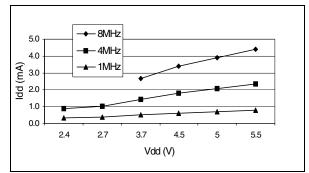

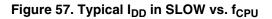

# **13.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total de-

#### 13.4.1 Supply Current

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified

| Symbol          | Parameter                                                       |                                      | Conditions                             |      | Max  | Unit |

|-----------------|-----------------------------------------------------------------|--------------------------------------|----------------------------------------|------|------|------|

|                 | Supply current in RUN mode                                      |                                      | f <sub>CPU</sub> =8MHz <sup>1)</sup>   | 4.50 | 7.00 |      |

|                 |                                                                 | f <sub>CPU</sub> =8MHz <sup>2)</sup> | 1.75                                   | 2.70 | mA   |      |

|                 | Supply current in SLOW mode<br>Supply current in SLOW WAIT mode |                                      | f <sub>CPU</sub> =250kHz <sup>3)</sup> | 0.75 | 1.13 | ША   |

| I <sub>DD</sub> |                                                                 |                                      | f <sub>CPU</sub> =250kHz <sup>4)</sup> | 0.65 | 1    |      |

|                 |                                                                 |                                      | -40°C≤T <sub>A</sub> ≤+85°C            | 0.50 | 10   |      |

|                 | Supply current in HALT mode <sup>5)</sup>                       | -                                    | -40°C≤T <sub>A</sub> ≤+105°C           | TBD  | TBD  | μA   |

|                 |                                                                 |                                      | T <sub>A</sub> = +85°C                 | 5    | 100  |      |

is stopped).

#### Notes:

47/

1. CPU running with memory access, all I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

2. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

3. SLOW mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

**4.** SLOW-WAIT mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled. **5.** All I/O pins in output mode with a static value at  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max and  $f_{CPU}$  max.

### Figure 56. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

### **13.7 EMC (ELECTROMAGNETIC COMPATIBILITY) CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 13.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling two -+LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 13.7.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Level/<br>Class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD}$ =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2        | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | 3B              |

#### 13.7.2 EMI (Electromagnetic interference)

Based on a simple application running on the product (toggling two LEDs through the I/O ports), the product is monitored in terms of emission. This

emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

#### Table 20: EMI emissions

| Symbol Parameter                        | Parameter                                   | Conditions                                  | Monitored       | Max vs. [f | Unit |      |

|-----------------------------------------|---------------------------------------------|---------------------------------------------|-----------------|------------|------|------|

|                                         | conditions                                  | Frequency Band                              | 1/4MHz          | 1/8MHz     |      |      |

| V <sub>DD</sub> =5V, T <sub>4</sub> =+2 | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, | 0.1MHz to 30MHz                             | 8               | 14         |      |      |

| S                                       | Peak level                                  | SO16 package,<br>conforming to SAE J 1752/3 | 30MHz to 130MHz | 27         | 32   | dBμV |

| S <sub>EMI</sub>                        | I Eak level                                 |                                             | 130MHz to 1GHz  | 26         | 28   |      |

|                                         |                                             |                                             | SAE EMI Level   | 3.5        | 4    | -    |

Note:

1. Data based on characterization results, not tested in production.

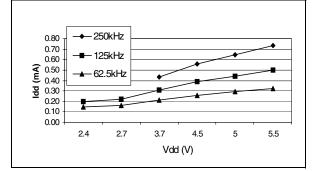

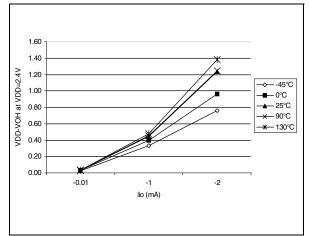

# I/O PORT PIN CHARACTERISTICS (Cont'd)

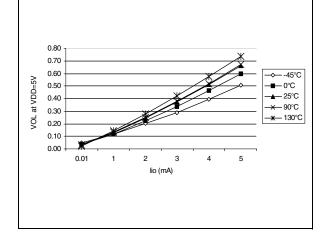

# Figure 64. Typical $V_{OL}$ at $V_{DD}$ =3.3V (standard)

# Figure 65. Typical $V_{OL}$ at $V_{DD}$ =5V (standard)

57

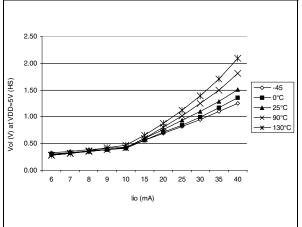

Figure 66. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)

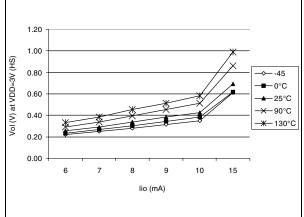

Figure 67. Typical V<sub>OL</sub> at V<sub>DD</sub>=3V (high-sink)

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

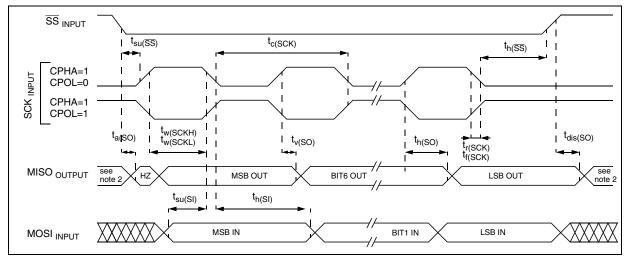

#### Figure 79. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

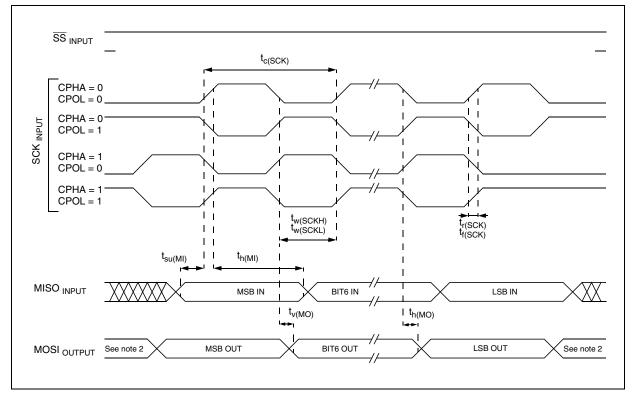

# Figure 80. SPI Master Timing Diagram 1)

#### Notes:

- 1. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

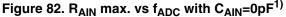

# ADC CHARACTERISTICS (Cont'd)

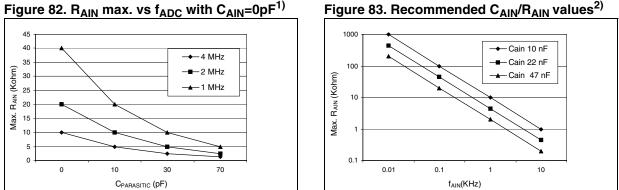

#### Notes:

<u>ل</u>حک

1.  $C_{PARASITIC}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (3pF). A high  $C_{PARASITIC}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2. This graph shows that depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization and to allow the use of a larger serial resistor ( $R_{AIN}$ ). It is valid for all  $f_{ADC}$  frequencies  $\leq 4MHz$ .

#### 13.11.1 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

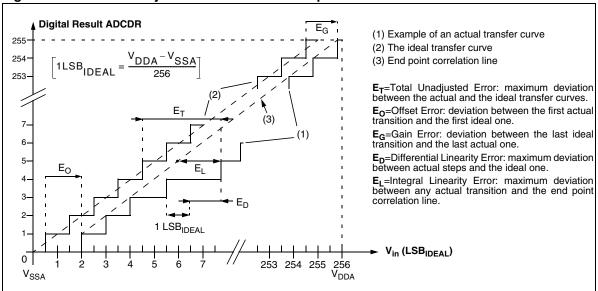

# ADC CHARACTERISTICS (Cont'd)

#### ADC Accuracy with V<sub>DD</sub>=5.0V

$T_A = -40^{\circ}C$  to 85°C, unless otherwise specified

| Symbol         | Parameter                                  | Conditions                                                            | Тур | Max              | Unit |

|----------------|--------------------------------------------|-----------------------------------------------------------------------|-----|------------------|------|

| E <sub>T</sub> | Total unadjusted error <sup>2)</sup>       |                                                                       |     |                  |      |

| EO             | Offset error <sup>2)</sup>                 |                                                                       |     | -0.5 / +1        | LSB  |

| E <sub>G</sub> | Gain Error <sup>2)</sup>                   | f <sub>CPU</sub> =4MHz, f <sub>ADC</sub> =2MHz, V <sub>DD</sub> =5.0V |     | ±1               |      |

| ED             | Differential linearity error <sup>2)</sup> |                                                                       |     | ±1 <sup>1)</sup> |      |

| EL             | Integral linearity error <sup>2)</sup>     |                                                                       |     | ±1 <sup>1)</sup> |      |

| E <sub>T</sub> | Total unadjusted error <sup>2)</sup>       |                                                                       | ±2  |                  |      |

| E <sub>O</sub> | Offset error <sup>2)</sup>                 |                                                                       |     | -0.5 / 3.5       |      |

| E <sub>G</sub> | Gain Error <sup>2)</sup>                   | f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz ,V <sub>DD</sub> =5.0V |     | -2 / 0           | LSB  |

| ED             | Differential linearity error <sup>2)</sup> |                                                                       |     | ±1 <sup>1)</sup> |      |

| EL             | Integral linearity error <sup>2)</sup>     |                                                                       |     | ±1 <sup>1)</sup> |      |

#### Notes:

1. Data based on characterization results over the whole temperature range, monitored in production.

2. Injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input.

Analog pins can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 13.8 does not affect the ADC accuracy.

\_

### ADC CHARACTERISTICS (Cont'd)

57

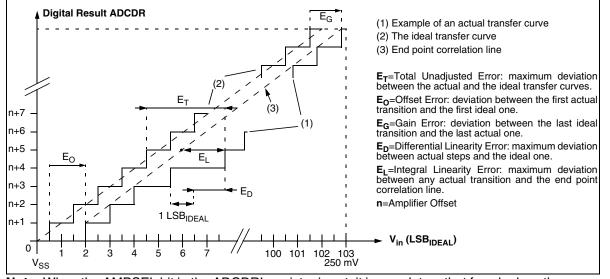

#### Figure 84. ADC Accuracy Characteristics with Amplifier disabled

#### Figure 85. ADC Accuracy Characteristics with Amplifier enabled

**Note:** When the AMPSEL bit in the ADCDRL register is set, it is mandatory that  $f_{ADC}$  be less than or equal to 2 MHz. (if  $f_{CPU}$ =8MHz. then SPEED=0, SLOW=1).

# **15.4 ST7 APPLICATION NOTES**

# Table 24. ST7 Application Notes

| IDENTIFICATION DESCRIPTION |                                                                                             |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| APPLICATION EXAMPLES       |                                                                                             |  |  |  |  |

| AN1658                     | SERIAL NUMBERING IMPLEMENTATION                                                             |  |  |  |  |

| AN1720                     | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                  |  |  |  |  |

| AN1755                     | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                 |  |  |  |  |

| AN1756                     | CHOOSING A DALI IMPLEMENTATION STRATEGY WITH ST7DALI                                        |  |  |  |  |

| AN1812                     | A HIGH PRECISION, LOW COST, SINGLE SUPPLY ADC FOR POSITIVE AND NEGATIVE IN-<br>PUT VOLTAGES |  |  |  |  |

| EXAMPLE DRIVE              | EXAMPLE DRIVERS                                                                             |  |  |  |  |

| AN 969                     | SCI COMMUNICATION BETWEEN ST7 AND PC                                                        |  |  |  |  |

| AN 970                     | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                    |  |  |  |  |

| AN 971                     | I <sup>2</sup> C COMMUNICATION BETWEEN ST7 AND M24CXX EEPROM                                |  |  |  |  |

| AN 972                     | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                       |  |  |  |  |

| AN 973                     | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                             |  |  |  |  |

| AN 974                     | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                               |  |  |  |  |

| AN 976                     | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                             |  |  |  |  |

| AN 979                     | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                 |  |  |  |  |

| AN 980                     | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                           |  |  |  |  |

| AN1017                     | USING THE ST7 UNIVERSAL SERIAL BUS MICROCONTROLLER                                          |  |  |  |  |

| AN1041                     | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                   |  |  |  |  |

| AN1042                     | ST7 ROUTINE FOR I <sup>2</sup> C SLAVE MODE MANAGEMENT                                      |  |  |  |  |

| AN1044                     | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                          |  |  |  |  |

| AN1045                     | ST7 S/W IMPLEMENTATION OF I <sup>2</sup> C BUS MASTER                                       |  |  |  |  |

| AN1046                     | UART EMULATION SOFTWARE                                                                     |  |  |  |  |

| AN1047                     | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                      |  |  |  |  |

| AN1048                     | ST7 SOFTWARE LCD DRIVER                                                                     |  |  |  |  |

| AN1078                     | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                |  |  |  |  |

| AN1082                     | DESCRIPTION OF THE ST72141 MOTOR CONTROL PERIPHERALS REGISTERS                              |  |  |  |  |

| AN1083                     | ST72141 BLDC MOTOR CONTROL SOFTWARE AND FLOWCHART EXAMPLE                                   |  |  |  |  |

| AN1105                     | ST7 PCAN PERIPHERAL DRIVER                                                                  |  |  |  |  |

| AN1129                     | PWM MANAGEMENT FOR BLDC MOTOR DRIVES USING THE ST72141                                      |  |  |  |  |

| AN1130                     | AN INTRODUCTION TO SENSORLESS BRUSHLESS DC MOTOR DRIVE APPLICATIONS WITH THE ST72141        |  |  |  |  |

| AN1148                     | USING THE ST7263 FOR DESIGNING A USB MOUSE                                                  |  |  |  |  |

| AN1149                     | HANDLING SUSPEND MODE ON A USB MOUSE                                                        |  |  |  |  |

| AN1180                     | USING THE ST7263 KIT TO IMPLEMENT A USB GAME PAD                                            |  |  |  |  |

| AN1276                     | BLDC MOTOR START ROUTINE FOR THE ST72141 MICROCONTROLLER                                    |  |  |  |  |

| AN1321                     | USING THE ST72141 MOTOR CONTROL MCU IN SENSOR MODE                                          |  |  |  |  |

| AN1325                     | USING THE ST7 USB LOW-SPEED FIRMWARE V4.X                                                   |  |  |  |  |

| AN1445                     | EMULATED 16-BIT SLAVE SPI                                                                   |  |  |  |  |

| AN1475                     | DEVELOPING AN ST7265X MASS STORAGE APPLICATION                                              |  |  |  |  |

| AN1504                     | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                     |  |  |  |  |

| AN1602                     | 16-BIT TIMING OPERATIONS USING ST7262 OR ST7263B ST7 USB MCUS                               |  |  |  |  |

| AN1633                     | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION IN ST7 NON-USB APPLICATIONS                    |  |  |  |  |

| AN1712                     | GENERATING A HIGH RESOLUTION SINEWAVE USING ST7 PWMART                                      |  |  |  |  |

| AN1713                     | SMBUS SLAVE DRIVER FOR ST7 I2C PERIPHERALS                                                  |  |  |  |  |

| AN1753                     | SOFTWARE UART USING 12-BIT ART                                                              |  |  |  |  |

|                            |                                                                                             |  |  |  |  |

# Table 24. ST7 Application Notes

| IDENTIFICATION     | DESCRIPTION                                                                 |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|

| AN1947             | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                         |  |  |  |

| GENERAL PURPOSE    |                                                                             |  |  |  |

| AN1476             | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                   |  |  |  |

| AN1526             | ST7FLITE0 QUICK REFERENCE NOTE                                              |  |  |  |

| AN1709             | EMC DESIGN FOR ST MICROCONTROLLERS                                          |  |  |  |

| AN1752             | ST72324 QUICK REFERENCE NOTE                                                |  |  |  |

| PRODUCT EVALUATION |                                                                             |  |  |  |

| AN 910             | PERFORMANCE BENCHMARKING                                                    |  |  |  |

| AN 990             | ST7 BENEFITS VS INDUSTRY STANDARD                                           |  |  |  |

| AN1077             | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                   |  |  |  |

| AN1086             | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                  |  |  |  |

| AN1103             | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141            |  |  |  |

| AN1150             | BENCHMARK ST72 VS PC16                                                      |  |  |  |

| AN1151             | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                           |  |  |  |

| AN1278             | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                  |  |  |  |

| PRODUCT MIGRA      | TION                                                                        |  |  |  |

| AN1131             | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324          |  |  |  |

| AN1322             | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                       |  |  |  |

| AN1365             | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                  |  |  |  |

| AN1604             | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                      |  |  |  |

| AN2200             | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB              |  |  |  |

| PRODUCT OPTIMI     | ZATION                                                                      |  |  |  |

| AN 982             | USING ST7 WITH CERAMIC RESONATOR                                            |  |  |  |

| AN1014             | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                   |  |  |  |

| AN1015             | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE           |  |  |  |

| AN1040             | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                     |  |  |  |

| AN1070             | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                       |  |  |  |

| AN1181             | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                               |  |  |  |

| AN1324             | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS          |  |  |  |

| AN1502             | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                |  |  |  |

| AN1529             | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY        |  |  |  |

| AN1530             | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLATOR |  |  |  |

| AN1605             | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE            |  |  |  |

| AN1636             | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                          |  |  |  |

| AN1828             | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE           |  |  |  |

| AN1946             | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC          |  |  |  |

| AN1953             | PFC FOR ST7MC STARTER KIT                                                   |  |  |  |

| AN1971             | ST7LITE0 MICROCONTROLLED BALLAST                                            |  |  |  |

| PROGRAMMING A      | ND TOOLS                                                                    |  |  |  |

| AN 978             | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                          |  |  |  |

| AN 983             | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                           |  |  |  |

| AN 985             | EXECUTING CODE IN ST7 RAM                                                   |  |  |  |

| AN 986             | USING THE INDIRECT ADDRESSING MODE WITH ST7                                 |  |  |  |

| AN 987             | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                      |  |  |  |

| AN 988             | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                       |  |  |  |

| AN1039             | ST7 MATH UTILITY ROUTINES                                                   |  |  |  |

| 09-Oct-06 | 5 | Removed QFN20 pinout and mechanical data.<br>Modified text in External Interrupt Function section in section 10.2.1 on page 42<br>Modified Table 24 on page 116 (and QFN20 rows in grey).<br>Added "External Clock Source" on page 91 and Figure 61 on page 91<br>Modified description of CNTR[11:0] bits in section 11.2.6 on page 56<br>Updated option list on page 116<br>Changed section 15.3 on page 117                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Nov-07 | 6 | Title of the document modified<br>Modified LOCKED bit description in section 8.4.4 on page 36<br>In Table 1 on page 7 and section 13.2.2 on page 82, note "negative injection not allowed on<br>PB0 and PB1 pins" replaced by "negative injection not allowed on PB1 pin"<br>Added QFN20 package pinout (with new QFN20 mechanical data): Figure 2 on page 6 and<br>Figure 86 on page 109<br>Modified section 8.4.4 on page 36<br>Removed one note in section 11.1.3.1 on page 49<br>Modified section 13.7 on page 93<br>Modified "PACKAGE MECHANICAL DATA" on page 109 (values in inches rounded to 4 dec-<br>imal digits)<br>Modified section 15.2 on page 114 ("Ordering information scheme" on page 115 added and<br>table removed) and option list on page 116<br>Removed "soldering information" section<br>Modified section 15.3.5 on page 117 |

57

Notes:

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com