Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1KB (1K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flites2y0b6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

\_

| 10 I. | /O P0     | ORTS                                                                                         | 42  |

|-------|-----------|----------------------------------------------------------------------------------------------|-----|

| 1     | 10.1      |                                                                                              | 42  |

| 1     | 10.2      | FUNCTIONAL DESCRIPTION                                                                       | 42  |

| 1     | 10.3      | UNUSED I/O PINS                                                                              | 46  |

| 1     | 10.4      | LOW POWER MODES                                                                              | 46  |

| 1     | 10.5      | INTERRUPTS                                                                                   | 46  |

| 1     | 10.6      | I/O PORT IMPLEMENTATION                                                                      | 46  |

| 11 (  | ON-C      | HIP PERIPHERALS                                                                              | 48  |

| 1     | 11.1      | LITE TIMER (LT)                                                                              |     |

| 1     | 11.2      | 12-BIT AUTORELOAD TIMER (AT)                                                                 |     |

| 1     | 11.3      | SERIAL PERIPHERAL INTERFACE (SPI)                                                            | 59  |

|       |           | 8-BIT A/D CONVERTER (ADC)                                                                    |     |

| 12 I  | NSTE      |                                                                                              |     |

|       | 12.1      | ST7 ADDRESSING MODES                                                                         |     |

|       |           | INSTRUCTION GROUPS                                                                           |     |

| 13 E  | ELEC      |                                                                                              | -   |

| 1     | 13.1      | PARAMETER CONDITIONS                                                                         | -   |

| 1     | 13.2      | ABSOLUTE MAXIMUM RATINGS                                                                     |     |

| 1     | 13.3      | OPERATING CONDITIONS                                                                         |     |

| 1     | 13.4      | SUPPLY CURRENT CHARACTERISTICS                                                               |     |

| 1     | 13.5      | CLOCK AND TIMING CHARACTERISTICS                                                             |     |

| 1     | 13.6      | MEMORY CHARACTERISTICS                                                                       |     |

| 1     | 13.7      | EMC (ELECTROMAGNETIC COMPATIBILITY) CHARACTERISTICS                                          |     |

| 1     | 13.8      | I/O PORT PIN CHARACTERISTICS                                                                 | 95  |

| 1     | 13.9      | CONTROL PIN CHARACTERISTICS 10                                                               | 00  |

| 1     | 13.10     | COMMUNICATION INTERFACE CHARACTERISTICS                                                      | 02  |

| 1     | 13.11     | 8-BIT ADC CHARACTERISTICS 10                                                                 | 04  |

| 14 F  | PACK      | (AGE CHARACTERISTICS                                                                         |     |

|       | 14.1      |                                                                                              |     |

|       |           | THERMAL CHARACTERISTICS 1                                                                    |     |

|       |           | CE CONFIGURATION AND ORDERING INFORMATION                                                    |     |

|       | -         | OPTION BYTES 1                                                                               |     |

|       |           | DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE 1                                  |     |

|       |           | DEVELOPMENT TOOLS                                                                            |     |

|       |           | ST7 APPLICATION NOTES                                                                        |     |

|       |           | WN LIMITATIONS                                                                               |     |

|       |           | EXECUTION OF BTJX INSTRUCTION 12                                                             |     |

| 1     | 16.2<br>V | IN-CIRCUIT PROGRAMMING OF DEVICES PREVIOUSLY PROGRAMMED WITH HAF<br>WARE WATCHDOG OPTION 121 | ≀D- |

| 1     | 16.3      | IN-CIRCUIT DEBUGGING WITH HARDWARE WATCHDOG 12                                               | 21  |

| 1     | 16.4      | RECOMMENDATIONS WHEN LVD IS ENABLED                                                          | 21  |

| 1     | 16.5      | CLEARING ACTIVE INTERRUPTS OUTSIDE INTERRUPT ROUTINE 12                                      | 21  |

| 17 F  | REVIS     | SION HISTORY                                                                                 | 22  |

| Pin   | n°      |            |     | Level         |        | Level Port / Control |     |     |     |     |     |                  |                          |

|-------|---------|------------|-----|---------------|--------|----------------------|-----|-----|-----|-----|-----|------------------|--------------------------|

| 0     | IP16    | Pin Name   | be  | L.            |        |                      | Inp | out |     | Out | put | Main<br>Function | Alternate Function       |

| QFN20 | SO16/DI |            | Ту  | Type<br>Input | Output | float                | ndw | int | ana | OD  | ЬΡ  | (after reset)    |                          |

| 15    | 14      | PA2/ATPWM0 | I/O | $C_T$         | HS     | Х                    | Х   |     |     | Х   | Х   | Port A2          | Auto-Reload Timer PWM0   |

| 16    | 15      | PA1        | I/O | $C_T$         | HS     | Х                    | Х   |     |     | х   | Х   | Port A1          |                          |

| 17    | 16      | PA0/LTIC   | I/O | $C_T$         | HS     | X                    | е   | i0  |     | Х   | Х   | Port A0          | Lite Timer Input Capture |

## Note:

In the interrupt input column, " $ei_x$ " defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

## REGISTER AND MEMORY MAP (Cont'd)

## Legend: x=undefined, R/W=read/write

## Table 2. Hardware Register Map

| Address                                                     | Block                | Register<br>Label                                           | Register Name                                                                                                                                                                                           | Reset<br>Status                               | Remarks                                                   |

|-------------------------------------------------------------|----------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 0000h<br>0001h<br>0002h                                     | Port A               | PADR<br>PADDR<br>PAOR                                       | Port A Data Register<br>Port A Data Direction Register<br>Port A Option Register                                                                                                                        | 00h <sup>1)</sup><br>00h<br>40h               | R/W<br>R/W<br>R/W                                         |

| 0003h<br>0004h<br>0005h                                     | Port B               | PBDR<br>PBDDR<br>PBOR                                       | Port B Data Register<br>Port B Data Direction Register<br>Port B Option Register                                                                                                                        | E0h <sup>1)</sup><br>00h<br>00h               | R/W<br>R/W<br>R/W <sup>2)</sup>                           |

| 0006h to<br>000Ah                                           |                      |                                                             | Reserved area (5 bytes)                                                                                                                                                                                 |                                               |                                                           |

| 000Bh<br>000Ch                                              | LITE<br>TIMER        | LTCSR<br>LTICR                                              | Lite Timer Control/Status Register<br>Lite Timer Input Capture Register                                                                                                                                 | xxh<br>xxh                                    | R/W<br>Read Only                                          |

| 000Dh<br>000Eh<br>000Fh<br>0010h<br>0011h<br>0012h<br>0013h | AUTO-RELOAD<br>TIMER | ATCSR<br>CNTRH<br>CNTRL<br>ATRH<br>ATRL<br>PWMCR<br>PWM0CSR | Timer Control/Status Register<br>Counter Register High<br>Counter Register Low<br>Auto-Reload Register High<br>Auto-Reload Register Low<br>PWM Output Control Register<br>PWM 0 Control/Status Register | 00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>R/W<br>R/W |

| 0014h to<br>0016h                                           |                      |                                                             | Reserved area (3 bytes)                                                                                                                                                                                 |                                               |                                                           |

| 0017h<br>0018h                                              | AUTO-RELOAD<br>TIMER | DCR0H<br>DCR0L                                              | PWM 0 Duty Cycle Register High<br>PWM 0 Duty Cycle Register Low                                                                                                                                         | 00h<br>00h                                    | R/W<br>R/W                                                |

| 0019h to<br>002Eh                                           |                      |                                                             | Reserved area (22 bytes)                                                                                                                                                                                |                                               |                                                           |

| 0002Fh                                                      | FLASH                | FCSR                                                        | Flash Control/Status Register                                                                                                                                                                           | 00h                                           | R/W                                                       |

| 00030h                                                      | EEPROM               | EECSR                                                       | Data EEPROM Control/Status Register                                                                                                                                                                     | 00h                                           | R/W                                                       |

| 0031h<br>0032h<br>0033h                                     | SPI                  | SPIDR<br>SPICR<br>SPICSR                                    | SPI Data I/O Register<br>SPI Control Register<br>SPI Control/Status Register                                                                                                                            | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                                         |

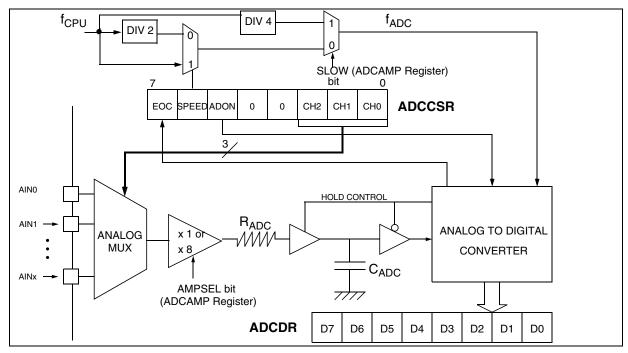

| 0034h<br>0035h<br>0036h                                     | ADC                  | ADCCSR<br>ADCDR<br>ADCAMP                                   | A/D Control Status Register<br>A/D Data Register<br>A/D Amplifier Control Register                                                                                                                      | 00h<br>00h<br>00h                             | R/W<br>Read Only<br>R/W                                   |

| 0037h                                                       | ITC                  | EICR                                                        | External Interrupt Control Register                                                                                                                                                                     | 00h                                           | R/W                                                       |

| 0038h<br>0039h                                              | CLOCKS               | MCCSR<br>RCCR                                               | Main Clock Control/Status Register<br>RC oscillator Control Register                                                                                                                                    | 00h<br>FFh                                    | R/W<br>R/W                                                |

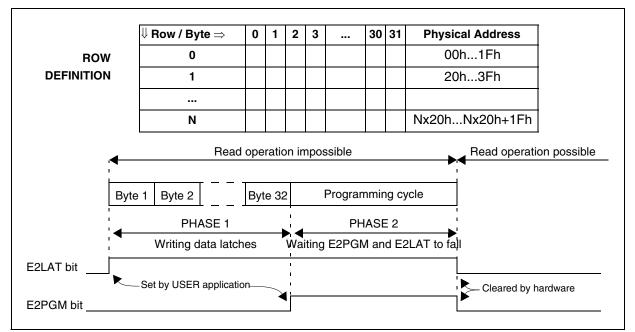

## DATA EEPROM (Cont'd)

## Figure 9. Data E<sup>2</sup>PROM Write Operation

**Note:** If a programming cycle is interrupted (by RESET action), the integrity of the data in memory will not be guaranteed.

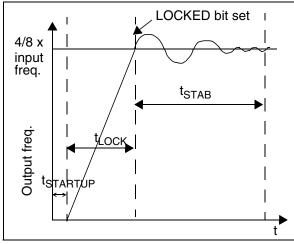

Figure 13. PLL Output Frequency Timing Diagram

When the PLL is started, after reset or wakeup from Halt mode or AWUFH mode, it outputs the clock after a delay of t<sub>STARTUP</sub>.

When the PLL output signal reaches the operating frequency, the LOCKED bit in the SICSCR register is set. Full PLL accuracy (ACC<sub>PLL</sub>) is reached after a stabilization time of  $t_{STAB}$  (see Figure 13 and 13.3.4 Internal RC Oscillator and PLL)

Refer to section 8.4.4 on page 36 for a description of the LOCKED bit in the SICSR register.

## 7.3 REGISTER DESCRIPTION

# MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |

Bits 7:2 = Reserved, must be kept cleared.

## Table 5. Clock Register Map and Reset Values

Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

- 0: MCO clock disabled, I/O port free for general purpose I/O.

- 1: MCO clock enabled.

## Bit 0 = SMS Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ .

0: Normal mode (f<sub>CPU =</sub> f<sub>OSC</sub>

1: Slow mode  $(f_{CPU} = f_{OSC}/32)$

## **RC CONTROL REGISTER (RCCR)**

Read / Write

Reset Value: 1111 1111 (FFh)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CR7 | CR6 | CR5 | CR4 | CR3 | CR2 | CR1 | CR0 |

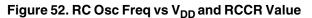

# Bits 7:0 = **CR[7:0]** *RC* Oscillator Frequency Adjustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up.

00h = maximum available frequency

FFh = lowest available frequency

**Note:** To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

| Address<br>(Hex.) | Register<br>Label    | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|-------------------|----------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| 0038h             | MCCSR<br>Reset Value | 0        | 0        | 0        | 0        | 0        | 0        | MCO<br>0 | SMS<br>0 |

| 0039h             | RCCR<br>Reset Value  | CR7<br>1 | CR6<br>1 | CR5<br>1 | CR4<br>1 | CR3<br>1 | CR2<br>1 | CR1<br>1 | CR0<br>1 |

## 7.4 RESET SEQUENCE MANAGER (RSM)

## 7.4.1 Introduction

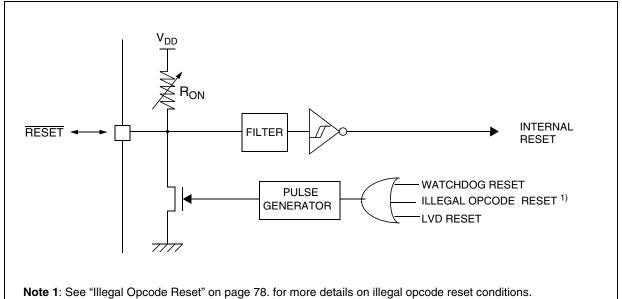

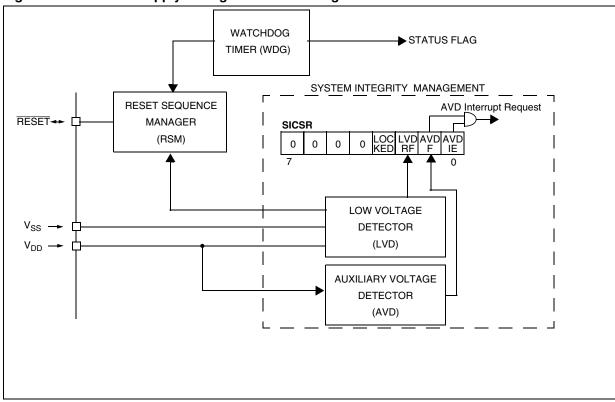

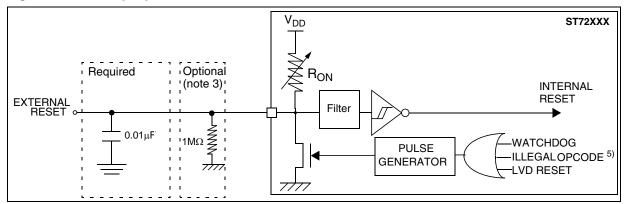

The reset sequence manager includes three RE-SET sources as shown in Figure 16:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to section 11.2.1 on page 53 for further details.

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

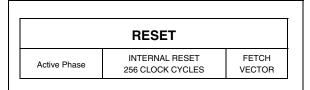

The basic RESET sequence consists of 3 phases as shown in Figure 15:

- Active Phase depending on the RESET source

- 256 CPU clock cycle delay

- RESET vector fetch

57/

## Figure 16.Reset Block Diagram

The 256 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state.

The RESET vector fetch phase duration is 2 clock cycles.

If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 13).

### Figure 15. RESET Sequence Phases

<u>ل</u>حک

## I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

## Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING:** The analog input voltage level must be within the limits stated in the absolute maximum ratings.

## 10.3 UNUSED I/O PINS

Unused I/O pins must be connected to fixed voltage levels. Refer to Section 13.8.

## **10.4 LOW POWER MODES**

| Mode | Description                                                                          |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |  |  |  |  |  |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |  |  |  |  |  |

#### **10.5 INTERRUPTS**

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  | Yes                  |

## **10.6 I/O PORT IMPLEMENTATION**

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input.

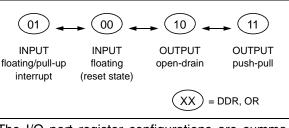

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 30 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

## Figure 30. Interrupt I/O Port State Transitions

The I/O port register configurations are summarised as follows.

| Port   | Pin name     | Input (  | DDR=0)            | Output (DDR=1) |           |  |

|--------|--------------|----------|-------------------|----------------|-----------|--|

| POIL   | Fill liallie | OR = 0   | OR = 1            | OR = 0         | OR = 1    |  |

|        | PA7          | floating | pull-up interrupt | open drain     | push-pull |  |

| Port A | PA6:1        | floating | pull-up           | open drain     | push-pull |  |

|        | PA0          | floating | pull-up interrupt | open drain     | push-pull |  |

|        | PB4          | floating | pull-up           | open drain     | push-pull |  |

| Port B | PB3          | floating | pull-up interrupt | open drain     | push-pull |  |

| TOILD  | PB2:1        | floating | pull-up           | open drain     | push-pull |  |

|        | PB0          | floating | pull-up interrupt | open drain     | push-pull |  |

#### **Table 11. Port Configuration**

## SERIAL PERIPHERAL INTERFACE (Cont'd)

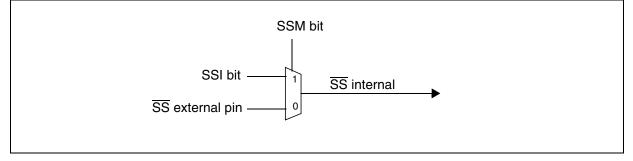

## 11.3.3.2 Slave Select Management

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see Figure 40)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$ signal level is driven by writing to the SSI bit in the SPICSR register.

## In Master mode:

5/

- SS internal must be held high continuously

## In Slave Mode:

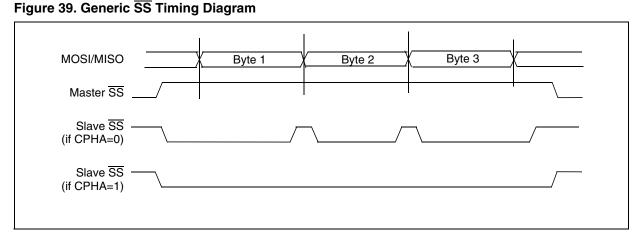

There are two cases depending on the data/clock timing relationship (see Figure 39):

- If CPHA=1 (data latched on 2nd clock edge):

- $\overline{SS}$  internal must be held low during the entire transmission. This implies that in single slave applications the  $\overline{SS}$  pin either can be tied to  $V_{SS}$ , or made free for standard I/O by managing the  $\overline{SS}$  function by software (SSM= 1 and SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

- SS internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see Section 11.3.5.3).

## Figure 40. Hardware/Software Slave Select Management

## ST7 ADDRESSING MODES (cont'd)

## 12.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                            |

|----------------------------|-------------------------------------|

| NOP                        | No operation                        |

| TRAP                       | S/W Interrupt                       |

| WFI                        | Wait For Interrupt (Low Power Mode) |

| HALT                       | Halt Oscillator (Lowest Power Mode) |

| RET                        | Subroutine Return                   |

| IRET                       | Interrupt Subroutine Return         |

| SIM                        | Set Interrupt Mask                  |

| RIM                        | Reset Interrupt Mask                |

| SCF                        | Set Carry Flag                      |

| RCF                        | Reset Carry Flag                    |

| RSP                        | Reset Stack Pointer                 |

| LD                         | Load                                |

| CLR                        | Clear                               |

| PUSH/POP                   | Push/Pop to/from the stack          |

| INC/DEC                    | Increment/Decrement                 |

| TNZ                        | Test Negative or Zero               |

| CPL, NEG                   | 1 or 2 Complement                   |

| MUL                        | Byte Multiplication                 |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations         |

| SWAP                       | Swap Nibbles                        |

## 12.1.2 Immediate

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

## 12.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

## **Direct (Short)**

The address is a byte, thus requires only 1 byte after the opcode, but only allows 00 - FF addressing space.

## Direct (Long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

## 12.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three submodes:

## Indexed (No Offset)

There is no offset (no extra byte after the opcode), and allows 00 - FF addressing space.

## Indexed (Short)

The offset is a byte, thus requires only 1 byte after the opcode and allows 00 - 1FE addressing space.

## Indexed (Long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

## 12.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer).

The pointer address follows the opcode. The indirect addressing mode consists of two submodes:

## Indirect (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

#### Indirect (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

## INSTRUCTION GROUPS (cont'd)

| Mnemo | Description                | Function/Example    | Dst    | Src | н | I | Ν | Z | С |

|-------|----------------------------|---------------------|--------|-----|---|---|---|---|---|

| ADC   | Add with Carry             | A = A + M + C       | А      | М   | Н |   | Ν | Z | С |

| ADD   | Addition                   | A=A+M               | А      | М   | Н |   | Ν | Z | С |

| AND   | Logical And                | A = A . M           | А      | М   |   |   | Ν | Z |   |

| BCP   | Bit compare A, Memory      | tst (A . M)         | А      | М   |   |   | Ν | Z |   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |   |   |   |   |   |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| CALL  | Call subroutine            |                     |        |     |   |   |   |   |   |

| CALLR | Call subroutine relative   |                     |        |     |   |   |   |   |   |

| CLR   | Clear                      |                     | reg, M |     |   |   | 0 | 1 |   |

| CP    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |   |   | Ν | Z | С |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |   |   | Ν | Z | 1 |

| DEC   | Decrement                  | dec Y               | reg, M |     |   |   | Ν | Z |   |

| HALT  | Halt                       |                     |        |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     | Н | I | Ν | Z | С |

| INC   | Increment                  | inc X               | reg, M |     |   |   | Ν | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |   |   |   |   |   |

| JRA   | Jump relative always       |                     |        |     |   |   |   |   |   |

| JRT   | Jump relative              |                     |        |     |   |   |   |   |   |

| JRF   | Never jump                 | jrf *               |        |     |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |   |   |   |   |   |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |   |   |   |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |   |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |   |   |   |   |   |

| JRNC  | Jump if C = 0              | C = 0 ?             |        |     |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |   |   |   |   |   |

| JRUGE | Jump if C = 0              | Jmp if unsigned >=  |        |     |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |   |   |   |   |   |

## **OPERATING CONDITIONS** (Cont'd)

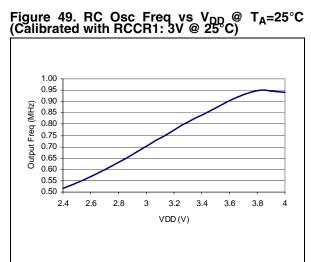

#### Figure 50. RC Osc Freq vs V<sub>DD</sub> (Calibrated with RCCR0: 5V@ 25°C)

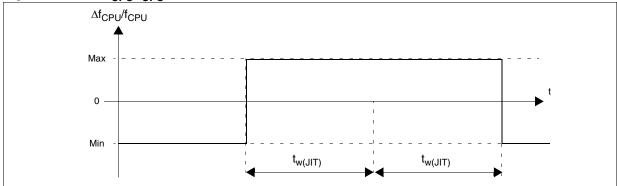

## Figure 53. PLL $\Delta f_{CPU}/f_{CPU}$ versus time

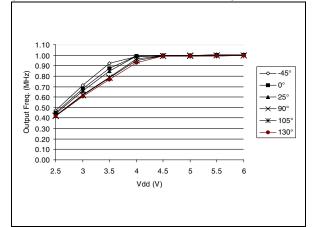

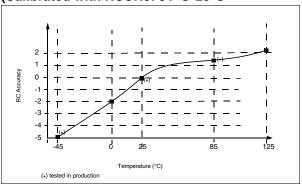

Figure 51. Typical RC oscillator Accuracy vs temperature @ V<sub>DD</sub>=5V (Calibrated with RCCR0: 5V @ 25°C

vice consumption, the two current values must be

added (except for HALT mode for which the clock

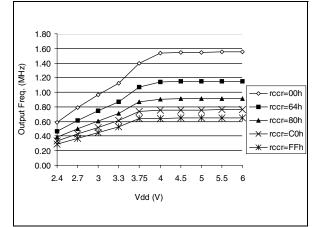

## **13.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total de-

## 13.4.1 Supply Current

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified

| Symbol          | Parameter                                                       | Conditions |                                        | Тур  | Max  | Unit |  |

|-----------------|-----------------------------------------------------------------|------------|----------------------------------------|------|------|------|--|

|                 | Supply current in RUN mode                                      |            | f <sub>CPU</sub> =8MHz <sup>1)</sup>   | 4.50 | 7.00 |      |  |

|                 | Supply current in WAIT mode                                     |            | f <sub>CPU</sub> =8MHz <sup>2)</sup>   | 1.75 | 2.70 | mA   |  |

|                 | Supply current in SLOW mode<br>Supply current in SLOW WAIT mode |            | f <sub>CPU</sub> =250kHz <sup>3)</sup> | 0.75 | 1.13 |      |  |

| I <sub>DD</sub> |                                                                 |            | f <sub>CPU</sub> =250kHz <sup>4)</sup> | 0.65 | 1    |      |  |

|                 | Supply current in HALT mode <sup>5)</sup>                       |            | -40°C≤T <sub>A</sub> ≤+85°C            | 0.50 | 10   |      |  |

|                 |                                                                 |            | -40°C≤T <sub>A</sub> ≤+105°C           | TBD  | TBD  | μA   |  |

|                 |                                                                 |            | T <sub>A</sub> = +85°C                 | 5    | 100  |      |  |

is stopped).

#### Notes:

47/

1. CPU running with memory access, all I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

2. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

3. SLOW mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

**4.** SLOW-WAIT mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled. **5.** All I/O pins in output mode with a static value at  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max and  $f_{CPU}$  max.

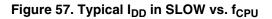

## Figure 56. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

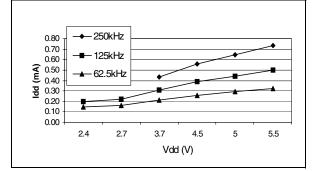

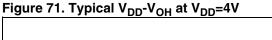

## Figure 69. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=2.7V

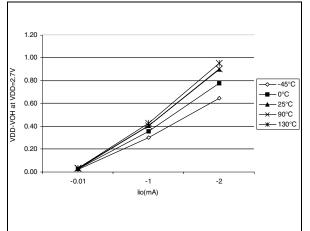

## Figure 70. Typical $V_{DD}$ - $V_{OH}$ at $V_{DD}$ =3V

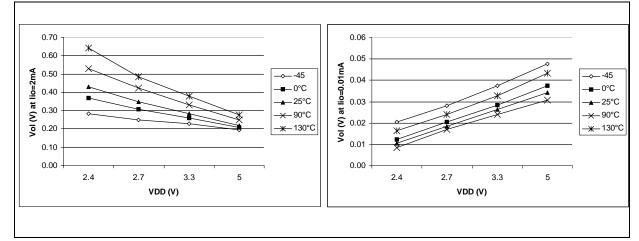

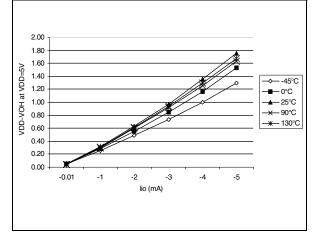

Figure 73. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard I/Os)

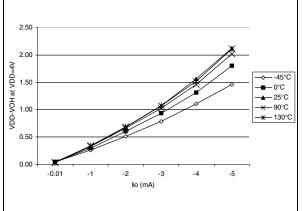

Figure 72. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=5V

## CONTROL PIN CHARACTERISTICS (Cont'd)

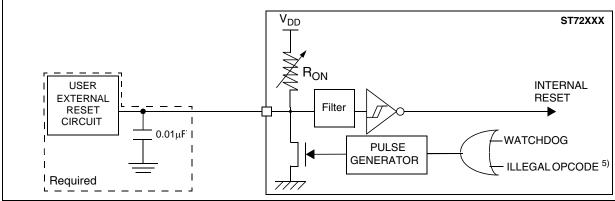

Figure 77. RESET pin protection when LVD is disabled.<sup>1)</sup>

#### Note 1:

57

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 13.9.1 on page 100. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 13.2.2 on page 82.

**Note 2:** When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a 1M $\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add 5µA to the power consumption of the MCU).

**Note 4:** Tips when using the LVD:

- 1. Check that all recommendations related to ICCCLK and reset circuit have been applied (see caution in Table 1 on page 7 and notes above)

- 2. Check that the power supply is properly decoupled (100nF + 10µF close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1MΩ pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality. <u>In most</u> cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor."

Note 5: See "Illegal Opcode Reset" on page 78. for more details on illegal opcode reset conditions

## ADC CHARACTERISTICS (Cont'd)

57

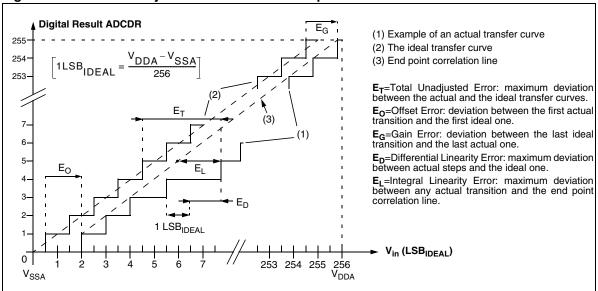

## Figure 84. ADC Accuracy Characteristics with Amplifier disabled

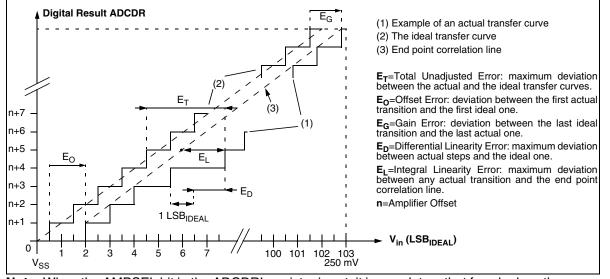

## Figure 85. ADC Accuracy Characteristics with Amplifier enabled

**Note:** When the AMPSEL bit in the ADCDRL register is set, it is mandatory that  $f_{ADC}$  be less than or equal to 2 MHz. (if  $f_{CPU}$ =8MHz. then SPEED=0, SLOW=1).

## Figure 89. Ordering information scheme

**\$7**

| Example:                                                    | ST7          | F      | LITES5       | Υ      | 0       | М       | 6     | TR       |

|-------------------------------------------------------------|--------------|--------|--------------|--------|---------|---------|-------|----------|

| Family                                                      |              |        |              |        |         |         |       |          |

| ST7 Microcontroller Family                                  |              |        |              |        |         |         |       |          |

| Mamanyahuna                                                 |              |        |              |        |         |         |       |          |

| Memory type                                                 |              |        |              |        |         |         |       |          |

| F: Flash<br>P: FASTROM                                      |              |        |              |        |         |         |       |          |

| P. FASTROM                                                  |              |        |              |        |         |         |       |          |

| Sub-family                                                  |              |        |              |        |         |         |       |          |

| LITES2, LITES5, LITE02, LITE0                               | 5 or LITE09  |        |              |        |         |         |       |          |

| , , ,                                                       |              |        |              |        |         |         |       |          |

| No. of pins                                                 |              |        |              |        |         |         |       |          |

| Y = 16                                                      |              |        |              |        |         |         |       |          |

| Memory size                                                 |              |        |              |        |         |         |       |          |

| 0 = 1K (LITESx versions) or 1.5                             | K (LITE0x ve | rsions | .)           |        |         |         |       |          |

| Destaux                                                     |              |        |              |        |         |         |       |          |

| Package                                                     |              |        |              |        |         |         |       |          |

| B = DIP<br>M = SO                                           |              |        |              |        |         |         |       |          |

| M = SO<br>U = QFN                                           |              |        |              |        |         |         |       |          |

|                                                             |              |        |              |        |         |         |       |          |

| Temperature range                                           |              |        |              |        |         |         |       |          |

| 6 = -40 °C to 85 °C                                         |              |        |              |        |         |         |       |          |

| Shipping Option —                                           |              |        |              |        |         |         |       |          |

| TR = Tape & Reel packing<br>Blank = Tube (DIP16 or SO16) of | or Tray (QFN | 20)    |              |        |         |         |       |          |

|                                                             |              |        |              |        |         |         |       |          |

| For a list of available options (e.                         | g. data EEPF | ROM,   | package) and | d orde | rable p | part nu | Imber | s or for |

further information on any aspect of this device, please contact the ST Sales Office nearest to you.

## **15.3 DEVELOPMENT TOOLS**

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and thirdparty tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete, affordable hardware/software tool packages that include features and samples to help you quickly start developing your application.

#### 15.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16KBytes of code.

The range of hardware tools includes full-featured **ST7-EMU3 series emulators**, cost effective **ST7-DVP3 series emulators** and the low-cost **RLink** in-circuit debugger/programmer. These tools are supported by the **ST7 Toolset** from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level lan-

guage debugger, editor, project manager and integrated programming interface.

#### 15.3.3 Programming tools

During the development cycle, the **ST7-DVP3** and **ST7-EMU3 series emulators** and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

## 15.3.4 Order Codes for Development and Programming Tools

Table 23 below lists the ordering codes for the ST7LITE0/ST7LITES development and programming tools. For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.

## 15.3.5 Order codes for ST7LITE0/ST7LITES development tools

## Table 23. Development tool order codes for the ST7LITE0/ST7LITES family

| MCU         | In-circuit Debu | igger, RLink Series <sup>1)</sup> | Emu                | lator      | Programming Tool          |               |  |

|-------------|-----------------|-----------------------------------|--------------------|------------|---------------------------|---------------|--|

| ST7FLITE02, | Starter Kit     | Starter Kit with                  |                    |            |                           | ST Socket     |  |

| ST7FLITE05, | without Demo    | Demo Board                        | DVP Series         | EMU Series | In-circuit<br>Programmer  | Boards and    |  |

| ST7FLITE09, | Board           | Demo Doard                        |                    |            | riogrammer                | EPBs          |  |

| ST7FLITES2, | STX-BI INK2)    | ST7FLITE-SK/RAIS <sup>2)</sup>    | ST7MDT10-          | ST7MDT10-  | STX-RLINK                 | ST7SB10-SU04) |  |

| ST7FLITES5  | OTX-HEINIK      |                                   | DVP3 <sup>3)</sup> | EMU3       | ST7-STICK <sup>4)5)</sup> | 0170010-000   |  |

Notes:

1. Available from ST or from Raisonance, www.raisonance.com

2. USB connection to PC

3. Includes connection kit for DIP16/SO16 only. See "How to order an EMU or DVP" in ST product and tool selection guide for connection kit ordering information

4. Add suffix /EU, /UK or /US for the power supply for your region

5. Parallel port connection to PC

## **16 KNOWN LIMITATIONS**

## **16.1 Execution of BTJX Instruction**

## Description

Executing a BTJx instruction jumps to a random address in the following conditions: the jump goes to a lower address (jump backward) and the test is performed on a data located at the address 00FFh.

## 16.2 In-Circuit Programming of devices previously programmed with Hardware Watchdog option

## Description

In-Circuit Programming of devices configured with Hardware Watchdog (WDGSW bit in option byte 1 programmed to 0) requires certain precautions (see below).

In-Circuit Programming uses ICC mode. In this mode, the Hardware Watchdog is not automatically deactivated as one might expect. As a consequence, internal resets are generated every 2 ms by the watchdog, thus preventing programming.

The device factory configuration is Software Watchdog so this issue is not seen with devices that are programmed for the first time. For the same reason, devices programmed by the user with the Software Watchdog option are not impacted.

The only devices impacted are those that have previously been programmed with the Hardware Watchdog option.

## Workaround

57/

Devices configured with Hardware Watchdog must be programmed using a specific programming mode that ignores the option byte settings. In this mode, an external clock, normally provided by the programming tool, has to be used. In ST tools, this mode is called "ICP OPTIONS DISABLED".

Sockets on ST programming tools (such as ST7MDT10-EPB) are controlled using "ICP OP-TIONS DISABLED" mode. Devices can therefore be reprogrammed by plugging them in the ST Programming Board socket, whatever the watchdog configuration.

When using third-party tools, please refer the manufacturer's documentation to check how to access specific programming modes. If a tool does not have a mode that ignores the option byte set-

tings, devices programmed with the Hardware watchdog option cannot be reprogrammed using this tool.

# 16.3 In-Circuit Debugging with Hardware Watchdog

In Circuit Debugging is impacted in the same way as In Circuit Programming by the activation of the hardware watchdog in ICC mode. Please refer to Section 16.2.

## 16.4 Recommendations when LVD is enabled

When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

# 16.5 Clearing Active Interrupts Outside Interrupt Routine

When an active interrupt request occurs at the same time as the related flag or interrupt mask is being cleared, the CC register may be corrupted.

## Concurrent interrupt context

The symptom does not occur when the interrupts are handled normally, i.e. when:

- The interrupt request is cleared (flag reset or interrupt mask) within its own interrupt routine

- The interrupt request is cleared (flag reset or interrupt mask) within any interrupt routine

- The interrupt request is cleared (flag reset or interrupt mask) in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request

Ex:

SIM

reset flag or interrupt mask

RIM