# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr               | Name                  | Bit 7                                                                      | Bit 6                                                                                 | Bit 5           | Bit 4           | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|-----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|-----------------|--------------|---------|---------|---------|----------------------|---------------------------------|

| Banl               | k7                    |                                                                            | •                                                                                     |                 | •               | •            | •       |         |         | •                    | •                               |

| 38Ch               | INLVLA                | _                                                                          | —                                                                                     | INLVLA5         | INLVLA4         | INLVLA3      | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111              | 11 1111                         |

| 38Dh               | INLVLB <sup>(3)</sup> | INLVLB7                                                                    | INLVLB6                                                                               | INLVLB5         | INLVLB4         | —            | —       | _       | —       | 1111                 | 1111                            |

| 38Eh               | INLVLC                | INLVLC7 <sup>(3)</sup>                                                     | INLVLC6(3)                                                                            | INLVLC5         | INLVLC4         | INLVLC3      | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111            | 1111 1111                       |

| 38Fh               | —                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | —                    | —                               |

| 390h               | —                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | _                    | —                               |

| 391h               | IOCAP                 | —                                                                          | —                                                                                     | IOCAP5          | IOCAP4          | IOCAP3       | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000              | 00 0000                         |

| 392h               | IOCAN                 | _                                                                          | —                                                                                     | IOCAN5          | IOCAN4          | IOCAN3       | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000              | 00 0000                         |

| 393h               | IOCAF                 | _                                                                          | —                                                                                     | IOCAF5          | IOCAF4          | IOCAF3       | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000              | 00 0000                         |

| 394h               | IOCBP <sup>(3)</sup>  | IOCBP7                                                                     | IOCBP6                                                                                | IOCBP5          | IOCBP4          | —            | —       | —       | —       | 0000                 | 0000                            |

| 395h               | IOCBN <sup>(3)</sup>  | IOCBN7                                                                     | IOCBN6                                                                                | IOCBN5          | IOCBN4          | —            | —       | —       | —       | 0000                 | 0000                            |

| 396h               | IOCBF <sup>(3)</sup>  | IOCBF7                                                                     | IOCBF6                                                                                | IOCBF5          | IOCBF4          | —            | —       | —       | _       | 0000                 | 0000                            |

| 397h               | IOCCP                 | IOCCP7 <sup>(3)</sup>                                                      | IOCCP6 <sup>(3)</sup>                                                                 | IOCCP5          | IOCCP4          | IOCCP3       | IOCCP2  | IIOCCP1 | IOCCP0  | 0000 0000            | 0000 0000                       |

| 398h               | IOCCN                 | IOCCN7 <sup>(3)</sup>                                                      | IOCCN6 <sup>(3)</sup>                                                                 | IOCCN5          | IOCCN4          | IOCCN3       | IOCCN2  | IIOCCN1 | IOCCN0  | 0000 0000            | 0000 0000                       |

| 399h               | IOCCF                 | IOCCF7 <sup>(3)</sup>                                                      | IOCCF6 <sup>(3)</sup>                                                                 | IOCCF5          | IOCCF4          | IOCCF3       | IOCCF2  | IIOCCF1 | IOCCF0  | 0000 0000            | 0000 0000                       |

| 39Ah               | _                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | _                    | _                               |

| 39Fh               |                       |                                                                            |                                                                                       |                 |                 |              |         |         |         |                      |                                 |

| Banl               | k 8                   |                                                                            |                                                                                       |                 |                 |              |         |         |         | •                    | T                               |

| 40Ch<br><br>414h   | _                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | -                    | -                               |

| 415h               | TMR4                  | Holding Regi                                                               | Holding Register for the Least Significant Byte of the 16-bit TMR4 Register xxxx xxxx |                 |                 |              |         |         |         |                      | uuuu uuuu                       |

| 416h               | PR4                   | Holding Register for the Most Significant Byte of the 16-bit TMR4 Register |                                                                                       |                 |                 |              |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| 417h               | T4CON                 | _                                                                          |                                                                                       | T4OUT           | PS<3:0>         |              | TMR4ON  | T4CKF   | PS<1:0> | -000 0000            | -000 0000                       |

| 418h<br><br>41Bh   | _                     | Unimplement                                                                | Unimplemented —                                                                       |                 |                 |              |         |         |         | _                    |                                 |

| 41Ch               | TMR6                  | Holding Regi                                                               | ster for the Lea                                                                      | ast Significant | Byte of the 16  | -bit TMR6 Re | gister  |         |         | XXXX XXXX            | uuuu uuuu                       |

| 41Dh               | PR6                   | Holding Regi                                                               | ster for the Mo                                                                       | st Significant  | Byte of the 16- | bit TMR6 Reg | ister   |         |         | XXXX XXXX            | uuuu uuuu                       |

| 41Eh               | T6CON                 | _                                                                          |                                                                                       | T6OUT           | PS<3:0>         |              | TMR6ON  | T6CKF   | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh               | —                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | —                    | —                               |

| Banl               | k 9                   |                                                                            |                                                                                       |                 |                 |              |         |         |         |                      |                                 |

| 48Ch<br>to<br>49Fh | _                     | Unimplement                                                                | Unimplemented                                                                         |                 |                 |              |         |         |         | _                    | _                               |

| Banl               | k 10                  |                                                                            |                                                                                       |                 |                 |              |         |         |         |                      |                                 |

| 50Ch               |                       |                                                                            |                                                                                       |                 |                 |              |         |         |         |                      |                                 |

| <br>510h           | —                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | _                    | -                               |

| 511h               | OPA1CON               | OPA1EN                                                                     | OPA1SP                                                                                | _               | OPA1UG          | _            | _       | OPA1P   | CH<1:0> | 00-000               | 00-000                          |

| 512h               | _                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | _                    | _                               |

| 514h               | 00400011              | 0.000                                                                      | 004000                                                                                |                 | 0040110         |              |         | 0.01157 | 011.4.6 |                      |                                 |

| 515h               | OPA2CON               | OPA2EN                                                                     | OPA2SP                                                                                | _               | OPA2UG          | —            | —       | OPA2P   | CH<1:0> | 00-000               | 00-000                          |

| 516h<br><br>51Fh   | —                     | Unimplement                                                                | ted                                                                                   |                 |                 |              |         |         |         | -                    | -                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-10:**

Note

Unimplemented, read as '1'. PIC16(L)F1704 only. 1:

2:

3:

PIC16(L)F1708 only. Unimplemented on PIC16LF1704/8. 4:

| TABLE J- | ABLE 3-3. SUMMART OF REGISTERS ASSOCIATED WITH RESETS |        |            |       |       |       |        |        |                     |

|----------|-------------------------------------------------------|--------|------------|-------|-------|-------|--------|--------|---------------------|

| Name     | Bit 7                                                 | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

| BORCON   | SBOREN                                                | BORFS  | _          |       | —     |       |        | BORRDY | 56                  |

| PCON     | STKOVF                                                | STKUNF | _          | RWDT  | RMCLR | RI    | POR    | BOR    | 60                  |

| STATUS   | _                                                     | _      | _          | TO    | PD    | Z     | DC     | С      | 23                  |

| WDTCON   | _                                                     |        | WDTPS<4:0> |       |       |       | SWDTEN | 100    |                     |

TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

### 6.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC connect to a multiplexer (see Figure 6-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

#### 6.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the SPLLEN option will not be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

#### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### MEMORY MODIFY FLOWCHART Start Modify Operation **Read Operation** Figure 10-1 An image of the entire row read must be stored in RAM Modify Image The words to be modified are changed in the RAM image Erase Operation Figure 10-4 Write Operation use RAM image Figure 10-6 End Modify Operation

**FLASH PROGRAM**

**FIGURE 10-7:**

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

#### 11.6 **Register Definitions: PORTC**

#### **REGISTER 11-17: PORTC: PORTC REGISTER**

| R/W-x/u                                 | R/W-x/u            | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|---------|

| RC7 <sup>(2)</sup>                      | RC6 <sup>(2)</sup> | RC5     | RC4                                                   | RC3     | RC2     | RC1     | RC0     |

| bit 7                                   |                    |         |                                                       |         |         |         | bit 0   |

| Legend:                                 |                    |         |                                                       |         |         |         |         |

| R = Readable bit W = Writable bit       |                    | it      | U = Unimplemented bit, read as '0'                    |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown |                    | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |

| '1' = Bit is set '0' = Bit is clear     |                    |         | ed                                                    |         |         |         |         |

RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1, 2)</sup> bit 7-0 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

2: RC<7:6> are available on PIC16(L)F1708 only.

#### **REGISTER 11-18: TRISC: PORTC TRI-STATE REGISTER**

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

TRISC<7:0>: PORTC Tri-State Control bits(1) 1 = PORTC pin configured as an input (tri-stated)

bit 7-0

0 = PORTC pin configured as an output

Note 1: TRISC<7:6> are available on PIC16(L)F1708 only.

#### **REGISTER 11-19: LATC: PORTC DATA LATCH REGISTER**

| R/W-x/u                                 | R/W-x/u              | R/W-x/u | R/W-x/u                            | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|----------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|---------|--|

| LATC7 <sup>(1)</sup>                    | LATC6 <sup>(1)</sup> | LATC5   | LATC4                              | LATC3                                                 | LATC2   | LATC1   | LATC0   |  |

| bit 7                                   |                      |         |                                    |                                                       |         | •       | bit 0   |  |

|                                         |                      |         |                                    |                                                       |         |         |         |  |

| Legend:                                 |                      |         |                                    |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit       |                      | t       | U = Unimplemented bit, read as '0' |                                                       |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                      |         | wn                                 | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

'1' = Bit is set '0' = Bit is cleared

LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup> bit 7-0

Note 1: LATC<7:6> are available on PIC16(L)F1708 only.

### 17.1 **PWMx Pin Configuration**

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

#### 17.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

Note: The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

**Note:** The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

#### 17.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

#### 17.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 17-1.

#### EQUATION 17-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$

(TMR2 Prescale Value)

```

Note: Tosc = 1/Fosc

```

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

#### 17.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 17-2 is used to calculate the PWM pulse width.

Equation 17-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 17-2: PULSE WIDTH

$Pulse Width = (PWMxDCH:PWMxDCL<7:6>) \bullet$

Tosc • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

### EQUATION 17-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/FOSC, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

| R/W-0/0          | R/W-0/0                                                                                                                                                                            | R/W-0/0                                | R/W-0/0         | R/W-0/0           | R/W-0/0           | R/W-0/0   | R/W-0/0    |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|-------------------|-------------------|-----------|------------|--|--|--|

| GxSDATD          | GxSDATC                                                                                                                                                                            | GxSDATB                                | GxSDATA         | GxSTRD            | GxSTRC            | GxSTRB    | GxSTRA     |  |  |  |

| bit 7            | •                                                                                                                                                                                  |                                        |                 | •                 | •                 |           | bit (      |  |  |  |

|                  |                                                                                                                                                                                    |                                        |                 |                   |                   |           |            |  |  |  |

| Legend:          | . 1. 1                                                                                                                                                                             |                                        | 1.11            |                   | (                 |           |            |  |  |  |

| R = Readable     |                                                                                                                                                                                    | W = Writable                           |                 | •                 | ented bit, read   |           |            |  |  |  |

| u = Bit is unc   | •                                                                                                                                                                                  | x = Bit is unkr                        |                 |                   | POR and BOF       |           | ner Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                    | '0' = Bit is clea                      | ared            | q = Value depe    | ends on condition | on        |            |  |  |  |

| bit 7            | GXSDATD (                                                                                                                                                                          | COGxD Static C                         | )utnut Data hit |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | static data is hi                      | •               |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | static data is lo                      | 0               |                   |                   |           |            |  |  |  |

| bit 6            | GxSDATC: (                                                                                                                                                                         | COGxC Static C                         | Output Data bit |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | static data is hi                      | 0               |                   |                   |           |            |  |  |  |

|                  | 0 = COGxC                                                                                                                                                                          | static data is lo                      | W               |                   |                   |           |            |  |  |  |

| bit 5            | GxSDATB: (                                                                                                                                                                         | COGxB Static C                         | Output Data bit |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | static data is hi                      | 0               |                   |                   |           |            |  |  |  |

| L *1 - A         |                                                                                                                                                                                    | static data is lo                      |                 |                   |                   |           |            |  |  |  |

| bit 4            |                                                                                                                                                                                    | OGxA Static C                          |                 |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | static data is hi<br>static data is lo | 0               |                   |                   |           |            |  |  |  |

| bit 3            |                                                                                                                                                                                    | OGxD Steering                          |                 |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | •                                      |                 | orm with polarity | control from G    | xPOLD bit |            |  |  |  |

|                  |                                                                                                                                                                                    |                                        |                 | letermined by th  |                   |           |            |  |  |  |

| bit 2            | GxSTRC: CO                                                                                                                                                                         | OGxC Steering                          | Control bit     |                   |                   |           |            |  |  |  |

|                  | 1 = COGxC output has the COGxC waveform with polarity control from GxPOLC bit                                                                                                      |                                        |                 |                   |                   |           |            |  |  |  |

|                  |                                                                                                                                                                                    | •                                      |                 | letermined by th  | ie GxSDATC bi     | t         |            |  |  |  |

| bit 1            |                                                                                                                                                                                    | OGxB Steering Control bit              |                 |                   |                   |           |            |  |  |  |

|                  | <ul> <li>1 = COGxB output has the COGxB waveform with polarity control from GxPOLB bit</li> <li>0 = COGxB output is the static data level determined by the GxSDATB bit</li> </ul> |                                        |                 |                   |                   |           |            |  |  |  |

| <b>h</b> # 0     |                                                                                                                                                                                    |                                        |                 | letermined by tr  | IE GXSDATB DI     | L         |            |  |  |  |

| bit 0            |                                                                                                                                                                                    | OGxA Steering                          |                 | m with polority   | control from C    |           |            |  |  |  |

|                  | $\perp = COGXA$                                                                                                                                                                    | output has the                         | UUGXA waveld    | orm with polarity | CONTROL ITOM G    |           |            |  |  |  |

#### REGISTER 18-9: COGxSTR: COG STEERING CONTROL REGISTER 1

#### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

#### TABLE 19-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- Gate 3: CLCxGLS2 (Register 19-9)

- Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

### 21.1 OPA Module Performance

Common AC and DC performance specifications for the OPA module:

- Common Mode Voltage Range

- Leakage Current

- Input Offset Voltage

- Open Loop Gain

- · Gain Bandwidth Product

**Common mode voltage range** is the specified voltage range for the OPA+ and OPA- inputs, for which the OPA module will perform to within its specifications. The OPA module is designed to operate with input voltages between Vss and VDD. Behavior for Common mode voltages greater than VDD, or below Vss, are not guaranteed.

**Leakage current** is a measure of the small source or sink currents on the OPA+ and OPA- inputs. To minimize the effect of leakage currents, the effective impedances connected to the OPA+ and OPA- inputs should be kept as small as possible and equal.

**Input offset voltage** is a measure of the voltage difference between the OPA+ and OPA- inputs in a closed loop circuit with the OPA in its linear region. The offset voltage will appear as a DC offset in the output equal to the input offset voltage, multiplied by the gain of the circuit. The input offset voltage is also affected by the Common mode voltage. The OPA is factory calibrated to minimize the input offset voltage of the module.

**Open loop gain** is the ratio of the output voltage to the differential input voltage, (OPA+) - (OPA-). The gain is greatest at DC and falls off with frequency.

**Gain Bandwidth Product** or GBWP is the frequency at which the open loop gain falls off to 0 dB.

#### 21.1.1 OPA Module Control

The OPA module is enabled by setting the OPAxEN bit of the OPAxCON register. When enabled, the OPA forces the output driver of OPAxOUT pin into tri-state to prevent contention between the driver and the OPA output.

Note: When the OPA module is enabled, the OPAxOUT pin is driven by the op amp output, not by the PORT digital driver. Refer to Table 32-17: Operational Amplifier (OPA) for the op amp output drive capability.

#### 21.1.2 UNITY GAIN MODE

The OPAxUG bit of the OPAxCON register selects the Unity Gain mode. When unity gain is selected, the OPA output is connected to the inverting input and the OPAxIN pin is relinquished, releasing the pin for general purpose input and output.

#### 21.2 Effects of Reset

A device Reset forces all registers to their Reset state. This disables the OPA module.

#### 28.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any SSPBUF register write to the during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSPSTAT register indicates the various Status conditions.

#### 28.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 28-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 28-6, Figure 28-8, Figure 28-9 and Figure 28-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 28-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

Note: In Master mode the clock signal output to the SCK pin is also the clock signal input to the peripheral. The pin selected for output with the RxyPPS register must also be selected as the peripheral input with the SSPCLKPPS register.

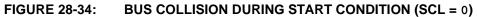

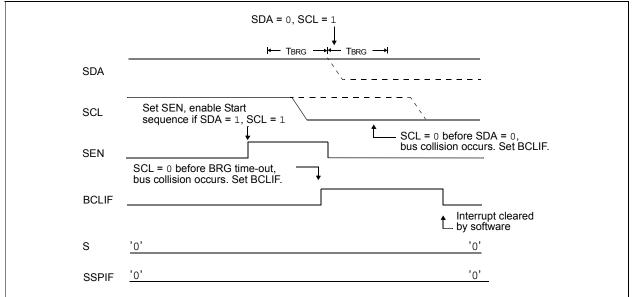

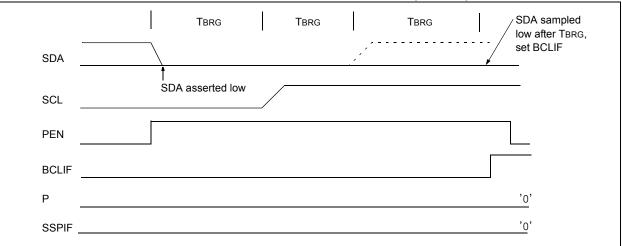

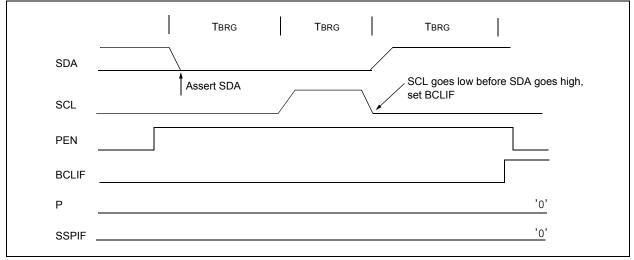

#### 28.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 28-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 28-39).

#### FIGURE 28-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 28-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

. .

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                          |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                      |

|------------------|------------------------------------------------------|

| Syntax:          | [label] OPTION                                       |

| Operands:        | None                                                 |

| Operation:       | $(W) \rightarrow OPTION\_REG$                        |

| Status Affected: | None                                                 |

| Description:     | Move data from W register to<br>OPTION_REG register. |

| Words:           | 1                                                    |

| Cycles:          | 1                                                    |

| Example:         | OPTION                                               |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F  |

|                  | After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F   |

| RESET            | Software Reset                                                                      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RESET                                                                       |  |  |  |  |

| Operands:        | None                                                                                |  |  |  |  |

| Operation:       | Execute a device Reset. Resets the $\overrightarrow{RI}$ flag of the PCON register. |  |  |  |  |

| Status Affected: | None                                                                                |  |  |  |  |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software.      |  |  |  |  |

| PIC16LF1 | 1704/8          | Standard Operating Conditions (unless otherwise stated) |       |      |       |     |                             |  |

|----------|-----------------|---------------------------------------------------------|-------|------|-------|-----|-----------------------------|--|

| PIC16F17 | /04/8           | Standard Operating Conditions (unless otherwise stated) |       |      |       |     |                             |  |

| Param.   | Device          | Min                                                     | True  | Max  |       |     | Conditions                  |  |

| No.      | Characteristics | Min.                                                    | Тур.† | Max. | Units | Vdd | Note                        |  |

| D020     |                 | -                                                       | 2.3   | 3.0  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | —                                                       | 2.8   | 3.5  | mA    | 3.6 | HFINTOSC mode (Note 5)      |  |

| D020     |                 | —                                                       | 2.4   | 3.1  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | —                                                       | 2.6   | 3.4  | mA    | 5.0 | HFINTOSC mode (Note 5)      |  |

| D022     |                 | —                                                       | 2     | 3.0  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | —                                                       | 2.6   | 3.5  | mA    | 3.6 | HS Oscillator mode (Note 5) |  |

| D022     |                 | _                                                       | 2.1   | 3.0  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | _                                                       | 3     | 3.5  | mA    | 5.0 | HS Oscillator mode (Note 5) |  |

### TABLE 32-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 8 MHz clock with 4x PLL enabled.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

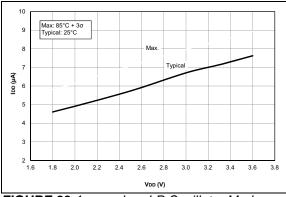

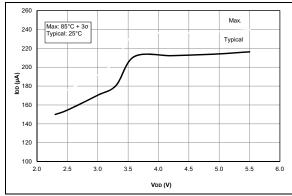

FIGURE 33-1: IDD, LP Oscillator Mode, Fosc = 32 kHz. PIC16LF1704/8 Only.

FIGURE 33-2: IDD, LP Oscillator Mode, Fosc = 32 kHz. PIC16F1704/8 Only.

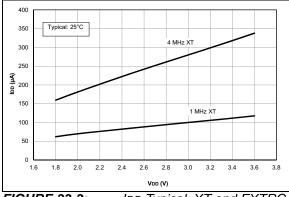

FIGURE 33-3: IDD Typical, XT and EXTRC Oscillator. PIC16LF1704/8 Only.

FIGURE 33-4: IDD Maximum, XT and EXTRC Oscillator. PIC16LF1704/8 Only.

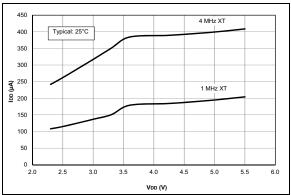

FIGURE 33-5: IDD Typical, XT and EXTRC Oscillator. PIC16F1704/8 Only.

FIGURE 33-6: IDD Maximum, XT and EXTRC Oscillator. PIC16F1704/8 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

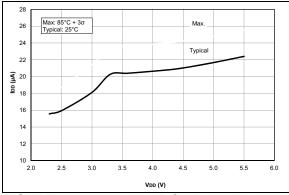

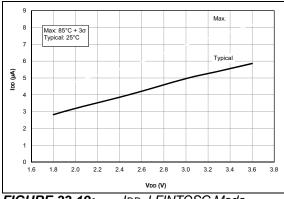

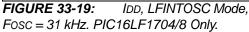

FIGURE 33-20: IDD, LFINTOSC Mode, Fosc = 31 kHz. PIC16F1704/8 Only.

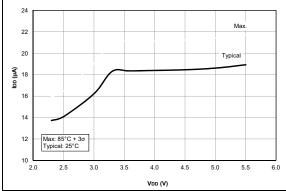

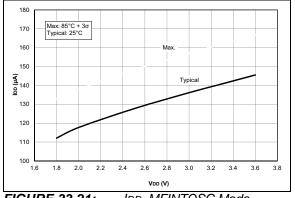

FIGURE 33-21: IDD, MFINTOSC Mode, Fosc = 500 kHz. PIC16LF1704/8 Only.

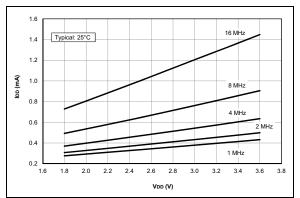

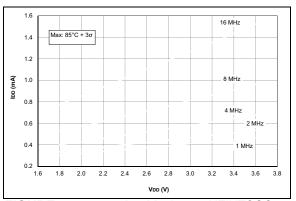

FIGURE 33-22: IDD, MFINTOSC Mode, Fosc = 500 kHz. PIC16F1704/8 Only.

FIGURE 33-23: IDD Typical, HFINTOSC Mode. PIC16LF1704/8 Only.

FIGURE 33-24: IDD Maximum, HFINTOSC Mode. PIC16LF1704/8 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

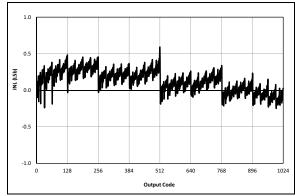

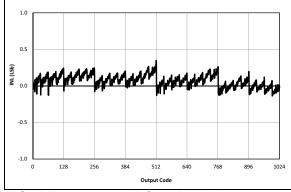

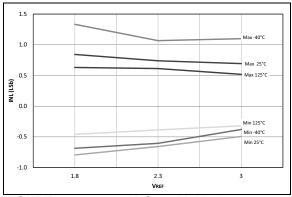

**FIGURE 33-79:** ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 1 us, 25°C.

**FIGURE 33-80:** ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 4 us, 25°C.

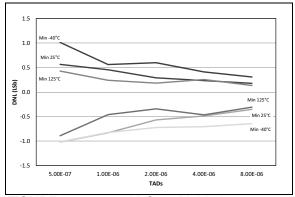

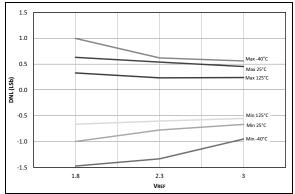

FIGURE 33-81: ADC 10-Bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

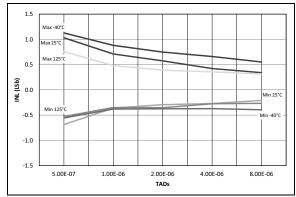

FIGURE 33-82: ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

FIGURE 33-83: ADC 10-Bit Mode, Single-Ended DNL, VDD = 3.0V, TAD = 1 us.

FIGURE 33-84: ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 1 us.

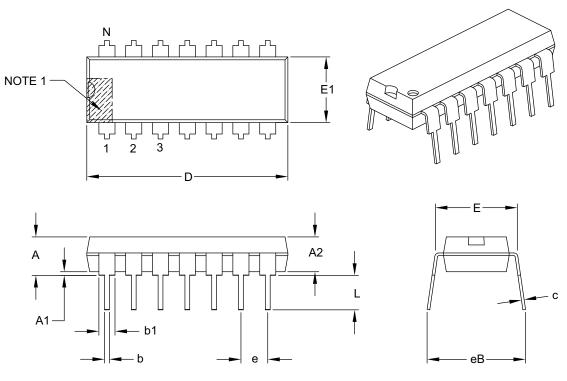

#### 35.2 Package Details

The following sections give the technical details of the packages.

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units       |          |      | INCHES |  |  |

|----------------------------|-------------|----------|------|--------|--|--|

| Dimens                     | sion Limits | MIN      | NOM  | MAX    |  |  |

| Number of Pins             | Ν           | 14       |      |        |  |  |

| Pitch                      | е           | .100 BSC |      |        |  |  |

| Top to Seating Plane       | Α           | -        | -    | .210   |  |  |

| Molded Package Thickness   | A2          | .115     | .130 | .195   |  |  |

| Base to Seating Plane      | A1          | .015     | -    | _      |  |  |

| Shoulder to Shoulder Width | E           | .290     | .310 | .325   |  |  |

| Molded Package Width       | E1          | .240     | .250 | .280   |  |  |

| Overall Length             | D           | .735     | .750 | .775   |  |  |

| Tip to Seating Plane       | L           | .115     | .130 | .150   |  |  |

| Lead Thickness             | С           | .008     | .010 | .015   |  |  |

| Upper Lead Width           | b1          | .045     | .060 | .070   |  |  |

| Lower Lead Width           | b           | .014     | .018 | .022   |  |  |

| Overall Row Spacing §      | eB          | _        | -    | .430   |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B