Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-e-sl |

TABLE 1-3: PIC16(L)F1708 PIN OUT DESCRIPTION (CONTINUED)

| Name               | Function           | Input<br>Type    | Output<br>Type | Description                                          |

|--------------------|--------------------|------------------|----------------|------------------------------------------------------|

| Vss                | Vss                | Power            | _              | Ground reference.                                    |

| OUT <sup>(2)</sup> | C1OUT              | _                | CMOS           | Comparator output.                                   |

|                    | C2OUT              | _                | CMOS           | Comparator output.                                   |

|                    | CCP1               | _                | CMOS           | Capture/Compare/PWM1 output.                         |

|                    | CCP2               | _                | CMOS           | Capture/Compare/PWM2 output.                         |

|                    | PWM3OUT            | _                | CMOS           | PWM3 output.                                         |

|                    | PWM4OUT            | _                | CMOS           | PWM4 output.                                         |

|                    | COGA               | _                | CMOS           | Complementary Output Generator Output A.             |

|                    | COGB               | _                | CMOS           | Complementary Output Generator Output B.             |

|                    | COGC               | _                | CMOS           | Complementary Output Generator Output C.             |

|                    | COGD               | _                | CMOS           | Complementary Output Generator Output D.             |

|                    | SDA <sup>(3)</sup> | _                | OD             | I <sup>2</sup> C data input/output.                  |

|                    | SDO                | _                | CMOS           | SPI data output.                                     |

|                    | SCK                | _                | CMOS           | SPI clock output.                                    |

|                    | SCL <sup>(3)</sup> | I <sup>2</sup> C | OD             | I <sup>2</sup> C clock output.                       |

|                    | TX/CK              | _                | CMOS           | USART asynchronous TX data/synchronous clock output. |

|                    | DT                 |                  | CMOS           | USART synchronous data output.                       |

|                    | CLC10UT            | _                | CMOS           | Configurable Logic Cell 1 source output.             |

|                    | CLC2OUT            | _                | CMOS           | Configurable Logic Cell 2 source output.             |

|                    | CLC3OUT            | _                | CMOS           | Configurable Logic Cell 3 source output.             |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>2:</sup> All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-3.

# 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-9 can be addressed from any Bank.

TABLE 3-9: CORE FUNCTION REGISTERS SUMMARY

| Addr            | Name   | Bit 7      Bit 6      Bit 5      Bit 4      Bit 3      Bit 2      Bit 1      Bit 0                     |                                                          |               |              |             |               |        |       | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|--------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|---------------------------|

| Bank 0-31       |        |                                                                                                        |                                                          |               |              |             |               |        |       |                      |                           |

| x00h or<br>x80h | INDF0  | Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register) |                                                          |               |              |             |               |        |       |                      | uuuu uuuu                 |

| x01h or<br>x81h | INDF1  |                                                                                                        | this location ical register)                             |               | nts of FSR1H | /FSR1L to a | ddress data r | memory |       | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h | PCL    | Program Co                                                                                             | ounter (PC)                                              | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS | _                                                                                                      | _                                                        | 1             | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L  | Indirect Dat                                                                                           | ta Memory A                                              | ddress 0 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H  | Indirect Dat                                                                                           | ta Memory A                                              | ddress 0 Hiç  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h | FSR1L  | Indirect Dat                                                                                           | ta Memory A                                              | ddress 1 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h | FSR1H  | Indirect Dat                                                                                           | ta Memory A                                              | ddress 1 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR    | _                                                                                                      |                                                          | 1             | BSR4         | BSR3        | BSR2          | BSR1   | BSR0  | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG   | Working Re                                                                                             | Working Register                                         |               |              |             |               |        |       |                      | uuuu uuuu                 |

| x0Ahor<br>x8Ah  | PCLATH | _                                                                                                      | Write Buffer for the upper 7 bits of the Program Counter |               |              |             |               |        |       |                      | -000 0000                 |

| x0Bhor<br>x8Bh  | INTCON | GIE                                                                                                    | PEIE                                                     | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

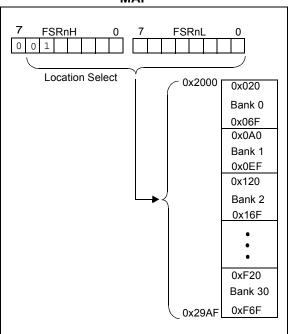

#### 3.7.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

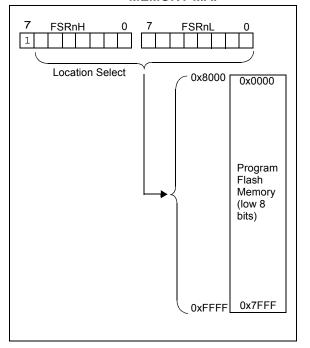

### 3.7.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the Program Flash Memory cannot be accomplished via the FSR/INDF interface. All instructions that access Program Flash Memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

# 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

# 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 0  | х  | Illegal, TO is set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | х  | 0  | Illegal, PD is set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu 0uuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 0uuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 1uuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 0uuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | 1u uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register on Page |

|--------|--------|-------|-------|-------|-----------|-------|-------|--------|------------------|

| OSCCON | SPLLEN |       | IRCF  | <3:0> |           | _     | SCS-  | <1:0>  | 77               |

| STATUS | _      | _     | _     | TO    | PD        | Z     | DC    | С      | 23               |

| WDTCON | _      | _     |       | V     | NDTPS<4:0 | >     |       | SWDTEN | 100              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|-----------|---------|---------|------------------|

| CONFIG1 | 13:8 | _       |         | FCMEN    | IESO     | CLKOUTEN | BORE      | N<1:0>  | _       | 49               |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   | FOSC<2:0> |         | >       | 49               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|-------|--------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELA     | _     | _      | _       | ANSA4   | _       | ANSA2   | ANSA1   | ANSA0   | 122              |

| INLVLA     | _     | _      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124              |

| LATA       | _     | _      | LATA5   | LATA4   | _       | LATA2   | LATA1   | LATA0   | 122              |

| ODCONA     | _     | _      | ODA5    | ODA4    | _       | ODA2    | ODA1    | ODA0    | 123              |

| OPTION_REG | WPUEN | INTEDG | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 244              |

| PORTA      | _     | _      | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 121              |

| SLRCONA    | _     | _      | SLRA5   | SLRA4   | _       | SLRA2   | SLRA1   | SLRA0   | 124              |

| TRISA      | _     | _      | TRISA5  | TRISA4  | (1)     | TRISA2  | TRISA1  | TRISA0  | 121              |

| WPUA       | _     | _      | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 123              |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

TABLE 11-3: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|-----------|---------|---------|------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BORE      | N<1:0>  | _       | 49               |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | FOSC<2:0> |         |         | 49               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# 11.3 PORTB Registers (PIC16(L)F1708 only)

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 32-4: I/O Ports for more information on threshold levels.

Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 11.3.5 ANALOG CONTROL

Note:

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

# 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions may continue to control the pin when it is in Analog mode.

## 11.4 Register Definitions: PORTB

## **REGISTER 11-9: PORTB: PORTB REGISTER**

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| RB7     | RB6     | RB5     | RB4     | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 RB<7:4>: PORTB General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

bit 3-0 **Unimplemented:** Read as '0'

Note 1: Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

### **REGISTER 11-10: TRISB: PORTB TRI-STATE REGISTER**

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | _   |     | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 TRISB<7:4>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

bit 3-0 **Unimplemented:** Read as '0'

#### REGISTER 11-11: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| LATB7   | LATB6   | LATB5   | LATB4   | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 LATB<7:4>: PORTB Output Latch Value bits<sup>(1)</sup>

bit 3-0 **Unimplemented:** Read as '0'

Note 1: Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 18-4: COGXRSIM: COG RISING EVENT SOURCE INPUT MODE REGISTER

| U-0   | R/W-0/0 |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | GxRSIM6 | GxRSIM5 | GxRSIM4 | GxRSIM3 | GxRSIM2 | GxRSIM1 | GxRSIM0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

bit 7 Unimplemented: Read as '0'

bit 6 GxRSIM6: COGx Rising Event Input Source 6 Mode bit

GxRIS6 = 1:

1 = PWM3 output low-to-high transition will cause a rising event after rising event phase delay

0 = PWM3 output high level will cause an immediate rising event

GxRIS6 = 0:

PWM3 output has no effect on rising event

bit 5 GxRSIM5: COGx Rising Event Input Source 5 Mode bit

GxRIS5 = 1:

1 = CCP2 output low-to-high transition will cause a rising event after rising event phase delay

0 = CCP2 output high level will cause an immediate rising event

GxRIS5 = 0

CCP2 output has no effect on rising event

bit 4 GxRSIM4: COGx Rising Event Input Source 4 Mode bit

GxRIS4 = 1:

1 = CCP1 low-to-high transition will cause a rising event after rising event phase delay

0 = CCP1 high level will cause an immediate rising event

GxRIS4 = 0:

CCP1 has no effect on rising event

bit 3 GxRSIM3: COGx Rising Event Input Source 3 Mode bit

GxRIS3 = 1:

1 = CLC1 output low-to-high transition will cause a rising event after rising event phase delay

0 = CLC1 output high level will cause an immediate rising event

GxRIS3 = 0:

CLC1 output has no effect on rising event

bit 2 GxRSIM2: COGx Rising Event Input Source 2 Mode bit

GxRIS2 = 1:

1 = Comparator 2 low-to-high transition will cause a rising event after rising event phase delay

0 = Comparator 2 high level will cause an immediate rising event

GxRIS2 = 0:

Comparator 2 has no effect on rising event

bit 1 GxRSIM1: COGx Rising Event Input Source 1 Mode bit

GxRIS1 = 1:

1 = Comparator 1 low-to-high transition will cause a rising event after rising event phase delay

0 = Comparator 1 high level will cause an immediate rising event

GxRIS1 = 0:

Comparator 1 has no effect on rising event

bit 0 GxRSIM0: COGx Rising Event Input Source 0 Mode bit

GxRIS0 = 1:

1 = Pin selected with COGxPPS control low-to-high transition will cause a rising event after rising event phase delay

0 = Pin selected with COGxPPS control high level will cause an immediate rising event

GxRIS0 = 0:

Pin selected with COGxPPS control has no effect on rising event

#### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

**Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

**TABLE 19-2: DATA GATING LOGIC**

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- Gate 3: CLCxGLS2 (Register 19-9)

- · Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- · AND-OR

- OR-XOR

- AND

- S-R Latch

- · D Flip-Flop with Set and Reset

- · D Flip-Flop with Reset

- · J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

# 19.6 Register Definitions: CLC Control

# REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 |

|---------|-----|--------|---------|---------|---------|--------------|---------|

| LCxEN   | _   | LCxOUT | LCxINTP | LCxINTN |         | LCxMODE<2:0> |         |

| bit 7   |     |        |         |         |         |              | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | LCxEN: Configurable Logic Cell Enable bit                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Configurable logic cell is enabled and mixing input signals</li><li>0 = Configurable logic cell is disabled and has logic zero output</li></ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 5   | LCxOUT: Configurable Logic Cell Data Output bit                                                                                                             |

|         | Read-only: logic cell output data, after LCxPOL; sampled from lcx_out wire.                                                                                 |

| bit 4   | LCxINTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit                                                                                   |

|         | <ul><li>1 = CLCxIF will be set when a rising edge occurs on lcx_out</li><li>0 = CLCxIF will not be set</li></ul>                                            |

| bit 3   | LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit                                                                                   |

|         | <ul><li>1 = CLCxIF will be set when a falling edge occurs on lcx_out</li><li>0 = CLCxIF will not be set</li></ul>                                           |

| bit 2-0 | LCxMODE<2:0>: Configurable Logic Cell Functional Mode bits                                                                                                  |

|         | 111 = Cell is 1-input transparent latch with S and R                                                                                                        |

|         | 110 = Cell is J-K flip-flop with R                                                                                                                          |

|         | 101 = Cell is 2-input D flip-flop with R<br>100 = Cell is 1-input D flip-flop with S and R                                                                  |

|         | 011 = Cell is S-R latch                                                                                                                                     |

|         | 010 = Cell is 4-input AND                                                                                                                                   |

|         | 001 = Cell is OR-XOR                                                                                                                                        |

|         | 000 = Cell is AND-OR                                                                                                                                        |

#### REGISTER 19-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | U-0 | R/W-x/u  | R/W-x/u  | R/W-x/u  | R/W-x/u  |

|---------|-----|-----|-----|----------|----------|----------|----------|

| LCxPOL  | _   | _   | _   | LCxG4POL | LCxG3POL | LCxG2POL | LCxG1POL |

| bit 7   | •   |     |     | •        |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 LCxPOL: LCOUT Polarity Control bit

1 = The output of the logic cell is inverted0 = The output of the logic cell is not inverted

bit 6-4 Unimplemented: Read as '0'

bit 3 LCxG4POL: Gate 4 Output Polarity Control bit

1 = The output of gate 4 is inverted when applied to the logic cell

0 = The output of gate 4 is not inverted

bit 2 LCxG3POL: Gate 3 Output Polarity Control bit

1 = The output of gate 3 is inverted when applied to the logic cell

0 = The output of gate 3 is not inverted

bit 1 LCxG2POL: Gate 2 Output Polarity Control bit

1 = The output of gate 2 is inverted when applied to the logic cell

0 = The output of gate 2 is not inverted

bit 0 LCxG1POL: Gate 1 Output Polarity Control bit

1 = The output of gate 1 is inverted when applied to the logic cell

0 = The output of gate 1 is not inverted

## **REGISTER 19-11: CLCDATA: CLC DATA OUTPUT**

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |     | •       |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0'         |

|---------|------------------------------------|

| bit 2   | MLC3OUT: Mirror copy of LC3OUT bit |

| bit 1   | MLC2OUT: Mirror copy of LC2OUT bit |

| bit 0   | MLC1OUT: Mirror copy of LC1OUT bit |

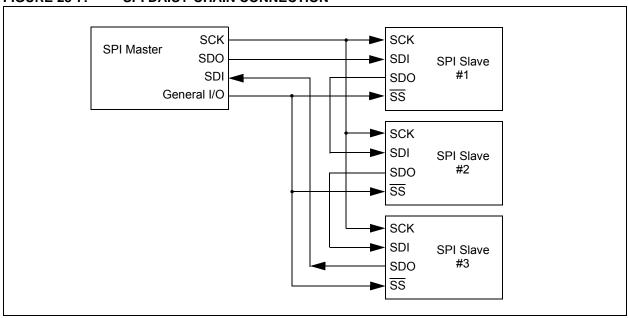

### 28.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- · Serial Data In (SDI)

- Slave Select (SS)

Figure 28-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 28-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 28-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data

- Master sends useful data and slave sends useful data

- Master sends dummy data and slave sends useful data

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

FIGURE 28-7: SPI DAISY-CHAIN CONNECTION

# REGISTER 28-5: SSP1MSK: SSP MASK REGISTER

| R/W-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|--|

| MSK<7:0> |         |         |         |         |         |         |         |  |  |

| bit 7    |         |         |         |         |         |         |         |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-1 MSK<7:1>: Mask bits

1 = The received address bit n is compared to SSPADD<n> to detect I<sup>2</sup>C address match

0 = The received address bit n is not used to detect I<sup>2</sup>C address match

bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address

$I^{2}C$  Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):

1 = The received address bit 0 is compared to SSPADD<0> to detect  $I^2C$  address match

0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

# REGISTER 28-6: SSP1ADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|

| ADD<7:0> |         |         |         |         |         |         |         |  |

| bit 7    |         |         |         |         |         |         | bit 0   |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits

SCL pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

### 10-Bit Slave mode - Most Significant Address Byte:

bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit

pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits

are compared by hardware and are not affected by the value in this register.

bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

bit 0 **Not used:** Unused in this mode. Bit state is a "don't care".

#### 10-Bit Slave mode - Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

## 7-Bit Slave mode:

bit 7-1 ADD<7:1>: 7-bit address

bit 0 **Not used:** Unused in this mode. Bit state is a "don't care".

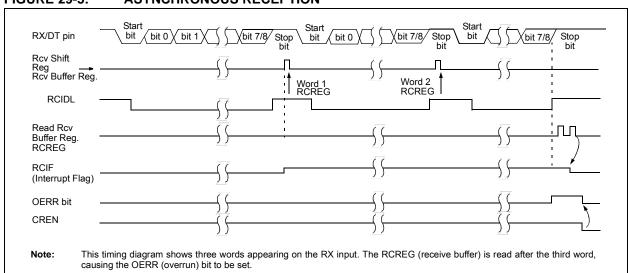

### 29.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 29.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit.

The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 29.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 29.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit.

The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

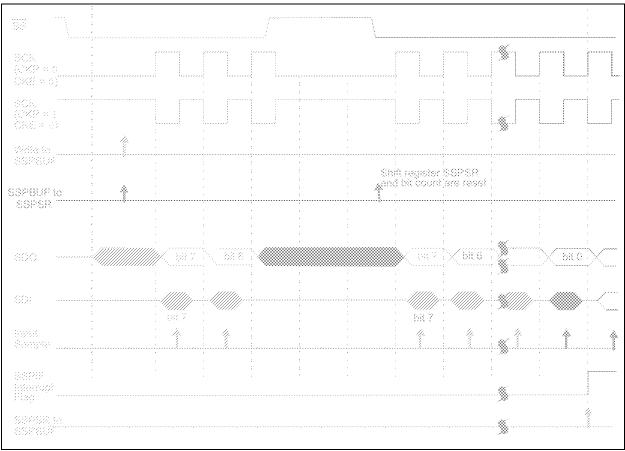

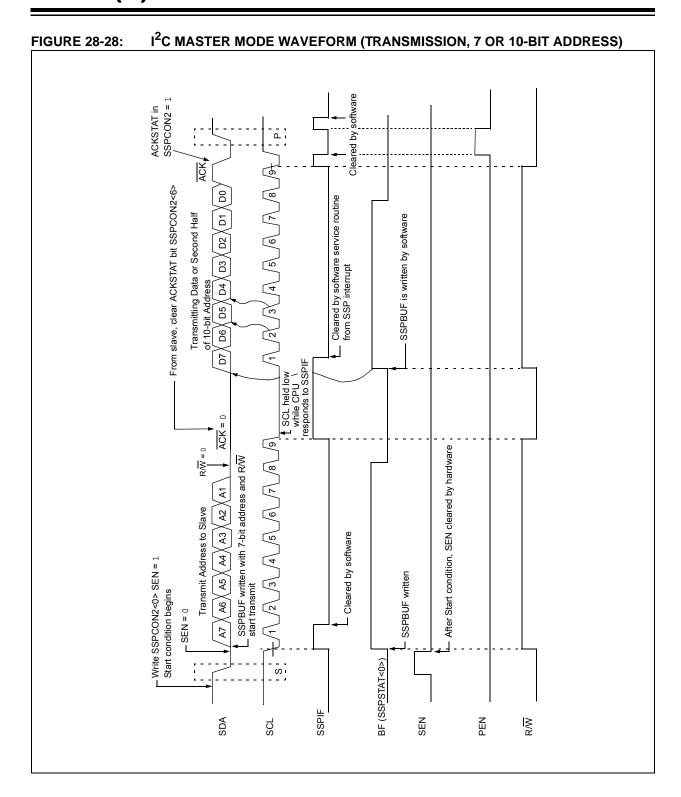

## FIGURE 29-5: ASYNCHRONOUS RECEPTION

**Note:** Unless otherwise noted, Vin = 5V, Fosc = 500 kHz,  $Cin = 0.1 \mu F$ , TA = 25°C.

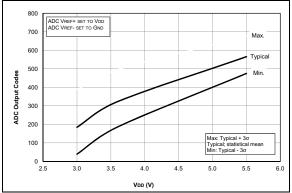

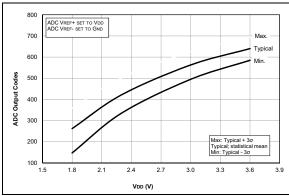

**FIGURE 33-85:** Temperature Indicator Initial Offset, High Range, Temp. = 20°C, PIC16F1704/8 Only.

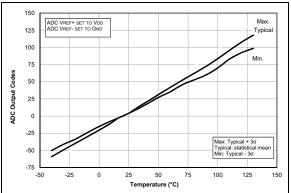

**FIGURE 33-86:** Temperature Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16F1704/8 Only.

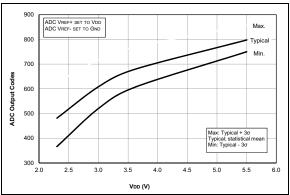

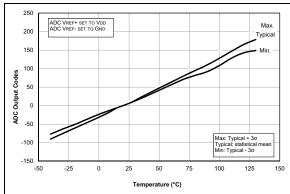

FIGURE 33-87: Temperature Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16LF1704/8 Only.

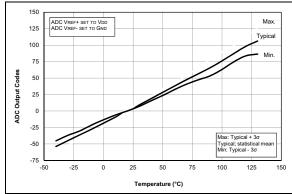

**FIGURE 33-88:** Temperature Indicator Slope Normalized to 20°C, High Range, VDD = 5.5V, PIC16LF1704/8 Only.

**FIGURE 33-89:** Temperature Indicator Slope Normalized to 20°C, High Range, VDD = 3V, PIC16F1704/8 Only.

FIGURE 33-90: Temperature Indicator Slope Normalized to 20°C, Low Range, VDD = 3.0V, PIC16F1704/8 Only.