Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-e-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

The PIC16(L)F1704/8 are described within this data sheet. They are available in 14-pin and 20-pin DIP packages and 16-pin and 20-pin QFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F1704/8 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| <b></b>                                                    |             |               |               |

|------------------------------------------------------------|-------------|---------------|---------------|

| Peripheral                                                 |             | PIC16(L)F1704 | PIC16(L)F1708 |

| Analog-to-Digital Converter (A                             | ADC)        | ٠             | •             |

| Digital-to-Analog Converter (I                             | DAC)        | •             | •             |

| Complementary Output Generation                            | ator (COG)  | •             | •             |

| Fixed Voltage Reference (FV                                | R)          | •             | •             |

| Zero Cross Detection (ZCD)                                 |             | •             | •             |

| Temperature Indicator                                      |             | •             | •             |

| Capture/Compare/PWM (CCF                                   | P/ECCP) Mod | ules          |               |

|                                                            | CCP1        | •             | •             |

|                                                            | CCP2        | •             | •             |

| Comparators                                                |             |               |               |

|                                                            | C1          | •             | •             |

|                                                            | C2          | •             | •             |

| Configurable Logic Cell (CLC                               | )           |               |               |

|                                                            | CLC1        | •             | •             |

|                                                            | CLC2        | •             | •             |

|                                                            | •           | •             |               |

| Enhanced Universal Synchron<br>Receiver/Transmitter (EUSAR |             | nous          |               |

|                                                            | EUSART      | •             | •             |

| Master Synchronous Serial P                                | orts        |               |               |

|                                                            | MSSP        | •             | •             |

| Op Amp                                                     |             |               |               |

|                                                            | Op Amp 1    | •             | •             |

|                                                            | Op Amp 2    | •             | •             |

| Pulse Width Modulator (PWN                                 | 1)          |               |               |

|                                                            | PWM3        | •             | •             |

|                                                            | PWM4        | •             | •             |

| Timers                                                     |             |               |               |

|                                                            | Timer0      | •             | •             |

|                                                            | Timer1      | •             | •             |

|                                                            | Timer2      |               |               |

© 2013-2015 Microchip Technology Inc.

|                                                                      | ACK EXAMPLE                                                                          | 2                                                                                                                                         |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      |                                                                                      |                                                                                                                                           |

| 0x0F                                                                 |                                                                                      |                                                                                                                                           |

| 0x0E                                                                 |                                                                                      |                                                                                                                                           |

| 0x0E                                                                 | )                                                                                    |                                                                                                                                           |

| 0x0C                                                                 | :                                                                                    |                                                                                                                                           |

| 0x0E                                                                 | 3                                                                                    |                                                                                                                                           |

| 0x0A                                                                 | <b>x</b>                                                                             |                                                                                                                                           |

| 0x09                                                                 | )                                                                                    | This figure shows the stack configuration                                                                                                 |

| 30x0                                                                 | 3                                                                                    | after the first CALL or a single interrupt.<br>If a RETURN instruction is executed, the                                                   |

| 0x07                                                                 | •                                                                                    | return address will be placed in the<br>Program Counter and the Stack Pointer                                                             |

| 0x06                                                                 | 3                                                                                    | decremented to the empty state (0x1F).                                                                                                    |

| 0x05                                                                 | 5                                                                                    |                                                                                                                                           |

| 0x04                                                                 |                                                                                      |                                                                                                                                           |

| 0x03                                                                 | 3                                                                                    |                                                                                                                                           |

| 0x02                                                                 | 2                                                                                    |                                                                                                                                           |

| 0x01                                                                 |                                                                                      |                                                                                                                                           |

| TOSH:TOSL 0x00                                                       | Return Address                                                                       | STKPTR = 0x00                                                                                                                             |

|                                                                      |                                                                                      |                                                                                                                                           |

| 0x0F                                                                 |                                                                                      |                                                                                                                                           |

| 0x0E                                                                 |                                                                                      |                                                                                                                                           |

| 0x0D                                                                 |                                                                                      |                                                                                                                                           |

| 0x0C                                                                 |                                                                                      | After seven CALLs or six CALLs and an                                                                                                     |

| 0x0B                                                                 |                                                                                      |                                                                                                                                           |

|                                                                      |                                                                                      | interrupt, the stack looks like the figure<br>on the left. A series of RETURN instructions                                                |

| 0x0A                                                                 |                                                                                      |                                                                                                                                           |

| 0x0A<br>0x09                                                         |                                                                                      | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses                                                |

| 0x0A<br>0x09<br>0x08                                                 |                                                                                      | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses                                                |

| 0x0A<br>0x09<br>0x08<br>0x07                                         | Return Address                                                                       | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

| 0x0A<br>0x09<br>0x08<br>0x07<br>TOSH:TOSL 0x06                       | Return Address                                                                       | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses                                                |

| 0x0A<br>0x09<br>0x08<br>0x07<br>TOSH:TOSL<br>0x06<br>0x05            | Return Address                                                                       | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

| 0x0A<br>0x09<br>0x08<br>0x07<br>TOSH:TOSL 0x06                       | Return Address<br>Return Address                                                     | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

| 0x0A<br>0x09<br>0x08<br>0x07<br>TOSH:TOSL<br>0x06<br>0x05<br>0x04    | Return Address<br>Return Address                                                     | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

| 0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03         | Return Address<br>Return Address<br>Return Address                                   | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

| 0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03<br>0x02 | Return AddressReturn AddressReturn AddressReturn AddressReturn AddressReturn Address | on the left. A series of RETURN instructions<br>will repeatedly place the return addresses<br>into the Program Counter and pop the stack. |

$\ensuremath{\textcircled{}^{\odot}}$  2013-2015 Microchip Technology Inc.

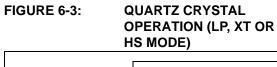

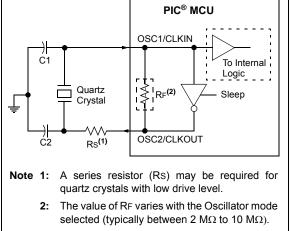

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### FIGURE 6-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

#### 6.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended, unless either FSCM or Two-Speed Start-Up are enabled. In this case, code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 6.4 "Two-Speed Clock Start-up Mode"**).

| U-0          | U-0                                                                                                                                          | R/W-0/0                                                                                    | R/W-0/0                                           | U-0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|------------------|----------|-------------|

|              | _                                                                                                                                            | COGIF                                                                                      | ZCDIF                                             |             | CLC3IF           | CLC2IF   | CLC1IF      |

| bit 7        |                                                                                                                                              |                                                                                            |                                                   |             |                  |          | bit C       |

| Legend:      |                                                                                                                                              |                                                                                            |                                                   |             |                  |          |             |

| R = Read     | lable bit                                                                                                                                    | W = Writable                                                                               | bit                                               | U = Unimple | mented bit, read | l as '0' |             |

|              | unchanged                                                                                                                                    | x = Bit is unk                                                                             |                                                   | •           | at POR and BO    |          | ther Resets |

| '1' = Bit is | •                                                                                                                                            | '0' = Bit is cle                                                                           |                                                   |             |                  |          |             |

|              |                                                                                                                                              |                                                                                            |                                                   |             |                  |          |             |

| bit 7-6      | -                                                                                                                                            | nted: Read as '0'                                                                          |                                                   |             |                  |          |             |

| bit 5        |                                                                                                                                              | G Auto-Shutdov                                                                             | vn Interrupt Fla                                  | ıg bit      |                  |          |             |

|              | 1 = Interrupt<br>0 = Interrupt                                                                                                               | t is pending<br>t is not pending                                                           |                                                   |             |                  |          |             |

| bit 4        | ZCDIF: Zero                                                                                                                                  | o-Cross Detectio                                                                           | on Interrupt Fla                                  | g bit       |                  |          |             |

|              | 1 = Interrupt<br>0 = Interrupt                                                                                                               | t is pending<br>t is not pending                                                           |                                                   |             |                  |          |             |

| bit 3        | Unimplemer                                                                                                                                   | nted: Read as '0'                                                                          |                                                   |             |                  |          |             |

| bit 2        | CLC3IF: CL                                                                                                                                   | .C3 Interrupt Fla                                                                          | g bit                                             |             |                  |          |             |

|              | 1 = Interrupt<br>0 = Interrupt                                                                                                               | t is pending<br>t is not pending                                                           |                                                   |             |                  |          |             |

| bit 1        | CLC2IF: CL                                                                                                                                   | .C2 Interrupt Fla                                                                          | g bit                                             |             |                  |          |             |

|              | 1 = Interrupt<br>0 = Interrupt                                                                                                               | t is pending<br>t is not pending                                                           |                                                   |             |                  |          |             |

| bit 0        | CLC1IF: CL                                                                                                                                   | C1 Interrupt Fla                                                                           | g bit                                             |             |                  |          |             |

|              | 1 = Interrupt<br>0 = Interrupt                                                                                                               | t is pending<br>t is not pending                                                           |                                                   |             |                  |          |             |

| Note:        | Interrupt flag bits<br>condition occurs,<br>its corresponding<br>Enable bit, GIE,<br>User software<br>appropriate inter<br>prior to enabling | regardless of th<br>g enable bit or th<br>of the INTCON<br>should ens<br>rrupt flag bits a | e state of<br>ne Global<br>I register.<br>ure the |             |                  |          |             |

#### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

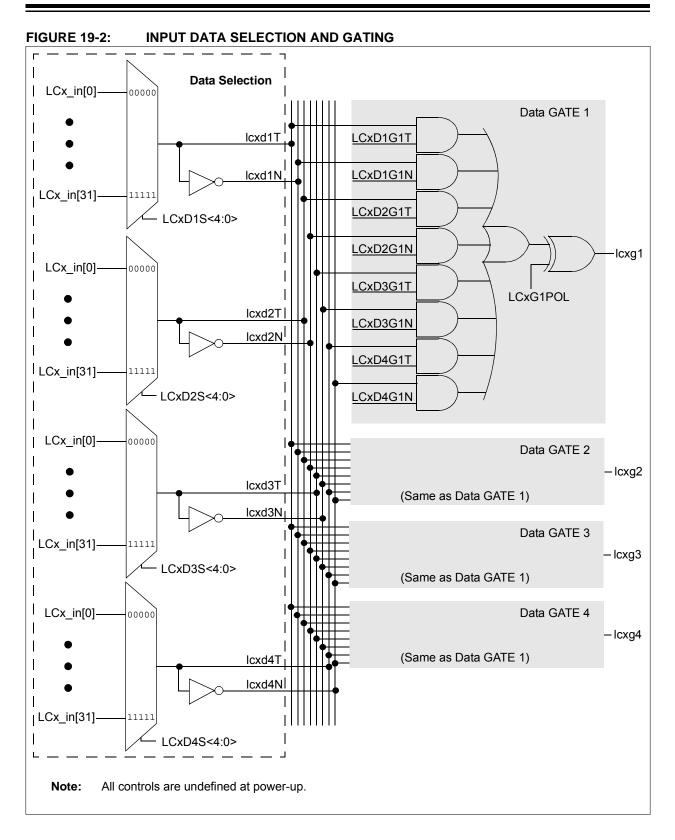

#### REGISTER 19-6: CLCxSEL3: GENERIC CLCx DATA 4 SELECT REGISTER

| U-0                                  | U-0 | U-0               | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u     | R/W-x/u |

|--------------------------------------|-----|-------------------|----------------|---------------|------------------|-------------|---------|

| —                                    | _   | —                 |                |               | LCxD4S<4:0>      |             |         |

| bit 7                                |     |                   |                |               |                  |             | bit 0   |

|                                      |     |                   |                |               |                  |             |         |

| Legend:                              |     |                   |                |               |                  |             |         |

| R = Readable bit W = Writable b      |     |                   | bit            | U = Unimpler  | nented bit, read | l as '0'    |         |

| u = Bit is unchanged x = Bit is unkn |     | iown              | -n/n = Value a | at POR and BO | R/Value at all o | ther Resets |         |

| '1' = Bit is set                     |     | '0' = Bit is clea | ared           |               |                  |             |         |

|                                      |     |                   |                |               |                  |             |         |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 LCxD4S<4:0>: CLCx Data 4 Input Selection bits See Table 19-1.

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4                | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|-----------|----------------------|--------|---------|---------|---------|---------------------|

| ADCON0                | —                     |                       |           | CHS<4:0>             |        |         | GO/DONE | ADON    | 223                 |

| ADCON1                | ADFM                  |                       | ADCS<2:0> |                      | _      | ADNREF  | ADPRE   | F<1:0>  | 224                 |

| ADCON2                |                       | TRIGSE                | EL<3:0>   |                      | _      | —       | —       | —       | 225                 |

| ADRESH                | ADC Result            | Register Hig          | h         |                      |        |         |         |         | 226, 227            |

| ADRESL                | ADC Result            | Register Lov          | v         |                      |        |         |         |         | 226, 227            |

| ANSELA                | —                     | —                     | —         | ANSA4                | —      | ANSA2   | ANSA1   | ANSA0   | 122                 |

| ANSELB <sup>(1)</sup> | —                     | _                     | ANSB5     | ANSB4                | _      | —       | —       | _       | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2)  | ANSC4 <sup>(2)</sup> | ANSC3  | ANSC2   | ANSC1   | ANSC0   | 133                 |

| INTCON                | GIE                   | PEIE                  | TMR0IE    | INTE                 | IOCIE  | TMR0IF  | INTF    | IOCIF   | 85                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE      | TXIE                 | SSP1IE | CCP1IE  | TMR2IE  | TMR1IE  | 86                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF      | TXIF                 | SSP1IF | CCP1IF  | TMR2IF  | TMR1IF  | 89                  |

| TRISA                 | —                     | —                     | TRISA5    | TRISA4               | (3)    | TRISA2  | TRISA1  | TRISA0  | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5    | TRISB4               | _      | —       | —       | _       | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5    | TRISC4               | TRISC3 | TRISC2  | TRISC1  | TRISC0  | 132                 |

| FVRCON                | FVREN                 | FVRRDY                | TSEN      | TSRNG                | CDAFV  | /R<1:0> | ADFVI   | R<1:0>  | 151                 |

| DAC1CON0              | DAC1EN                | _                     | DAC10E1   | DAC10E2              | DAC1PS | SS<1:0> | —       | DAC1NSS | 237                 |

#### TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for the ADC module.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

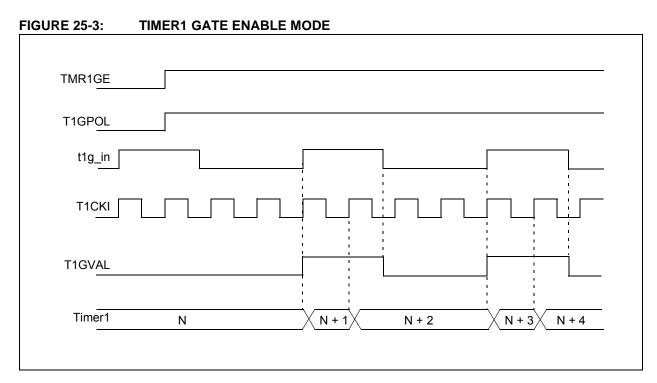

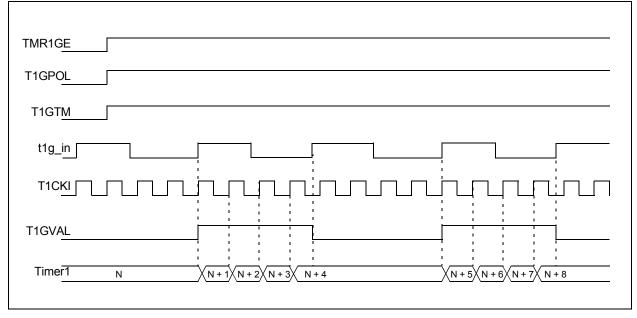

#### FIGURE 25-4: TIMER1 GATE TOGGLE MODE

#### 28.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any SSPBUF register write to the during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSPSTAT register indicates the various Status conditions.

#### 28.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

#### 28.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 28.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 28-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 28-5) affects the address matching process. See **Section 28.5.9** "**SSP Mask Register**" for more information.

28.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

28.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 28.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 28.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

#### 28.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

#### 28.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 28-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPIF bit.

- 4. Slave hardware generates an ACK and sets SSPIF.

- 5. SSPIF bit is cleared by user.

- 6. Software reads the received address from SSPBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

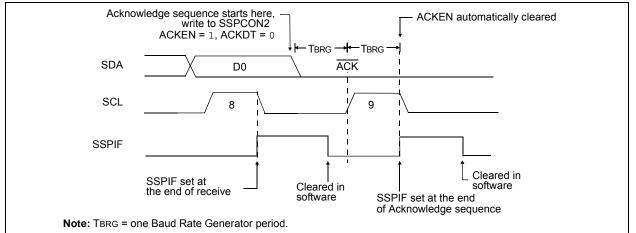

#### 28.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 28-30).

#### 28.6.8.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

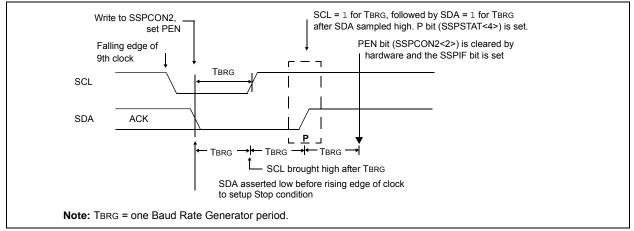

#### 28.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 28-31).

#### 28.6.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 28-30: ACKNOWLEDGE SEQUENCE WAVEFORM

| Name                  | Bit 7                 | Bit 6                 | Bit 5                | Bit 4                | Bit 3   | Bit 2       | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|-----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|-------------|--------|--------|-----------------------------|

| ANSELA                | —                     | _                     | _                    | ANSA4                | —       | ANSA2       | ANSA1  | ANSA0  | 122                         |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5                | ANSB4                | —       | —           | —      | —      | 128                         |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5 <sup>(2)</sup> | ANSC4 <sup>(2)</sup> | ANSC3   | ANSC2       | ANSC1  | ANSC0  | 133                         |

| INTCON                | GIE                   | PEIE                  | TMR0IE               | INTE                 | IOCIE   | TMR0IF      | INTF   | IOCIF  | 85                          |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE                 | TXIE                 | SSP1IE  | CCP1IE      | TMR2IE | TMR1IE | 86                          |

| PIE2                  | OSFIE                 | C2IE                  | C1IE                 | _                    | BCL1IE  | TMR6IE      | TMR4IE | CCP2IE | 87                          |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF                 | TXIF                 | SSP1IF  | CCP1IF      | TMR2IF | TMR1IF | 89                          |

| PIR2                  | OSFIF                 | C2IF                  | C1IF                 | _                    | BCL1IF  | TMR6IF      | TMR4IF | CCP2IF | 90                          |

| RxyPPS                |                       | _                     | _                    |                      |         | RxyPPS<4:0> | >      |        | 140                         |

| SSPCLKPPS             | —                     | _                     | _                    | SSPCLKPPS<4:0>       |         |             |        |        | 138, 139                    |

| SSPDATPPS             | —                     | _                     | _                    |                      | SS      | SPDATPPS<4  | :0>    |        | 138, 139                    |

| SSPSSPPS              | —                     | _                     | _                    |                      | S       | SPSSPPS<4:  | )>     |        | 138, 139                    |

| SSP1ADD               |                       |                       |                      | ADD                  | <7:0>   |             |        |        | 323                         |

| SSP1BUF               | Synchronous           | s Serial Port F       | Receive Buffe        | r/Transmit Re        | egister |             |        |        | 272*                        |

| SSP1CON1              | WCOL                  | SSPOV                 | SSPEN                | CKP                  |         | SSPM        | l<3:0> |        | 319                         |

| SSP1CON2              | GCEN                  | ACKSTAT               | ACKDT                | ACKEN                | RCEN    | PEN         | RSEN   | SEN    | 321                         |

| SSP1CON3              | ACKTIM                | PCIE                  | SCIE                 | BOEN                 | SDAHT   | SBCDE       | AHEN   | DHEN   | 322                         |

| SSP1MSK               | MSK<7:0>              |                       |                      |                      |         |             |        | 323    |                             |

| SSP1STAT              | SMP                   | CKE                   | D/A                  | Р                    | S       | R/W         | UA     | BF     | 317                         |

| TRISA                 | —                     | —                     | TRISA5               | TRISA4               | (3)     | TRISA2      | TRISA1 | TRISA0 | 121                         |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5               | TRISB4               | —       | —           | —      | —      | 127                         |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5               | TRISC4               | TRISC3  | TRISC2      | TRISC1 | TRISA0 | 132                         |

TABLE 28-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

\* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

#### REGISTER 28-1: SSP1STAT: SSP STATUS REGISTER (CONTINUED)

- bit 0 BF: Buffer Full Status bit

- <u>Receive (SPI and I<sup>2</sup>C modes):</u> 1 = Receive complete, SSPBUF is full

- 0 = Receive not complete, SSPBUF is empty

- Transmit (I<sup>2</sup>C mode only):

- 1 = Data transmit in progress (does not include the  $\overline{ACK}$  and Stop bits), SSPBUF is full

- 0 = Data transmit complete (does not include the ACK and Stop bits), SSPBUF is empty

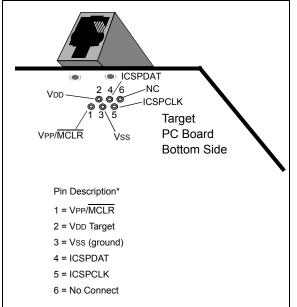

#### 30.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16(L)F170X Memory Programming Specification*" (DS41683).

#### 30.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 30.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 5.5 "MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### **30.3 Common Programming Interfaces**

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 30-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 30-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 30-3 for more information.

#### 31.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 31-3 lists the instructions recognized by the MPASMTM assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 31.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 31-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

#### TABLE 31-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

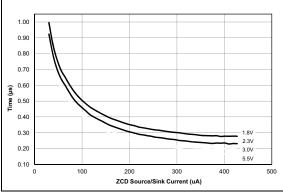

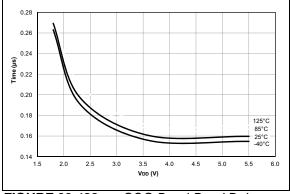

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

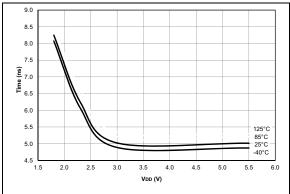

**FIGURE 33-121:** ZCD Pin Response Time Over Current, Typical Measured Values from -40°C to 125°C.

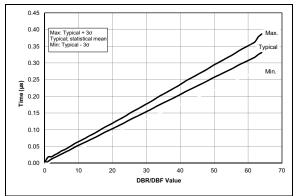

FIGURE 33-122: COG Dead-Band Delay, DBR/DBF = 32, Typical Measured Values.

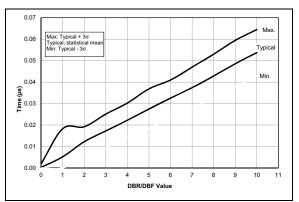

FIGURE 33-123: COG Dead-Band DBR/DBF Delay Per Step, Typical Measured Values.

FIGURE 33-124: COG Dead-Band Delay per Step, Typical Measured Values.

**FIGURE 33-125:** COG Dead-Band Delay per Step, Zoomed to First 10 Codes, Typical Measured Values.

#### 34.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 34.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradeable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 34.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 34.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 34.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15