Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

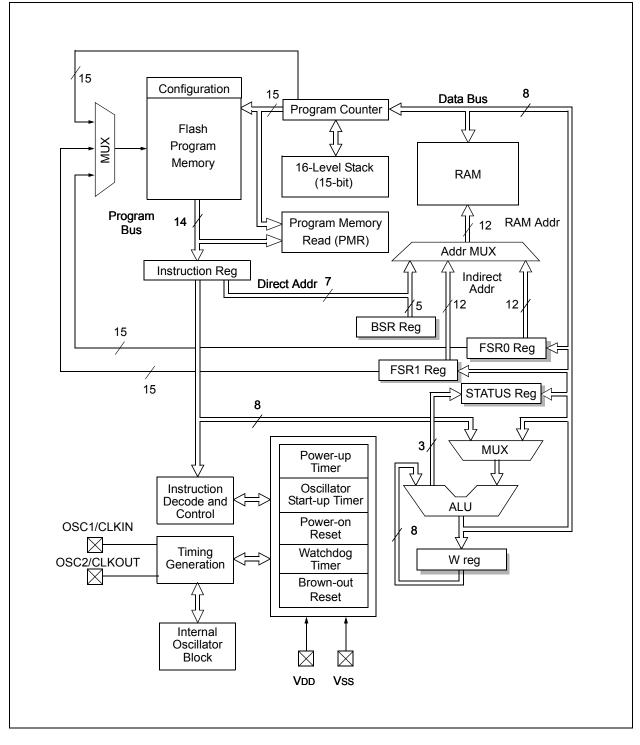

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

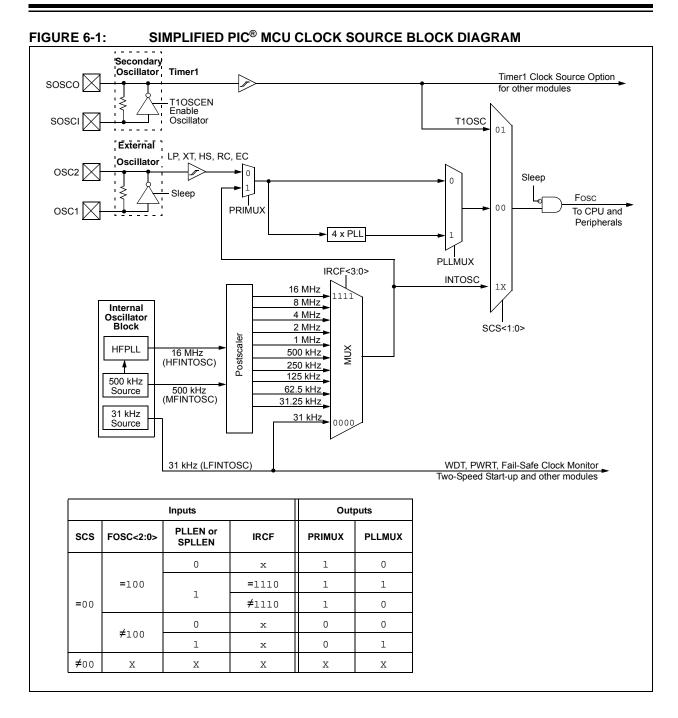

## 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3** "**Clock Switching**" for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 6.3 "Clock Switching" for more information.

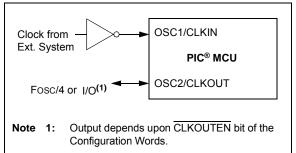

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

- ; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$   $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>MOVWF | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary<br>; Load upper 6 bits of erase address boundary                                                                                                                                                                                             |

|----------------------|--------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | BCF<br>BSF<br>BSF                                | PMADKH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN            | ; Not configuration space<br>; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                             |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP     | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                       | PMCON1,WREN<br>INTCON,GIE                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                  |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|

| ANSELB  | _       | _       | ANSB5   | ANSB4   |       | —     | _     | _     | 128                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 |       | —     | _     | _     | 129                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   |       | —     | _     | _     | 127                 |

| ODCONB  | ODB7    | ODB6    | ODB5    | ODB4    |       | —     | _     | _     | 129                 |

| PORTB   | RB7     | RB6     | RB5     | RB4     |       | —     | _     | _     | 127                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   |       | —     | _     | _     | 129                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  |       | —     | —     | —     | 129                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   |       | —     |       | _     | 128                 |

### TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

| Peripheral | Conditions                                                    | Description                                                 |

|------------|---------------------------------------------------------------|-------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> ≠ 000x                       | INTOSC is active and device is not in Sleep                 |

|            | BOREN<1:0> = 11                                               | BOR always enabled                                          |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                 | BOR disabled in Sleep mode, BOR Fast Start enabled          |

|            | BOREN<1:0> = 01 and BORFS = 1                                 | BOR under software control, BOR Fast Start enabled          |

| LDO        | All PIC16F1704/8 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the ULP regulator when in Sleep mode |

## TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

# 14.3 FVR Buffer Stabilization Period

When either FVR Buffer1 or FVR Buffer2 is enabled, then the buffer amplifier circuits require  $30 \ \mu s$  to stabilize. This stabilization time is still required when the FVR buffer is in operation.

| R/W-0/0          | R/W-0/0                             | R/W-0/0                                                   | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |

|------------------|-------------------------------------|-----------------------------------------------------------|-----------------|-----------------|-----------------|----------------|--------------|

| CxINTP           | CxINTN                              |                                                           | CxPCH<2:0>      |                 |                 | CxNCH<2:0>     |              |

| bit 7            |                                     |                                                           |                 |                 |                 |                | bit C        |

|                  |                                     |                                                           |                 |                 |                 |                |              |

| Legend:          |                                     |                                                           |                 |                 |                 |                |              |

| R = Readable     |                                     | W = Writable                                              |                 | •               | nented bit, rea |                |              |

| u = Bit is unc   | 0                                   | x = Bit is unkr                                           |                 | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |

| '1' = Bit is set |                                     | '0' = Bit is cle                                          | ared            |                 |                 |                |              |

| bit 7            | CxINTP: Co                          | mparator Interru                                          | ıpt on Positive | Going Edge E    | nable bits      |                |              |

|                  |                                     | F interrupt flag v<br>rupt flag will be                   |                 |                 |                 |                |              |

| bit 6            |                                     | mparator Interru<br>F interrupt flag                      |                 |                 |                 | e CxOUT bit    |              |

|                  | 0 = No inter                        | rupt flag will be                                         | set on a nega   | tive going edge | of the CxOUT    | bit            |              |

| bit 5-3          | CxPCH<2:0                           | CxPCH<2:0>: Comparator Positive Input Channel Select bits |                 |                 |                 |                |              |

|                  | 111 = CxVP connects to AGND         |                                                           |                 |                 |                 |                |              |

|                  | 110 = CxVP connects to FVR Buffer 2 |                                                           |                 |                 |                 |                |              |

|                  |                                     | P connects to VDAC<br>P unconnected, input floating       |                 |                 |                 |                |              |

|                  |                                     | unconnected, i                                            |                 |                 |                 |                |              |

|                  |                                     | unconnected, i                                            |                 |                 |                 |                |              |

|                  |                                     | unconnected, i                                            | · •             |                 |                 |                |              |

|                  | 000 = CxVP                          | connects to Cx                                            | IN+ pin         |                 |                 |                |              |

| bit 2-0          | CxNCH<2:0                           | >: Comparator I                                           | Negative Input  | t Channel Seleo | ct bits         |                |              |

|                  | 111 = CxVN                          | connects to AC                                            | GND             |                 |                 |                |              |

|                  | 110 = CxVN connects to FVR Buffer 2 |                                                           |                 |                 |                 |                |              |

|                  |                                     | unconnected, i                                            |                 |                 |                 |                |              |

|                  |                                     | unconnected, i                                            |                 |                 |                 |                |              |

|                  |                                     | connects to Cx                                            |                 |                 |                 |                |              |

|                  |                                     | connects to Cx                                            |                 |                 |                 |                |              |

|                  | 001 = CXVN $000 = CXVN$             | connects to Cx                                            |                 |                 |                 |                |              |

### REGISTER 16-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

# 19.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- · Data gating

- Logic function selection

- · Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 19.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 19-2. Data inputs in the figure are identified by a generic numbered input name.

Table 19-1 correlates the generic input name to the actual signal for each CLC module. The column labeled lcxdy indicates the MUX selection code for the selected data input. DxS is an abbreviation for the MUX select input codes: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 19-3 through Register 19-6).

**Note:** Data selections are undefined at power-up.

#### TABLE 19-1: CLCx DATA INPUT SELECTION

| Data Input | lcxdy<br>DxS | CLCx                                               |

|------------|--------------|----------------------------------------------------|

| LCx_in[31] | 11111        | Fosc                                               |

| LCx_in[30] | 11110        | HFINTOSC                                           |

| LCx_in[29] | 11101        | LFINTOSC                                           |

| LCx_in[28] | 11100        | ADC FRC                                            |

| LCx_in[27] | 11011        | IOCIF set signal (bit?)                            |

| LCx_in[26] | 11010        | T2_match                                           |

| LCx_in[25] | 11001        | T1_overflow                                        |

| LCx_in[24] | 11000        | T0_overflow                                        |

| LCx_in[23] | 10111        | T6_match                                           |

| LCx_in[22] | 10110        | T4_match                                           |

| LCx_in[21] | 10101        | DT from EUSART                                     |

| LCx_in[20] | 10100        | TX/CK from EUSART                                  |

| LCx_in[19] | 10011        | ZCDx_out from Zero-Cross Detect                    |

| LCx_in[18] | 10010        | SDO from MSSP                                      |

| LCx_in[17] | 10001        | Reserved                                           |

| LCx_in[16] | 10000        | SCK from MSSP                                      |

| LCx_in[15] | 01111        | PWM4_out                                           |

| LCx_in[14] | 01110        | PWM3_out                                           |

| LCx_in[13] | 01101        | CCP2 output                                        |

| LCx_in[12] | 01100        | CCP1 output                                        |

| LCx_in[11] | 01011        | COG1B                                              |

| LCx_in[10] | 01010        | COG1A                                              |

| LCx_in[9]  | 01001        | C2OUT                                              |

| LCx_in[8]  | 01000        | C1OUT                                              |

| LCx_in[7]  | 00111        | Reserved                                           |

| LCx_in[6]  | 00110        | LC3_out from the CLC3                              |

| LCx_in[5]  | 00101        | LC2_out from the CLC2                              |

| LCx_in[4]  | 00100        | LC1_out from the CLC1                              |

| LCx_in[3]  | 00011        | CLCIN3 pin input selected in<br>CLCIN3PPS register |

| LCx_in[2]  | 00010        | CLCIN2 pin input selected in<br>CLCIN2PPS register |

| LCx_in[1]  | 00001        | CLCIN1 pin input selected in<br>CLCIN1PPS register |

| LCx_in[0]  | 00000        | CLCIN0 pin input selected in<br>CLCIN0PPS register |

### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

#### TABLE 19-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- Gate 3: CLCxGLS2 (Register 19-9)

- Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

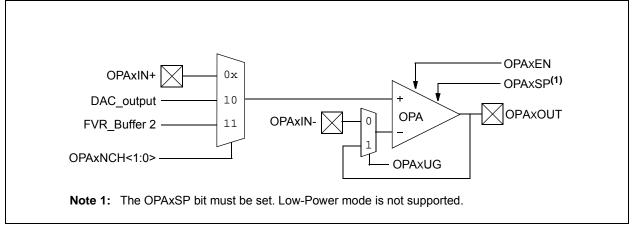

# 21.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard three-terminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- Low leakage inputs

- Factory Calibrated Input Offset Voltage

#### 28.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 28-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 28-6, Figure 28-8, Figure 28-9 and Figure 28-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 28-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

**Note:** In Master mode the clock signal output to the SCK pin is also the clock signal input to the peripheral. The pin selected for output with the RxyPPS register must also be selected as the peripheral input with the SSPCLKPPS register.

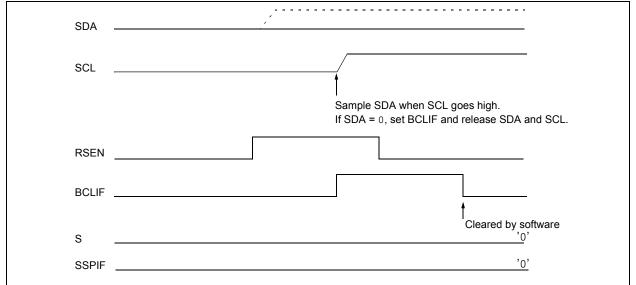

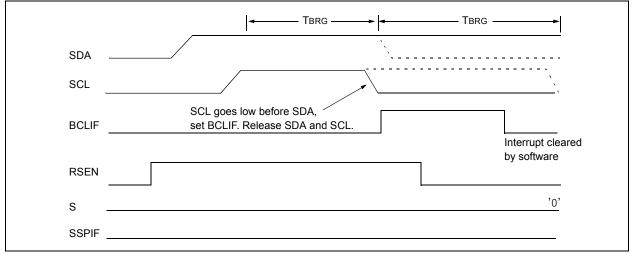

# 28.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 28-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 28-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 28-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

# 29.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 29.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 29.5.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 29.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCSTA and TXSTA Control registers must be configured for synchronous slave transmission (see Section 29.5.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| LSLF             | Logical Left Shift                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]LSLF f{,d}                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \ \in \ [0,1] \end{array}$                                                                                                                                                                 |

| Operation:       | $(f<7>) \rightarrow C$<br>$(f<6:0>) \rightarrow dest<7:1>$<br>$0 \rightarrow dest<0>$                                                                                                                                               |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the left through the Carry flag.<br>A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. |

|                  | C ← register f ←0                                                                                                                                                                                                                   |

| LSRF             | Logical Right Shift                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} 0 \rightarrow \text{dest<7>} \\ (\text{f<7:1>}) \rightarrow \text{dest<6:0>}, \\ (\text{f<0>}) \rightarrow \text{C}, \end{array}$                                                                                  |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |

| Ū |    | 010.04 |      | <br>- <u>-</u> |   |  |

|---|----|--------|------|----------------|---|--|

|   | 0- | regist | er f |                | С |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                 |

| Cycles:          | 1                                                                                                                                                                                                                                                                                 |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                                           |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                               |

| Example:         | RETFIE                                                                                                                                                                                                          |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                  |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                           |                                           | Detete Left ( through Orang                                                                                                                                                       |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                           | RLF                                       | Rotate Left f through Carry                                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                  | Syntax:                                   | [ <i>label</i> ] RLF f,d                                                                                                                                                          |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                       | Operands: $0 \le f \le 127$ $d \in [0,1]$ |                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected: | None                                                                                                                               | Operation:                                | See description below                                                                                                                                                             |  |  |  |  |  |

| Description:     | The W register is loaded with the 8-bit                                                                                            | Status Affected:                          | Status Affected: C                                                                                                                                                                |  |  |  |  |  |

| Description.     | literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:                              | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is |  |  |  |  |  |

| Words:           | 1                                                                                                                                  |                                           | stored back in register 'f'.                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                  |                                           | ← C ← Register f ←                                                                                                                                                                |  |  |  |  |  |

| Example:         | CALL TABLE; W contains table                                                                                                       | Words:                                    | 1                                                                                                                                                                                 |  |  |  |  |  |

|                  | <pre>;offset value ,W now has table value</pre>                                                                                    | Cycles:                                   | 1                                                                                                                                                                                 |  |  |  |  |  |

| TABLE            | •                                                                                                                                  | Example:                                  | RLF REG1,0                                                                                                                                                                        |  |  |  |  |  |

|                  | •                                                                                                                                  |                                           | Before Instruction                                                                                                                                                                |  |  |  |  |  |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table                                                                                      |                                           | $\begin{array}{rcl} \text{REG1} &=& 1110 & 0110 \\ \text{C} &=& 0 \end{array}$                                                                                                    |  |  |  |  |  |

|                  | RETLW k2 ;                                                                                                                         |                                           | After Instruction                                                                                                                                                                 |  |  |  |  |  |

|                  | •                                                                                                                                  |                                           | REG1 = 1110 0110                                                                                                                                                                  |  |  |  |  |  |

|                  |                                                                                                                                    |                                           | $W = 1100 \ 1100$                                                                                                                                                                 |  |  |  |  |  |

|                  | RETLW kn ; End of table                                                                                                            |                                           | C = 1                                                                                                                                                                             |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                             |                                           |                                                                                                                                                                                   |  |  |  |  |  |

| PIC16LF1      | 1704/8          | Standa | Standard Operating Conditions (unless otherwise stated) |      |       |                             |                             |  |  |  |

|---------------|-----------------|--------|---------------------------------------------------------|------|-------|-----------------------------|-----------------------------|--|--|--|

| PIC16F17      | /04/8           | Standa | Standard Operating Conditions (unless otherwise stated) |      |       |                             |                             |  |  |  |

| Param. Device |                 |        | Tree d                                                  | Mari | Unite | Conditions                  |                             |  |  |  |

| No. Cha       | Characteristics | Min.   | Тур.†                                                   | Max. | Units | Vdd                         | Note                        |  |  |  |

| D020          |                 | -      | 2.3                                                     | 3.0  | mA    | 3.0                         | Fosc = 32 MHz,              |  |  |  |

|               |                 | —      | 2.8                                                     | 3.5  | mA    | 3.6                         | HFINTOSC mode (Note 5)      |  |  |  |

| D020          |                 | —      | 2.4                                                     | 3.1  | mA    | 3.0                         | Fosc = 32 MHz,              |  |  |  |

|               |                 | —      | 2.6                                                     | 3.4  | mA    | 5.0                         | HFINTOSC mode (Note 5)      |  |  |  |

| D022          |                 | —      | 2                                                       | 3.0  | mA    | 3.0                         | Fosc = 32 MHz,              |  |  |  |

|               |                 | —      | 2.6                                                     | 3.5  | mA    | 3.6                         | HS Oscillator mode (Note 5) |  |  |  |

| D022          |                 | _      | 2.1                                                     | 3.0  | mA    | 3.0                         | Fosc = 32 MHz,              |  |  |  |

|               | _               | 3      | 3.5                                                     | mA   | 5.0   | HS Oscillator mode (Note 5) |                             |  |  |  |

# TABLE 32-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 8 MHz clock with 4x PLL enabled.

| PIC16LF1704/8 |                                                      |       | Standard Operating Conditions (unless otherwise stated)<br>Low-Power Sleep Mode |      |      |     |                        |                        |  |

|---------------|------------------------------------------------------|-------|---------------------------------------------------------------------------------|------|------|-----|------------------------|------------------------|--|

| PIC16F1704/8  |                                                      |       | Low-Power Sleep Mode, VREGPM = 1                                                |      |      |     |                        |                        |  |

| Param.        |                                                      |       | <b>T</b> 1                                                                      | Max. | Max. |     | Conditions             |                        |  |

| No.           | Device Characteristics Min. Typ.† +85°C +125°C Units | Units | Vdd                                                                             | Note |      |     |                        |                        |  |

| D030          |                                                      | _     | 250                                                                             | _    | —    | μA  | 1.8                    | ADC Current (Note 3),  |  |

|               | _                                                    | 250   |                                                                                 | _    | μA   | 3.0 | conversion in progress |                        |  |

| D030          |                                                      | _     | 280                                                                             | _    | _    | μA  | 2.3                    | ADC Current (Note 3),  |  |

|               |                                                      | _     | 280                                                                             | _    | _    | μA  | 3.0                    | conversion in progress |  |

|               |                                                      |       | 280                                                                             |      | _    | μA  | 5.0                    |                        |  |

| D031          |                                                      | _     | 250                                                                             | 650  | _    | μA  | 3.0                    | Op Amp (High-power)    |  |

| D031          |                                                      | _     | 250                                                                             | 650  | _    | μA  | 3.0                    | Op Amp (High-power)    |  |

|               |                                                      | 350   | 850                                                                             | _    | μA   | 5.0 |                        |                        |  |

| D032          |                                                      | _     | 250                                                                             | 600  | _    | μA  | 1.8                    | Comparator, CxSP = 1   |  |

|               |                                                      | _     | 300                                                                             | 650  | _    | μA  | 3.0                    |                        |  |

| D032          |                                                      | —     | 280                                                                             | 600  | _    | μA  | 2.3                    | Comparator, CxSP = 1   |  |

|               |                                                      |       | 300                                                                             | 650  | _    | μA  | 3.0                    | VREGPM = 0             |  |

|               |                                                      |       | 310                                                                             | 650  | _    | μA  | 5.0                    |                        |  |

# TABLE 32-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED)

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC oscillator source is FRC.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

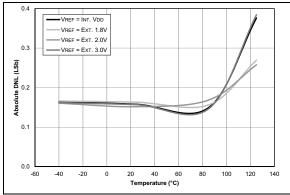

**FIGURE 33-115:** Absolute Value of DAC DNL Error, VDD = 3.0V, VREF = VDD.

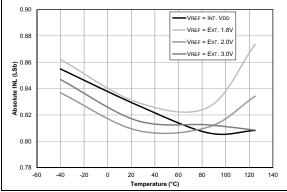

**FIGURE 33-116:** Absolute Value of DAC INL Error, VDD = 3.0V, VREF = VDD.

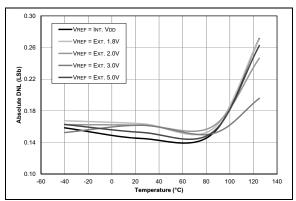

**FIGURE 33-117:** Absolute Value of DAC DNL Error, VDD = 5.0V, VREF = VDD, PIC16F1704/8 Only.

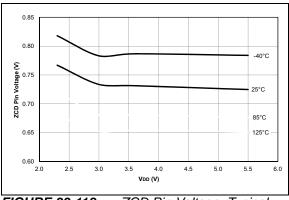

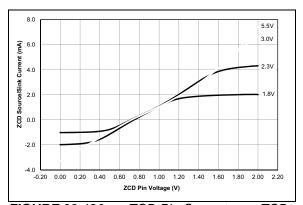

**FIGURE 33-118:** ZCD Pin Voltage. Typical Measured Values.

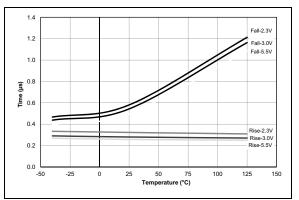

FIGURE 33-119: ZCD Response Time over Voltage, Typical Measured Values.

**FIGURE 33-120:** ZCD Pin Current over ZCD Pin Voltage, Typical Measured Values from -40°C to 125°C.

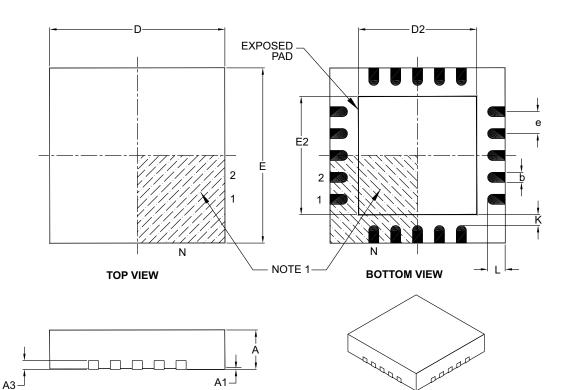

# 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          |      |      |  |

|------------------------|------------------|----------|------|------|--|

|                        | MILLIMETERS      |          |      |      |  |

| Dimer                  | Dimension Limits |          |      | MAX  |  |

| Number of Pins         | Ν                | 20       |      |      |  |

| Pitch                  | е                | 0.50 BSC |      |      |  |

| Overall Height         | Α                | 0.80     | 0.90 | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02 | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |      |      |  |

| Overall Width          | E                | 4.00 BSC |      |      |  |

| Exposed Pad Width      | E2               | 2.60     | 2.70 | 2.80 |  |

| Overall Length         | D                | 4.00 BSC |      |      |  |

| Exposed Pad Length     | D2               | 2.60     | 2.70 | 2.80 |  |

| Contact Width          | b                | 0.18     | 0.25 | 0.30 |  |

| Contact Length         | L                | 0.30     | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K                | 0.20     | -    | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B