## Microchip Technology - PIC16F1704-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

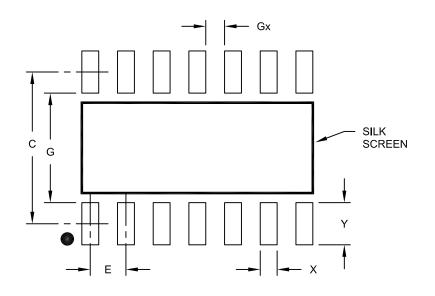

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| RA0/ANOVREF-/C1IN+/<br>DAC10UT/ICSPDAT         RA0         TTL/ST         CMOS         General purpose I/O.           AN0         AN         -         ADC Channel 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Name                                                           | Function | Input<br>Type    | Output<br>Type | Description                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------|------------------|----------------|----------------------------------------------|

| NNO         NNO         NNO         NNO         NNO         NNO         NNO           VREF.         NN         -         ADC Chalmed viluge Reference input.           C1IN+         NN         -         AND Chalmed viluge Reference input.           C1IN+         NN         -         AND Chalmed viluge Reference input.           ICSPCLK         RA1         TTLST         CMOS         ICSPM Viluge Reference input.           C1IN-         AN         -         ADC Channel 1 input.           VREF.         AN         -         ADC Voltage Reference input.           C1IN-         AN         -         Serial Programming Clock.           RA2/AN2/DAC10UT2/ZCD/<br>TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> RA2         TTLST         CMOS           AND         -         Serial Programming Clock.         ADC           RA2/AN2/DAC10UT2/ZCD/<br>TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> RA2         NN         -         ADC Channel 2 input.           DAC10UT2         -         AN         Digital-to-Analog Converter output.         DCC           TUCST         -         AND         Consparator Cors Delection Current Source/Sink.           TOCKI         TTL/ST         -         Term Cors Delection Current Source/Sink.           TOCKI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                | RA0      | TTL/ST           | CMOS           | General purpose I/O.                         |

| Clin+         AN          Comparator C1 positive input.           DQ101         -         AN         Digital-o-Analog Converter output.           ICSPCLK         ICSPDAT         ST         CMOS         ICSP <sup>TM</sup> Data I/O.           ICSPCLK         RA1         TIUST         CMOS         ICSP <sup>TM</sup> Data I/O.           ICSPCLK         RA1         TIUST         CMOS         General purpose I/O.           ICSPCLK         AN         -         ADC Channel 1 input.           VEF.+         AN         -         ADC Channel 2 input.           C2INO-         AN         -         Comparator C3 negative input.           C2INO-         AN         -         Serial Programming Clock.           RA2/AN2/DAC10UT2/ZCD/         RA2         TIUST         MOS General purpose I/O.           TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> //INT <sup>(1)</sup> RA2         TIUST         AN         Deficitator.Analog Converter output.           ZCD         -         AN         Digitator.Analog Converter output.         DIGItator.Analog Converter output.           ZCD         -         AN         Digitator.Analog Converter output.         DIGItator.           ZCD         -         AN         Digitator.Analog Converter output.         DIGItator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DAC1OUT/ICSPDAT                                                | AN0      | AN               | _              | ADC Channel 0 input.                         |

| DAC10UT         —         AN         Digital-to-Analog Converter output.           ICSPCLK         ICSPCIA         ST         CMOS         ICSP <sup>™</sup> Data I/O.           RA1/AN1/VREF+/C1INO-/C2INO-/<br>ICSPCLK         RA1         TTL/ST         CMOS         General purpose I/O.           ICSPCLK         AN1         AN         —         ADC Channel 1 input.           VREF+         AN         —         ADC Channel 1 input.           VREF+         AN         —         Comparator C2 negative input.           C2INO-         AN         —         Comparator C3 negative input.           C2INO-         AN         —         Comparator C3 negative input.           C2INO-         AN         —         Comparator C3 negative input.           CCRO         AN         —         Serial Programming Clock.           RA2/AN2/DAC10UT2/ZCD/         TDCKI         TTL/ST         MC         Channel 2 input.           CCGIN         TTL/ST         MC         Comparator C3 negative input.           TOCKI <sup>(1)</sup> (COGIN <sup>(1)</sup> ///INT <sup>(1)</sup> AN         —         ADC Channel 2 input.           TU/ST         —         XTL/ST         —         Comparator C3 negative input.           RA3         TTL/ST         —         Tore Coss D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                | VREF-    | AN               | _              | ADC Negative Voltage Reference input.        |

| ICSPDAT         ST         CMOS         ICSP™ Data I/O.           RA1/AN1/VREF+/C1IN0-/C2IN0-/<br>ICSPCLK         RA1         TTL/ST         CMOS         General purpose I/O.           ICSPCLK         AN1         AN         A         ACC Channel 1 input.           [VEF+         AN         -         ADC Voltage Reference input.           [C1IN0-         AN         -         Comparator C2 negative input.           [C2IN0-         AN         -         Comparator C3 negative input.           [CSPCLK         ST         -         Serial Programming Clock.           [CSPCLK]         AN         -         ADC Channel 2 input.           [CSPCLK]         AN         -         ADC Channel 2 input.           [CACI0T2]         -         AN         Digital-to-Analog Converter output.           [COCIN]         TTL/ST         -         ADC Channel 2 input.           [COCIN]         TTL/ST         -         Complementary Output Generator input.           [TOCKI]         TTL/ST         -         External interrupt.           [RA3/MCLR/VPP         RA3         TTL/ST         Complementary Output Generator input.           [TULST         -         Programming voltage.         Radintary Output Generator input.           <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                | C1IN+    | AN               | —              | Comparator C1 positive input.                |

| RA1/AN1/VREF+/C1IN0-/C2IN0-/<br>ICSPCLK         RA1         TTLST         CMOS         General purpose I/O.           ICSPCLK         AN1         AN          ADC Channel 1 input.           VREF+         AN          ADC Channel 1 input.           C1IN0-         AN          Comparator C2 negative input.           C2IN0-         AN          Comparator C3 negative input.           C2IN0-         AN          Comparator C3 negative input.           ICSPCLK         ST          Serial Programming Clock.           RA2/AN2/DAC1OUT2/ZCD/         RA2         TTLST         CMOS         General purpose I/O.           DAC1OUT2          AN         Digital-to-Analog Converter output.         DAC1OUT2           DAC1OUT2          AN         Zero Cross Detection Current Source/Sink.           T0CKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> TTL/ST          External interrupt.           RA3         TTL/ST          External interrupt.           RA3/MCLR/VPP         RA3         TTL/ST         CMOS           RA4/AN3/T1G <sup>(1)</sup> /SOSCO/         RA4         TTL/ST         CMOS           SOSCO         XTAL         XTAL         Secondary Oscilla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                | DAC10UT  | _                | AN             | Digital-to-Analog Converter output.          |

| ICSPCLK         AN1         AN         —         ADC Channel 1 input.           VREF+         AN         —         ADC Voltage Reference input.           C1IN0-         AN         —         Comparator C2 negative input.           C2IN0-         AN         —         Comparator C3 negative input.           ICSPCLK         ST         —         Serial Programming Clock.           RA2/AN2/DAC1OUT2/ZCD/<br>TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> RA2         TTL/ST         CMOS         General purpose I/O.           DAC10UT2         —         AN         Det Constraints         Det Constraints         Det Constraints           TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> AN2         AN         —         ADC Channel 2 input.           ZCD         —         AN         Digital-to-Analog Converter output.         ZCD           ZCD         —         AN         Digital-to-Analog Converter output.         ZCD           ZCD         —         AN         Digital-to-Analog Converter output.         ZCD           ZCOGIN         TTL/ST         —         Complementary Output Generator input.           TOCKI         TTL/ST         —         Master Clear with internal pull-up.           VPP         HV         —         Programming voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                              |

| NN         NN         AN         A         Action of the sector of th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RA1/AN1/VREF+/C1IN0-/C2IN0-/                                   | RA1      | TTL/ST           | CMOS           | General purpose I/O.                         |

| $ \left  \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ICSPCLK                                                        | AN1      | AN               | _              | ADC Channel 1 input.                         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                | VREF+    | AN               | _              | ADC Voltage Reference input.                 |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                | C1IN0-   | AN               | —              | Comparator C2 negative input.                |

| RA2/AN2/DAC1OUT2/ZCD/<br>TOCKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> RA2         TTL/ST         CMOS         General purpose I/O.           AN2         AN         —         ADC Channel 2 input.         DAC10UT2         —         AN         Digital-to-Analog Converter output.           ZCD         —         AN         Digital-to-Analog Converter output.         Color         Color         AN         Zero Cross Detection Current Source/Sink.           TOCKI         TTL/ST         —         AN         Zero Cross Detection Current Source/Sink.           TOCKI         TTL/ST         —         Complementary Output Generator input.           INT         TTL/ST         —         External interrupt.           RA3/MCLR/VPP         RA3         TTL/ST         CMOS         General purpose input.           MCLR         ST         —         Master Clear with internal pull-up.           VPP         HV         —         Programming voltage.           RA4/AN3/T1G <sup>(1)</sup> /SOSCO/         RA4         TTL/ST         CMOS         General purpose I/O.           OSC2/CLKOUT         RA4         TTL/ST         —         Timer1 gate input.           SOSCO         XTAL         XTAL         Secondary Oscillator Connection.           CLKOUT         —         CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                | C2IN0-   | AN               | —              | Comparator C3 negative input.                |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                | ICSPCLK  | ST               |                | Serial Programming Clock.                    |

| $ \begin{array}{ c c c c c } \hline ANZ & AN & - & ANC & Criatiner input. \\ \hline DAC1OUT2 & - & AN & Digital-to-Analog Converter output. \\ \hline DAC1OUT2 & - & AN & Zero Cross Detection Current Source/Sink. \\ \hline TOCKI & TTL/ST & - & Timer0 clock input. \\ \hline COGIN & TTL/ST & - & Complementary Output Generator input. \\ \hline COGIN & TTL/ST & - & External interrupt. \\ \hline RA3/MCLR/VPP & RA3 & TTL/ST & CMOS & General purpose input. \\ \hline MCLR & ST & - & Master Clear with internal pull-up. \\ \hline VPP & HV & - & Programming voltage. \\ \hline RA4/AN3/T1G^{(1)} SOSCO' & RA4 & TTL/ST & CMOS & General purpose I/O. \\ \hline OSC2/CLKOUT & RA3 & AN & - & ADC Channel 3 input. \\ \hline T1G & TTL/ST & - & Timer1 gate input. \\ \hline SOSCO & XTAL & XTAL & Secondary Oscillator Connection. \\ \hline OSC2 & - & XTAL & Crystal/Resonator (LP, XT, HS modes). \\ \hline CLCIN3^{(1)} OSC1/CLKIN & & RA5 & TTL/ST & CMOS & General purpose I/O. \\ \hline AN3 & ATL & XTAL & Secondary Oscillator Connection. \\ \hline OSC2 & - & XTAL & Crystal/Resonator (LP, XT, HS modes). \\ \hline CLCIN3^{(1)} OSC1/CLKIN & & & TTL/ST & - & Timer1 clock input. \\ \hline SOSCI & XTAL & XTAL & Secondary Oscillator Connection. \\ \hline CLCIN3 & TTL/ST & - & Configurable Logic Cell source input. \\ \hline SOSCI & XTAL & XTAL & Secondary Oscillator Connection. \\ \hline CLCIN3 & TTL/ST & - & & Configurable Logic Cell source input. \\ \hline SOSCI & TTL & TTL & Crystal/Resonator (LP, XT, HS modes). \\ \hline CLCIN3 & TTL/ST & - & & Cendarl Oscinput. \\ \hline SOSC1 & - & XTAL & Crystal/Resonator (LP, XT, HS modes). \\ \hline CLCIN3 & TTL/ST & - & & & & & & & & & & & & & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                | RA2      | TTL/ST           | CMOS           | General purpose I/O.                         |

| ZCD         -         AN         Zero Cross Detection Current Source/Sink.           T0CKI         TTL/ST         -         Timer0 clock input.           COGIN         TTL/ST         -         Complementary Output Generator input.           INT         TTL/ST         -         External interrupt.           RA3/MCLR/VPP         RA3         TTL/ST         CMOS           General purpose input.         MCLR         ST         -           MCLR         ST         -         Master Clear with internal pull-up.           VPP         HV         -         Programming voltage.           RA4/AN3/T1G <sup>(1)</sup> /SOSCO/         RA4         TTL/ST         CMOS           SC2/CLKOUT         RA4         TTL/ST         -           AN         AN         -         ADC Channel 3 input.           SOSCO         XTAL         XTAL         Secondary Oscillator Connection.           OSC2         -         XTAL         Secondary Oscillator Connection.           OSC2         -         XTAL         Secondary Oscillator Connection.           OSC2         -         XTAL         Secondary Oscillator Connection.           CLKOUT         -         CMOS         General purpose I/O.           CLKNN <td>T0CKI<sup>(1)</sup>/COGIN<sup>(1)</sup>/INT<sup>(1)</sup></td> <td>AN2</td> <td>AN</td> <td>—</td> <td>ADC Channel 2 input.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | T0CKI <sup>(1)</sup> /COGIN <sup>(1)</sup> /INT <sup>(1)</sup> | AN2      | AN               | —              | ADC Channel 2 input.                         |

| $ \begin{array}{ c c c c c c } \hline \begin{tabular}{ c c c c c } \hline $TCKI $TL/ST $ $Timer0 clock input. $$CKI $TTL/ST $ $$Complementary Output Generator input. $$CKI $TTL/ST $ $$Complementary Output Generator input. $$TTL/ST $ $$Complementary Output Generator input. $$TTL/ST $ $$Complementary Output Generator input. $$TTL/ST $ $$Complementary Output Generator input. $$$Complementary Output Generator input. $$$Complementary Output Generator input. $$$$Complementary Output Generator input. $$$$Complementary Output Generator input. $$$$$$$$Complementary Output Generator input. $$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                | DAC10UT2 | _                | AN             | Digital-to-Analog Converter output.          |

| COGINTTL/ST—Complementary Output Generator input.INTTTL/ST—External interrupt.RA3/MCLR/VPPRA3TTL/STCMOSGeneral purpose input.MCLRST—Master Clear with internal pull-up.VPPHV—Programming voltage.RA4/AN3/T1G <sup>(1)</sup> /SOSCO/<br>OSC2/CLKOUTRA4TTL/STCMOSGeneral purpose I/O.AN3AN—ADC Channel 3 input.T1GTTL/ST—Timer1 gate input.SOSCOXTALXTALSecondary Oscillator Connection.OSC2—XTALCrystal/Resonator (LP, XT, HS modes).CLKOUT—CMOSFosc/4 output.RA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3 <sup>(1)</sup> /OSC1//CLKINRA5TTL/STCMOSRA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3RA5TTL/STCMOSRA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3RA5TTL/STCMOSRA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3RA5TTL/STCMOSCLCIN3TTL/ST—Timer1 clock input.SOSCIXTALXTALSecondary Oscillator Connection.CLCIN3TTL/ST—Configurable Logic Cell source input.OSCI—XTALCrystal/Resonator (LP, XT, HS modes).CLCIN3TTL/ST—Configurable Logic Cell source input.OSCI—XTALCrystal/Resonator (LP, XT, HS modes).CLCIN3TTL/ST—Central Logic Cell source input.OSCI—XTALCrystal/Resonator (LP, XT, HS modes). <td></td> <td>ZCD</td> <td>_</td> <td>AN</td> <td>Zero Cross Detection Current Source/Sink.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                | ZCD      | _                | AN             | Zero Cross Detection Current Source/Sink.    |

| INTTTL/ST—External interrupt.RA3/MCLR/VPPRA3TTL/STCMOSGeneral purpose input.MCLRST—Master Clear with internal pull-up.VPPHV—Programming voltage.RA4/AN3/T1G <sup>(1)</sup> /SOSCO/<br>OSC2/CLKOUTRA4TTL/STCMOSGSC2/CLKOUTRA4TTL/STCMOSGSC2/CLKOUTRA4TTL/ST—AN3AN—ADC Channel 3 input.T1GTTL/ST—Timer1 gate input.SOSCOXTALXTALSecondary Oscillator Connection.OSC2—XTALCrystal/Resonator (LP, XT, HS modes).CLKOUT—CMOSFosc/4 output.RA5/T1CK/I <sup>(1)</sup> /SOSCI/<br>CLCIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/STCMOSCOSCIXTALXTALSOSCIXTALXTALSecondary Oscillator Connection.CLCIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/ST—CLCIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/ST—CLCIN3TTL/ST—Configurable Logic Cell source input.SOSCIXTALXTALSecondary Oscillator Connection.CLCIN3TTL/ST—Configurable Logic Cell source input.OSC1—XTALCrystal/Resonator (LP, XT, HS modes).CLCIN3TTL/ST—General purpose I/O.SCK <sup>(1)</sup> /SCL <sup>(3)</sup> RC0TTL/ST—General purpose I/O.RC0/AN4/C2IN+/OPA1IN+/<br>SCKRC0TTL/ST—General purpose I/O.RC0/AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                | TOCKI    | TTL/ST           | _              | Timer0 clock input.                          |

| RA3/MCLR/VPP         RA3         TTL/ST         CMOS         General purpose input.           MCLR         ST         —         Master Clear with internal pull-up.           VPP         HV         —         Programming voltage.           RA4/AN3/T1G <sup>(1)</sup> /SOSCO/<br>OSC2/CLKOUT         RA4         TTL/ST         CMOS         General purpose I/O.           AN3         AN         —         ADC Channel 3 input.         TIG         TTL/ST         —         Timer1 gate input.           SOSCO         XTAL         XTAL         Secondary Oscillator Connection.         OSC2/CLKOUT         OSC2         —         XTAL         Secondary Oscillator Connection.           SOSCO         XTAL         XTAL         Crystal/Resonator (LP, XT, HS modes).         CLKOUT         —         CMOS         General purpose I/O.           CLKNUT         —         CMOS         General purpose I/O.         TTL/ST         —         Timer1 clock input.           CLCIN3 <sup>(1)</sup> /SOSC1/CLKIN         TTL/ST         —         Timer1 clock input.         SOSCI         XTAL         XTAL         Secondary Oscillator Connection.           CLCIN3 <sup>(1)</sup> /SOSC1/CLKIN         TTL/ST         —         Timer1 clock input.         SOSCI         SOSCI         XTAL         Secondary Oscillator Connection.      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                | COGIN    | TTL/ST           | _              | Complementary Output Generator input.        |

| MCLRST—Master Clear with internal pull-up.VPPHV—Programming voltage.RA4/AN3/T1G <sup>(1)</sup> /SOSCO/<br>OSC2/CLKOUTRA4TTL/STCMOSGeneral purpose I/O.AN3AN—ADC Channel 3 input.T1GTTL/ST—T1GTTL/ST—Timer1 gate input.SOSCOXTALXTALSecondary Oscillator Connection.OSC2—XTALCrystal/Resonator (LP, XT, HS modes).CLKOUT—CMOSFosc/4 output.RA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/ST—RA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3RA5TTL/ST—CCICIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/ST—RA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3TTL/ST—Configurable Logic Cell source input.SOSCIXTALXTALSecondary Oscillator Connection.CLCIN3TTL/ST—Configurable Logic Cell source input.OSC1—XTALCrystal/Resonator (LP, XT, HS modes).CLCIN3TTL/ST—General purpose I/O.CC/AN4/C2IN+/OPA1IN+/<br>SCK <sup>(1)</sup> /SCL <sup>(3)</sup> RC0TTL/ST—RC0/AN4/C2IN+/OPA1IN+/<br>SCK <sup>(1)</sup> /SCL <sup>(3)</sup> AN4AN—AN4AN—ADC Channel 4 input.C2IN+AN—Comparator positive input.OPA1IN+AN—Operational Amplifier 1 non-inverting input.SCKTTL/ST—SPI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                | INT      | TTL/ST           | _              | External interrupt.                          |

| VPPHVProgramming voltage.RA4/AN3/T1G <sup>(1)</sup> /SOSCO/<br>OSC2/CLKOUTRA4TTL/STCMOSGeneral purpose I/O.OSC2/CLKOUTAN3ANADC Channel 3 input.T1GTTL/STTimer1 gate input.SOSCOXTALXTALSecondary Oscillator Connection.OSC2XTALCrystal/Resonator (LP, XT, HS modes).CLKOUTCMOSFosc/4 output.RA5/T1CKI <sup>(1)</sup> /SOSCI/<br>CLCIN3 <sup>(1)</sup> /OSC1/CLKINRA5TTL/STCMOSGOSC1XTALXTALSecondary Oscillator Connection.OSC1TTL/STTimer1 clock input.SOSC1XTALXTALSecondary Oscillator Connection.CLCIN3TTL/STTimer1 clock input.SOSC1XTALXTALSecondary Oscillator Connection.CLCIN3TTL/STConfigurable Logic Cell source input.OSC1XTALCrystal/Resonator (LP, XT, HS modes).CLKINTTL/STExternal clock input (EC mode).RC0/AN4/C2IN+/OPA1IN+/<br>SCK <sup>(1)</sup> /SCL <sup>(3)</sup> RC0TTL/STRC0/AN4/C2IN+/OPA1IN+/<br>SCKAN4ANADCChannel 4 input.C2IN+ANOPA1IN+ANOperational Amplifier 1 non-inverting input.SCKTTL/STSPI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RA3/MCLR/VPP                                                   | RA3      | TTL/ST           | CMOS           | General purpose input.                       |