Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704-i-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

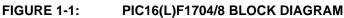

### PIC16(L)F1704/8

### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

### Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device          | Program Memory Space | Last Program Memory | High-Endurance Flash                |  |

|-----------------|----------------------|---------------------|-------------------------------------|--|

|                 | (Words)              | Address             | Memory Address Range <sup>(1)</sup> |  |

| PIC16(L)F1704/8 | 4,096                | 0FFFh               | 0F80h - 0FFFh                       |  |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1704/8 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

### 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

| Note 1: | Code    | protection                                          | of | the   | entire | Fla | ash |  |  |

|---------|---------|-----------------------------------------------------|----|-------|--------|-----|-----|--|--|

|         | progra  | m m <u>em</u> ory                                   | ar | ray i | s enab | led | by  |  |  |

|         | clearin | clearing the $\overline{CP}$ bit of Configuration V |    |       |        |     |     |  |  |

### **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

### 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

### 13.0 INTERRUPT-ON-CHANGE

All pins on all ports can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

### 13.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

### 13.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

### 13.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCxF bits.

### 13.4 Clearing Interrupt Flags

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

### 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the affected IOCxF register will be updated prior to the first instruction executed out of Sleep.

### **15.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFVR<1:0> |       | ADFVF | R<1:0> | 151                 |

**Legend:** Shaded cells are unused by the temperature indicator module.

### PIC16(L)F1704/8

### 16.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 16-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Zero latency filter

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 16-2) contains Control bits for the following:

- Interrupt enable

- · Interrupt edge polarity

- Positive input channel selection

- Negative input channel selection

### 16.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 16.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · Desired pin PPS control

- Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 16.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 16-2 shows the output state versus input conditions, including polarity control.

# TABLE 16-2:COMPARATOR OUTPUT<br/>STATE VS. INPUT<br/>CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

### 16.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1', which selects the Normal-Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

### 17.1 **PWMx Pin Configuration**

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

### 17.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

Note: The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

**Note:** The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

### 17.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

### 17.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 17-1.

### EQUATION 17-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$

(TMR2 Prescale Value)

```

Note: Tosc = 1/Fosc

```

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

### 17.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 17-2 is used to calculate the PWM pulse width.

Equation 17-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 17-2: PULSE WIDTH

$Pulse Width = (PWMxDCH:PWMxDCL<7:6>) \bullet$

Tosc • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

### EQUATION 17-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/FOSC, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

### TABLE 19-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |  |

|----------|----------|------------|--|

| 0x55     | 1        | AND        |  |

| 0x55     | 0        | NAND       |  |

| 0xAA     | 1        | NOR        |  |

| 0xAA     | 0        | OR         |  |

| 0x00     | 0        | Logic 0    |  |

| 0x00     | 1        | Logic 1    |  |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- Gate 3: CLCxGLS2 (Register 19-9)

- Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

# PIC16(L)F1704/8

| TABLE 19-3: | SUMMARY OF REGISTERS ASSOCIATED WITH CLCx |

|-------------|-------------------------------------------|

|-------------|-------------------------------------------|

| Name                  | Bit7                  | Bit6                 | Bit5     | Bit4                 | Blt3     | Bit2         | Bit1       | Bit0     | Register<br>on Page |

|-----------------------|-----------------------|----------------------|----------|----------------------|----------|--------------|------------|----------|---------------------|

| ANSELA                | _                     | _                    | _        | ANSA4                | —        | ANSA2        | ANSA1      | ANSA0    | 122                 |

| ANSELB <sup>(1)</sup> | _                     | _                    | ANSB5    | ANSB4                | —        | _            | —          | —        | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup> | ANSC5(2) | ANSC4 <sup>(2)</sup> | ANSC3    | ANSC2        | ANSC1      | ANSC0    | 133                 |

| CLC1CON               | LC1EN                 | _                    | LC10UT   | LC1INTP              | LC1INTN  | L            | C1MODE<2:0 | >        | 207                 |

| CLC2CON               | LC2EN                 | _                    | LC2OUT   | LC2INTP              | LC2INTN  | L            | C2MODE<2:0 | >        | 207                 |

| CLC3CON               | LC3EN                 | _                    | LC3OUT   | LC3INTP              | LC3INTN  | L            | C3MODE<2:0 | >        | 207                 |

| CLCDATA               | _                     | _                    | _        | _                    | _        | MLC3OUT      | MLC2OUT    | MLC10UT  | 215                 |

| CLC1GLS0              | LC1G1D4T              | LC1G1D4N             | LC1G1D3T | LC1G1D3N             | LC1G1D2T | LC1G1D2N     | LC1G1D1T   | LC1G1D1N | 211                 |

| CLC1GLS1              | LC1G2D4T              | LC1G2D4N             | LC1G2D3T | LC1G2D3N             | LC1G2D2T | LC1G2D2N     | LC1G2D1T   | LC1G2D1N | 212                 |

| CLC1GLS2              | LC1G3D4T              | LC1G3D4N             | LC1G3D3T | LC1G3D3N             | LC1G3D2T | LC1G3D2N     | LC1G3D1T   | LC1G3D1N | 213                 |

| CLC1GLS3              | LC1G4D4T              | LC1G4D4N             | LC1G4D3T | LC1G4D3N             | LC1G4D2T | LC1G4D2N     | LC1G4D1T   | LC1G4D1N | 214                 |

| CLC1POL               | LC1POL                | _                    | _        | _                    | LC1G4POL | LC1G3POL     | LC1G2POL   | LC1G1POL | 208                 |

| CLC1SEL0              | -                     | —                    | _        |                      |          | LC1D1S<4:0>  |            |          | 209                 |

| CLC1SEL1              | —                     | —                    | -        |                      |          | LC1D2S<4:0>  |            |          | 209                 |

| CLC1SEL2              | —                     | —                    | -        |                      |          | LC1D3S<4:0>  |            |          | 209                 |

| CLC1SEL3              | _                     | _                    | _        | LC1D4S<4:0>          |          |              |            |          | 210                 |

| CLC2GLS0              | LC2G1D4T              | LC2G1D4N             | LC2G1D3T | LC2G1D3N             | LC2G1D2T | LC2G1D2N     | LC2G1D1T   | LC2G1D1N | 211                 |

| CLC2GLS1              | LC2G2D4T              | LC2G2D4N             | LC2G2D3T | LC2G2D3N             | LC2G2D2T | LC2G2D2N     | LC2G2D1T   | LC2G2D1N | 212                 |

| CLC2GLS2              | LC2G3D4T              | LC2G3D4N             | LC2G3D3T | LC2G3D3N             | LC2G3D2T | LC2G3D2N     | LC2G3D1T   | LC2G3D1N | 213                 |

| CLC2GLS3              | LC2G4D4T              | LC2G4D4N             | LC2G4D3T | LC2G4D3N             | LC2G4D2T | LC2G4D2N     | LC2G4D1T   | LC2G4D1N | 214                 |

| CLC2POL               | LC2POL                | _                    | _        | _                    | LC2G4POL | LC2G3POL     | LC2G2POL   | LC2G1POL | 208                 |

| CLC2SEL0              | _                     | _                    | _        |                      |          | LC2D1S<4:0>  |            |          | 209                 |

| CLC2SEL1              | _                     | _                    | _        |                      |          | LC2D2S<4:0>  |            |          | 209                 |

| CLC2SEL2              | _                     | _                    | _        |                      |          | LC2D3S<4:0>  |            |          | 209                 |

| CLC2SEL3              | _                     | _                    | _        |                      |          | LC2D4S<4:0>  |            |          | 210                 |

| CLC3GLS0              | LC3G1D4T              | LC3G1D4N             | LC3G1D3T | LC3G1D3N             | LC3G1D2T | LC3G1D2N     | LC3G1D1T   | LC3G1D1N | 211                 |

| CLC3GLS1              | LC3G2D4T              | LC3G2D4N             | LC3G2D3T | LC3G2D3N             | LC3G2D2T | LC3G2D2N     | LC3G2D1T   | LC3G2D1N | 212                 |

| CLC3GLS2              | LC3G3D4T              | LC3G3D4N             | LC3G3D3T | LC3G3D3N             | LC3G3D2T | LC3G3D2N     | LC3G3D1T   | LC3G3D1N | 213                 |

| CLC3GLS3              | LC3G4D4T              | LC3G4D4N             | LC3G4D3T | LC3G4D3N             | LC3G4D2T | LC3G4D2N     | LC3G4D1T   | LC3G4D1N | 214                 |

| CLC3POL               | LC3POL                | _                    | _        | _                    | LC3G4POL | LC3G3POL     | LC3G2POL   | LC3G1POL | 208                 |

| CLC3SEL0              | _                     | _                    | _        |                      | •        | LC3D1S<4:0>  | •          |          | 209                 |

| CLC3SEL1              | _                     | _                    | _        |                      |          | LC3D2S<4:0>  |            |          | 209                 |

| CLC3SEL2              | —                     | —                    | -        |                      |          | LC3D3S<4:0>  |            |          | 209                 |

| CLC3SEL3              | _                     | —                    | _        |                      |          | LC3D4S<4:0>  |            |          | 210                 |

| CLCxPPS               | —                     | —                    | _        |                      |          | CLCxPPS<4:0> |            |          | 138, 139            |

| INTCON                | GIE                   | PEIE                 | TMR0IE   | INTE                 | IOCIE    | TMR0IF       | INTF       | IOCIF    | 85                  |

| PIE3                  | —                     | —                    | COGIE    | ZCDIE                | —        | CLC3IE       | CLC2IE     | CLC1IE   | 88                  |

| PIR3                  | —                     | —                    | COGIF    | ZCDIF                | —        | CLC3IF       | CLC2IF     | CLC1IF   | 91                  |

| RxyPPS                | _                     | —                    | _        |                      |          | RxyPPS<4:0>  |            |          | 140                 |

| TRISA                 | _                     | _                    | TRISA5   | TRISA4               | (3)      | TRISA2       | TRISA1     | TRISA0   | 121                 |

| TRISB <sup>(4)</sup>  | TRISB7                | TRISB6               | TRISB5   | TRISB4               | _        | _            | —          | —        | 127                 |

| TRISC                 | TRISC7 <sup>(4)</sup> | TRISC6(4)            | TRISC5   | TRISC4               | TRISC3   | TRISC2       | TRISC1     | TRISC0   | 132                 |

– = unimplemented read as '0'. Shaded cells are not used for CLC module.

PIC16(L)F1708 only. Legend: Note 1:

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

### 23.9 Register Definitions: ZCD Control

### REGISTER 23-1: ZCDxCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-0/0         | U-0             | R-x/x                                                      | R/W-0/0            | U-0              | U-0                | R/W-0/0          | R/W-0/0      |  |  |  |

|-----------------|-----------------|------------------------------------------------------------|--------------------|------------------|--------------------|------------------|--------------|--|--|--|

| ZCDxEN          | —               | ZCDxOUT                                                    | ZCDxPOL            | —                | —                  | ZCDxINTP         | ZCDxINTN     |  |  |  |

| bit 7           | ·               |                                                            |                    |                  |                    |                  | bit 0        |  |  |  |

|                 |                 |                                                            |                    |                  |                    |                  |              |  |  |  |

| Legend:         |                 |                                                            |                    |                  |                    |                  |              |  |  |  |

| R = Readabl     | le bit          | W = Writable                                               | bit                | U = Unimpler     | mented bit, read   | l as '0'         |              |  |  |  |

| u = Bit is und  | changed         | x = Bit is unkr                                            | nown               | -n/n = Value a   | at POR and BO      | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is se | et              | '0' = Bit is cle                                           | ared               | q = value dep    | ends on config     | uration bits     |              |  |  |  |

|                 |                 |                                                            |                    |                  |                    |                  |              |  |  |  |

| oit 7           |                 | ro-Cross Detec                                             |                    |                  |                    |                  |              |  |  |  |

|                 |                 |                                                            |                    |                  | utput to source    |                  |              |  |  |  |

|                 |                 |                                                            | •                  | n operates acc   | ording to PPS a    | and TRIS contr   | OIS.         |  |  |  |

| oit 6           | •               | ted: Read as '                                             |                    |                  |                    |                  |              |  |  |  |

| oit 5           |                 | ero-Cross Dete                                             | ection Logic Le    | evel bit         |                    |                  |              |  |  |  |

|                 |                 | <u>ZCDxPOL bit = 0</u> :<br>1 = ZCD pin is sinking current |                    |                  |                    |                  |              |  |  |  |

|                 |                 | is sourcing cure                                           |                    |                  |                    |                  |              |  |  |  |

|                 | ZCDxPOL bit     | •                                                          |                    |                  |                    |                  |              |  |  |  |

|                 |                 |                                                            | s sourcing current |                  |                    |                  |              |  |  |  |

|                 | •               | is sinking curre                                           |                    |                  |                    |                  |              |  |  |  |

| bit 4           |                 | ero-Cross Dete<br>c output is inve                         |                    | utput Polarity b | Dit                |                  |              |  |  |  |

|                 | 0               | c output is inve                                           |                    |                  |                    |                  |              |  |  |  |

| bit 3-2         | 0               | ted: Read as '                                             |                    |                  |                    |                  |              |  |  |  |

| bit 1           | -               | ero-Cross Pos                                              |                    | errupt Enable b  | bit                |                  |              |  |  |  |

|                 |                 | t is set on low-                                           | •                  | •                |                    |                  |              |  |  |  |

|                 | 0 = ZCDIF bi    | t is unaffected                                            | by low-to-high     | n ZCDx_output    | transition         |                  |              |  |  |  |

| pit 0           | ZCDxINTN: Z     | Zero-Cross Neg                                             | ative Edge In      | terrupt Enable   | bit                |                  |              |  |  |  |

|                 |                 | t is set on high                                           |                    |                  |                    |                  |              |  |  |  |

|                 |                 | t is unaffected                                            |                    | — ·              |                    |                  |              |  |  |  |

| Note 1: T       | he ZCDxEN bit h | as no effect wh                                            | en the ZCDD        | IS Configuration | on bit is cleared. |                  |              |  |  |  |

| TABLE 23-1: SU | JMMARY OF REGISTERS | <b>ASSOCIATED WITH</b> | THE ZCD MODULE |

|----------------|---------------------|------------------------|----------------|

|----------------|---------------------|------------------------|----------------|

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|-------|---------|---------|-------|-------|----------|----------|---------------------|

| PIE3    | —      | —     | COGIE   | ZCDIE   | _     | —     | —        | —        | 88                  |

| PIR3    | —      | _     | CWGIF   | ZCDIF   | _     | _     | —        | _        | 91                  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL |       |       | ZCD1INTP | ZCD1INTN | 241                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

### TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | —       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 51                  |

|         | 7:0  | ZCDDIS  | _       | _        | _        | _        | _        | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

### 27.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 25.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

### 27.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

|       |                                         |

### 27.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 27-1 demonstrates the code to perform this function.

### EXAMPLE 27-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point<br>;to CCPxCON |

|---------|-------------|----------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                   |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                   |

|         |             | ;the new prescaler                     |

|         |             | ;move value and CCP ON                 |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this                |

|         |             | ;value                                 |

### 27.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

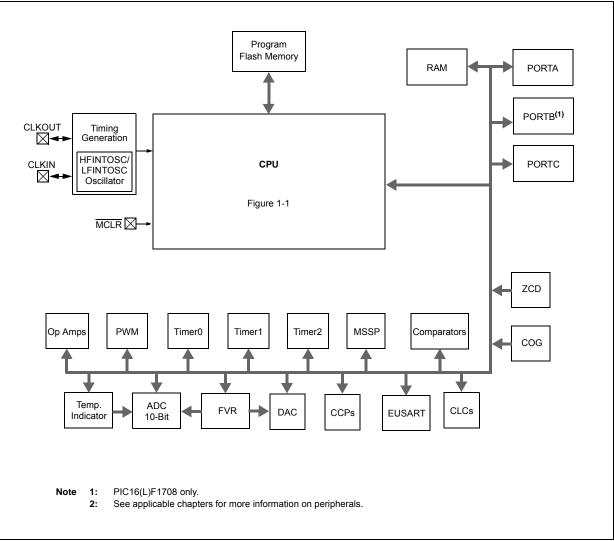

### 27.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 27-2 shows a simplified diagram of the compare operation.

### COMPARE MODE OPERATION BLOCK DIAGRAM

### 28.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

### 28.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 28-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

### 28.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with SS pir<br>control enabled (SSPCON1<3:0> =<br>0100), the SPI module will reset if the SS<br>pin is set to VDD. |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SS}$ pin control.                                               |  |  |

**3:** While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

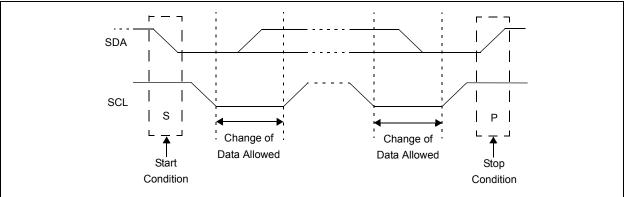

### 28.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 28-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

### 28.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

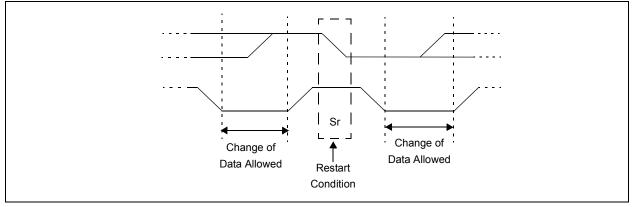

### 28.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 28-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with R/W clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with R/W clear, or high address match fails.

### 28.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

### FIGURE 28-12: I<sup>2</sup>C START AND STOP CONDITIONS

### FIGURE 28-13: I<sup>2</sup>C RESTART CONDITION

### 28.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 28.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### 28.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

### 28.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 28-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPIF bit.

- 4. Slave hardware generates an ACK and sets SSPIF.

- 5. SSPIF bit is cleared by user.

- 6. Software reads the received address from SSPBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

#### 28.5.9 SSP MASK REGISTER

An SSP Mask (SSPMSK) register (Register 28-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

### 28.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

### TABLE 29-3: BAUD RATE FORMULAS

| (    | Configuration Bi | ts   |                     | David Data Farmula |  |  |

|------|------------------|------|---------------------|--------------------|--|--|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Rate Formula  |  |  |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]    |  |  |

| 0    | 0                | 1    | 8-bit/Asynchronous  |                    |  |  |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]    |  |  |

| 0    | 1                | 1    | 16-bit/Asynchronous |                    |  |  |

| 1    | 0                | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]     |  |  |

| 1    | 1                | х    | 16-bit/Synchronous  |                    |  |  |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair.

### TABLE 29-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|----------|-------|-------|-------|--------|-------|-------|-------|---------------------|

| BAUD1CON | ABDOVF   | RCIDL | _     | SCKP  | BRG16  | _     | WUE   | ABDEN | 336                 |

| RC1STA   | SPEN     | RX9   | SREN  | CREN  | ADDEN  | FERR  | OERR  | RX9D  | 335                 |

| SP1BRGL  | BRG<7:0> |       |       |       | 337    |       |       |       |                     |

| SP1BRGH  |          |       |       | BRG<  | <15:8> |       |       |       | 337                 |

| TX1STA   | CSRC     | TX9   | TXEN  | SYNC  | SENDB  | BRGH  | TRMT  | TX9D  | 334                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

### **31.2** Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                              |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                         |

| Operands:        | -32 ≤ k ≤ 31<br>n ∈ [ 0, 1]                                                                      |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |

| Status Affected: | None                                                                                             |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair.          |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

wrap-around.

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                   |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                             |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

| ADDWFC ADD W and CARRY bit to f |

|---------------------------------|

|---------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (W) + (f) + (C) $\rightarrow$ dest                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

### 32.3 DC Characteristics

### TABLE 32-1:SUPPLY VOLTAGE

| PIC16LF1704/8<br>PIC16F1704/8 |        |                                                                       |                 | Standard Operating Conditions (unless otherwise stated) |            |            |                                                                                               |  |  |  |  |

|-------------------------------|--------|-----------------------------------------------------------------------|-----------------|---------------------------------------------------------|------------|------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

|                               |        |                                                                       |                 | Standard Operating Conditions (unless otherwise stated) |            |            |                                                                                               |  |  |  |  |

| Param.<br>No.                 | Sym.   | Characteristic                                                        | Min. Typ.† Max. |                                                         | Units      | Conditions |                                                                                               |  |  |  |  |

| D001                          | Vdd    | Supply Voltage                                                        |                 |                                                         |            |            |                                                                                               |  |  |  |  |

|                               |        | PIC16LF1704/8                                                         | 1.8<br>2.5      |                                                         | 3.6<br>3.6 | V<br>V     | Fosc ≤ 16 MHz<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                              |  |  |  |  |

| D001                          |        | PIC16F1704/8                                                          | 2.3<br>2.5      | _                                                       | 5.5<br>5.5 | V<br>V     | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                             |  |  |  |  |

| D002* VDR                     |        | RAM Data Retention Voltage <sup>(1)</sup>                             |                 |                                                         |            |            |                                                                                               |  |  |  |  |

|                               |        | PIC16LF1704/8                                                         | 1.5             | —                                                       | _          | V          | Device in Sleep mode                                                                          |  |  |  |  |

| D002*                         |        | PIC16F1704/8                                                          | 1.7             | —                                                       | _          | V          | Device in Sleep mode                                                                          |  |  |  |  |

| D002A*                        | VPOR   | Power-on Reset Release Voltage <sup>(3)</sup>                         |                 |                                                         |            |            |                                                                                               |  |  |  |  |

|                               |        | PIC16LF1704/8                                                         | _               | 1.6                                                     | _          | V          |                                                                                               |  |  |  |  |

| D002A*                        |        | PIC16F1704/8                                                          | _               | 1.6                                                     | _          | V          |                                                                                               |  |  |  |  |

| D002B*                        | VPORR* | Power-on Reset Rearm Voltage <sup>(3)</sup>                           | )               |                                                         |            |            |                                                                                               |  |  |  |  |

|                               |        | PIC16LF1704/8                                                         |                 | 0.8                                                     | —          | V          |                                                                                               |  |  |  |  |

| D002B*                        |        | PIC16F1704/8                                                          |                 | 1.5                                                     | —          | V          |                                                                                               |  |  |  |  |

| D003                          | VFVR   | Fixed Voltage Reference Voltage                                       |                 |                                                         |            |            |                                                                                               |  |  |  |  |

|                               |        | 1x gain (1.024 nominal)                                               | -4              | _                                                       | +4         | %          | $VDD \ge 2.5V$ , -40°C to 85°C                                                                |  |  |  |  |

|                               |        | 2x gain (2.048 nominal)                                               | -4              | _                                                       | +4         | %          | VDD $\ge$ 2.5V, -40°C to 85°C                                                                 |  |  |  |  |

|                               |        | 4x gain (4.096 nominal)                                               | -5              | _                                                       | +5         | %          | $V \text{DD} \geq 4.75 \text{V}, \ \text{-}40^\circ \text{C} \ \text{to} \ 85^\circ \text{C}$ |  |  |  |  |

| D004*                         | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal <sup>(2)</sup> | 0.05            | —                                                       | _          | V/ms       | See Section 5.1 "Power-On Reset (POR)" for details.                                           |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ." column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

\*

3: See Figure 32-3: POR and POR Rearm with Slow Rising VDD.

### TABLE 32-8: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated) |          |                                                          |                    |      |       |      |       |                                       |  |

|---------------------------------------------------------|----------|----------------------------------------------------------|--------------------|------|-------|------|-------|---------------------------------------|--|

| Param.<br>No.                                           | Sym.     | Characteristic                                           | Freq.<br>Tolerance | Min. | Typ.† | Max. | Units | Conditions                            |  |

| OS08                                                    | HFosc    | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                |      | 16.0  | I    | MHz   | 3.2V, 25°C                            |  |

| OS08A                                                   | MFosc    | Internal Calibrated MFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                | _    | 500   | -    | kHz   |                                       |  |

| OS09                                                    | LFosc    | Internal LFINTOSC Frequency                              | _                  | _    | 31    | _    | kHz   | $-40^\circ C \le TA \le +125^\circ C$ |  |

| OS10*                                                   | TIOSC ST | HFINTOSC<br>Wake-up from Sleep Start-up Time             | _                  | _    | 3.2   | 8    | μS    |                                       |  |

|                                                         |          | MFINTOSC<br>Wake-up from Sleep Start-up Time             | —                  | _    | 24    | 35   | μS    |                                       |  |

These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

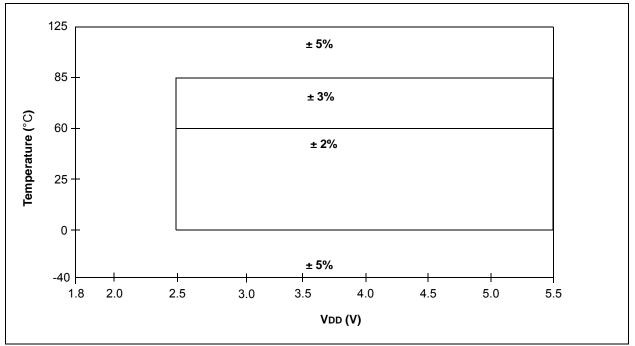

### FIGURE 32-6: HFINTOSC AND MFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

# PIC16(L)F1704/8

### TABLE 32-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No.  | Symbol<br>Thigh                 | Characteristic             |              | Min.       | Max. | Units                                | Conditions                                  |

|----------------|---------------------------------|----------------------------|--------------|------------|------|--------------------------------------|---------------------------------------------|

| SP100*         |                                 | Clock high time            | 100 kHz mode | 4.0        |      | μS                                   | Device must operate at a minimum of 1.5 MHz |

|                |                                 |                            | 400 kHz mode | 0.6        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |

|                |                                 |                            | SSP module   | 1.5 TCY    |      |                                      |                                             |

| SP101*         | SP101* TLOW (                   | Clock low time             | 100 kHz mode | 4.7        | _    | μS                                   | Device must operate at a minimum of 1.5 MHz |

|                |                                 |                            | 400 kHz mode | 1.3        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |

|                |                                 | SSP module                 | 1.5 TCY      | _          | —    |                                      |                                             |

| SP102*         | SP102* TR SDA and SCL rise time | SDA and SCL rise           | 100 kHz mode | _          | 1000 | ns                                   |                                             |

|                |                                 | time                       | 400 kHz mode | 20 + 0.1Св | 300  | ns                                   | CB is specified to be from 10-400 pF        |

| SP103*         | TF                              | SDA and SCL fall           | 100 kHz mode | —          | 250  | ns                                   |                                             |

| tim            | time                            | 400 kHz mode               | 20 + 0.1Св   | 250        | ns   | CB is specified to be from 10-400 pF |                                             |

| SP106* THD:DAT | THD:DAT                         | Data input hold time       | 100 kHz mode | 0          | _    | ns                                   |                                             |

|                |                                 |                            | 400 kHz mode | 0          | 0.9  | μS                                   |                                             |

| SP107*         | TSU:DAT                         | Data input setup<br>time   | 100 kHz mode | 250        |      | ns                                   | (Note 2)                                    |

|                |                                 |                            | 400 kHz mode | 100        | _    | ns                                   |                                             |