Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1704t-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

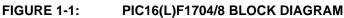

## PIC16(L)F1704/8

| TABLE 1-3: PIC16(L)F1708 PIN OUT DESCRIPTION (CONTINUED |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Name                                               | Function | Input<br>Type    | Output<br>Type | Description                                  |  |  |

|----------------------------------------------------|----------|------------------|----------------|----------------------------------------------|--|--|

| RB5/AN11/OPA1IN+/RX <sup>(1)</sup>                 | RB5      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | AN11     | AN               | _              | ADC Channel 11 input.                        |  |  |

|                                                    | OPA1IN+  | AN               | _              | Operational Amplifier 1 non-inverting input. |  |  |

|                                                    | RX       | ST               | _              | USART asynchronous input.                    |  |  |

| RB6/SDI <sup>(1)</sup> /SCL <sup>(3)</sup>         | RB6      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | SDI      | CMOS             |                | SPI data input.                              |  |  |

|                                                    | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                      |  |  |

| RB7/CK <sup>(1)</sup>                              | RB7      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | СК       | ST               | CMOS           | USART synchronous clock.                     |  |  |

| RC0/AN4/C2IN+                                      | RC0      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | AN4      | AN               |                | ADC Channel 4 input.                         |  |  |

|                                                    | C2IN+    | AN               |                | Comparator positive input.                   |  |  |

| RC1/AN5/C1IN1-/C2IN1-/                             | RC1      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| CLCIN2 <sup>(1)</sup>                              | AN5      | AN               | —              | ADC Channel 5 input.                         |  |  |

|                                                    | C1IN1-   | AN               | _              | Comparator C1 negative input.                |  |  |

|                                                    | C2IN1-   | AN               | _              | Comparator C2 negative input.                |  |  |

|                                                    | CLCIN2   | ST               | _              | Configurable Logic Cell source input.        |  |  |

| RC2/AN6/C1IN2-/C2IN2-/                             | RC2      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| OPA1OUT                                            | AN6      | AN               |                | ADC Channel 6 input.                         |  |  |

|                                                    | C1IN2-   | AN               |                | Comparator C1 negative input.                |  |  |

|                                                    | C2IN2-   | AN               |                | Comparator C2 negative input.                |  |  |

|                                                    | OPA1OUT  | _                | AN             | Operational Amplifier 1 output.              |  |  |

| RC3/AN7/C1IN3-/C2IN3-/                             | RC3      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| OPA2OUT/CCP2 <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> | AN7      | AN               |                | ADC Channel 7 input.                         |  |  |

|                                                    | C1IN3-   | AN               | _              | Comparator C1 negative input.                |  |  |

|                                                    | C2IN3-   | AN               |                | Comparator C2 negative input.                |  |  |

|                                                    | OPA2OUT  | _                | AN             | Operational Amplifier 2 output.              |  |  |

|                                                    | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                        |  |  |

|                                                    | CLCIN0   | ST               | _              | Configurable Logic Cell source input.        |  |  |

| RC4/CLCIN1 <sup>(1)</sup>                          | RC4      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | CLCIN1   | ST               | _              | Configurable Logic Cell source input.        |  |  |

| RC5/CCP1 <sup>(1)</sup>                            | RC5      |                  | CMOS           | General purpose I/O.                         |  |  |

|                                                    | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                        |  |  |

| RC6/AN8/OPA2IN-/SS <sup>(1)</sup>                  | RC6      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | AN8      | AN               | _              | ADC Channel 8 input.                         |  |  |

|                                                    | OPA2IN-  | AN               |                | Operational Amplifier 2 inverting input.     |  |  |

|                                                    | SS       | ST               |                | Slave Select input.                          |  |  |

| RC7/AN9/OPA2IN+                                    | RC7      | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                                                    | AN9      | AN               |                | ADC Channel 9 input.                         |  |  |

|                                                    | OPA2IN+  | AN               |                | Operational Amplifier 2 non-inverting input. |  |  |

| VDD                                                | VDD      | Power            |                | Positive supply.                             |  |  |

| Legend: AN = Analog input or                       |          |                  |                |                                              |  |  |

XTAL = Crystal levels

= Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-3.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

HV = High Voltage

#### TABLE 3-3:PIC16(L)F1704 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h | Core Registers<br>(Table 3-2) | 080h | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h | Core Registers<br>(Table 3-2) | 280h | Core Registers<br>(Table 3-2) | 300h | Core Registers<br>(Table 3-2) | 380h | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | WPUA                          | 28Ch | ODCONA                        | 30Ch | SLRCONA                       | 38Ch | INLVLA                        |

| 00Dh |                               | 08Dh | -                             | 10Dh | -                             | 18Dh | _                             | 20Dh | _                             | 28Dh | _                             | 30Dh | _                             | 38Dh | _                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | WPUC                          | 28Eh | ODCONC                        | 30Eh | SLRCONC                       | 38Eh | INLVLC                        |

| 00Fh | -                             | 08Fh | -                             | 10Fh | -                             | 18Fh | —                             | 20Fh | —                             | 28Fh | —                             | 30Fh | —                             | 38Fh | _                             |

| 010h | -                             | 090h | -                             | 110h | -                             | 190h | —                             | 210h | —                             | 290h | —                             | 310h | —                             | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h | SSP1BUF                       | 291h | CCPR1L                        | 311h | —                             | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h | SSP1ADD                       | 292h | CCPR1H                        | 312h | —                             | 392h | IOCAN                         |

| 013h | PIR3                          | 093h | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h | SSP1MSK                       | 293h | CCP1CON                       | 313h | —                             | 393h | IOCAF                         |

| 014h | -                             | 094h | -                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h | SSP1STAT                      | 294h | —                             | 314h | _                             | 394h | _                             |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h | SSP1CON                       | 295h | _                             | 315h | —                             | 395h | —                             |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h | SSP1CON2                      | 296h |                               | 316h | —                             | 396h | —                             |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h | SSP1CON3                      | 297h | _                             | 317h | _                             | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | DAC1CON0                      | 198h | _                             | 218h | _                             | 298h | CCPR2L                        | 318h | _                             | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | DAC1CON1                      | 199h | RC1REG                        | 219h | _                             | 299h | CCPR2H                        | 319h | _                             | 399h | IOCCF                         |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | _                             | 19Ah | TX1REG                        | 21Ah | —                             | 29Ah | CCP2CON                       | 31Ah | _                             | 39Ah | _                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | _                             | 19Bh | SP1BRGL                       | 21Bh | —                             | 29Bh | —                             | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | ZCD1CON                       | 19Ch | SP1BRGH                       | 21Ch | —                             | 29Ch | —                             | 31Ch | —                             | 39Ch | _                             |

| 01Dh | —                             | 09Dh | ADCON0                        | 11Dh | —                             | 19Dh | RC1STA                        | 21Dh | —                             | 29Dh | —                             | 31Dh | —                             | 39Dh |                               |

| 01Eh | _                             | 09Eh | ADCON1                        | 11Eh | —                             | 19Eh | TX1STA                        | 21Eh | —                             | 29Eh | CCPTMRS                       | 31Eh | —                             | 39Eh |                               |

| 01Fh |                               | 09Fh | ADCON2                        | 11Fh |                               | 19Fh | BAUD1CON                      | 21Fh |                               | 29Fh | _                             | 31Fh | _                             | 39Fh | _                             |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h | General Purpose               | 3A0h |                               |

|      | <b>.</b> .                    |      | <b>a</b> .                    |      | <b>a</b>                      |      | <b>A</b> 1                    |      | <u> </u>                      |      | <b>.</b> .                    |      | Register                      |      |                               |

|      | General<br>Purpose            | 32Fh | 16 Bytes                      |      | Unimplemented                 |

|      | Register                      | 330h |                               |      | Read as '0'                   |

|      | 80 Bytes                      |      | Unimplemented                 |      |                               |

|      | -                             |      | -                             |      | -                             |      | -                             |      | -                             |      | -                             |      | Read as '0'                   |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h |                               | 170h |                               | 1F0h |                               | 270h |                               | 2F0h |                               | 370h |                               | 3F0h |                               |

|      | Common RAM<br>70h – 7Fh       |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| 075  | 1011 - 1711                   | 0551 | /011 - / F11                  |      | /011 - / F11                  | 4551 | 1011 - 1711                   | 075  | 1011 - 1711                   | 055  | /011-/11                      | 075  | /011-/11                      | 0551 | 1011 - 1711                   |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                               | 27Fh |                               | 2FFh |                               | 37Fh |                               | 3FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1704.

### 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-9 can be addressed from any Bank.

| Addr            | Name      | Bit 7                                      | Bit 6                                                    | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all<br>other Resets |

|-----------------|-----------|--------------------------------------------|----------------------------------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|------------------------------|

| Bank            | Bank 0-31 |                                            |                                                          |               |              |             |               |        |       |                      |                              |

| x00h or<br>x80h | INDF0     |                                            | this location ical register)                             |               | nts of FSR0H | /FSR0L to a | ddress data r | memory |       | XXXX XXXX            | uuuu uuuu                    |

| x01h or<br>x81h | INDF1     |                                            | this location ical register)                             |               | nts of FSR1H | /FSR1L to a | ddress data r | memory |       | xxxx xxxx            | uuuu uuuu                    |

| x02h or<br>x82h | PCL       | Program Co                                 | ounter (PC)                                              | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                    |

| x03h or<br>x83h | STATUS    | —                                          | _                                                        | -             | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                       |

| x04h or<br>x84h | FSR0L     | Indirect Data Memory Address 0 Low Pointer |                                                          |               |              |             |               |        |       | 0000 0000            | uuuu uuuu                    |

| x05h or<br>x85h | FSR0H     | Indirect Dat                               | Indirect Data Memory Address 0 High Pointer              |               |              |             |               |        |       |                      | 0000 0000                    |

| x06h or<br>x86h | FSR1L     | Indirect Dat                               | Indirect Data Memory Address 1 Low Pointer               |               |              |             |               |        |       |                      | uuuu uuuu                    |

| x07h or<br>x87h | FSR1H     | Indirect Dat                               | ta Memory A                                              | ddress 1 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                    |

| x08h or<br>x88h | BSR       | _                                          | _                                                        | _             | BSR4         | BSR3        | BSR2          | BSR1   | BSR0  | 0 0000               | 0 0000                       |

| x09h or<br>x89h | WREG      | Working Register                           |                                                          |               |              |             |               |        |       | 0000 0000            | uuuu uuuu                    |

| x0Ahor<br>x8Ah  | PCLATH    | _                                          | Write Buffer for the upper 7 bits of the Program Counter |               |              |             |               |        |       | -000 0000            | -000 0000                    |

| x0Bhor<br>x8Bh  | INTCON    | GIE                                        | PEIE                                                     | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                    |

#### TABLE 3-9: CORE FUNCTION REGISTERS SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

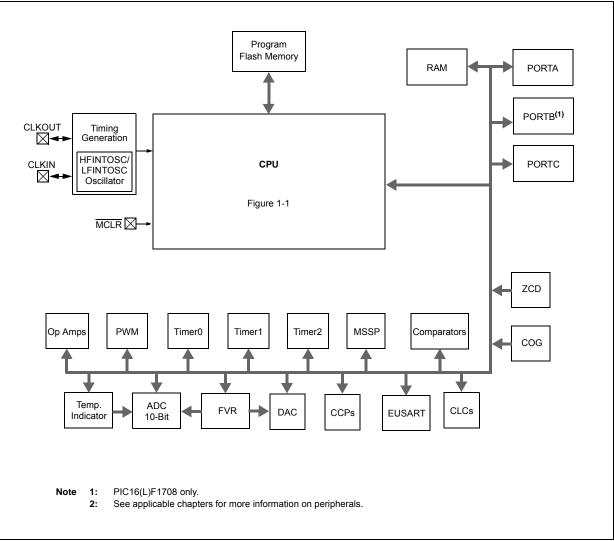

#### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

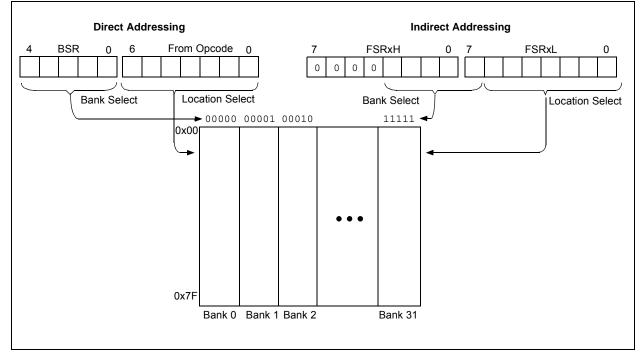

#### 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

#### FIGURE 7-1: INTERRUPT LOGIC

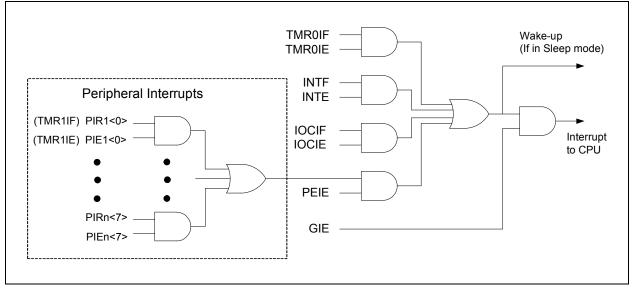

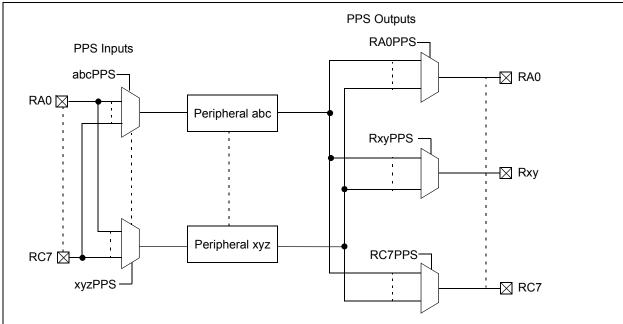

#### 12.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 12-1.

#### 12.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has associated analog functions, the ANSEL bit for that pin must be cleared to enable the digital input buffer. Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 12-1 for PIC16(L)F1704 devices and Register 12-2 for PIC16(L)F1708 devices.

| Note: | The notation "xxx" in the register name is    |

|-------|-----------------------------------------------|

|       | a place holder for the peripheral identifier. |

|       | For example, CLC1PPS.                         |

#### 12.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- · COG (auto-shutdown)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 12-3.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

#### FIGURE 12-1: SIMPLIFIED PPS BLOCK DIAGRAM

## PIC16(L)F1704/8

#### 16.11 Register Definitions: Comparator Control

#### REGISTER 16-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0          | R-0/0                                                                             | U-0                                    | R/W-0/0           | R/W-0/0                                           | R/W-1/1          | R/W-0/0       | R/W-0/0      |  |  |  |

|------------------|-----------------------------------------------------------------------------------|----------------------------------------|-------------------|---------------------------------------------------|------------------|---------------|--------------|--|--|--|

| CxON             | CxOUT                                                                             | —                                      | CxPOL             | CxZLF                                             | CxSP             | CxHYS         | CxSYNC       |  |  |  |

| bit 7            | ·                                                                                 |                                        |                   |                                                   |                  | ÷             | bit 0        |  |  |  |

| Legend:          |                                                                                   |                                        |                   |                                                   |                  |               |              |  |  |  |

| R = Readable     | e bit                                                                             | W = Writable                           | e bit             | U = Unimpler                                      | nented bit, read | d as '0'      |              |  |  |  |

| u = Bit is unc   | hanged                                                                            | x = Bit is unk                         | nown              | -n/n = Value at POR and BOR/Value at all other Re |                  |               |              |  |  |  |

| '1' = Bit is set |                                                                                   |                                        |                   |                                                   |                  |               |              |  |  |  |

|                  |                                                                                   |                                        |                   |                                                   |                  |               |              |  |  |  |

| bit 7            | CxON: Com                                                                         | parator Enable                         | bit               |                                                   |                  |               |              |  |  |  |

|                  |                                                                                   | ator is enabled                        |                   |                                                   |                  |               |              |  |  |  |

| <b>h</b> :+ C    |                                                                                   |                                        | and consumes      | no active pow                                     | er               |               |              |  |  |  |

| bit 6            |                                                                                   | mparator Outpu<br>1 (inverted pola     |                   |                                                   |                  |               |              |  |  |  |

|                  | 1 = CxVP <                                                                        | •                                      | <u>inty).</u>     |                                                   |                  |               |              |  |  |  |

|                  | 0 = CxVP >                                                                        |                                        |                   |                                                   |                  |               |              |  |  |  |

|                  | <u>lf CxPOL = (</u><br>1 = CxVP >                                                 | ) (non-inverted                        | <u>polarity):</u> |                                                   |                  |               |              |  |  |  |

|                  | 1 = CXVP > 0 = CXVP < 0 = CXVP < 0 = CXVP < 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 | -                                      |                   |                                                   |                  |               |              |  |  |  |

| bit 5            | Unimpleme                                                                         | nted: Read as                          | <b>'</b> 0'       |                                                   |                  |               |              |  |  |  |

| bit 4            | CxPOL: Co                                                                         | mparator Outpu                         | ut Polarity Selec | t bit                                             |                  |               |              |  |  |  |

|                  |                                                                                   | ator output is ir                      |                   |                                                   |                  |               |              |  |  |  |

|                  |                                                                                   | ator output is n                       |                   |                                                   |                  |               |              |  |  |  |

| bit 3            |                                                                                   | •                                      | atency Filter E   | hable bit                                         |                  |               |              |  |  |  |

|                  |                                                                                   | ator output is fil<br>ator output is u |                   |                                                   |                  |               |              |  |  |  |

| bit 2            | -                                                                                 | •                                      | Power Select b    | it                                                |                  |               |              |  |  |  |

|                  |                                                                                   |                                        | n normal power,   |                                                   | mode             |               |              |  |  |  |

|                  |                                                                                   | •                                      | n low-power, low  | -                                                 |                  |               |              |  |  |  |

| bit 1            |                                                                                   |                                        | resis Enable bi   | t                                                 |                  |               |              |  |  |  |

|                  |                                                                                   | rator hysteresis<br>rator hysteresis   |                   |                                                   |                  |               |              |  |  |  |

| bit 0            | •                                                                                 | •                                      | put Synchronou    | is Mode hit                                       |                  |               |              |  |  |  |

|                  |                                                                                   |                                        | Timer1 and I/C    |                                                   | onous to chan    | ues on Timer1 | clock source |  |  |  |

|                  |                                                                                   |                                        | falling edge of   |                                                   |                  | ,,            |              |  |  |  |

|                  | 0 = Compa                                                                         | rator output to -                      | Timer1 and I/O    | nin is sevnehro                                   | noue             |               |              |  |  |  |

#### 18.1.4 HALF-BRIDGE MODE

In half-bridge mode, the COG generates a two output complementary PWM waveform from rising and falling event sources. In the simplest configuration, the rising and falling event sources are the same signal, which is a PWM signal with the desired period and duty cycle. The COG converts this single PWM input into a dual complementary PWM output. The frequency and duty cycle of the dual PWM output match those of the single input PWM signal. The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time immediately after the PWM transition where neither output is driven. This is referred to as dead time and is covered in **Section 18.5 "Dead-Band Control"**.

A typical operating waveform, with dead-band, generated from a single CCP1 input is shown in Figure 18-9.

The primary output can be steered to either or both COGxA and COGxC. The complementary output can be steered to either or both COGxB and COGxD.

Half-Bridge mode is selected by setting the GxMD bits of the COGxCON0 register to '100'.

#### 18.1.5 PUSH-PULL MODE

In Push-Pull mode, the COG generates a single PWM output that alternates, every PWM period, between the two pairs of the COG outputs. COGxA has the same signal as COGxC. COGxB has the same signal as COGxD. The output drive activates with the rising input event and terminates with the falling event input. Each rising event starts a new period and causes the output to switch to the COG pair not used in the previous period.

The push-pull configuration is shown in Figure 18-6. A typical push-pull waveform generated from a single CCP1 input is shown in Figure 18-11.

Push-Pull mode is selected by setting the GxMD bits of the COGxCON0 register to '101'.

#### 18.1.6 EVENT DRIVEN PWM (ALL MODES)

Besides generating PWM and complementary outputs from a single PWM input, the COG can also generate PWM waveforms from a periodic rising event and a separate falling event. In this case, the falling event is usually derived from analog feedback within the external PWM driver circuit. In this configuration, high power switching transients may trigger a false falling event that needs to be blanked out. The COG can be configured to blank falling (and rising) event inputs for a period of time immediately following the rising (and falling) event drive output. This is referred to as input blanking and is covered in **Section 18.6 "Blanking Control"**. It may be necessary to guard against the possibility of circuit faults. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 18.8 "Auto-shutdown Control"**.

The COG can be configured to operate in phase delayed conjunction with another PWM. The active drive cycle is delayed from the rising event by a phase delay timer. Phase delay is covered in more detail in **Section 18.7 "Phase Delay"**.

A typical operating waveform, with phase delay and dead-band, generated from a single CCP1 input is shown in Figure 18-10.

#### 18.2 Clock Sources

The COG\_clock is used as the reference clock to the various timers in the peripheral. Timers that use the COG\_clock include:

- Rising and falling dead-band time

- Rising and falling blanking time

- · Rising and falling event phase delay

Clock sources available for selection include:

- 8 MHz HFINTOSC (active during Sleep)

- Instruction clock (Fosc/4)

- System clock (Fosc)

The clock source is selected with the GxCS<1:0> bits of the COGxCON0 register (Register 18-1).

#### 18.3 Selectable Event Sources

The COG uses any combination of independently selectable event sources to generate the complementary waveform. Sources fall into two categories:

- Rising event sources

- · Falling event sources

The rising event sources are selected by setting bits in the COGxRIS register (Register 18-3). The falling event sources are selected by setting bits in the COGxFIS register (Register 18-5). All selected sources are 'OR'd together to generate the corresponding event signal. Refer to Figure 18-7.

#### 18.3.1 EDGE VS. LEVEL SENSING

Event input detection may be selected as level or edge sensitive. The detection mode is individually selectable for every source. Rising source detection modes are selected with the COGxRSIM register (Register 18-4). Falling source detection modes are selected with the COGxFSIM register (Register 18-6). A set bit enables edge detection for the corresponding event source. A cleared bit enables level detection.

In general, events that are driven from a periodic source should be edge detected and events that are derived from voltage thresholds at the target circuit should be level sensitive. Consider the following two examples:

1. The first example is an application in which the period is determined by a 50% duty cycle clock and the COG output duty cycle is determined by a voltage level fed back through a comparator. If the clock input is level sensitive, duty cycles less than 50% will exhibit erratic operation.

2. The second example is similar to the first except that the duty cycle is close to 100%. The feedback comparator high-to-low transition trips the COG drive off, but almost immediately the period source turns the drive back on. If the off cycle is short enough, the comparator input may not reach the low side of the hysteresis band precluding an output change. The comparator output stays low and without a high-to-low transition to trigger the edge sense, the drive of the COG output will be stuck in a constant drive-on condition. See Figure 18-14.

#### FIGURE 18-14: EDGE VS LEVEL SENSE

| Rising (CCP1)   |

|-----------------|

| Falling (C1OUT) |

| C1IN- hyst I    |

| COGOUT          |

| Edge Sensitive  |

| Rising (CCP1)   |

| Falling (C1OUT) |

| C1IN- hyst      |

| COGOUT          |

| Level Sensitive |

#### 18.3.2 RISING EVENT

The rising event starts the PWM output active duty cycle period. The rising event is the low-to-high transition of the rising\_event output. When the rising event phase delay and dead-band time values are zero, the primary output starts immediately. Otherwise, the primary output is delayed. The rising event source causes all the following actions:

- · Start rising event phase delay counter (if enabled).

- · Clear complementary output after phase delay.

- Start falling event input blanking (if enabled).

- · Start dead-band delay (if enabled).

- Set primary output after dead-band delay expires.

#### 18.3.3 FALLING EVENT

The falling event terminates the PWM output active duty cycle period. The falling event is the high-to-low transition of the falling\_event output. When the falling event phase delay and dead-band time values are zero, the complementary output starts immediately. Otherwise, the complementary output is delayed. The falling event source causes all the following actions:

- Start falling event phase delay counter (if enabled).

- · Clear primary output.

- · Start rising event input blanking (if enabled).

- · Start falling event dead-band delay (if enabled).

- Set complementary output after dead-band delay expires.

#### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

#### TABLE 19-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- Gate 3: CLCxGLS2 (Register 19-9)

- Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

#### 23.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The ZCDxOUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The ZCDxOUT bit is affected by the polarity bit.

#### 23.3 ZCD Logic Polarity

The ZCDxPOL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the ZCDxPOL bit is set, a ZCDxOUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The ZCDxPOL bit affects the ZCD interrupts. See **Section 23.4 "ZCD Interrupts"**.

#### 23.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The ZCDxINTP enables rising edge interrupts and the ZCDxINTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- · ZCDIE bit of the PIE3 register

- ZCDxINTP bit of the ZCDxCON register (for a rising edge detection)

- ZCDxINTN bit of the ZCDxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

Changing the ZCDxPOL bit will cause an interrupt, regardless of the level of the ZCDxEN bit.

The ZCDIF bit of the PIR3 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

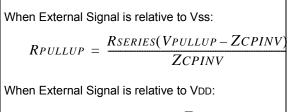

#### 23.5 Correcting for ZCPINV offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms, other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late. When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 23-2.

#### EQUATION 23-2: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{ZCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{V_{DD}-ZCPINV}{V_{PEAK}}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the ZCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 23-3 or Equation 23-4.

#### EQUATION 23-3: ZCD PULL-UP/DOWN

$$R_{PULLDOWN} = \frac{R_{SERIES}(ZCPINV)}{(VDD - ZCPINV)}$$

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

| Note: | The Timer postscaler (see Section 26.1 |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|

|       | "Timer2 Operation") is not used in the |  |  |  |  |  |  |

|       | determination of the PWM frequency.    |  |  |  |  |  |  |

#### 27.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 27-2 is used to calculate the PWM pulse width.

Equation 27-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 27-2: PULSE WIDTH

$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

#### EQUATION 27-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 27-4).

#### 27.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 27-4.

#### EQUATION 27-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + I)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### 28.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 28-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPIF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See **Section 28.5.6.2** "10-bit Addressing Mode" for more detail.

28.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 28-14 and Figure 28-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPIF bit.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPIF bit.

- 10. Software clears SSPIF.

- 11. Software reads the received byte from SSPBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPSTAT, and the bus goes idle.

#### 28.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus™ that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 28-16 displays a module using both address and data holding. Figure 28-17 includes the operation with the SEN bit of the SSPCON2 register set.

- 1. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPIF.

- Slave can look at the ACKTIM bit of the SSPCON3 register to determine if the SSPIF was after or before the ACK.

- 5. Slave reads the address value from SSPBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPIF.

Note: SSPIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPIF not set

- 11. SSPIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

| R/W-1/1                               | R/W-1/1                                                          | R/W-1/1         | R/W-1/1         | R/W-1/1                                               | R/W-1/1                         | R/W-1/1       | R/W-1/1 |  |  |  |

|---------------------------------------|------------------------------------------------------------------|-----------------|-----------------|-------------------------------------------------------|---------------------------------|---------------|---------|--|--|--|

|                                       |                                                                  |                 | MSK             | <<7:0>                                                |                                 |               |         |  |  |  |

| bit 7                                 |                                                                  |                 |                 |                                                       |                                 |               | bit 0   |  |  |  |

|                                       |                                                                  |                 |                 |                                                       |                                 |               |         |  |  |  |

| Legend:                               |                                                                  |                 |                 |                                                       |                                 |               |         |  |  |  |

| R = Readab                            | le bit                                                           | W = Writable    | bit             | U = Unimplemented bit, read as '0'                    |                                 |               |         |  |  |  |

| u = Bit is und                        | changed                                                          | x = Bit is unki | nown            | -n/n = Value at POR and BOR/Value at all other Resets |                                 |               |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                  |                 |                 |                                                       |                                 |               |         |  |  |  |

|                                       |                                                                  |                 |                 |                                                       |                                 |               |         |  |  |  |

| bit 7-1                               | MSK<7:1>:                                                        |                 |                 |                                                       |                                 |               |         |  |  |  |

|                                       | 1 = The rec                                                      | eived address b | it n is compai  | red to SSPADD                                         | <n> to detect I<sup>2</sup></n> | C address mat | tch     |  |  |  |

|                                       | 0 = The rec                                                      | eived address b | it n is not use | ed to detect I <sup>2</sup> C                         | address match                   |               |         |  |  |  |

| bit 0                                 | MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address |                 |                 |                                                       |                                 |               |         |  |  |  |

#### REGISTER 28-5: SSP1MSK: SSP MASK REGISTER

| I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111): | 0 |

|-------------------------------------------------------------------------|---|

|-------------------------------------------------------------------------|---|

1 = The received address bit 0 is compared to SSPADD<0> to detect I<sup>2</sup>C address match

0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

#### REGISTER 28-6: SSP1ADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| ADD<7:0> |         |         |         |         |         |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |  |  |

|---------|-------------------------------------------------|--|--|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |  |  |

#### <u> 10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode – Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

| bit 7-1 | ADD<7:1>: 7-bit address |

|---------|-------------------------|

|         |                         |

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## PIC16(L)F1704/8

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |  |  |  |  |

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Syntax:          | [label] BRA label                                                                                                                                                                                                                               | Syntax:       |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                                        | Operands:     |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255                                                                                                                                                                                                           |               |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                                            | Operation:    |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   | Status Affect |

| Status Affected: | None                                                                                                                                                                                                                                            | Description:  |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |               |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |  |  |  |

# BRW Relative Branch with W Syntax: [/abe/]BRW Operands: None

| Operands:        | None                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [label]BSF f,b                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |

#### TABLE 32-17: OPERATIONAL AMPLIFIER (OPA)

|               | Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C, OPAxSP = 1 (High GBWP mode) |                              |      |      |      |         |            |  |

|---------------|---------------------------------------------------------------------------------------------------------------|------------------------------|------|------|------|---------|------------|--|

| Param.<br>No. | Symbol                                                                                                        | Parameters                   | Min. | Тур. | Max. | Units   | Conditions |  |

| OPA01*        | GBWP                                                                                                          | Gain Bandwidth Product       | —    | 3.5  | _    | MHz     |            |  |

| OPA02*        | Ton                                                                                                           | Turn on Time                 | —    | 10   | _    | μS      |            |  |

| OPA03*        | Рм                                                                                                            | Phase Margin                 | —    | 40   | —    | degrees |            |  |

| OPA04*        | Sr                                                                                                            | Slew Rate                    | —    | 3    | —    | V/μs    |            |  |

| OPA05         | Off                                                                                                           | Offset                       | —    | ±3   | ±9   | mV      |            |  |

| OPA06         | CMRR                                                                                                          | Common Mode Rejection Ratio  | 52   | 70   | —    | dB      |            |  |

| OPA07*        | Aol                                                                                                           | Open Loop Gain               | —    | 90   | _    | dB      |            |  |

| OPA08         | VICM                                                                                                          | Common Mode Input Voltage    | 0    | _    | Vdd  | V       | VDD > 2.5V |  |

| OPA09*        | PSRR                                                                                                          | Power Supply Rejection Ratio | —    | 80   |      | dB      |            |  |

\* These parameters are characterized but not tested.

#### TABLE 32-18: COMPARATOR SPECIFICATIONS

| VDD = 3.0    | V, TA = 25°           | Conditions (unless otherwise s<br>C<br>C and AC Characteristics Graph |      | harts" f | or opera | ating cha | racterization.                                                 |

|--------------|-----------------------|-----------------------------------------------------------------------|------|----------|----------|-----------|----------------------------------------------------------------|

| Param<br>No. | Sym.                  | Characteristics                                                       | Min. | Тур.     | Max.     | Units     | Comments                                                       |

| CM01         | VIOFF                 | Input Offset Voltage                                                  | —    | ±2.5     | ±5       | mV        | Normal-Power mode<br>measured at VDD/2                         |

| CM02         | VICM                  | Input Common Mode Voltage                                             | 0    | _        | Vdd      | V         |                                                                |

| CM03         | CMRR                  | Common Mode Rejection Ratio                                           | 40   | 50       |          | dB        |                                                                |

| CM04A        |                       | Response Time Rising Edge                                             | —    | 60       | 125      | ns        | Normal-Power mode measured at VDD/2 (Note1)                    |