Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1708-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-6**: PIC16(L)F1704/8 MEMORY MAP, BANK 24-31

= Unimplemented data memory locations, read as '0'.

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh |                               | C8Bh |                               | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| C0Ch | —                             | C8Ch | _                             | D0Ch | —                             | D8Ch | _                             | E0Ch |                               | E8Ch |                               | F0Ch |                               | F8Ch |                               |

| C0Dh | —                             | C8Dh | _                             | D0Dh | _                             | D8Dh | _                             | E0Dh |                               | E8Dh |                               | F0Dh |                               | F8Dh |                               |

| C0Eh | —                             | C8Eh | —                             | D0Eh | —                             | D8Eh | _                             | E0Eh |                               | E8Eh |                               | F0Eh |                               | F8Eh |                               |

| C0Fh | —                             | C8Fh | —                             | D0Fh | —                             | D8Fh | _                             | E0Fh |                               | E8Fh |                               | F0Fh |                               | F8Fh |                               |

| C10h | —                             | C90h | —                             | D10h | —                             | D90h | _                             | E10h |                               | E90h |                               | F10h |                               | F90h |                               |

| C11h | —                             | C91h | -                             | D11h | -                             | D91h | —                             | E11h |                               | E91h |                               | F11h |                               | F91h |                               |

| C12h | —                             | C92h | _                             | D12h | —                             | D92h | _                             | E12h |                               | E92h |                               | F12h |                               | F92h |                               |

| C13h | —                             | C93h | _                             | D13h | —                             | D93h | _                             | E13h |                               | E93h |                               | F13h |                               | F93h |                               |

| C14h | —                             | C94h | -                             | D14h | -                             | D94h | -                             | E14h |                               | E94h |                               | F14h |                               | F94h |                               |

| C15h | —                             | C95h | -                             | D15h | -                             | D95h | —                             | E15h |                               | E95h |                               | F15h |                               | F95h |                               |

| C16h | —                             | C96h | —                             | D16h | —                             | D96h | _                             | E16h |                               | E96h |                               | F16h |                               | F96h |                               |

| C17h | —                             | C97h | —                             | D17h | —                             | D97h | _                             | E17h | See Table 3-7 for             | E97h | See Table 3-7 for             | F17h | See Table 3-7 for             | F97h | See Table 3-8 for             |

| C18h | —                             | C98h | —                             | D18h | —                             | D98h | _                             | E18h | register mapping              | E98h | register mapping              | F18h | register mapping              | F98h | register mapping              |

| C19h | —                             | C99h | _                             | D19h | —                             | D99h | _                             | E19h | details                       | E99h | details                       | F19h | details                       | F99h | details                       |

| C1Ah | —                             | C9Ah | _                             | D1Ah | —                             | D9Ah | _                             | E1Ah |                               | E9Ah |                               | F1Ah |                               | F9Ah |                               |

| C1Bh | —                             | C9Bh | —                             | D1Bh | —                             | D9Bh | —                             | E1Bh |                               | E9Bh |                               | F1Bh |                               | F9Bh |                               |

| C1Ch | —                             | C9Ch | -                             | D1Ch | -                             | D9Ch | —                             | E1Ch |                               | E9Ch |                               | F1Ch |                               | F9Ch |                               |

| C1Dh | —                             | C9Dh | —                             | D1Dh | —                             | D9Dh | _                             | E1Dh |                               | E9Dh |                               | F1Dh |                               | F9Dh |                               |

| C1Eh | —                             | C9Eh | —                             | D1Eh | —                             | D9Eh | _                             | E1Eh |                               | E9Eh |                               | F1Eh |                               | F9Eh |                               |

| C1Fh | —                             | C9Fh | _                             | D1Fh | —                             | D9Fh | _                             | E1Fh |                               | E9Fh |                               | F1Fh |                               | F9Fh |                               |

| C20h |                               | CA0h |                               | D20h |                               | DA0h |                               | E20h |                               | EA0h |                               | F20h |                               | FA0h |                               |

|      | Unimplemented<br>Read as '0'  |      |                               |      |                               |      |                               |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

|      | Accesses<br>70h – 7Fh         |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                               | E7Fh |                               | EFFh |                               | F7Fh |                               | FFFh |                               |

DS40001715D-page 28

© 2013-2015 Microchip Technology Inc.

Legend:

PIC16(L)F1704/8

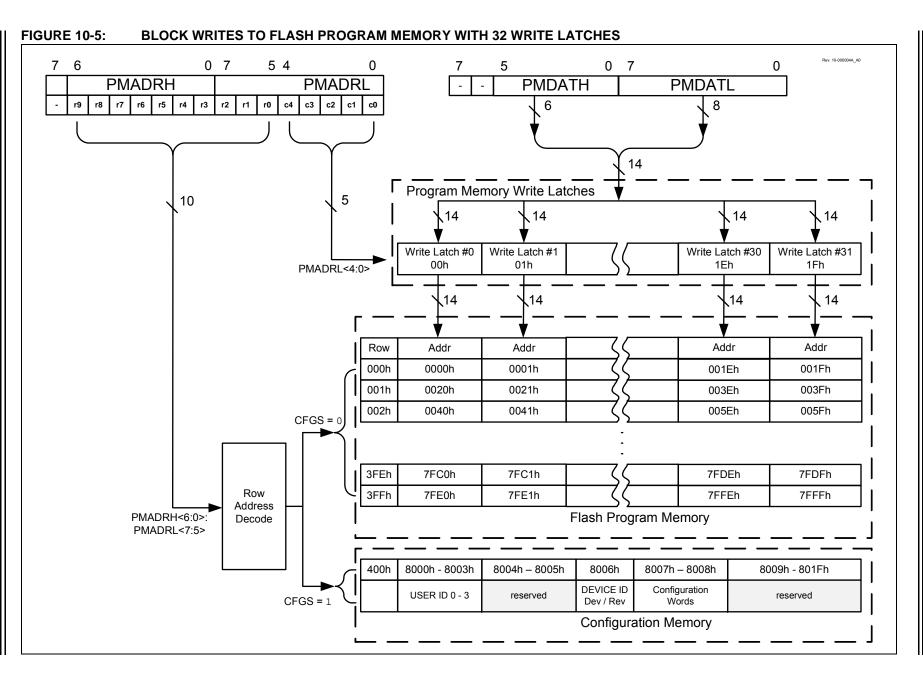

#### 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

| Note 1: | Code    | protection        | of   | the    | entire  | Fla | ash |

|---------|---------|-------------------|------|--------|---------|-----|-----|

|         | progra  | m m <u>em</u> ory | ar   | ray i  | s enab  | led | by  |

|         | clearin | g the CP bit      | of C | Config | uration | Wor | ds. |

#### **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

#### 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

#### REGISTER 16-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | _   | _   | _   | _   | _   | MC2OUT | MC10UT |

| bit 7 |     |     |     |     |     |        | bit 0  |

|       |     |     |     |     |     |        |        |

#### Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 MC2OUT: Mirror Copy of C2OUT bit

bit 0 MC1OUT: Mirror Copy of C1OUT bit

#### TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                  | Bit 7                 | Bit 6                 | Bit 5      | Bit 4                | Bit 3  | Bit 2      | Bit 1  | Bit 0   | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|------------|----------------------|--------|------------|--------|---------|---------------------|

| ANSELA                | —                     | —                     | —          | ANSA4                | _      | ANSA2      | ANSA1  | ANSA0   | 122                 |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5      | ANSB4                | _      | _          | _      | _       | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2)   | ANSC4 <sup>(2)</sup> | ANSC3  | ANSC2      | ANSC1  | ANSC0   | 133                 |

| CM1CON0               | C1ON                  | C1OUT                 | _          | C1POL                | C1ZLF  | C1SP       | C1HYS  | C1SYNC  | 160                 |

| CM2CON0               | C2ON                  | C2OUT                 | —          | C2POL                | C2ZLF  | C2SP       | C2HYS  | C2SYNC  | 160                 |

| CM1CON1               | C1NTP                 | C1INTN                |            | C1PCH<2:0>           |        | C1NCH<2:0> |        |         | 161                 |

| CM2CON1               | C2NTP                 | C2INTN                | C2PCH<2:0> |                      |        | C2NCH<2:0> |        |         |                     |

| CMOUT                 | _                     | _                     | _          | _                    | _      | _          | MC2OUT | MC10UT  | 162                 |

| FVRCON                | FVREN                 | FVRRDY                | TSEN       | TSRNG                | CDAFV  | ′R<1:0>    | ADFV   | R<1:0>  | 151                 |

| DAC1CON0              | DAC1EN                | —                     | DAC10E1    | DAC10E2              | DAC1PS | SS<1:0>    | —      | DAC1NSS | 237                 |

| DAC1CON1              |                       |                       |            | DAC1R                | <7:0>  |            |        |         | 237                 |

| INTCON                | GIE                   | PEIE                  | TMR0IE     | INTE                 | IOCIE  | TMR0IF     | INTF   | IOCIF   | 85                  |

| PIE2                  | OSFIE                 | C2IE                  | C1IE       | —                    | BCL1IE | TMR6IE     | TMR4IE | CCP2IE  | 87                  |

| PIR2                  | OSFIF                 | C2IF                  | C1IF       | _                    | BCL1IF | TMR6IF     | TMR4IF | CCP2IF  | 90                  |

| TRISA                 | —                     | —                     | TRISA5     | TRISA4               | (3)    | TRISA2     | TRISA1 | TRISA0  | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5     | TRISB4               | _      | —          | _      | _       | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5     | TRISC4               | TRISC3 | TRISC2     | TRISC1 | TRISC0  | 132                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0    | R/W-0/0                                | R/W-0/0         | R/W-0/0           | R/W-0/0           | R/W-0/0   | R/W-0/0    |

|------------------|------------|----------------------------------------|-----------------|-------------------|-------------------|-----------|------------|

| GxSDATD          | GxSDATC    | GxSDATB                                | GxSDATA         | GxSTRD            | GxSTRC            | GxSTRB    | GxSTRA     |

| bit 7            | •          |                                        |                 | •                 | •                 |           | bit (      |

|                  |            |                                        |                 |                   |                   |           |            |

| Legend:          | . 1. 1     |                                        | 1.11            |                   | (                 | (0)       |            |

| R = Readable     |            | W = Writable                           |                 | •                 | ented bit, read   |           |            |

| u = Bit is unc   | •          | x = Bit is unkr                        |                 |                   | POR and BOF       |           | ner Resets |

| '1' = Bit is set |            | '0' = Bit is clea                      | ared            | q = Value depe    | ends on condition | on        |            |

| bit 7            | GXSDATD.   | COGxD Static C                         | )utnut Data hit |                   |                   |           |            |

|                  |            | static data is hi                      | •               |                   |                   |           |            |

|                  |            | static data is lo                      | 0               |                   |                   |           |            |

| bit 6            | GxSDATC: ( | COGxC Static C                         | Output Data bit |                   |                   |           |            |

|                  |            | static data is hi                      | 0               |                   |                   |           |            |

|                  | 0 = COGxC  | static data is lo                      | W               |                   |                   |           |            |

| bit 5            | GxSDATB: ( | COGxB Static C                         | Output Data bit |                   |                   |           |            |

|                  |            | static data is hi                      | 0               |                   |                   |           |            |

| L *1 - A         |            | static data is lo                      |                 |                   |                   |           |            |

| bit 4            |            | OGxA Static C                          |                 |                   |                   |           |            |

|                  |            | static data is hi<br>static data is lo | 0               |                   |                   |           |            |

| bit 3            |            | OGxD Steering                          |                 |                   |                   |           |            |

|                  |            | •                                      |                 | orm with polarity | control from G    | xPOLD bit |            |

|                  |            |                                        |                 | letermined by th  |                   |           |            |

| bit 2            | GxSTRC: CO | OGxC Steering                          | Control bit     |                   |                   |           |            |

|                  |            | •                                      |                 | orm with polarity |                   |           |            |

|                  |            | •                                      |                 | letermined by th  | ie GxSDATC bi     | t         |            |

| bit 1            |            | OGxB Steering                          |                 |                   |                   |           |            |

|                  |            |                                        |                 | orm with polarity |                   |           |            |

| <b>h</b> # 0     |            |                                        |                 | letermined by th  | IE GXSDATB DI     | L         |            |

| bit 0            |            | OGxA Steering                          |                 | m with polority   | control from C    |           |            |

|                  |            | oulput has the                         | UUGXA waveld    | orm with polarity | CONTROL ITOM G    |           |            |

#### REGISTER 18-9: COGxSTR: COG STEERING CONTROL REGISTER 1

| Name                  | Bit 7                | Bit 6                | Bit 5    | Bit 4                | Bit 3   | Bit 2       | Bit 1     | Bit 0   | Register<br>on Page |

|-----------------------|----------------------|----------------------|----------|----------------------|---------|-------------|-----------|---------|---------------------|

| ANSELA                | _                    | —                    | _        | ANSA4                | —       | ANSA2       | ANSA1     | ANSA0   | 122                 |

| ANSELB <sup>(1)</sup> | _                    | _                    | ANSB5    | ANSB4                | —       | —           | —         | —       | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup> | ANSC6 <sup>(1)</sup> | ANSC5(2) | ANSC4 <sup>(2)</sup> | ANSC3   | ANSC2       | ANSC1     | ANSC0   | 133                 |

| COG1PHR               |                      | _                    |          |                      | G1PH    | R<5:0>      |           |         | 199                 |

| COG1PHF               |                      | _                    |          |                      | G1PH    | F<5:0>      |           |         | 199                 |

| COG1BLKR              |                      | _                    |          |                      | G1BLK   | R<5:0>      |           |         | 198                 |

| COG1BLKF              |                      | _                    |          |                      | G1BLK   | (F<5:0>     |           |         | 198                 |

| COG1DBR               |                      | _                    |          |                      | G1DB    | R<5:0>      |           |         | 197                 |

| COG1DBF               |                      | _                    |          |                      | G1DB    | F<5:0>      |           |         | 197                 |

| COG1RIS               |                      | G1RIS6               | G1RIS5   | G1RIS4               | G1RIS3  | G1RIS2      | G1RIS1    | G1RIS0  | 190                 |

| COG1RSIM              |                      | G1RSIM6              | G1RSIM5  | G1RSIM4              | G1RSIM3 | G1RSIM2     | G1RSIM1   | G1RSIM0 | 191                 |

| COG1FIS               |                      | G1FIS6               | G1FIS5   | G1FIS4               | G1FIS3  | G1FIS2      | G1FIS1    | G1FIS0  | 192                 |

| COG1FSIM              |                      | G1FSIM6              | G1FSIM5  | G1FSIM4              | G1FSIM3 | G1FSIM2     | G1FSIM1   | G1FSIM0 | 193                 |

| COG1CON0              | G1EN                 | G1LD                 |          | G1CS                 | 6<1:0>  |             | G1MD<2:0> |         | 188                 |

| COG1CON1              | G1RDBS               | G1FDBS               |          |                      | G1POLD  | G1POLC      | G1POLB    | G1POLA  | 189                 |

| COG1ASD0              | G1ASE                | G1ARSEN              | G1ASDI   | 3D<1:0>              | G1ASD/  | AC<1:0>     | —         | —       | 194                 |

| COG1ASD1              |                      | _                    |          |                      | G1AS3E  | G1AS2E      | G1AS1E    | G1AS0E  | 195                 |

| COG1STR               | G1SDATD              | G1SDATC              | G1SDATB  | G1SDATA              | G1STRD  | G1STRC      | G1STRB    | G1STRA  | 196                 |

| INTCON                | GIE                  | PEIE                 | T0IE     | INTE                 | IOCIE   | TOIF        | INTF      | IOCIF   | 85                  |

| COG1PPS               | _                    | —                    | _        |                      | (       | COG1PPS<4:0 | >         |         | 139                 |

| PIE2                  | OSFIE                | C2IE                 | C1IE     | _                    | BCL1IE  | TMR6IE      | TMR4IE    | CCP2IE  | 87                  |

| PIR2                  | OSFIF                | C2IF                 | C1IF     | _                    | BCL1IF  | TMR6IF      | TMR4IF    | CCP2IF  | 90                  |

| RxyPPS                | _                    | _                    | _        |                      |         | RxyPPS<4:0> |           |         | 140                 |

#### TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH COG

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by COG.

**Note 1:** PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

#### 19.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 19-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- · Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

#### 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

#### **19.3 Output Mirror Copies**

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

#### 19.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

#### 19.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 20.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

|         |                                          |

2: The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

#### 20.1.6 RESULT FORMATTING

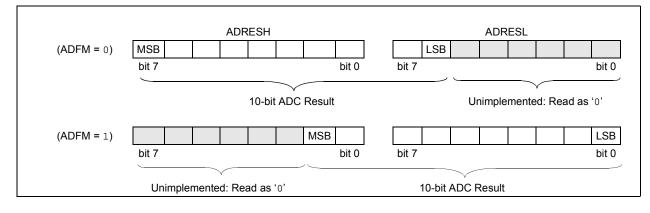

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 20-3 shows the two output formats.

#### FIGURE 20-3: 10-BIT ADC CONVERSION RESULT FORMAT

#### 24.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

#### 24.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |

#### 24.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in Table 32-12: Timer0 and Timer1 External Clock Requirements.

#### 24.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

#### 28.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any SSPBUF register write to the during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSPSTAT register indicates the various Status conditions.

#### 28.6.10 SLEEP OPERATION

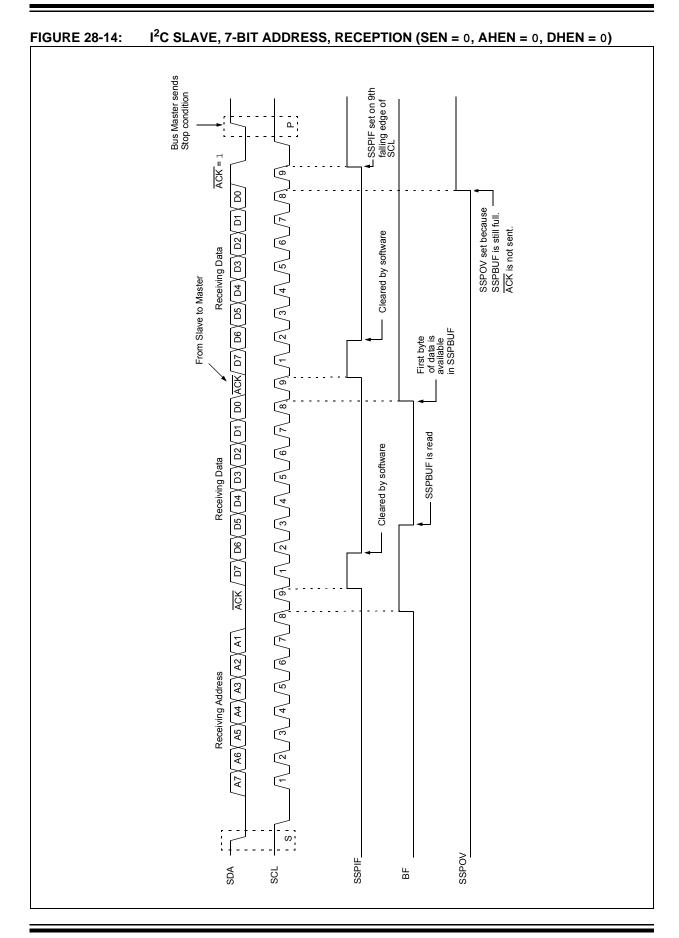

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 28.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 28.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

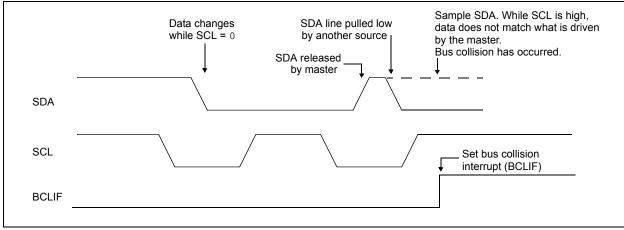

#### 28.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $l^2C$  port to its Idle state (Figure 28-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 28-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

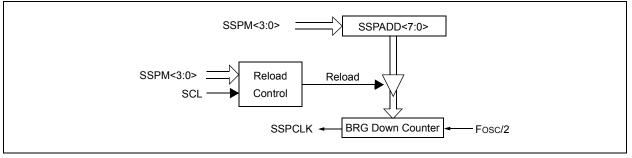

#### 28.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both  $I^2C$  SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Register 28-6). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 28-40 triggers the value from SSPADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module

clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 28-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

$$FCLOCK = \frac{Fosc}{(SSPxADD + 1)(4)}$$

#### FIGURE 28-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### TABLE 28-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 32-4 to ensure the system is designed to support IOL requirements.

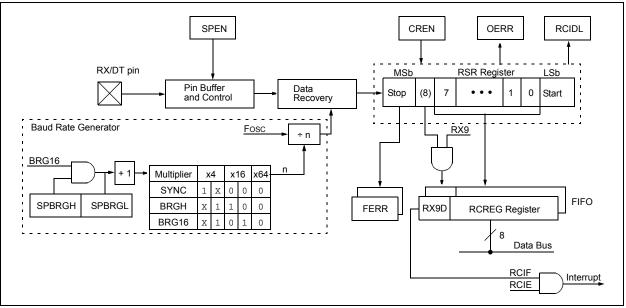

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 29-1, Register 29-2 and Register 29-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

#### 29.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 29-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 29.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 29-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 29.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 29.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 29.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 29.5.1.2 "Clock Polarity"**.

#### 29.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | 0 → (f <b>)</b>                                                     |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Syntax:          | [label] BRA label                                                                                                                                                                                                                               | Syntax:        |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                                        | Operands:      |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255                                                                                                                                                                                                           |                |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                                            | Operation:     |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   | Status Affecte |

| Status Affected: | None                                                                                                                                                                                                                                            | Description:   |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |                |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |

# BRW Relative Branch with W Syntax: [/abe/]BRW Operands: None

| Operands:        | None                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

#### TABLE 32-19: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

#### Standard Operating Conditions (unless otherwise stated)

$VDD = 3.0V, TA = 25^{\circ}C$

See Section 33.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

| Param.<br>No. | Sym. | Characteristics                  | Min. | Тур.    | Max.  | Units | Comments |

|---------------|------|----------------------------------|------|---------|-------|-------|----------|

| DAC01*        | Clsb | Step Size <sup>(1)</sup>         | —    | VDD/256 |       | V     |          |

| DAC02*        | CACC | Absolute Accuracy                | —    | —       | ± 1.5 | LSb   |          |

| DAC03*        | CR   | Unit Resistor Value <sup>®</sup> | _    | 600     | _     | Ω     |          |

| DAC04*        | CST  | Settling Time <sup>(2)</sup>     | —    | —       | 10    | μS    |          |

\* These parameters are characterized but not tested.

Note 1: Comparator hysteresis is available when the CxHYS bit of the CMxCON0 register is enabled.

2: Response time measured with one comparator input at VDD/2 while other input transitions from Vss to VDD.

#### TABLE 32-20: ZERO-CROSS PIN SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = $3.0V$ , TA = $25^{\circ}C$ |        |                            |      |      |      |       |              |

|----------------------------------------------------------------------------------------------|--------|----------------------------|------|------|------|-------|--------------|

| Param.<br>No.                                                                                | Sym.   | Characteristics            | Min. | Тур. | Max. | Units | Comments     |

| ZC01                                                                                         | ZCPINV | Voltage on Zero-Cross Pin  |      | 0.75 |      | V     |              |

| ZC02                                                                                         | ZCSRC  | Source current             | —    | _    | -600 | μA    | ZCPINV = VSS |

| ZC03                                                                                         | ZCSNK  | Sink current               | 600  | _    | _    | μA    | ZCPINV = VDD |

| ZC04*                                                                                        | Zcisw  | Response Time Rising Edge  |      | 1    | _    | μS    |              |

|                                                                                              |        | Response Time Falling Edge | —    | 1    | _    | μS    |              |

| ZC05*                                                                                        | ZCOUT  | Response Time Rising Edge  | —    | 1    | _    | μS    |              |

|                                                                                              |        | Response Time Falling Edge | —    | 1    |      | μS    |              |

\* These parameters are characterized but not tested.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

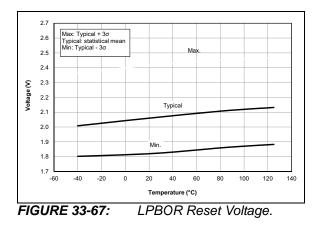

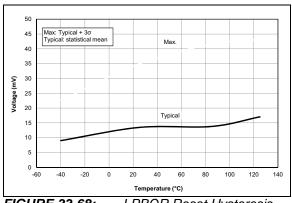

FIGURE 33-68: LPBOR F

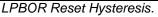

FIGURE 33-69: PWRT Pe PIC16F1704/8 Only.

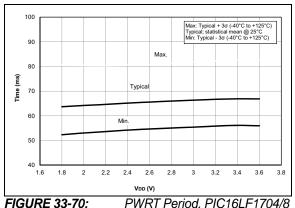

FIGURE 33-70: PWRT Period. PIC16LF1704/8 Only.

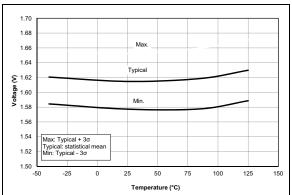

FIGURE 33-71: POR Release Voltage. All devices

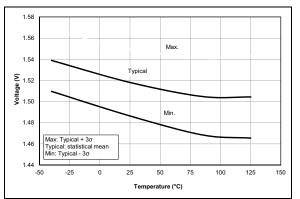

**FIGURE 33-72:** POR Rearm Voltage, Normal Power Mode (VREGPM 1 = 0), PIC16F1704/8 Only.

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

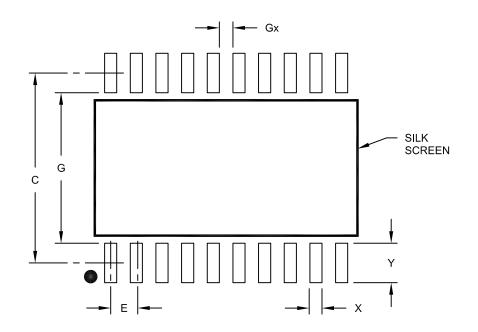

#### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |  |

|--------------------------|-------------|----------|------|------|--|

| Dimensior                | MIN         | NOM      | MAX  |      |  |

| Contact Pitch            | E           | 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С           |          | 9.40 |      |  |

| Contact Pad Width (X20)  | X           |          |      | 0.60 |  |

| Contact Pad Length (X20) | Y           |          |      | 1.95 |  |

| Distance Between Pads    | Gx          | 0.67     |      |      |  |

| Distance Between Pads    | G           | 7.45     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15