# Microchip Technology - PIC16F1708-E/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1708-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-8:PIC16(L)F1704/8 MEMORY<br/>MAP, BANK 31

|         | Bank 31                         |

|---------|---------------------------------|

| F8Ch    | Unimplemented                   |

| FE3h    | Read as '0'                     |

| FE4h    | STATUS_SHAD                     |

| FE5h    | WREG_SHAD                       |

| FE6h    | BSR_SHAD                        |

| FE7h    | PCLATH_SHAD                     |

| FE8h    | FSR0L_SHAD                      |

| FE9h    | FSR0H_SHAD                      |

| FEAh    | FSR1L_SHAD                      |

| FEBh    | FSR1H_SHAD                      |

| FECh    | -                               |

| FEDh    | STKPTR                          |

| FEEh    | TOSL                            |

| FEFh    | TOSH                            |

| Legend: | = Unimplemented da read as '0', |

### 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

## 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3** "**Clock Switching**" for additional information.

### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 6.3 "Clock Switching" for more information.

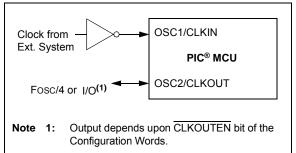

### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| R/W-0/                      | 0 R/W-0/0                           | R/W-0/0                      | U-0            | R/W-0/0       | R/W-0/0                           | R/W-0/0           | R/W-0/0     |

|-----------------------------|-------------------------------------|------------------------------|----------------|---------------|-----------------------------------|-------------------|-------------|

| OSFIF                       | C2IF                                | C1IF                         | _              | BCL1IF        | TMR6IF                            | TMR4IF            | CCP2IF      |

| bit 7                       |                                     |                              |                |               |                                   |                   | bit (       |

|                             |                                     |                              |                |               |                                   |                   |             |

| <b>Legend:</b><br>R = Reada | able bit                            | W = Writable                 |                | II – Unimplor | monted bit read                   | 1 00 '0'          |             |

|                             | inchanged                           | x = Bit is unkr              |                | •             | nented bit, reac<br>at POR and BO |                   | thar Pasate |

| '1' = Bit is                | 0                                   | 0' = Bit is clear            |                |               | at FOR and BO                     | R/ value at all C |             |

| 1 - Di(13                   | 301                                 |                              |                |               |                                   |                   |             |

| bit 7                       | <b>OSFIF:</b> Osci                  | llator Fail Interru          | pt Flag bit    |               |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 6                       |                                     | arator C2 Interru            | ipt Flag bit   |               |                                   |                   |             |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending |                |               |                                   |                   |             |

| bit 5                       | C1IF: Compa                         | arator C1 Interru            | pt Flag bit    |               |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 4                       | Unimplemer                          | nted: Read as '              | )'             |               |                                   |                   |             |

| bit 3                       | BCL1IF: MS                          | SP Bus Collisio              | n Interrupt Fl | ag bit        |                                   |                   |             |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending |                |               |                                   |                   |             |

| bit 2                       | TMR6IF: Tim                         | er6 to PR6 Inte              | rrupt Flag bit | :             |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 1                       |                                     | er4 to PR4 Inte              | rrupt Flag bit | İ             |                                   |                   |             |

|                             | 1 = Interrupt                       | 1 0                          |                |               |                                   |                   |             |

| bit 0                       | -                                   | is not pending               | a hit          |               |                                   |                   |             |

|                             | 1 = Interrupt                       | P2 Interrupt Fla             | y bit          |               |                                   |                   |             |

|                             |                                     | is not pending               |                |               |                                   |                   |             |

| Note:                       | Interrupt flag bits a               |                              |                |               |                                   |                   |             |

|                             | condition occurs, its corresponding |                              |                |               |                                   |                   |             |

|                             | Enable bit, GIE,                    |                              |                |               |                                   |                   |             |

|                             | User software                       | should ensu                  | ire the        |               |                                   |                   |             |

|                             | appropriate intern                  |                              | re clear       |               |                                   |                   |             |

|                             | prior to enabling a                 | an interrupt.                |                |               |                                   |                   |             |

# REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

# 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 22.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 5.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

| Name       | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|-------|--------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA     | —     | —      |         | ANSA4   | -       | ANSA2   | ANSA1   | ANSA0   | 122                 |

| INLVLA     | —     | _      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 124                 |

| LATA       | _     | _      | LATA5   | LATA4   | _       | LATA2   | LATA1   | LATA0   | 122                 |

| ODCONA     | _     | _      | ODA5    | ODA4    | _       | ODA2    | ODA1    | ODA0    | 123                 |

| OPTION_REG | WPUEN | INTEDG | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 244                 |

| PORTA      | —     | _      | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 121                 |

| SLRCONA    | _     | _      | SLRA5   | SLRA4   | _       | SLRA2   | SLRA1   | SLRA0   | 124                 |

| TRISA      | —     | —      | TRISA5  | TRISA4  | _(1)    | TRISA2  | TRISA1  | TRISA0  | 121                 |

| WPUA       | _     | _      | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 123                 |

### TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.**Note 1:**Unimplemented, read as '1'.

#### TABLE 11-3: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2     | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|--------------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0>   |         | _       | 49                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | :0> FOSC<2:0 |         |         | 49                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

| Peripheral | Conditions                                                    | Description                                                 |

|------------|---------------------------------------------------------------|-------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> ≠ 000x                       | INTOSC is active and device is not in Sleep                 |

|            | BOREN<1:0> = 11                                               | BOR always enabled                                          |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                 | BOR disabled in Sleep mode, BOR Fast Start enabled          |

|            | BOREN<1:0> = 01 and BORFS = 1                                 | BOR under software control, BOR Fast Start enabled          |

| LDO        | All PIC16F1704/8 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the ULP regulator when in Sleep mode |

## TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

# 14.3 FVR Buffer Stabilization Period

When either FVR Buffer1 or FVR Buffer2 is enabled, then the buffer amplifier circuits require  $30 \ \mu s$  to stabilize. This stabilization time is still required when the FVR buffer is in operation.

## 16.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 32-18: Comparator Specifications for more information.

# 16.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 25.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

### 16.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 16-2) and the Timer1 Block Diagram (Figure 25-1) for more information.

### 16.5 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0

register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

# 16.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information on the Fixed Voltage Reference module.

See Section 22.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 16.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON0 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- · CxIN- pin

- FVR (Fixed Voltage Reference)

- Analog Ground

Some inverting input selections share a pin with the operational amplifier output function. Enabling both functions at the same time will direct the operational amplifier output to the comparator inverting input.

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

| FIGURE 18-12: | FULL-BRIDGE FORWARD MODE COG OPERATION WITH CCP1 |  |

|---------------|--------------------------------------------------|--|

| CCP1          |                                                  |  |

| COGxA         |                                                  |  |

| COGxB         |                                                  |  |

| COGxC         |                                                  |  |

| COGxD         |                                                  |  |

### FIGURE 18-13: FULL-BRIDGE MODE COG OPERATION WITH CCP1 AND DIRECTION CHANGE

| CCP1  |                           |

|-------|---------------------------|

| COGxA | → Falling_event Dead-Band |

| COGxB |                           |

| COGxC |                           |

| COGxD |                           |

| CxMD0 |                           |

Γ

| R/W-0/0          | R/W-0/0       | U-0               | U-0              | R/W-0/0                            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------------|-------------------|------------------|------------------------------------|------------------|------------------|--------------|

| GxRDBS           | GxFDBS        | —                 | —                | GxPOLD                             | GxPOLC           | GxPOLB           | GxPOLA       |

| bit 7            |               |                   |                  |                                    |                  |                  | bit 0        |

|                  |               |                   |                  |                                    |                  |                  |              |

| Legend:          |               |                   |                  |                                    |                  |                  |              |

| R = Readable     | bit           | W = Writable      | bit              | U = Unimpler                       | mented bit, read | l as '0'         |              |

| u = Bit is unch  | anged         | x = Bit is unkr   | nown             | -n/n = Value a                     | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |               | '0' = Bit is clea | ared             | q = Value dep                      | pends on condit  | ion              |              |

|                  |               |                   |                  |                                    |                  |                  |              |

| bit 7            | GxRDBS: CO    | OGx Rising Eve    | ent Dead-ban     | d Timing Source                    | e Select bit     |                  |              |

|                  |               |                   |                  | ed for dead-ban                    |                  |                  |              |

|                  | —             |                   |                  | ed for dead-bar                    | 00               | ation            |              |

| bit 6            |               | 0                 |                  | d Timing Sourc                     |                  |                  |              |

|                  |               |                   |                  | for dead-band t<br>ed for dead-ban |                  |                  |              |

| bit 5-4          | _             | nted: Read as '   |                  |                                    | ia annig genere  |                  |              |

| bit 3            | -             | DGxD Output P     |                  | ol hit                             |                  |                  |              |

| Site             |               | evel of COGxD     | •                |                                    |                  |                  |              |

|                  |               | evel of COGxD     |                  |                                    |                  |                  |              |

| bit 2            | GxPOLC: CO    | OGxC Output P     | olarity Contro   | ol bit                             |                  |                  |              |

|                  |               | evel of COGxC     |                  |                                    |                  |                  |              |

|                  | 0 = Active le | evel of COGxC     | output is higl   | h                                  |                  |                  |              |

| bit 1            |               | DGxB Output P     | •                |                                    |                  |                  |              |

|                  |               | evel of COGxB     |                  |                                    |                  |                  |              |

| <b>h</b> # 0     |               | evel of COGxB     |                  |                                    |                  |                  |              |

| bit 0            |               | DGxA Output Po    | ,                |                                    |                  |                  |              |

|                  |               | evel of COGxA     |                  |                                    |                  |                  |              |

|                  |               |                   | e alpar lo riigi |                                    |                  |                  |              |

### REGISTER 18-2: COGxCON1: COG CONTROL REGISTER 1

| U-0                       | R/W-0/0                               | R/W-0/0                                                                                                                                        | R/W-0/0           | R/W-0/0          | R/W-0/0            | R/W-0/0           | R/W-0/0          |  |  |  |  |

|---------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|--------------------|-------------------|------------------|--|--|--|--|

| —                         | GxFSIM6                               | GxFSIM5                                                                                                                                        | GxFSIM4           | GxFSIM3          | GxFSIM2            | GxFSIM1           | GxFSIM0          |  |  |  |  |

| bit 7                     |                                       |                                                                                                                                                |                   |                  |                    |                   | bit 0            |  |  |  |  |

|                           |                                       |                                                                                                                                                |                   |                  |                    |                   |                  |  |  |  |  |

| Legend:<br>R = Readable I | oit                                   | W = Writable                                                                                                                                   | bit               | II – Unimplen    | nented bit, read   | ac 'O'            |                  |  |  |  |  |

| u = Bit is uncha          |                                       | x = Bit is unkr                                                                                                                                |                   |                  | at POR and BOF     |                   | har Pasats       |  |  |  |  |

| '1' = Bit is set          | angeu                                 | x = Bit is unki $0' = Bit is clear$                                                                                                            |                   |                  |                    |                   | lei Resels       |  |  |  |  |

| I - DILIS SEL             |                                       |                                                                                                                                                | areu              | q – value dep    | ends on conditi    | 011               |                  |  |  |  |  |

| bit 7                     | Unimplement                           | ted: Read as 'd                                                                                                                                | )'                |                  |                    |                   |                  |  |  |  |  |

| bit 6                     | GxFSIM6: CC                           | Gx Falling Eve                                                                                                                                 | ent Input Sourc   | e 6 Mode bit     |                    |                   |                  |  |  |  |  |

|                           | <u>GxFIS6 = 1:</u>                    |                                                                                                                                                |                   |                  |                    |                   |                  |  |  |  |  |

|                           |                                       |                                                                                                                                                |                   |                  | g event after fall | ing event phase   | e delay          |  |  |  |  |

|                           |                                       | Itput low level                                                                                                                                | will cause an ir  | nmediate falling | g event            |                   |                  |  |  |  |  |

|                           | GxFIS6 = 0:<br>PWM3 output            | has no effect of                                                                                                                               | on falling event  | ł                |                    |                   |                  |  |  |  |  |

| bit 5                     |                                       | )Gx Falling Eve                                                                                                                                | •                 |                  |                    |                   |                  |  |  |  |  |

| bit b                     | GxFIS5 = 1:                           |                                                                                                                                                |                   |                  |                    |                   |                  |  |  |  |  |

|                           |                                       | tput high-to-lov                                                                                                                               | v transition will | cause a falling  | event after falli  | ng event phase    | delay            |  |  |  |  |

|                           |                                       | tput low level w                                                                                                                               | /ill cause an in  | nmediate falling | event              |                   |                  |  |  |  |  |

|                           | GxFIS5 = 0:                           | and the officiation                                                                                                                            | a falling avant   |                  |                    |                   |                  |  |  |  |  |

| h:+ 4                     |                                       | has no effect of                                                                                                                               |                   | a 4 Mada hit     |                    |                   |                  |  |  |  |  |

| bit 4                     | GxFSIM4: CC<br>GxFIS4 = 1:            | Gx Falling Eve                                                                                                                                 | ent input Sourc   | e 4 Mode bit     |                    |                   |                  |  |  |  |  |

|                           |                                       | ih-to-low transi                                                                                                                               | tion will cause   | a falling event  | after falling ever | nt phase delay    |                  |  |  |  |  |

|                           |                                       | CCP1 high-to-low transition will cause a falling event after falling event phase delay<br>CCP1 low level will cause an immediate falling event |                   |                  |                    |                   |                  |  |  |  |  |

|                           | <u>GxFIS4 = 0:</u>                    |                                                                                                                                                |                   |                  |                    |                   |                  |  |  |  |  |

|                           | CCP1 has no                           | effect on falling                                                                                                                              | g event           |                  |                    |                   |                  |  |  |  |  |

| bit 3                     |                                       | Gx Falling Eve                                                                                                                                 | ent Input Sourc   | e 3 Mode bit     |                    |                   |                  |  |  |  |  |

|                           | $\frac{\text{GxFIS3} = 1:}{1 - CLC1}$ | bout bigh to low                                                                                                                               | transition will   | anuna a falling  | avent offer fallin | a avant phase     | dalay            |  |  |  |  |

|                           |                                       |                                                                                                                                                |                   | mediate falling  | event after fallir | ig event phase    | delay            |  |  |  |  |

|                           | <u>GxFIS3 = 0:</u>                    |                                                                                                                                                |                   |                  | ovent              |                   |                  |  |  |  |  |

|                           |                                       | nas no effect or                                                                                                                               | n falling event   |                  |                    |                   |                  |  |  |  |  |

| bit 2                     | GxFSIM2: CC                           | Gx Falling Eve                                                                                                                                 | ent Input Sourc   | e 2 Mode bit     |                    |                   |                  |  |  |  |  |

|                           | <u>GxFIS2 = 1:</u>                    |                                                                                                                                                |                   |                  |                    |                   |                  |  |  |  |  |

|                           |                                       | -                                                                                                                                              |                   |                  | g event after fall | ing event phase   | e delay          |  |  |  |  |

|                           | 0 = Compara GxFIS2 = 0:               | tor 2 low level                                                                                                                                | will cause an il  | mmediate falling | g event            |                   |                  |  |  |  |  |

|                           |                                       | has no effect of                                                                                                                               | on falling event  | t                |                    |                   |                  |  |  |  |  |

| bit 1                     | -                                     | Gx Falling Eve                                                                                                                                 | -                 |                  |                    |                   |                  |  |  |  |  |

|                           | <u>GxFIS1 = 1:</u>                    | 0                                                                                                                                              | ·                 |                  |                    |                   |                  |  |  |  |  |

|                           |                                       |                                                                                                                                                |                   |                  | g event after fall | ing event phase   | e delay          |  |  |  |  |

|                           |                                       | tor 1 low level                                                                                                                                | will cause an ir  | mmediate falling | g event            |                   |                  |  |  |  |  |

|                           | GxFIS1 = 0:<br>Comparator 1           | has no effect of                                                                                                                               | n falling even    | ŀ                |                    |                   |                  |  |  |  |  |

| bit 0                     | •                                     | Gx Falling Eve                                                                                                                                 | •                 |                  |                    |                   |                  |  |  |  |  |

|                           | <u>GxFIS0 = 1:</u>                    |                                                                                                                                                | an input Sould    |                  |                    |                   |                  |  |  |  |  |

|                           |                                       | ted with COGx                                                                                                                                  | PS control high   | gh-to-low transi | tion will cause a  | falling event aft | er falling event |  |  |  |  |

|                           | phase de                              | lay                                                                                                                                            |                   | -                |                    | -                 | <u> </u>         |  |  |  |  |

|                           |                                       | ted with COGx                                                                                                                                  | PPS control lo    | w level will cau | se an immediate    | e falling event   |                  |  |  |  |  |

|                           | GxFIS0 = 0:                           |                                                                                                                                                | control has as    | offoot on fallin | a overt            |                   |                  |  |  |  |  |

|                           | EIL SEIECIED V                        |                                                                                                                                                | CONTROL MAS NO    | effect on fallin | y event            |                   |                  |  |  |  |  |

# REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

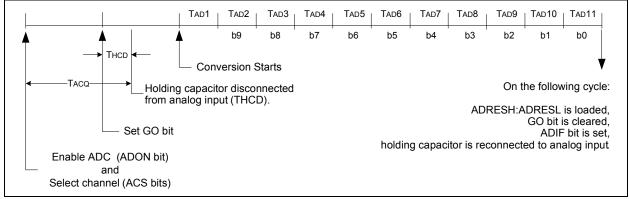

### TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |  |  |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for FRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

# 25.11 Register Definitions: Timer1 Control

Т

# REGISTER 25-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u     | R/W-0/u | R/W-0/u R/W-0/u |  | R/W-0/u | R/W-0/u | U-0   | R/W-0/u |

|-------------|---------|-----------------|--|---------|---------|-------|---------|

| TMR1CS<1:0> |         | T1CKPS<1:0>     |  | T1OSCEN | T1SYNC  | _     | TMR10N  |

| bit 7       |         |                 |  |         |         | bit 0 |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                   |

|---------|------------------------------------------------------------------------------------------------|

|         | 11 = LFINTOSC                                                                                  |

|         | 10 = Timer1 clock source is pin or oscillator:                                                 |

|         | $\frac{ \text{fT10SCEN} = 0}{\text{From T4CK} + \sin(\cos \theta + \sin(\cos \theta + \sin))}$ |

|         | External clock from T1CKI pin (on the rising edge)<br>If T1OSCEN = 1:                          |

|         | Crystal oscillator on SOSCI/SOSCO pins                                                         |

|         | 01 = Timer1 clock source is system clock (Fosc)                                                |

|         | 00 = Timer1 clock source is instruction clock (Fosc/4)                                         |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                           |

|         | 11 = 1:8 Prescale value                                                                        |

|         | 10 = 1:4 Prescale value                                                                        |

|         | 01 = 1:2 Prescale value                                                                        |

|         | 00 = 1:1 Prescale value                                                                        |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit                                                      |

|         | 1 = Dedicated secondary oscillator circuit enabled                                             |

|         | 0 = Dedicated secondary oscillator circuit disabled                                            |

| bit 2   | T1SYNC: Timer1 Synchronization Control bit                                                     |

|         | 1 = Do not synchronize asynchronous clock input                                                |

|         | 0 = Synchronize asynchronous clock input with system clock (Fosc)                              |

| bit 1   | Unimplemented: Read as '0'                                                                     |

| bit 0   | TMR1ON: Timer1 On bit                                                                          |

|         | 1 = Enables Timer1                                                                             |

|         | 0 = Stops Timer1 and clears Timer1 gate flip-flop                                              |

|         |                                                                                                |

## 29.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 29-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 29.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 29-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

### 29.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 29.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

### 29.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 29.5.1.2 "Clock Polarity"**.

### 29.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

| Name                  | Bit 7                        | Bit 6                 | Bit 5    | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|------------------------------|-----------------------|----------|----------|--------|--------|--------|--------|---------------------|

| ANSELA                | —                            | _                     |          | ANSA4    |        | ANSA2  | ANSA1  | ANSA0  | 122                 |

| ANSELB <sup>(1)</sup> | —                            | —                     | ANSB5    | ANSB4    | _      | _      | _      | _      | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>         | ANSC6 <sup>(1)</sup>  | ANSC5(2) | ANSC4(2) | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 133                 |

| BAUD1CON              | ABDOVF                       | RCIDL                 | -        | SCKP     | BRG16  | -      | WUE    | ABDEN  | 336                 |

| INTCON                | GIE                          | PEIE                  | TMR0IE   | INTE     | IOCIE  | TMR0IF | INTF   | IOCIF  | 85                  |

| PIE1                  | TMR1GIE                      | ADIE                  | RCIE     | TXIE     | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 86                  |

| PIR1                  | TMR1GIF                      | ADIF                  | RCIF     | TXIF     | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 89                  |

| RC1REG                | EUSART Receive Data Register |                       |          |          |        |        |        |        | 329*                |

| RC1STA                | SPEN                         | RX9                   | SREN     | CREN     | ADDEN  | FERR   | OERR   | RX9D   | 335                 |

| RxyPPS                | — — — RxyPPS<4:0>            |                       |          |          |        |        |        | 140    |                     |

| SP1BRGL               | BRG<7:0>                     |                       |          |          |        |        |        |        | 337                 |

| SP1BRGH               | BRG<15:8>                    |                       |          |          |        |        |        |        | 337                 |

| TRISA                 | —                            | _                     | TRISA5   | TRISA4   | _(3)   | TRISA2 | TRISA1 | TRISA0 | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                       | TRISB6                | TRISB5   | TRISB4   | _      | —      | —      | —      | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup>        | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4   | TRISC3 | TRISC2 | TRISC1 | TRISA0 | 132                 |

| TX1STA                | CSRC                         | TX9                   | TXEN     | SYNC     | SENDB  | BRGH   | TRMT   | TX9D   | 334                 |

### TABLE 29-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0          | R/W-0/0        | R/W-0/0        | R-0/0            | R-0/0            | R-0/0       |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN             | CREN           | ADDEN          | FERR             | OERR             | RX9D        |  |  |  |

| bit 7            |                                                                                                                                                    |                  |                |                |                  |                  | bit C       |  |  |  |

| <u> </u>         |                                                                                                                                                    |                  |                |                |                  |                  |             |  |  |  |

| Legend:          |                                                                                                                                                    |                  |                |                |                  | (2)              |             |  |  |  |

| R = Readable     |                                                                                                                                                    | W = Writable     |                | -              | nented bit, read |                  |             |  |  |  |

| u = Bit is unch  | anged                                                                                                                                              | x = Bit is unki  |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                    | '0' = Bit is cle | ared           |                |                  |                  |             |  |  |  |

| bit 7            | SDEN. Sorial                                                                                                                                       | Port Enable bi   | +              |                |                  |                  |             |  |  |  |

|                  | SPEN: Serial Port Enable bit<br>1 = Serial port enabled                                                                                            |                  |                |                |                  |                  |             |  |  |  |

|                  |                                                                                                                                                    | rt disabled (he  | ld in Reset)   |                |                  |                  |             |  |  |  |

| bit 6            | -                                                                                                                                                  | ceive Enable I   | -              |                |                  |                  |             |  |  |  |

|                  | 1 = Selects 9                                                                                                                                      |                  |                |                |                  |                  |             |  |  |  |

|                  | 0 = Selects 8                                                                                                                                      | •                |                |                |                  |                  |             |  |  |  |

| bit 5            | SREN: Single                                                                                                                                       | Receive Enal     | ole bit        |                |                  |                  |             |  |  |  |

|                  | Asynchronous                                                                                                                                       | <u>s mode</u> :  |                |                |                  |                  |             |  |  |  |

|                  | Don't care                                                                                                                                         |                  |                |                |                  |                  |             |  |  |  |

|                  | Synchronous mode – Master:                                                                                                                         |                  |                |                |                  |                  |             |  |  |  |

|                  | 1 = Enables single receive                                                                                                                         |                  |                |                |                  |                  |             |  |  |  |

|                  | 0 = Disables single receive                                                                                                                        |                  |                |                |                  |                  |             |  |  |  |

|                  | This bit is cleared after reception is complete.<br><u>Synchronous mode – Slave</u>                                                                |                  |                |                |                  |                  |             |  |  |  |

|                  | Don't care                                                                                                                                         |                  |                |                |                  |                  |             |  |  |  |

| bit 4            | CREN: Continuous Receive Enable bit                                                                                                                |                  |                |                |                  |                  |             |  |  |  |

|                  | Asynchronous mode:                                                                                                                                 |                  |                |                |                  |                  |             |  |  |  |

|                  | 1 = Enables receiver                                                                                                                               |                  |                |                |                  |                  |             |  |  |  |

|                  | 0 = Disables receiver                                                                                                                              |                  |                |                |                  |                  |             |  |  |  |

|                  | Synchronous mode:                                                                                                                                  |                  |                |                |                  |                  |             |  |  |  |

|                  | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                  |                |                |                  |                  |             |  |  |  |

| bit 3            | ADDEN: Add                                                                                                                                         | ress Detect Er   | able bit       |                |                  |                  |             |  |  |  |

|                  | Asynchronous mode 9-bit (RX9 = 1):                                                                                                                 |                  |                |                |                  |                  |             |  |  |  |

|                  | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                                     |                  |                |                |                  |                  |             |  |  |  |

|                  | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                                                     |                  |                |                |                  |                  |             |  |  |  |

|                  | Asynchronous mode 8-bit (RX9 = $0$ ):                                                                                                              |                  |                |                |                  |                  |             |  |  |  |

|                  | Don't care                                                                                                                                         |                  |                |                |                  |                  |             |  |  |  |

| bit 2            | FERR: Frami                                                                                                                                        | -                |                |                |                  |                  |             |  |  |  |

|                  | 1 = Framing<br>0 = No framir                                                                                                                       |                  | pdated by rea  | iding RCREG r  | egister and reco | eive next valid  | byte)       |  |  |  |

| bit 1            | OERR: Overr                                                                                                                                        | un Error bit     |                |                |                  |                  |             |  |  |  |

|                  | 1 = Overrun = 0 $0 = No overru$                                                                                                                    |                  | leared by clea | ring bit CREN) | 1                |                  |             |  |  |  |

| bit 0            |                                                                                                                                                    |                  |                |                |                  |                  |             |  |  |  |

| bit 0            | RX9D: Ninth I                                                                                                                                      | oit of Received  | Data           |                |                  |                  |             |  |  |  |

# REGISTER 29-2: RC1STA: RECEIVE STATUS AND CONTROL REGISTER

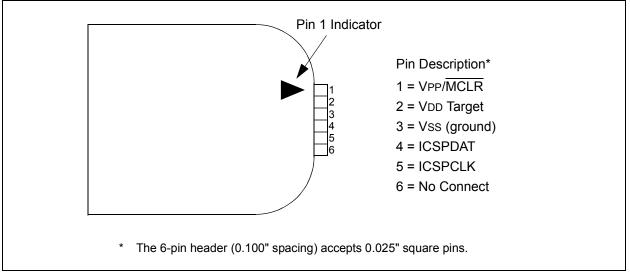

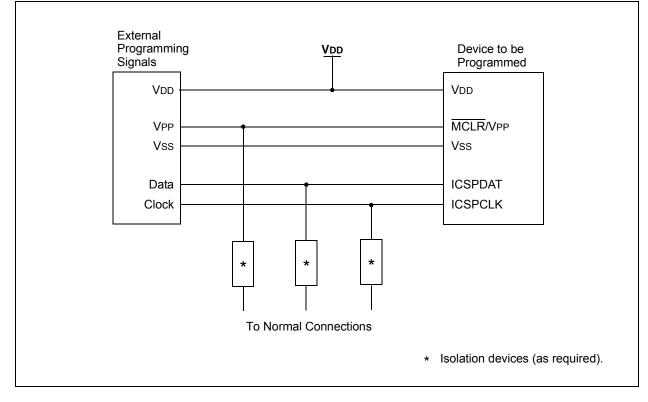

# FIGURE 30-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

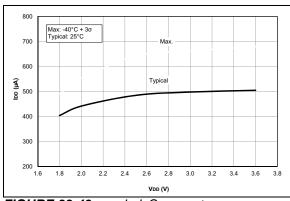

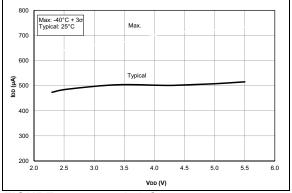

FIGURE 33-49: Ipd, Comparator, Normal-Power Mode (CxSP = 1). PIC16LF1704/8 Only.

FIGURE 33-50: Ipd, Comparator, Normal-Power Mode (CxSP = 1). PIC16F1704/8 Only.

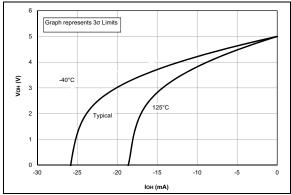

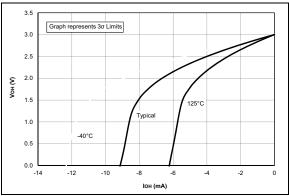

FIGURE 33-51: VOH vs. IOH, Over Temperature, VDD = 5.0V. PIC16F1704/8 Only.

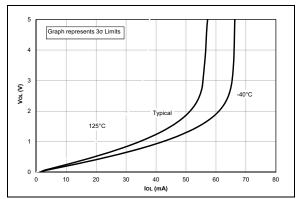

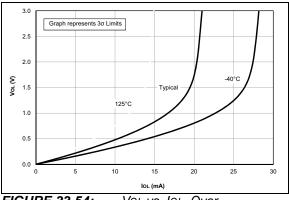

**FIGURE 33-52:** Vol vs. Iol Over Temperature, VDD = 5.0V. PIC16F1704/8 Only.

FIGURE 33-53: VOH vs. IOH, Over Temperature, VDD = 3.0V.

FIGURE 33-54: VOL vs. IOL, Over Temperature, VDD = 3.0V.

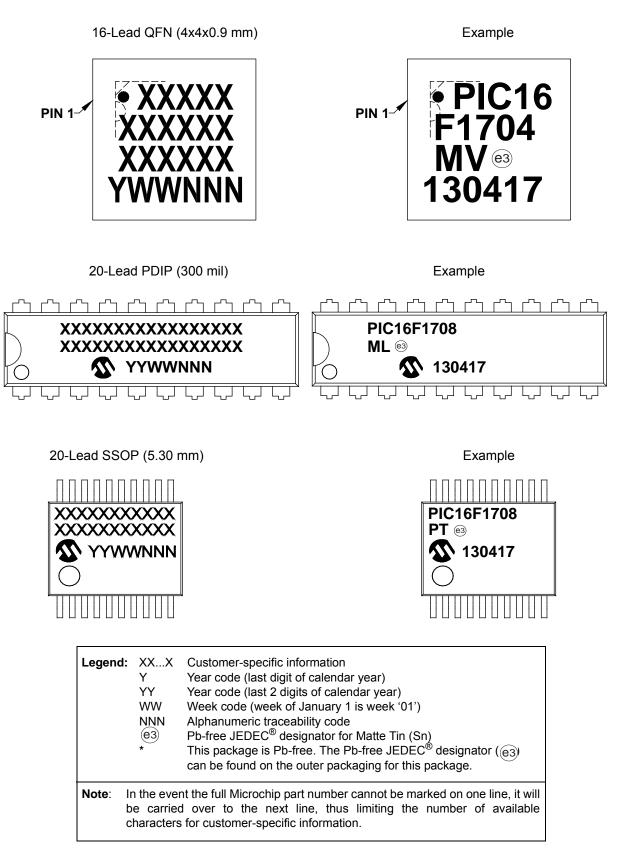

# Package Marking Information (Continued)

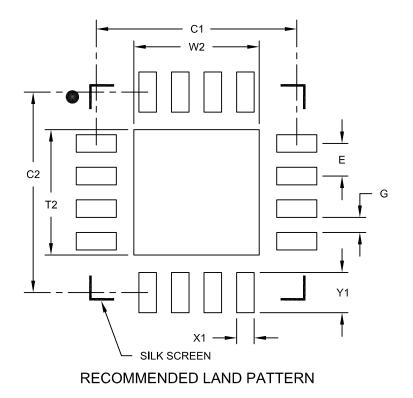

### 16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |          |      |      |  |  |

|----------------------------|------------------|----------|------|------|--|--|

| Dimensior                  | Dimension Limits |          |      |      |  |  |

| Contact Pitch              | E                | 0.65 BSC |      |      |  |  |

| Optional Center Pad Width  | W2               |          |      | 2.50 |  |  |

| Optional Center Pad Length | T2               |          |      | 2.50 |  |  |

| Contact Pad Spacing        | C1               |          | 4.00 |      |  |  |

| Contact Pad Spacing        | C2               |          | 4.00 |      |  |  |

| Contact Pad Width (X16)    | X1               |          |      | 0.35 |  |  |