Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

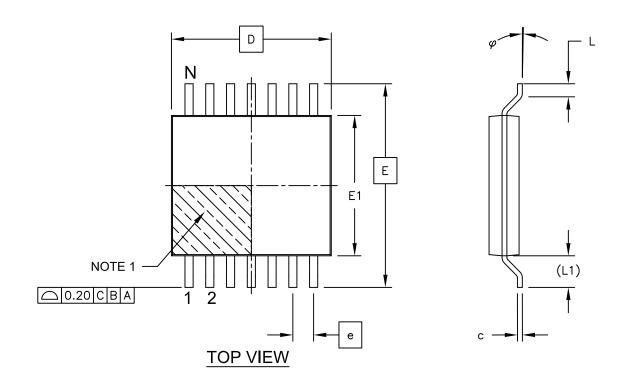

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1708-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-10:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr        | Name                  |             |       |       |       | I     |             |       |       |                      |                                 |

|-------------|-----------------------|-------------|-------|-------|-------|-------|-------------|-------|-------|----------------------|---------------------------------|

|             |                       | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank        | 29                    |             |       |       |       |       |             |       |       |                      |                                 |

| E8Ch        |                       |             |       |       |       |       |             |       |       |                      |                                 |

| <br>E8Fh    | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | _                               |

| E90h        | RA0PPS                | _           | _     | _     |       |       | RA0PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E91h        | RA1PPS                | _           | _     | _     |       |       | RA1PPS<4:02 | >     |       | 0 0000               | u uuuu                          |

| E92h        | RA2PPS                | _           | _     | _     |       |       | RA2PPS<4:02 | >     |       | 0 0000               | u uuuu                          |

| E93h -      |                       | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E94h        | RA4PPS                | _           | _     | _     |       |       | RA4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E95h        | RA5PPS                | _           | _     | _     |       |       | RA5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E96h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E97h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E98h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E99h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E9Ah -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E9Bh -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E9Ch        | RB4PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Dh        | RB5PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Eh        | RB6PPS <sup>(4)</sup> | _           | _     | _     |       |       | RB6PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Fh        | RB7PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB7PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA0h        | RC0PPS                | _           | _     | _     |       |       | RC0PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA1h        | RC1PPS                | _           | _     | _     |       |       | RC1PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA2h        | RC2PPS                | _           | _     | _     |       |       | RC2PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA3h        | RC3PPS                | _           | _     | _     |       |       | RC3PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA4h        | RC4PPS                | _           | _     | _     |       |       | RC4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA5h        | RC5PPS                | _           | _     | _     |       |       | RC5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA6h        | RC6PPS <sup>(4)</sup> | _           | _     | _     |       |       | RC6PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA7h        | RC7PPS <sup>(4)</sup> | _           | _     | _     |       |       | RC7PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA8h        |                       |             |       |       |       |       |             |       |       |                      |                                 |

| —<br>EEFh - | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | _                               |

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

PIC16(L)F1704 only. 2:

3:

PIC16(L)F1708 only. Unimplemented on PIC16LF1704/8. 4:

| IGURE 6-7:                                                    | INTERNAL OSCILLATOR SWITCH TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUNICISIO/<br>MUNICISIO<br>HFINTOSC/<br>MUNICISIO<br>LFINTOSC | LEINTOGO (FBCM and WDY disables d)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IRCF <3:0>                                                    | $\neq 0$ $= 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| System Clock                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HEINTOSCI<br>HEINTOSCI<br>MEINTOSCI<br>LFINTOSC               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRCF <3:0>                                                    | ≠ 0 X = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Clock                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CHINTOSC                                                      | ISTREMOSCARTINETORO<br>ISTREMOSCARTINETORO<br>ISTREMOSCARTINE OF FLOM is employed<br>ISTREMOSCARTINE OF FLOM<br>ISTREMOSCARTINE OF FLOM<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTREMOSCART<br>ISTRE |

| HERRESSO<br>MEDNYCER:                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 880,8 ×363×                                                   | 2-5-X X X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Clock                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Noth: See                                                     | Table 6-1 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

| R/W-0/0                                 | R/W-0/0               | R/W-0/0           | R/W-0/0                                               | R/W-0/0      | R/W-0/0           | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----------------------|-------------------|-------------------------------------------------------|--------------|-------------------|---------|---------|--|

| IOCCP7 <sup>(1)</sup>                   | IOCCP6 <sup>(1)</sup> | IOCCP5            | IOCCP4                                                | IOCCP3       | IOCCP2            | IOCCP1  | IOCCP0  |  |

| bit 7                                   | •                     | •                 | •                                                     |              |                   | •       | bit 0   |  |

|                                         |                       |                   |                                                       |              |                   |         |         |  |

| Legend:                                 |                       |                   |                                                       |              |                   |         |         |  |

| R = Readable b                          | bit                   | W = Writable b    | oit                                                   | U = Unimplem | ented bit, read a | as 'O'  |         |  |

| u = Bit is unchanged x = Bit is unknown |                       | own               | -n/n = Value at POR and BOR/Value at all other Resets |              |                   |         |         |  |

| '1' = Bit is set                        |                       | '0' = Bit is clea | red                                                   |              |                   |         |         |  |

bit 7-0

IOCCP<7:0>: Interrupt-on-Change PORTC Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

Note 1: PIC16(L)F1708 only.

#### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0               | R/W-0/0               | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| IOCCN7 <sup>(1)</sup> | IOCCN6 <sup>(1)</sup> | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCCN<7:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

Note 1: PIC16(L)F1708 only.

#### REGISTER 13-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-----------------------|-----------------------|------------|------------|------------|------------|------------|------------|

| IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup> | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7                 |                       |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

**IOCCF<7:0>:** Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

- 0 = No change was detected, or the user cleared the detected change.

Note 1: PIC16(L)F1708 only.

# 18.13 Register Definitions: COG Control

### REGISTER 18-1: COGxCON0: COG CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                                                 | U-0                                                                                               | R/W-0/0         | R/W-0/0           | R/W-0/0         | R/W-0/0           | R/W-0/0      |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-------------------|--------------|--|--|--|

| GxEN             | GxLD                                                                                                                                    | - GxCS                                                                                            |                 | CS<1:0> GxMD<2:0> |                 |                   |              |  |  |  |

| bit 7            |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   | bit C        |  |  |  |

|                  |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

| Legend:          |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

| R = Readable     | bit                                                                                                                                     | W = Writable                                                                                      | bit             | U = Unimpler      | mented bit, rea | d as '0'          |              |  |  |  |

| u = Bit is unch  | nanged                                                                                                                                  | x = Bit is unki                                                                                   | nown            | -n/n = Value a    | at POR and BC   | OR/Value at all o | ther Resets  |  |  |  |

| '1' = Bit is set |                                                                                                                                         | '0' = Bit is cle                                                                                  | ared            | q = Value de      | pends on cond   | tion              |              |  |  |  |

|                  |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

| bit 7            | GxEN: COG                                                                                                                               | x Enable bit                                                                                      |                 |                   |                 |                   |              |  |  |  |

|                  | 1 = Module is enabled                                                                                                                   |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  | 0 = Module i                                                                                                                            |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

| bit 6            | <b>GxLD:</b> COGx Load Buffers bit<br>1 = Phase, blanking, and dead-band buffers to be loaded with register values on next input events |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | to buffer transf                                                                                  |                 |                   | d with register | values on next i  | input events |  |  |  |

| bit 5            | Unimplemer                                                                                                                              | ted: Read as '                                                                                    | 0'              |                   |                 |                   |              |  |  |  |

| bit 4-3          | GxCS<1:0>:                                                                                                                              | COGx Clock S                                                                                      | election bits   |                   |                 |                   |              |  |  |  |

|                  | 11 = Reserved. Do not use.                                                                                                              |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  | 10 = COG_clock is HFINTOSC (stays active during Sleep)<br>01 = COG_clock is Fosc                                                        |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | CIOCK IS FOSC                                                                                     |                 |                   |                 |                   |              |  |  |  |

| bit 2-0          | _                                                                                                                                       | COGx Mode S                                                                                       | Selection bits  |                   |                 |                   |              |  |  |  |

| 5112 0           |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | <ul><li>11x = Reserved. Do not use.</li><li>101 = COG outputs operate in Push-Pull mode</li></ul> |                 |                   |                 |                   |              |  |  |  |

|                  | 100 = COG                                                                                                                               | outputs operate                                                                                   | e in Half-Bridg | e mode            |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | outputs operate                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | outputs operate<br>outputs operate                                                                |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         | outputs operate                                                                                   |                 |                   |                 |                   |              |  |  |  |

|                  |                                                                                                                                         |                                                                                                   |                 |                   |                 |                   |              |  |  |  |

### 20.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 20.4 "ADC Acquisition Requirements".

#### EXAMPLE 20-1: ADC CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, FRC ;oscillator and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, FRC MOVLW ;oscillator MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL WPUA BCF wpua,0 ;Disable weak ;pull-up on RA0 BANKSEL ADCON0 B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ; Turn ADC On CALL SampleTime ;Acquisiton delay BSF ADCON0, ADGO ;Start conversion ADCON0, ADGO ; Is conversion done? BTFSC GOTO \$-1 ;No, test again BANKSEL ADRESH ; ADRESH,W ;Read upper 2 bits MOVF RESULTHI ;store in GPR space MOVWE BANKSEL ADRESL ; MOVF ADRESL,W ;Read lower 8 bits MOVWF RESULTLO ;Store in GPR space

| R/W-0/0         | R/W-0/0                                                                                                           | R/W-0/0                | R/W-0/0           | U-0              | U-0              | U-0                                   | U-0         |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|------------------|------------------|---------------------------------------|-------------|--|--|

|                 | TRIGSE                                                                                                            | EL<3:0> <sup>(1)</sup> |                   | _                | _                | _                                     | _           |  |  |

| bit 7           |                                                                                                                   |                        |                   |                  |                  | · · · · · · · · · · · · · · · · · · · | bit 0       |  |  |

| Legend:         |                                                                                                                   |                        |                   |                  |                  |                                       |             |  |  |

| R = Readab      | le bit                                                                                                            | W = Writable           | bit               | U = Unimplen     | nented bit, read | 1 as '0'                              |             |  |  |

| u = Bit is und  | changed                                                                                                           | x = Bit is unk         | nown              | -n/n = Value a   | at POR and BO    | R/Value at all c                      | ther Resets |  |  |

| '1' = Bit is se | •                                                                                                                 | '0' = Bit is cle       | ared              |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   |                        |                   |                  |                  |                                       |             |  |  |

| bit 7-4         | TRIGSEL<3                                                                                                         | :0>: Auto-Conv         | ersion Triager    | Selection bits(1 | )                |                                       |             |  |  |

|                 | TRIGSEL<3:0>: Auto-Conversion Trigger Selection bits <sup>(1)</sup><br>0000 = No auto-conversion trigger selected |                        |                   |                  |                  |                                       |             |  |  |

|                 | 0001 = CC                                                                                                         |                        | r ingger eereet   | 00               |                  |                                       |             |  |  |

|                 | 0010 = CC                                                                                                         | P2                     |                   |                  |                  |                                       |             |  |  |

|                 | 0011 = Time                                                                                                       | er0 – T0 overflo       | <sub>DW</sub> (2) |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | er1 – T1 overflo       |                   |                  |                  |                                       |             |  |  |

|                 | 0101 = Time                                                                                                       | er2 – T2_match         |                   |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | nparator C1 – C        |                   |                  |                  |                                       |             |  |  |

|                 | 0111 <b>= Con</b>                                                                                                 | nparator C2 – C        | 2OUT_sync         |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | C1 – LC1_out           |                   |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | C2 – LC2_out           |                   |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | C3 – LC3_out           |                   |                  |                  |                                       |             |  |  |

|                 | 1011 = Res                                                                                                        |                        |                   |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | er4 – T4_match         |                   |                  |                  |                                       |             |  |  |

|                 |                                                                                                                   | er6 – T6_match         | ו                 |                  |                  |                                       |             |  |  |

|                 | 1110 = Res                                                                                                        |                        |                   |                  |                  |                                       |             |  |  |

|                 | 1111 = Res                                                                                                        |                        |                   |                  |                  |                                       |             |  |  |

| bit 3-0         | Unimpleme                                                                                                         | nted: Read as          | 0'                |                  |                  |                                       |             |  |  |

| Note 1: ⊤       | his is a rising ed                                                                                                | dge sensitive in       | out for all sour  | ces.             |                  |                                       |             |  |  |

# REGISTER 20-3: ADCON2: ADC CONTROL REGISTER 2

- This is a rising edge sensitive input for all sources. Note 1:

- 2: Signal also sets its corresponding interrupt flag.

# 22.0 8-BIT DIGITAL-TO-ANALOG CONVERTER (DAC1) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 256 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- · ADC input channel

- DAC1OUT1 pin

- DAC1OUT2 pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

# EQUATION 22-1: DAC OUTPUT VOLTAGE

$$\frac{IF \ DACIEN = 1}{Vout}$$

$$Vout = \left( (Vsource+ - Vsource-) \times \frac{DACIR[7:0]}{2^8} \right) + Vsource-$$

$$Vsource+ = VDD, \ Vref, \ or \ FVR \ BUFFER \ 2$$

$$Vsource- = Vss$$

# 22.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 32-19: Digital-to-Analog Converter (DAC) Specifications.

# 22.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT1 and DAC1OUT2 pins by setting the respective DAC1OE1 and DAC1OE2 bits of the DAC1CON0 register. Selecting the DAC voltage for output on either DAC1OUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DAC1OUTx pin when it has been configured for DAC voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage output for external connections to either DAC1OUTx pin. Figure 22-2 shows an example buffering technique.

# 22.1 Output Voltage Selection

The DAC has 256 voltage level ranges. The 256 levels are set with the DAC1R<7:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 22-1:

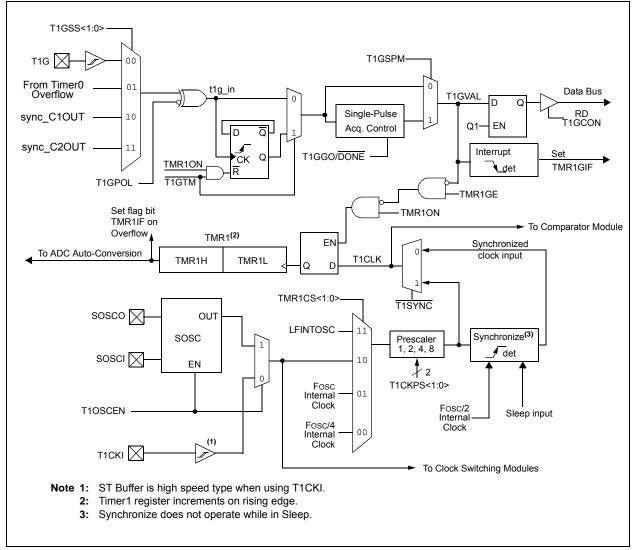

# 25.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- Gate Event Interrupt

- Figure 25-1 is a block diagram of the Timer1 module.

### FIGURE 25-1: TIMER1 BLOCK DIAGRAM

#### 29.1.1.5 TSR Status

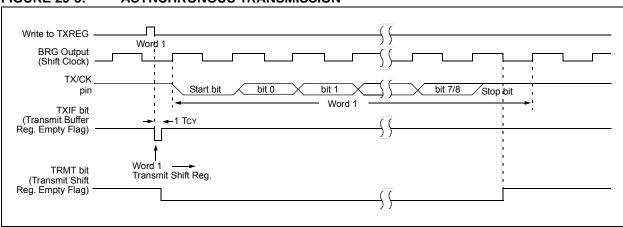

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 29.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 29.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 29.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 29.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 29-3: ASYNCHRONOUS TRANSMISSION

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4       | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|-------------|--------------|------------|--------|--------|---------------------|

| ANSELA                | —                     | _                     |          | ANSA4       |              | ANSA2      | ANSA1  | ANSA0  | 122                 |

| ANSELB <sup>(1)</sup> | —                     | —                     | ANSB5    | ANSB4       | _            | _          | _      | _      | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2) | ANSC4(2)    | ANSC3        | ANSC2      | ANSC1  | ANSC0  | 133                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | -        | SCKP        | BRG16        | —          | WUE    | ABDEN  | 336                 |

| INTCON                | GIE                   | PEIE                  | TMR0IE   | INTE        | IOCIE        | TMR0IF     | INTF   | IOCIF  | 85                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE     | TXIE        | SSP1IE       | CCP1IE     | TMR2IE | TMR1IE | 86                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF     | TXIF        | SSP1IF       | CCP1IF     | TMR2IF | TMR1IF | 89                  |

| RC1REG                |                       |                       | EUS      | SART Receiv | e Data Regis | ter        |        |        | 329*                |

| RC1STA                | SPEN                  | RX9                   | SREN     | CREN        | ADDEN        | FERR       | OERR   | RX9D   | 335                 |

| RxyPPS                | _                     | _                     | _        |             | ſ            | RxyPPS<4:0 | >      |        | 140                 |

| SP1BRGL               |                       |                       |          | BRG<        | 7:0>         |            |        |        | 337                 |

| SP1BRGH               |                       |                       |          | BRG<        | 15:8>        |            |        |        | 337                 |

| TRISA                 | —                     | _                     | TRISA5   | TRISA4      | _(3)         | TRISA2     | TRISA1 | TRISA0 | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4      | _            | —          | —      | —      | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4      | TRISC3       | TRISC2     | TRISC1 | TRISA0 | 132                 |

| TX1STA                | CSRC                  | TX9                   | TXEN     | SYNC        | SENDB        | BRGH       | TRMT   | TX9D   | 334                 |

#### TABLE 29-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0                            | R/W-0/0        | R/W-0/0        | R-0/0            | R-0/0            | R-0/0       |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN                               | CREN           | ADDEN          | FERR             | OERR             | RX9D        |  |  |  |

| bit 7            |                                                                                                                                                    |                                    |                |                |                  |                  | bit C       |  |  |  |

| <u> </u>         |                                                                                                                                                    |                                    |                |                |                  |                  |             |  |  |  |

| Legend:          |                                                                                                                                                    |                                    |                |                |                  | (2)              |             |  |  |  |

| R = Readable     |                                                                                                                                                    | W = Writable                       |                | -              | nented bit, read |                  |             |  |  |  |

| u = Bit is unch  | anged                                                                                                                                              | x = Bit is unki                    |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                    | '0' = Bit is cle                   | ared           |                |                  |                  |             |  |  |  |

| bit 7            | SDEN. Sorial                                                                                                                                       | Port Enable bi                     | +              |                |                  |                  |             |  |  |  |

|                  | 1 = Serial po                                                                                                                                      |                                    | L              |                |                  |                  |             |  |  |  |

|                  |                                                                                                                                                    | rt disabled (he                    | ld in Reset)   |                |                  |                  |             |  |  |  |

| bit 6            | -                                                                                                                                                  | ceive Enable I                     | -              |                |                  |                  |             |  |  |  |

|                  | 1 = Selects 9                                                                                                                                      |                                    |                |                |                  |                  |             |  |  |  |

|                  | 0 = Selects 8                                                                                                                                      | •                                  |                |                |                  |                  |             |  |  |  |

| bit 5            | SREN: Single                                                                                                                                       | Receive Enal                       | ole bit        |                |                  |                  |             |  |  |  |

|                  | Asynchronous                                                                                                                                       | <u>s mode</u> :                    |                |                |                  |                  |             |  |  |  |

|                  | Don't care                                                                                                                                         |                                    |                |                |                  |                  |             |  |  |  |