# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                     |

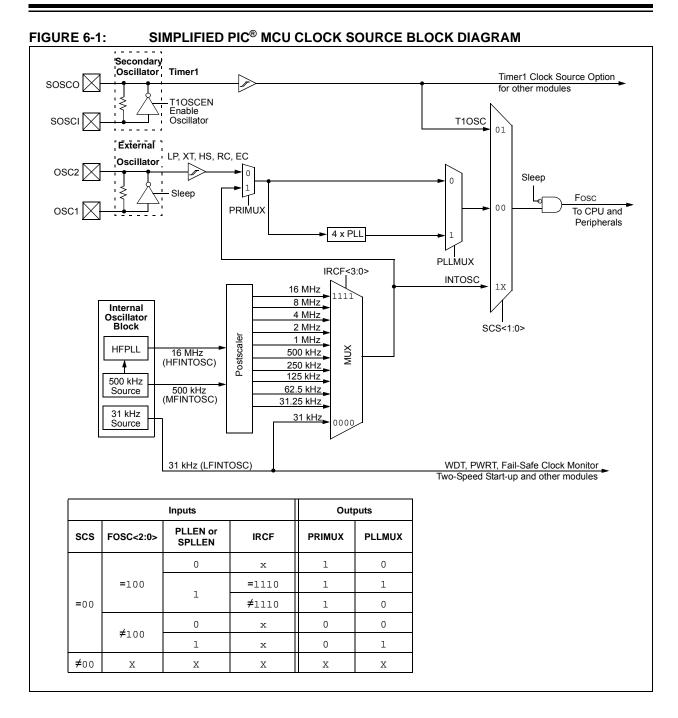

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1708-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

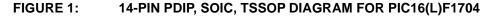

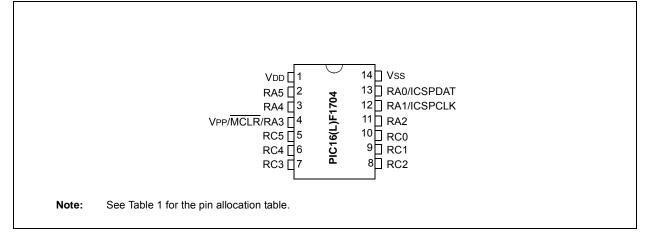

#### **PIN DIAGRAMS**

### 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-9 can be addressed from any Bank.

| Addr            | Name   | Bit 7        | Bit 6                        | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all<br>other Resets |

|-----------------|--------|--------------|------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|------------------------------|

| Bank            | 0-31   | •            | •                            | •             | •            |             |               |        |       |                      |                              |

| x00h or<br>x80h | INDF0  |              | this location ical register) |               | XXXX XXXX    | uuuu uuuu   |               |        |       |                      |                              |

| x01h or<br>x81h | INDF1  |              | this location ical register) |               | nts of FSR1H | /FSR1L to a | ddress data r | memory |       | xxxx xxxx            | uuuu uuuu                    |

| x02h or<br>x82h | PCL    | Program Co   | ounter (PC)                  | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                    |

| x03h or<br>x83h | STATUS | —            | _                            | -             | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                       |

| x04h or<br>x84h | FSR0L  | Indirect Dat | ta Memory A                  | ddress 0 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                    |

| x05h or<br>x85h | FSR0H  | Indirect Dat | ta Memory A                  | ddress 0 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                    |

| x06h or<br>x86h | FSR1L  | Indirect Dat | ta Memory A                  | ddress 1 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                    |

| x07h or<br>x87h | FSR1H  | Indirect Dat | ta Memory A                  | ddress 1 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                    |

| x08h or<br>x88h | BSR    | _            | _                            | _             | BSR4         | BSR3        | BSR2          | BSR1   | BSR0  | 0 0000               | 0 0000                       |

| x09h or<br>x89h | WREG   | Working Re   | Working Register             |               |              |             |               |        |       |                      | uuuu uuuu                    |

| x0Ahor<br>x8Ah  | PCLATH | _            | Write Buffer                 |               | -000 0000    | -000 0000   |               |        |       |                      |                              |

| x0Bhor<br>x8Bh  | INTCON | GIE          | PEIE                         | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                    |

#### TABLE 3-9: CORE FUNCTION REGISTERS SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

#### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

#### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### 4.7 Register Definitions: Device and Revision

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|   | R      | R      | R               | R      | R                  | R                  |

|---|--------|--------|-----------------|--------|--------------------|--------------------|

|   |        |        | DEV<            | :13:8> |                    |                    |

|   | bit 13 |        |                 |        |                    | bit 8              |

| D | D      | D      | D               | D      | D                  | R                  |

| Ν | ĸ      |        | <7:0>           | N      | Ν                  | N                  |

|   |        |        |                 |        |                    | bit 0              |

| - | R      | bit 13 | bit 13<br>R R R | DEV<   | DEV<13:8>   bit 13 | DEV<13:8>   bit 13 |

#### Legend:

R = Readable bit

'1' = Bit is set

'0' = Bit is cleared

bit 13-0 DEV<13:0>: Device ID bits

| Device      | DEVID<13:0> Values                 |  |  |  |  |  |  |  |  |  |

|-------------|------------------------------------|--|--|--|--|--|--|--|--|--|

| PIC16F1704  | 11 0000 0100 0011 ( <b>3043h</b> ) |  |  |  |  |  |  |  |  |  |

| PIC16LF1704 | 11 0000 0100 0101 ( <b>3045h</b> ) |  |  |  |  |  |  |  |  |  |

| PIC16F1708  | 11 0000 0100 0010 ( <b>3042h</b> ) |  |  |  |  |  |  |  |  |  |

| PIC16LF1708 | 11 0000 0100 0100 ( <b>3044h</b> ) |  |  |  |  |  |  |  |  |  |

#### REGISTER 4-4: REVID: REVISION ID REGISTER

|   | R      | R      | R      | R      | R           | R                  |

|---|--------|--------|--------|--------|-------------|--------------------|

|   |        |        | REV<   | :13:8> |             |                    |

|   | bit 13 |        |        |        |             | bit 8              |

|   |        |        |        |        |             |                    |

| R | R      | R      | R      | R      | R           | R                  |

|   |        | REV    | <7:0>  |        |             |                    |

|   |        |        |        |        |             | bit 0              |

|   | R      | bit 13 | bit 13 | REV<   | R R R R R R | REV<13:8>   bit 13 |

#### Legend:

R = Readable bit '1' = Bit is set '0' = Bit is cleared

bit 13-0 **REV<13:0>:** Revision ID bits

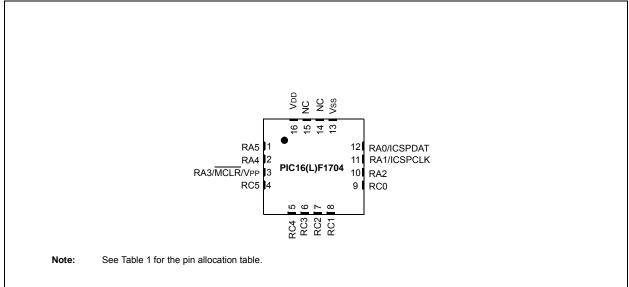

#### 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 7.6 Register Definitions: Interrupt Control

| R/W-0/0          | R/W-0/0                          | R/W-0/0                               | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0          | R-0/0                |

|------------------|----------------------------------|---------------------------------------|---------------|------------------|------------------|------------------|----------------------|

| GIE              | PEIE                             | TMR0IE                                | INTE          | IOCIE            | TMR0IF           | INTF             | IOCIF <sup>(1)</sup> |

| bit 7            |                                  |                                       |               |                  |                  |                  | bit (                |

|                  |                                  |                                       |               |                  |                  |                  |                      |

| Legend:          |                                  |                                       |               |                  |                  |                  |                      |

| R = Readable     | bit                              | W = Writable                          | bit           | U = Unimpler     | nented bit, read | l as '0'         |                      |

| u = Bit is unch  | anged                            | x = Bit is unkr                       | nown          | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets          |

| '1' = Bit is set |                                  | '0' = Bit is clea                     | ared          |                  |                  |                  |                      |

| bit 7            |                                  | atorrupt Epoble                       | hit           |                  |                  |                  |                      |

|                  |                                  | nterrupt Enable<br>all active interru |               |                  |                  |                  |                      |

|                  | 1 = Disables a<br>0 = Disables a |                                       | ipis          |                  |                  |                  |                      |

| bit 6            | PEIE: Periphe                    | eral Interrupt E                      | nable bit     |                  |                  |                  |                      |

|                  |                                  | all active periph                     |               | 3                |                  |                  |                      |

|                  |                                  | all peripheral ir                     | -             |                  |                  |                  |                      |

| bit 5            |                                  | er0 Overflow Ir                       |               | e bit            |                  |                  |                      |

|                  |                                  | he Timer0 inter<br>the Timer0 inte    |               |                  |                  |                  |                      |

| bit 4            |                                  | ternal Interrupt                      | •             |                  |                  |                  |                      |

| DIL 4            |                                  | he INT externa                        |               |                  |                  |                  |                      |

|                  |                                  | the INT externa                       |               |                  |                  |                  |                      |

| bit 3            | IOCIE: Interru                   | upt-on-Change                         | Enable bit    |                  |                  |                  |                      |

|                  |                                  | he interrupt-on                       |               |                  |                  |                  |                      |

|                  | 0 = Disables f                   | the interrupt-or                      | i-change      |                  |                  |                  |                      |

| bit 2            |                                  | er0 Overflow In                       |               | it               |                  |                  |                      |

|                  |                                  | jister has overf                      |               |                  |                  |                  |                      |

|                  | -                                | gister did not ov                     |               |                  |                  |                  |                      |

| bit 1            |                                  | ternal Interrupt                      | •             |                  |                  |                  |                      |

|                  |                                  | external interrup                     |               | ır               |                  |                  |                      |

| bit 0            |                                  | pt-on-Change                          |               |                  |                  |                  |                      |

| bit 0            |                                  | east one of the                       |               |                  | anged state      |                  |                      |

|                  |                                  | he interrupt-on-                      |               |                  |                  |                  |                      |

| Note 1: The      |                                  | is road only a                        | nd cleared wh | on all the inter | rupt-on-change   | flags in the IO( | NE register          |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

| R/W-0/       | 0 R/W-0/0                             | R-0/0                                | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|--------------|---------------------------------------|--------------------------------------|-----------------|------------------|------------------|------------------|-------------|

| TMR1G        | IF ADIF                               | RCIF                                 | TXIF            | SSP1IF           | CCP1IF           | TMR2IF           | TMR1IF      |

| bit 7        |                                       |                                      |                 | 1                | I                | 1                | bit 0       |

|              |                                       |                                      |                 |                  |                  |                  |             |

| Legend:      |                                       |                                      |                 |                  |                  |                  |             |

| R = Read     | able bit                              | W = Writable                         | bit             | U = Unimplei     | mented bit, read | l as '0'         |             |

| u = Bit is u | unchanged                             | x = Bit is unk                       | nown            | -n/n = Value     | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is | set                                   | '0' = Bit is cle                     | ared            |                  |                  |                  |             |

|              |                                       |                                      |                 |                  |                  |                  |             |

| bit 7        |                                       | Timer1 Gate Inte                     | errupt Flag bit |                  |                  |                  |             |

|              | 1 = Interrupt                         |                                      |                 |                  |                  |                  |             |

| bit 6        |                                       | t is not pending<br>g-to-Digital Con | wortor (ADC)    | Interrupt Elea k | sit              |                  |             |

| DILO         | 1 = Interrupt                         | • •                                  |                 | Interrupt Flag i | JIL              |                  |             |

|              |                                       | t is not pending                     |                 |                  |                  |                  |             |

| bit 5        | RCIF: USAF                            | RT Receive Inter                     | rrupt Flag bit  |                  |                  |                  |             |

|              | 1 = Interrupt                         |                                      |                 |                  |                  |                  |             |

|              |                                       | t is not pending                     |                 |                  |                  |                  |             |

| bit 4        |                                       | RT Transmit Inte                     | rrupt Flag bit  |                  |                  |                  |             |

|              | 1 = Interrupt<br>0 = Interrupt        | t is penaing                         |                 |                  |                  |                  |             |

| bit 3        | -                                     | nchronous Seria                      | al Port (MSSP   | ) Interrupt Flag | bit              |                  |             |

|              | 1 = Interrupt                         |                                      | (               | ,                |                  |                  |             |

|              | 0 = Interrupt                         | t is not pending                     |                 |                  |                  |                  |             |

| bit 2        |                                       | CP1 Interrupt Fla                    | ng bit          |                  |                  |                  |             |

|              | 1 = Interrupt                         |                                      |                 |                  |                  |                  |             |

| bit 1        | •                                     | t is not pending<br>ner2 to PR2 Inte | rrunt Eloa bit  |                  |                  |                  |             |

| DILI         | 1 = Interrupt                         |                                      | Filling bit     |                  |                  |                  |             |

|              | •                                     | t is not pending                     |                 |                  |                  |                  |             |

| bit 0        | •                                     | ner1 Overflow Ir                     | nterrupt Flag   | oit              |                  |                  |             |

|              | 1 = Interrupt                         |                                      |                 |                  |                  |                  |             |

|              | 0 = Interrup                          | t is not pending                     |                 |                  |                  |                  |             |

| Note:        | Interrupt flag bits                   | are set when ar                      | interrupt       |                  |                  |                  |             |

|              | condition occurs,                     | regardless of th                     | e state of      |                  |                  |                  |             |

|              | its corresponding<br>Enable bit, GIE, |                                      |                 |                  |                  |                  |             |

|              | User software                         | should ens                           | •               |                  |                  |                  |             |

|              | appropriate inter                     | rupt flag bits a                     |                 |                  |                  |                  |             |

|              | prior to enabling                     | an interrupt.                        |                 |                  |                  |                  |             |

#### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

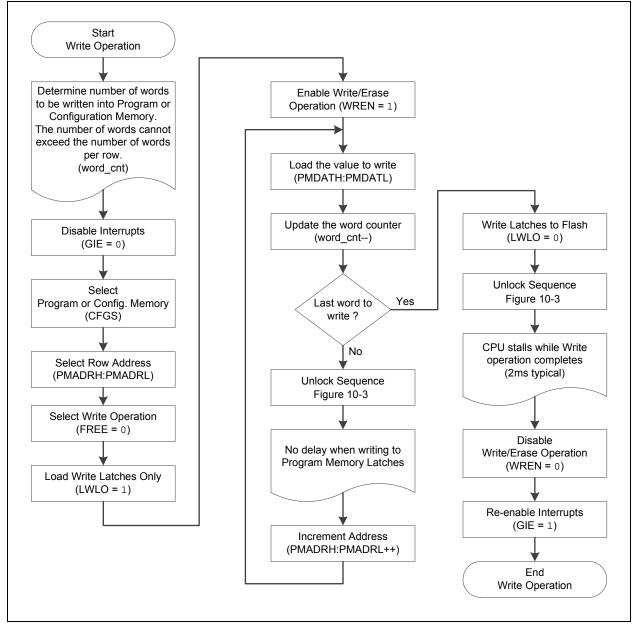

#### FIGURE 10-6: FLASH PROGRAM MEMORY WRITE FLOWCHART

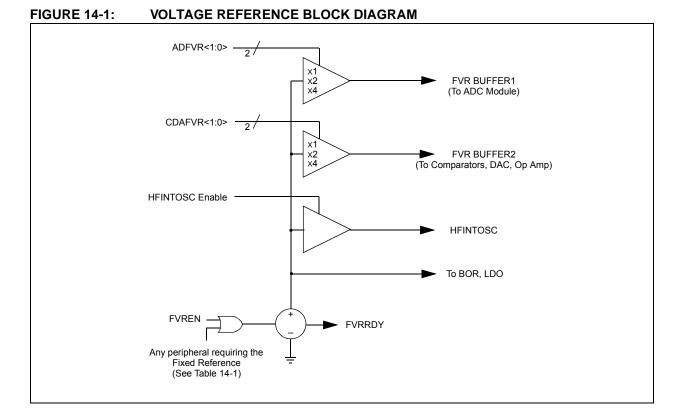

#### 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, and DAC is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 22.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" and Section 16.0 "Comparator Module" for additional information.

#### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See Figure 33-74: Wake from Sleep, VREGPM = 0.

#### © 2013-2015 Microchip Technology Inc.

| R/W-0/0         | R/W-0/0            | R/W-0/0                | R/W-0/0           | U-0              | U-0              | U-0                                   | U-0         |

|-----------------|--------------------|------------------------|-------------------|------------------|------------------|---------------------------------------|-------------|

|                 | TRIGSE             | EL<3:0> <sup>(1)</sup> |                   | _                | —                | _                                     | _           |

| bit 7           |                    |                        |                   |                  |                  | · · · · · · · · · · · · · · · · · · · | bit 0       |

| Legend:         |                    |                        |                   |                  |                  |                                       |             |

| R = Readab      | le bit             | W = Writable           | bit               | U = Unimplen     | nented bit, read | 1 as '0'                              |             |

| u = Bit is und  | changed            | x = Bit is unk         | nown              | -n/n = Value a   | at POR and BO    | R/Value at all c                      | ther Resets |

| '1' = Bit is se | •                  | '0' = Bit is cle       | ared              |                  |                  |                                       |             |

|                 |                    |                        |                   |                  |                  |                                       |             |

| bit 7-4         | TRIGSEL<3          | :0>: Auto-Conv         | ersion Triager    | Selection bits(1 | )                |                                       |             |

|                 |                    | auto-conversior        |                   |                  |                  |                                       |             |

|                 | 0001 = CC          |                        | r ingger eereet   | 00               |                  |                                       |             |

|                 | 0010 = CC          | P2                     |                   |                  |                  |                                       |             |

|                 | 0011 = Time        | er0 – T0 overflo       | <sub>DW</sub> (2) |                  |                  |                                       |             |

|                 |                    | er1 – T1 overflo       |                   |                  |                  |                                       |             |

|                 | 0101 = Time        | er2 – T2_match         |                   |                  |                  |                                       |             |

|                 |                    | nparator C1 – C        |                   |                  |                  |                                       |             |

|                 | 0111 <b>= Con</b>  | nparator C2 – C        | 2OUT_sync         |                  |                  |                                       |             |

|                 |                    | C1 – LC1_out           |                   |                  |                  |                                       |             |

|                 |                    | C2 – LC2_out           |                   |                  |                  |                                       |             |

|                 |                    | C3 – LC3_out           |                   |                  |                  |                                       |             |

|                 | 1011 = Res         |                        |                   |                  |                  |                                       |             |

|                 |                    | er4 – T4_match         |                   |                  |                  |                                       |             |

|                 |                    | er6 – T6_match         | ו                 |                  |                  |                                       |             |

|                 | 1110 = Res         |                        |                   |                  |                  |                                       |             |

|                 | 1111 = Res         |                        |                   |                  |                  |                                       |             |

| bit 3-0         | Unimpleme          | nted: Read as          | 0'                |                  |                  |                                       |             |

| Note 1: ⊤       | his is a rising ed | dge sensitive in       | out for all sour  | ces.             |                  |                                       |             |

#### REGISTER 20-3: ADCON2: ADC CONTROL REGISTER 2

- This is a rising edge sensitive input for all sources. Note 1:

- 2: Signal also sets its corresponding interrupt flag.

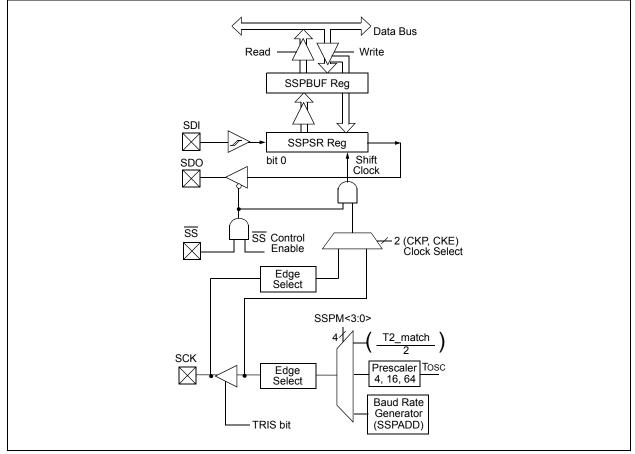

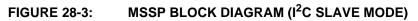

#### 28.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 28.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

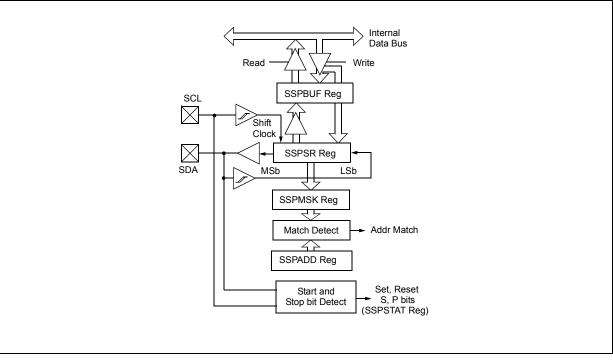

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 28-1 is a block diagram of the SPI interface module.

#### FIGURE 28-5: SPI MASTER/SLAVE CONNECTION

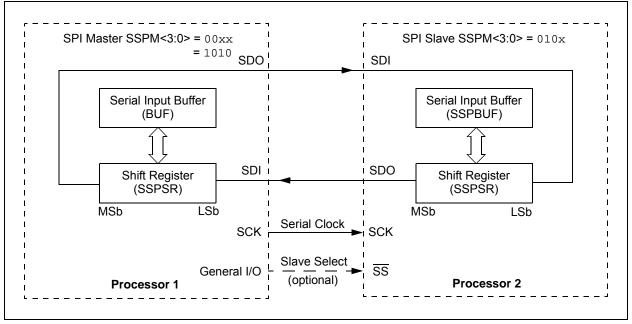

#### 28.6.8 ACKNOWLEDGE SEQUENCE TIMING

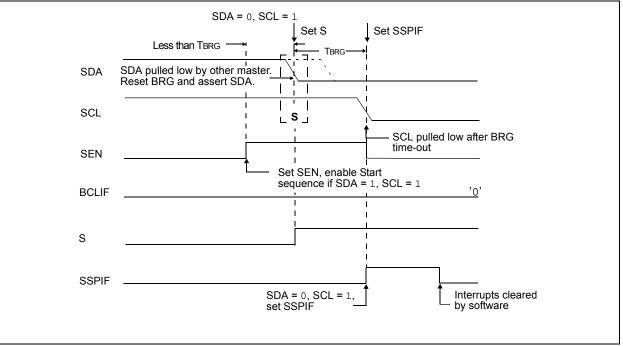

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 28-30).

#### 28.6.8.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

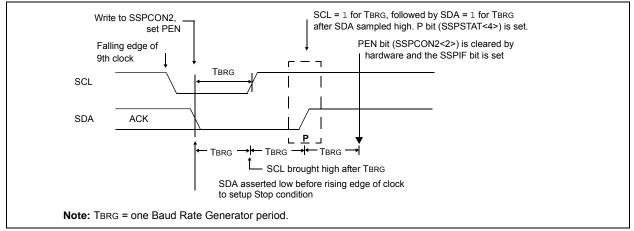

#### 28.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 28-31).

#### 28.6.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 28-30: ACKNOWLEDGE SEQUENCE WAVEFORM

|        |                |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>616 =</b> 0 |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686      | 4 MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | —                           | _              |            | _                           |                | _              | _                           | 300            | 0.16       | 207                         |

| 1200   | —              | _          | —                           | 1202           | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00           | 23                          | —              | —          | —                           |

| 10417  | 10417          | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00           | 11                          | _              | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | —              | _          | _                           | 57.60k         | 0.00           | 3                           | —              | _          | _                           |

| 115.2k | —              | _          | _                           | —              |            | _                           | 115.2k         | 0.00           | 1                           | _              | _          | —                           |

#### TABLE 29-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC     | <b>616 =</b> 1 |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Foso           | : = 32.00  | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc           | : = 18.43      | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 6666                        | 300.0          | -0.01      | 4166                        | 300.0          | 0.00           | 3839                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200           | -0.02      | 3332                        | 1200           | -0.03      | 1041                        | 1200           | 0.00           | 959                         | 1200           | 0.00       | 575                         |

| 2400   | 2401           | -0.04      | 832                         | 2399           | -0.03      | 520                         | 2400           | 0.00           | 479                         | 2400           | 0.00       | 287                         |

| 9600   | 9615           | 0.16       | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00           | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00       | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37          | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16       | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00           | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79      | 34                          | 56.818         | -1.36      | 21                          | 57.60k         | 0.00           | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.6k         | 2.12       | 16                          | 113.636        | -1.36      | 10                          | 115.2k         | 0.00           | 9                           | 115.2k         | 0.00       | 5                           |

|        |                |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG     | <b>616 =</b> 1 |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686      | 4 MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9          | -0.02      | 1666                        | 300.1          | 0.04       | 832                         | 300.0          | 0.00           | 767                         | 300.5          | 0.16       | 207                         |

| 1200   | 1199           | -0.08      | 416                         | 1202           | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00           | 23                          | _              | _          | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19.23k         | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.20k         | 0.00           | 11                          | —              | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | —              | _          | _                           | 57.60k         | 0.00           | 3                           | —              | _          | _                           |

| 115.2k | _              | _          | _                           | —              | _          | _                           | 115.2k         | 0.00           | 1                           | —              | _          | _                           |

### TABLE 29-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                | Bit 3         | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |  |  |

|-----------------------|-----------------------|-----------------------|----------|----------------------|---------------|------------|--------|--------|---------------------|--|--|--|

| ANSELA                | -                     | —                     |          | ANSA4                |               | ANSA2      | ANSA1  | ANSA0  | 122                 |  |  |  |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5    | ANSB4                |               | _          | _      | _      | 128                 |  |  |  |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2) | ANSC4 <sup>(2)</sup> | ANSC3         | ANSC2      | ANSC1  | ANSC0  | 133                 |  |  |  |

| BAUD1CON              | ABDOVF                | RCIDL                 | _        | SCKP                 | BRG16         | —          | WUE    | ABDEN  | 336                 |  |  |  |

| INTCON                | GIE                   | PEIE                  | TMR0IE   | INTE                 | IOCIE         | TMR0IF     | INTF   | IOCIF  | 85                  |  |  |  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE     | TXIE                 | SSP1IE        | CCP1IE     | TMR2IE | TMR1IE | 86                  |  |  |  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF     | TXIF                 | SSP1IF        | CCP1IF     | TMR2IF | TMR1IF | 89                  |  |  |  |

| RC1STA                | SPEN                  | RX9                   | SREN     | CREN                 | ADDEN         | FERR       | OERR   | RX9D   | 335                 |  |  |  |

| RxyPPS                | _                     | _                     | _        |                      | ſ             | RxyPPS<4:0 | >      |        | 140                 |  |  |  |

| SP1BRGL               |                       |                       |          | BRG<                 | 7:0>          |            |        |        | 337                 |  |  |  |

| SP1BRGH               |                       |                       |          | BRG<                 | 15:8>         |            |        |        | 337                 |  |  |  |

| TRISA                 | _                     | _                     | TRISA5   | TRISA4               | (3)           | TRISA2     | TRISA1 | TRISA0 | 121                 |  |  |  |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4               | _             | —          | _      | _      | 127                 |  |  |  |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4               | TRISC3        | TRISC2     | TRISC1 | TRISA0 | 132                 |  |  |  |

| TX1REG                |                       |                       | EUS      | ART Transm           | it Data Regis | ster       |        |        | 326*                |  |  |  |

| TX1STA                | CSRC                  | TX9                   | TXEN     | SYNC                 | SENDB         | BRGH       | TRMT   | TX9D   | 334                 |  |  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission. \* Page provides register information.

**Note 1:** PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

**3:** Unimplemented, read as '1'.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                      |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |

| INCF             | Increment f                                                                                                                                                               | IORWF            | Inclusive OR W with f                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                           | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                         | Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. | Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

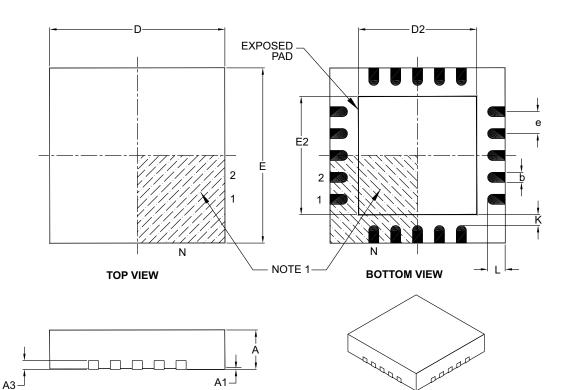

#### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |    | MILLIMETERS |      |      |

|------------------------|----|-------------|------|------|

| Dimension Limits       |    | MIN         | NOM  | MAX  |

| Number of Pins         | Ν  | 20          |      |      |

| Pitch                  | е  | 0.50 BSC    |      |      |

| Overall Height         | Α  | 0.80        | 0.90 | 1.00 |

| Standoff               | A1 | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3 | 0.20 REF    |      |      |

| Overall Width          | E  | 4.00 BSC    |      |      |

| Exposed Pad Width      | E2 | 2.60        | 2.70 | 2.80 |

| Overall Length         | D  | 4.00 BSC    |      |      |

| Exposed Pad Length     | D2 | 2.60        | 2.70 | 2.80 |

| Contact Width          | b  | 0.18        | 0.25 | 0.30 |

| Contact Length         | L  | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad | K  | 0.20        | -    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B