#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1708t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    | ABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |             |         |              |               |                |         |           |         |                      |                                 |  |

|--------------------|----------------------------------------------------------|-------------|---------|--------------|---------------|----------------|---------|-----------|---------|----------------------|---------------------------------|--|

| Addr               | Name                                                     | Bit 7       | Bit 6   | Bit 5        | Bit 4         | Bit 3          | Bit 2   | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

| Bank               | c 11                                                     |             |         |              |               |                |         |           |         |                      |                                 |  |

| D8Ch<br>to<br>DADh | _                                                        | Unimplement | ed      |              |               |                |         |           |         | _                    | _                               |  |

| Bank               | Bank 12                                                  |             |         |              |               |                |         |           |         |                      |                                 |  |

| 60Ch<br>to<br>616h | _                                                        | Unimplement | ed      |              |               |                |         |           |         | _                    | _                               |  |

| 617h               | PWM3DCL                                                  | PWM3E       | )C<1:0> | —            | _             | —              | —       | —         | _       | xx                   | uu                              |  |

| 618h               | PWM3DCH                                                  |             |         |              | PWM3          | DC<9:2>        |         |           |         | XXXX XXXX            | uuuu uuuu                       |  |

| 619h               | PWM3CON                                                  | PWM3EN      | —       | PWM3OUT      | PWM3POL       | —              | —       | —         | —       | 0-x0                 | u-uu                            |  |

| 61Ah               | PWM4DCL                                                  | PWM4D       | )C<1:0> | —            | —             | —              | —       | —         | —       | 00                   | uu                              |  |

| 61Bh               | PWM4DCH                                                  |             |         | 1            | PWM4          | DC<9:2>        |         |           |         | 0000 0000            | uuuu uuuu                       |  |

| 61Ch               | PWM4CON                                                  | PWM4EN      | —       | PWM4OUT      | PWM4POL       | —              | —       | —         | —       | 0-x0                 | u-uu                            |  |

| 61Dh<br>61Fh       | _                                                        | Unimplement | ed      |              |               |                |         |           |         | —                    | —                               |  |

| Bank               | c 13                                                     |             |         |              |               |                |         |           |         |                      |                                 |  |

| 68Ch<br>to<br>690h | _                                                        | Unimplement | ed      |              |               |                |         |           |         | _                    | _                               |  |

| 691h               | COG1PHR                                                  | —           |         | COG Rising I | Edge Phase C  | ounter Regist  | er      |           |         | xx xxxx              | uu uuuu                         |  |

| 692h               | COG1PHF                                                  | —           | —       | COG Falling  | Edge Phase C  | Counter Regist | er      |           |         | xx xxxx              | uu uuuu                         |  |

| 693h               | COG1BLKR                                                 | —           | _       | COG Rising I | Edge Blanking | Counter Regi   | ster    |           |         | xx xxxx              | uu uuuu                         |  |

| 694h               | COG1BLKF                                                 | —           | _       | COG Falling  | Edge Blanking | g Counter Reg  | ister   |           |         | xx xxxx              | uu uuuu                         |  |

| 695h               | COG1DBR                                                  | _           | _       | COG Rising I | Edge Dead-ba  | ind Counter R  | egister |           |         | xx xxxx              | uu uuuu                         |  |

| 696h               | COG1DBF                                                  | —           | —       | COG Falling  | Edge Dead-ba  | and Counter R  | egister |           |         | xx xxxx              | uu uuuu                         |  |

| 697h               | COG1CON0                                                 | G1EN        | G1LD    | —            | G1CS          | S<1:0>         |         | G1MD<2:0> |         | 00-0 0000            | 00-0 0000                       |  |

| 698h               | COG1CON1                                                 | G1RDBS      | G1FDBS  | _            | —             | G1POLD         | G1POLC  | G1POLB    | G1POLA  | 00 0000              | 00 0000                         |  |

| 699h               | COG1RIS                                                  | —           | G1RIS6  | G1RIS5       | G1RIS4        | G1RIS3         | G1RIS2  | G1RIS1    | G1RIS0  | -000 0000            | -000 0000                       |  |

| 69Ah               | COG1RSIM                                                 | -           | G1RSIM6 | G1RSIM5      | G1RSIM4       | G1RSIM3        | G1RSIM2 | G1RSIM1   | G1RSIM0 | -000 0000            | -000 0000                       |  |

| 69Bh               | COG1FIS                                                  | —           | G1FIS6  | G1FIS5       | G1FIS4        | G1FIS3         | G1FIS2  | G1FIS1    | G1FIS0  | -000 0000            | -000 0000                       |  |

| 69Ch               | COG1FSIM                                                 | _           | G1FSIM6 | G1FSIM5      | G1FSIM4       | G1FSIM3        | G1FSIM2 | G1FSIM1   | G1FSIM0 | -000 0000            | -000 0000                       |  |

| 69Dh               | COG1ASD0                                                 | G1ASE       | G1ARSEN | G1ASD        |               |                | AC<1:0> |           | _       | 0001 01              | 0001 01                         |  |

| 69Eh               | COG1ASD1                                                 | —           | —       | —            | _             | G1AS3E         | G1AS2E  | G1AS1E    | G1AS0E  | 0000                 | 0000                            |  |

| 69Fh               | COG1STR                                                  | G1SDATD     | G1SDATC | G1SDATB      | G1SDATA       | G1STRD         | G1STRC  | G1STRB    | G1STRA  | 0000 0001            | 0000 0001                       |  |

|                    |                                                          |             |         |              |               |                |         |           |         |                      |                                 |  |

| Dann  | 14 21  |               |   |   |

|-------|--------|---------------|---|---|

| x0Ch/ | _      | Unimplemented | - | _ |

| x8Ch  |        |               |   |   |

| —     |        |               |   |   |

| x1Fh/ |        |               |   |   |

| x9Fh  |        |               |   |   |

| 1     | يا ي ا |               |   |   |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note Unimplemented, read as '1'. 1:

PIC16(L)F1704 only. 2:

3:

PIC16(L)F1708 only. Unimplemented on PIC16LF1704/8. 4:

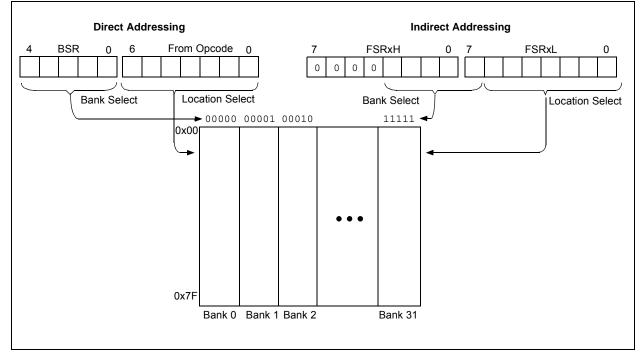

## 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## 5.3 Register Definitions: BOR Control

## REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u     | R/W-0/u              | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-------------|----------------------|-----|-----|-----|-----|-----|--------|

| SBOREN      | BORFS <sup>(1)</sup> | —   | —   | —   | —   | —   | BORRDY |

| bit 7 bit 0 |                      |     |     |     |     |     |        |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR.<br><u>If BOREN &lt;1:0&gt; in Configuration Words = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>BORFS: Brown-out Reset Fast Start bit<sup>(1)</sup></li> <li><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u></li> <li>BORFS is Read/Write, but has no effect.</li> <li><u>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u></li> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> <li>0 = Band gap operates normally, and may turn off</li> </ul> |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                                                                             |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

| TABLE J- | TABLE 3-3. SUMMART OF REGISTERS ASSOCIATED WITH RESETS |        |       |            |       |       |       |        |                     |  |

|----------|--------------------------------------------------------|--------|-------|------------|-------|-------|-------|--------|---------------------|--|

| Name     | Bit 7                                                  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |  |

| BORCON   | SBOREN                                                 | BORFS  | _     |            | —     |       |       | BORRDY | 56                  |  |

| PCON     | STKOVF                                                 | STKUNF | _     | RWDT       | RMCLR | RI    | POR   | BOR    | 60                  |  |

| STATUS   | _                                                      | _      | _     | TO         | PD    | Z     | DC    | С      | 23                  |  |

| WDTCON   | _                                                      |        |       | WDTPS<4:0> |       |       |       |        | 100                 |  |

TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/                      | 0 R/W-0/0                           | R/W-0/0                                       | U-0            | R/W-0/0       | R/W-0/0                           | R/W-0/0           | R/W-0/0     |  |  |

|-----------------------------|-------------------------------------|-----------------------------------------------|----------------|---------------|-----------------------------------|-------------------|-------------|--|--|

| OSFIF                       | C2IF                                | C1IF                                          | _              | BCL1IF        | TMR6IF                            | TMR4IF            | CCP2IF      |  |  |

| bit 7                       |                                     |                                               |                |               |                                   |                   | bit (       |  |  |

|                             |                                     |                                               |                |               |                                   |                   |             |  |  |

| <b>Legend:</b><br>R = Reada | able bit                            | W = Writable                                  |                | II – Unimplor | monted bit read                   | 1 00 '0'          |             |  |  |

|                             | inchanged                           | x = Bit is unkr                               |                | •             | nented bit, reac<br>at POR and BO |                   | thar Pasate |  |  |

| '1' = Bit is                | 0                                   | 0' = Bit is clear                             |                |               | at FOR and BO                     | rt/value at all c |             |  |  |

| 1 - Di(13                   | 301                                 |                                               |                |               |                                   |                   |             |  |  |

| bit 7                       | <b>OSFIF:</b> Osci                  | llator Fail Interru                           | pt Flag bit    |               |                                   |                   |             |  |  |

|                             | 1 = Interrupt                       |                                               |                |               |                                   |                   |             |  |  |

|                             | 0 = Interrupt                       | is not pending                                |                |               |                                   |                   |             |  |  |

| bit 6                       |                                     | arator C2 Interru                             | ipt Flag bit   |               |                                   |                   |             |  |  |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending                  |                |               |                                   |                   |             |  |  |

| bit 5                       | C1IF: Compa                         | arator C1 Interru                             | pt Flag bit    |               |                                   |                   |             |  |  |

|                             | 1 = Interrupt                       |                                               |                |               |                                   |                   |             |  |  |

|                             | 0 = Interrupt                       | is not pending                                |                |               |                                   |                   |             |  |  |

| bit 4                       | Unimplemer                          | nted: Read as '                               | )'             |               |                                   |                   |             |  |  |

| bit 3                       | BCL1IF: MS                          | BCL1IF: MSSP Bus Collision Interrupt Flag bit |                |               |                                   |                   |             |  |  |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending                  |                |               |                                   |                   |             |  |  |

| bit 2                       | TMR6IF: Tim                         | er6 to PR6 Inte                               | rrupt Flag bit | :             |                                   |                   |             |  |  |

|                             | 1 = Interrupt                       |                                               |                |               |                                   |                   |             |  |  |

|                             | 0 = Interrupt                       | is not pending                                |                |               |                                   |                   |             |  |  |

| bit 1                       |                                     | er4 to PR4 Inte                               | rrupt Flag bit | İ             |                                   |                   |             |  |  |

|                             | 1 = Interrupt                       | 1 0                                           |                |               |                                   |                   |             |  |  |

| bit 0                       | -                                   | is not pending                                | a hit          |               |                                   |                   |             |  |  |

|                             | 1 = Interrupt                       | P2 Interrupt Fla                              | y bit          |               |                                   |                   |             |  |  |

|                             |                                     | is not pending                                |                |               |                                   |                   |             |  |  |

| Note:                       | Interrupt flag bits a               |                                               |                |               |                                   |                   |             |  |  |

|                             | condition occurs, its corresponding |                                               |                |               |                                   |                   |             |  |  |

|                             | Enable bit, GIE,                    |                                               |                |               |                                   |                   |             |  |  |

|                             | User software                       | should ensu                                   | ire the        |               |                                   |                   |             |  |  |

|                             | appropriate intern                  |                                               | re clear       |               |                                   |                   |             |  |  |

|                             | prior to enabling a                 | an interrupt.                                 |                |               |                                   |                   |             |  |  |

## REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 22.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 5.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## 17.1 **PWMx Pin Configuration**

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

#### 17.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

Note: The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

**Note:** The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

#### 17.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

#### 17.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 17-1.

## EQUATION 17-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$

(TMR2 Prescale Value)

```

Note: Tosc = 1/Fosc

```

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

#### 17.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 17-2 is used to calculate the PWM pulse width.

Equation 17-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 17-2: PULSE WIDTH

$Pulse Width = (PWMxDCH:PWMxDCL<7:6>) \bullet$

Tosc • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

## EQUATION 17-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/FOSC, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

## 20.3 Register Definitions: ADC Control

## REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| U-0             | R/W-0/0                                                  | R/W-0/0                                      | R/W-0/0        | R/W-0/0            | R/W-0/0       | R/W-0/0           | R/W-0/0      |  |  |  |  |

|-----------------|----------------------------------------------------------|----------------------------------------------|----------------|--------------------|---------------|-------------------|--------------|--|--|--|--|

| _               |                                                          |                                              | CHS<4:0>       |                    |               | GO/DONE           | ADON         |  |  |  |  |

| oit 7           |                                                          |                                              |                |                    |               |                   | bit (        |  |  |  |  |

|                 |                                                          |                                              |                |                    |               |                   |              |  |  |  |  |

| Legend:         |                                                          |                                              |                |                    |               |                   |              |  |  |  |  |

| R = Readab      |                                                          | W = Writable                                 | bit            | U = Unimplen       |               |                   |              |  |  |  |  |

| u = Bit is un   | changed                                                  | x = Bit is unkr                              | nown           | -n/n = Value a     | at POR and BO | OR/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se | et                                                       | '0' = Bit is cle                             | ared           |                    |               |                   |              |  |  |  |  |

| bit 7           | Unimpleme                                                | nted: Read as '                              | 0'             |                    |               |                   |              |  |  |  |  |

| bit 6-2         | CHS<4:0>:                                                | Analog Channel                               | Select bits    |                    |               |                   |              |  |  |  |  |

|                 |                                                          | R_Buffer1 Outp                               | ( <b>a</b> )   |                    |               |                   |              |  |  |  |  |

|                 | 11110 <b>= DA</b>                                        | C_output <sup>(1)</sup>                      |                |                    |               |                   |              |  |  |  |  |

|                 |                                                          | 11101 = Temperature Indicator <sup>(3)</sup> |                |                    |               |                   |              |  |  |  |  |

|                 |                                                          | 11100 = Reserved. No channel connected       |                |                    |               |                   |              |  |  |  |  |

|                 | 11011 <b>= Re</b>                                        | served. No char                              | nnel connecte  | d.                 |               |                   |              |  |  |  |  |

|                 | •                                                        |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | •                                                        |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | 01100 = Re                                               | served. No cha                               | nel connecte   | d                  |               |                   |              |  |  |  |  |

|                 | 01011 = AN                                               |                                              |                | <b>.</b>           |               |                   |              |  |  |  |  |

|                 | 01010 = AN                                               | 110                                          |                |                    |               |                   |              |  |  |  |  |

|                 | 01001 = AN                                               | 19                                           |                |                    |               |                   |              |  |  |  |  |

|                 | 01000 = AN                                               | 18                                           |                |                    |               |                   |              |  |  |  |  |

|                 | 00111 = AN                                               | 17                                           |                |                    |               |                   |              |  |  |  |  |

|                 | 00110 = AN                                               |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | 00101 = AN                                               | -                                            |                |                    |               |                   |              |  |  |  |  |

|                 | 00100 = AN                                               |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | 00011 = AN<br>00010 = AN                                 | -                                            |                |                    |               |                   |              |  |  |  |  |

|                 | 00001 = AN                                               |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | 00000 = AN                                               |                                              |                |                    |               |                   |              |  |  |  |  |

| bit 1           | GO/DONE:                                                 | ADC Conversion                               | n Status bit   |                    |               |                   |              |  |  |  |  |

|                 | 1 = ADC cor                                              | nversion cycle ir                            | n progress. Se | tting this bit sta | rts an ADC co | nversion cycle.   |              |  |  |  |  |

|                 |                                                          |                                              |                |                    | e ADC conver  | sion has comple   | eted.        |  |  |  |  |

|                 | 0 = ADC cor                                              | nversion comple                              | ted/not in pro | gress              |               |                   |              |  |  |  |  |

| bit 0           | ADON: ADO                                                | Enable bit                                   |                |                    |               |                   |              |  |  |  |  |

|                 | 1 = ADC is e                                             |                                              |                |                    |               |                   |              |  |  |  |  |

|                 | 0 = ADC is o                                             | disabled and cor                             | nsumes no op   | erating current    |               |                   |              |  |  |  |  |

| <b>2:</b> S     | See Section 22.0<br>See Section 14.0<br>See Section 15.0 | 0 "Fixed Voltag                              | e Reference    | (FVR)" for more    | information.  | more information  | on.          |  |  |  |  |

## 23.9 Register Definitions: ZCD Control

#### REGISTER 23-1: ZCDxCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-0/0         | U-0             | R-x/x                                                                                                                        | R/W-0/0         | U-0              | U-0                | R/W-0/0          | R/W-0/0      |  |  |  |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|--------------------|------------------|--------------|--|--|--|

| ZCDxEN          | —               | ZCDxOUT                                                                                                                      | ZCDxPOL         | —                | —                  | ZCDxINTP         | ZCDxINTN     |  |  |  |

| bit 7           | ·               |                                                                                                                              |                 |                  |                    |                  | bit 0        |  |  |  |

|                 |                 |                                                                                                                              |                 |                  |                    |                  |              |  |  |  |

| Legend:         |                 |                                                                                                                              |                 |                  |                    |                  |              |  |  |  |

| R = Readabl     | le bit          | W = Writable                                                                                                                 | bit             | U = Unimpler     | mented bit, read   | l as '0'         |              |  |  |  |

| u = Bit is und  | changed         | x = Bit is unkr                                                                                                              | nown            | -n/n = Value a   | at POR and BO      | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is se | et              | '0' = Bit is cle                                                                                                             | ared            | q = value dep    | ends on config     | uration bits     |              |  |  |  |

|                 |                 |                                                                                                                              |                 |                  |                    |                  |              |  |  |  |

| oit 7           |                 | ro-Cross Detec                                                                                                               |                 |                  |                    |                  |              |  |  |  |

|                 |                 |                                                                                                                              |                 |                  | utput to source    |                  |              |  |  |  |

|                 |                 |                                                                                                                              | •               | n operates acc   | ording to PPS a    | and TRIS contr   | OIS.         |  |  |  |

| oit 6           | •               | ted: Read as '                                                                                                               |                 |                  |                    |                  |              |  |  |  |

| oit 5           |                 | ero-Cross Dete                                                                                                               | ection Logic Le | evel bit         |                    |                  |              |  |  |  |

|                 |                 | <u>CDxPOL bit = 0</u> :<br>= ZCD pin is sinking current                                                                      |                 |                  |                    |                  |              |  |  |  |

|                 |                 | is sourcing cure                                                                                                             |                 |                  |                    |                  |              |  |  |  |

|                 | ZCDxPOL bit     | •                                                                                                                            |                 |                  |                    |                  |              |  |  |  |

|                 |                 | is sourcing cur                                                                                                              |                 |                  |                    |                  |              |  |  |  |

|                 | •               | is sinking curre                                                                                                             |                 |                  |                    |                  |              |  |  |  |

| bit 4           |                 | ero-Cross Dete<br>c output is inve                                                                                           |                 | utput Polarity b | Dit                |                  |              |  |  |  |

|                 | 0               | c output is inve                                                                                                             |                 |                  |                    |                  |              |  |  |  |

| bit 3-2         | 0               | ted: Read as '                                                                                                               |                 |                  |                    |                  |              |  |  |  |

| bit 1           | -               |                                                                                                                              |                 | errupt Enable b  | bit                |                  |              |  |  |  |

|                 |                 | <b>ZCDxINTP:</b> Zero-Cross Positive Edge Interrupt Enable bit<br>1 = ZCDIF bit is set on low-to-high ZCDx output transition |                 |                  |                    |                  |              |  |  |  |

|                 | 0 = ZCDIF bi    | t is unaffected                                                                                                              | by low-to-high  | n ZCDx_output    | transition         |                  |              |  |  |  |

| pit 0           | ZCDxINTN: Z     | Zero-Cross Neg                                                                                                               | ative Edge In   | terrupt Enable   | bit                |                  |              |  |  |  |

|                 |                 | t is set on high                                                                                                             |                 |                  |                    |                  |              |  |  |  |

|                 |                 | t is unaffected                                                                                                              |                 | — ·              |                    |                  |              |  |  |  |

| Note 1: T       | he ZCDxEN bit h | as no effect wh                                                                                                              | en the ZCDD     | IS Configuration | on bit is cleared. |                  |              |  |  |  |

| TABLE 23-1: SU | JMMARY OF REGISTERS | <b>ASSOCIATED WITH</b> | THE ZCD MODULE |

|----------------|---------------------|------------------------|----------------|

|----------------|---------------------|------------------------|----------------|

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|-------|---------|---------|-------|-------|----------|----------|---------------------|

| PIE3    | —      | —     | COGIE   | ZCDIE   | _     | —     | —        | —        | 88                  |

| PIR3    | —      | _     | CWGIF   | ZCDIF   | _     | _     | —        | _        | 91                  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL |       |       | ZCD1INTP | ZCD1INTN | 241                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

## TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | —       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 51                  |

|         | 7:0  | ZCDDIS  | _       | _        | _        | _        | _        | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

| Name    | Bit 7        | Bit 6           | Bit 5           | Bit 4          | Bit 3                 | Bit 2      | Bit 1      | Bit 0  | Register<br>on Page |

|---------|--------------|-----------------|-----------------|----------------|-----------------------|------------|------------|--------|---------------------|

| ANSELA  | —            |                 | —               | ANSA4          | —                     | ANSA2      | ANSA1      | ANSA0  | 122                 |

| CCP1CON | —            | _               | DC1B            | <1:0>          |                       | CCP1M<3:0> |            |        |                     |

| CCP2CON | —            | -               | DC2B            | <1:0>          | CCP2M<3:0>            |            |            |        | 267                 |

| INTCON  | GIE          | PEIE            | TMR0IE          | INTE           | IOCIE                 | TMR0IF     | INTF       | IOCIF  | 85                  |

| PIE1    | TMR1GIE      | ADIE            | RCIE            | TXIE           | SSP1IE                | CCP1IE     | TMR2IE     | TMR1IE | 86                  |

| PIR1    | TMR1GIF      | ADIF            | RCIF            | TXIF           | SSP1IF                | CCP1IF     | TMR2IF     | TMR1IF | 89                  |

| TMR1H   | Holding Regi | ster for the M  | ost Significan  | t Byte of the  | 16-bit TMR1 F         | 245*       |            |        |                     |

| TMR1L   | Holding Regi | ster for the Le | east Significar | nt Byte of the | 16-bit TMR1 Register  |            |            |        | 245*                |

| TRISA   | —            | _               | TRISA5          | TRISA4         | _(1)                  | TRISA2     | TRISA1     | TRISA0 | 121                 |

| T1CON   | TMR1C        | :S<1:0>         | T1CKP           | S<1:0>         | T1OSCEN               | T1SYNC     | _          | TMR10N | 253                 |

| T1GCON  | TMR1GE       | T1GPOL          | T1GTM           | T1GSPM         | T1GGO/ T1GVAL<br>DONE |            | T1GSS<1:0> |        | 254                 |

#### TABLE 25-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

**Note 1:** Unimplemented, read as '1'.

#### 28.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 28.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 28-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 28.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON1<3:0> =<br>0100), the SPI module will reset if the $\overline{SS}$<br>pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SS}$ pin control.                                                                         |

**3:** While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

© 2013-2015 Microchip Technology Inc.

## 29.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

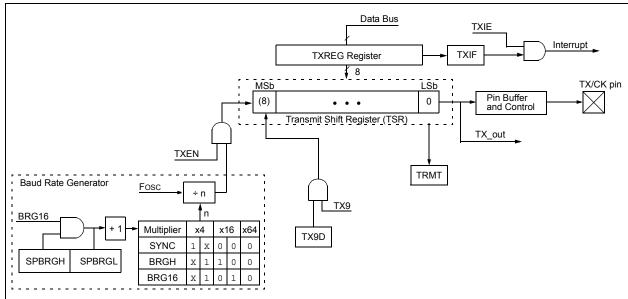

Block diagrams of the EUSART transmitter and receiver are shown in Figure 29-1 and Figure 29-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

## FIGURE 29-1: EUSART TRANSMIT BLOCK DIAGRAM

## 29.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 29.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

## 29.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 29.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 29.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

- 29.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 29.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

### 29.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |  |

## 29.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

## 29.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 29.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 29.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

<sup>© 2013-2015</sup> Microchip Technology Inc.

## TABLE 32-6: THERMAL CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated) |           |                                        |       |       |                                                          |  |  |

|---------------------------------------------------------|-----------|----------------------------------------|-------|-------|----------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.      | Characteristic                         | Тур.  | Units | Conditions                                               |  |  |

| TH01                                                    | θJA       | Thermal Resistance Junction to Ambient | 70.0  | °C/W  | 14-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 95.3  | °C/W  | 14-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 100.0 | °C/W  | 14-pin TSSOP package                                     |  |  |

|                                                         |           |                                        | 51.5  | °C/W  | 16-pin QFN 4x4mm package                                 |  |  |

|                                                         |           |                                        | 62.2  | °C/W  | 20-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 87.3  | °C/W  | 20-pin SSOP                                              |  |  |

|                                                         |           |                                        | 77.7  | °C/W  | 20-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 43.0  | °C/W  | 20-pin QFN 4x4mm package                                 |  |  |

| TH02                                                    | θJC       | Thermal Resistance Junction to Case    | 32.75 | °C/W  | 14-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 31.0  | °C/W  | 14-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 24.4  | °C/W  | 14-pin TSSOP package                                     |  |  |

|                                                         |           |                                        | 5.4   | °C/W  | 16-pin QFN 4x4mm package                                 |  |  |

|                                                         |           |                                        | 27.5  | °C/W  | 20-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 31.1  | °C/W  | 20-pin SSOP                                              |  |  |

|                                                         |           |                                        | 23.1  | °C/W  | 20-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 5.3   | °C/W  | 20-pin QFN 4x4mm package                                 |  |  |

| TH03                                                    | Тјмах     | Maximum Junction Temperature           | 150   | °C    |                                                          |  |  |

| TH04                                                    | PD        | Power Dissipation                      | —     | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                    | PINTERNAL | Internal Power Dissipation             | _     | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                    | Pi/o      | I/O Power Dissipation                  | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                    | Pder      | Derated Power                          | _     | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

Standard Operating Conditions (unless otherwise stated)

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

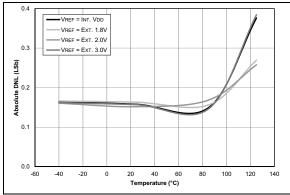

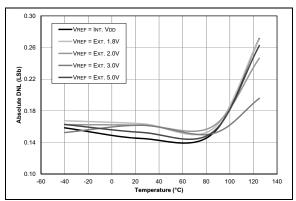

**FIGURE 33-115:** Absolute Value of DAC DNL Error, VDD = 3.0V, VREF = VDD.

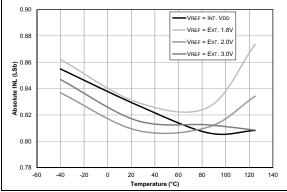

**FIGURE 33-116:** Absolute Value of DAC INL Error, VDD = 3.0V, VREF = VDD.

**FIGURE 33-117:** Absolute Value of DAC DNL Error, VDD = 5.0V, VREF = VDD, PIC16F1704/8 Only.

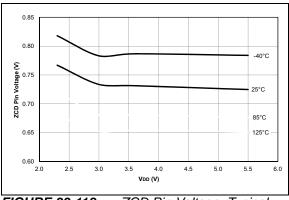

**FIGURE 33-118:** ZCD Pin Voltage. Typical Measured Values.

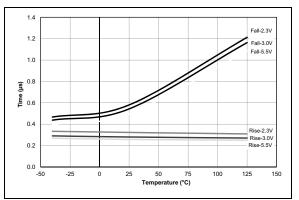

FIGURE 33-119: ZCD Response Time over Voltage, Typical Measured Values.

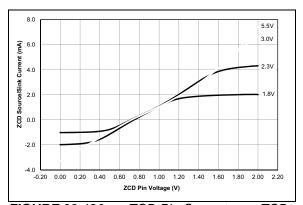

**FIGURE 33-120:** ZCD Pin Current over ZCD Pin Voltage, Typical Measured Values from -40°C to 125°C.

## 34.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 34.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 34.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 34.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

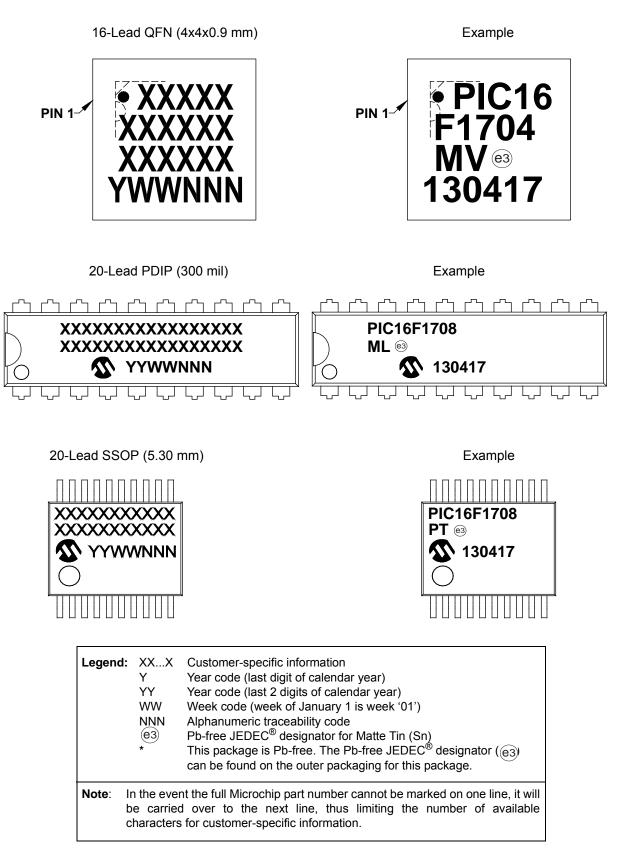

## Package Marking Information (Continued)