Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1704-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr               | Name                  | Bit 7                  | Bit 6                 | Bit 5           | Bit 4           | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|-----------------------|------------------------|-----------------------|-----------------|-----------------|--------------|---------|---------|---------|----------------------|---------------------------------|

| Banl               | k7                    |                        | •                     |                 | •               | •            | •       |         |         | •                    | •                               |

| 38Ch               | INLVLA                | _                      | —                     | INLVLA5         | INLVLA4         | INLVLA3      | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111              | 11 1111                         |

| 38Dh               | INLVLB <sup>(3)</sup> | INLVLB7                | INLVLB6               | INLVLB5         | INLVLB4         | —            | —       | _       | —       | 1111                 | 1111                            |

| 38Eh               | INLVLC                | INLVLC7 <sup>(3)</sup> | INLVLC6(3)            | INLVLC5         | INLVLC4         | INLVLC3      | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111            | 1111 1111                       |

| 38Fh               | —                     | Unimplement            | ted                   |                 |                 |              |         |         |         | —                    | —                               |

| 390h               | —                     | Unimplement            | ted                   |                 |                 |              |         |         |         | _                    | —                               |

| 391h               | IOCAP                 | —                      | —                     | IOCAP5          | IOCAP4          | IOCAP3       | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000              | 00 0000                         |

| 392h               | IOCAN                 | _                      | —                     | IOCAN5          | IOCAN4          | IOCAN3       | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000              | 00 0000                         |

| 393h               | IOCAF                 | _                      | —                     | IOCAF5          | IOCAF4          | IOCAF3       | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000              | 00 0000                         |

| 394h               | IOCBP <sup>(3)</sup>  | IOCBP7                 | IOCBP6                | IOCBP5          | IOCBP4          | —            | —       | —       | —       | 0000                 | 0000                            |

| 395h               | IOCBN <sup>(3)</sup>  | IOCBN7                 | IOCBN6                | IOCBN5          | IOCBN4          | —            | —       | —       | —       | 0000                 | 0000                            |

| 396h               | IOCBF <sup>(3)</sup>  | IOCBF7                 | IOCBF6                | IOCBF5          | IOCBF4          | —            | —       | —       | _       | 0000                 | 0000                            |

| 397h               | IOCCP                 | IOCCP7 <sup>(3)</sup>  | IOCCP6 <sup>(3)</sup> | IOCCP5          | IOCCP4          | IOCCP3       | IOCCP2  | IIOCCP1 | IOCCP0  | 0000 0000            | 0000 0000                       |

| 398h               | IOCCN                 | IOCCN7 <sup>(3)</sup>  | IOCCN6 <sup>(3)</sup> | IOCCN5          | IOCCN4          | IOCCN3       | IOCCN2  | IIOCCN1 | IOCCN0  | 0000 0000            | 0000 0000                       |

| 399h               | IOCCF                 | IOCCF7 <sup>(3)</sup>  | IOCCF6 <sup>(3)</sup> | IOCCF5          | IOCCF4          | IOCCF3       | IOCCF2  | IIOCCF1 | IOCCF0  | 0000 0000            | 0000 0000                       |

| 39Ah               | _                     | Unimplement            | ted                   |                 |                 |              |         |         |         | _                    | _                               |

| 39Fh               |                       |                        |                       |                 |                 |              |         |         |         |                      |                                 |

| Banl               | k 8                   |                        |                       |                 |                 |              |         |         |         | •                    | T                               |

| 40Ch<br><br>414h   | _                     | Unimplement            | ted                   |                 |                 |              |         |         |         | -                    | -                               |

| 415h               | TMR4                  | Holding Regi           | ster for the Lea      | ast Significant | Byte of the 16  | -bit TMR4 Re | gister  |         |         | xxxx xxxx            | uuuu uuuu                       |

| 416h               | PR4                   | Holding Regi           | ster for the Mo       | st Significant  | Byte of the 16- | bit TMR4 Reg | ister   |         |         | xxxx xxxx            | uuuu uuuu                       |

| 417h               | T4CON                 | _                      |                       | T4OUT           | PS<3:0>         |              | TMR4ON  | T4CKF   | PS<1:0> | -000 0000            | -000 0000                       |

| 418h<br><br>41Bh   | _                     | Unimplement            | ted                   |                 |                 |              |         |         |         | -                    | _                               |

| 41Ch               | TMR6                  | Holding Regi           | ster for the Lea      | ast Significant | Byte of the 16  | -bit TMR6 Re | gister  |         |         | XXXX XXXX            | uuuu uuuu                       |

| 41Dh               | PR6                   | Holding Regi           | ster for the Mo       | st Significant  | Byte of the 16- | bit TMR6 Reg | ister   |         |         | XXXX XXXX            | uuuu uuuu                       |

| 41Eh               | T6CON                 | _                      |                       | T6OUT           | PS<3:0>         |              | TMR6ON  | T6CKF   | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh               | —                     | Unimplement            | ted                   |                 |                 |              |         |         |         | —                    | —                               |

| Banl               | k 9                   |                        |                       |                 |                 |              |         |         |         |                      |                                 |

| 48Ch<br>to<br>49Fh | _                     | Unimplement            | ted                   |                 |                 |              |         |         |         | _                    | _                               |

| Banl               | k 10                  |                        |                       |                 |                 |              |         |         |         |                      |                                 |

| 50Ch               |                       |                        |                       |                 |                 |              |         |         |         |                      |                                 |

| <br>510h           | —                     | Unimplement            | ted                   |                 |                 |              |         |         |         | _                    | -                               |

| 511h               | OPA1CON               | OPA1EN                 | OPA1SP                | _               | OPA1UG          | _            | _       | OPA1P   | CH<1:0> | 00-000               | 00-000                          |

| 512h               | _                     | Unimplement            | ted                   |                 |                 |              |         |         |         | _                    | _                               |

| 514h               | 00400011              | 0.001051/              | 004000                |                 | 0040110         |              |         | 0.01157 | 011.4.6 |                      |                                 |

| 515h               | OPA2CON               | OPA2EN                 | OPA2SP                | _               | OPA2UG          | —            | —       | OPA2P   | CH<1:0> | 00-000               | 00-000                          |

| 516h<br><br>51Fh   | —                     | Unimplement            | ted                   |                 |                 |              |         |         |         | -                    | -                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-10:**

Note

Unimplemented, read as '1'. PIC16(L)F1704 only. 1:

2:

3:

PIC16(L)F1708 only. Unimplemented on PIC16LF1704/8. 4:

### 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

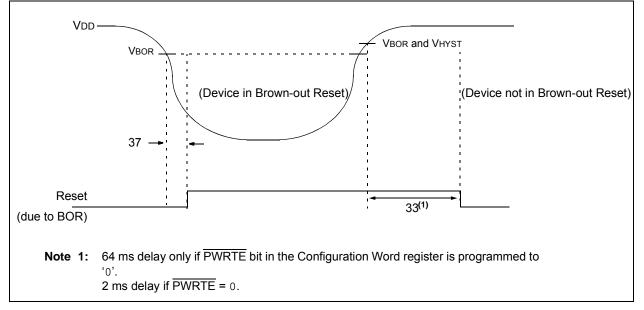

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 5-2.

# 5.14 Register Definitions: Power Control

### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |     |            |            |            |            | bit 0      |

| Legend:          |                |                                                        |                                                                   |  |  |  |  |

|------------------|----------------|--------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| HC = Bit is cle  | ared by hardwa | are                                                    | HS = Bit is set by hardware                                       |  |  |  |  |

| R = Readable     | bit            | W = Writable bit                                       | U = Unimplemented bit, read as '0'                                |  |  |  |  |

| u = Bit is unch  | anged          | x = Bit is unknown                                     | -m/n = Value at POR and BOR/Value at all other Rese               |  |  |  |  |

| '1' = Bit is set |                | '0' = Bit is cleared                                   | q = Value depends on condition                                    |  |  |  |  |

|                  |                |                                                        |                                                                   |  |  |  |  |

| bit 7            |                | ack Overflow Flag bit                                  |                                                                   |  |  |  |  |

|                  |                | Overflow occurred<br>Overflow has not occurrec         | l or cleared by firmware                                          |  |  |  |  |

| bit 6            | STKUNF: Sta    | ack Underflow Flag bit                                 |                                                                   |  |  |  |  |

|                  |                | Underflow occurred<br>Underflow has not occurre        | ed or cleared by firmware                                         |  |  |  |  |

| bit 5            | Unimplemer     | nted: Read as '0'                                      |                                                                   |  |  |  |  |

| bit 4            | RWDT: Watc     | hdog Timer Reset Flag bit                              |                                                                   |  |  |  |  |

|                  |                |                                                        | ccurred or set to '1' by firmware<br>rred (cleared by hardware)   |  |  |  |  |

| bit 3            | RMCLR: MC      | LR Reset Flag bit                                      |                                                                   |  |  |  |  |

|                  |                | Reset has not occurred or<br>Reset has occurred (clear |                                                                   |  |  |  |  |

| bit 2            | RI: RESET IN   | struction Flag bit                                     |                                                                   |  |  |  |  |

|                  |                |                                                        | executed or set to '1' by firmware<br>cuted (cleared by hardware) |  |  |  |  |

| bit 1            | POR: Power-    | -on Reset Status bit                                   |                                                                   |  |  |  |  |

|                  |                | r-on Reset occurred<br>on Reset occurred (must         | be set in software after a Power-on Reset occurs)                 |  |  |  |  |

| bit 0            | BOR: Brown     | -out Reset Status bit                                  |                                                                   |  |  |  |  |

|                  |                | n-out Reset occurred<br>out Reset occurred (must       | be set in software after a Power-on Reset or Brown-out Rese       |  |  |  |  |

# 6.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC connect to a multiplexer (see Figure 6-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

### 6.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the SPLLEN option will not be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

| R/W-0/                      | 0 R/W-0/0                           | R/W-0/0                      | U-0            | R/W-0/0       | R/W-0/0                           | R/W-0/0           | R/W-0/0     |

|-----------------------------|-------------------------------------|------------------------------|----------------|---------------|-----------------------------------|-------------------|-------------|

| OSFIF                       | C2IF                                | C1IF                         | _              | BCL1IF        | TMR6IF                            | TMR4IF            | CCP2IF      |

| bit 7                       |                                     |                              |                |               |                                   |                   | bit (       |

|                             |                                     |                              |                |               |                                   |                   |             |

| <b>Legend:</b><br>R = Reada | able bit                            | W = Writable                 |                | II – Unimplor | monted bit read                   | 1 00 '0'          |             |

|                             | inchanged                           | x = Bit is unkr              |                | •             | nented bit, reac<br>at POR and BO |                   | thar Pasate |

| '1' = Bit is                | 0                                   | 0' = Bit is clear            |                |               | at FOR and BO                     | rt/value at all c |             |

| 1 - Di(13                   | 301                                 |                              |                |               |                                   |                   |             |

| bit 7                       | <b>OSFIF:</b> Osci                  | llator Fail Interru          | pt Flag bit    |               |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 6                       |                                     | arator C2 Interru            | ipt Flag bit   |               |                                   |                   |             |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending |                |               |                                   |                   |             |

| bit 5                       | C1IF: Compa                         | arator C1 Interru            | pt Flag bit    |               |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 4                       | Unimplemer                          | nted: Read as '              | )'             |               |                                   |                   |             |

| bit 3                       | BCL1IF: MS                          | SP Bus Collisio              | n Interrupt Fl | ag bit        |                                   |                   |             |

|                             | 1 = Interrupt<br>0 = Interrupt      | is pending<br>is not pending |                |               |                                   |                   |             |

| bit 2                       | TMR6IF: Tim                         | er6 to PR6 Inte              | rrupt Flag bit | :             |                                   |                   |             |

|                             | 1 = Interrupt                       |                              |                |               |                                   |                   |             |

|                             | 0 = Interrupt                       | is not pending               |                |               |                                   |                   |             |

| bit 1                       |                                     | er4 to PR4 Inte              | rrupt Flag bit | İ             |                                   |                   |             |

|                             | 1 = Interrupt                       | 1 0                          |                |               |                                   |                   |             |

| bit 0                       | -                                   | is not pending               | a hit          |               |                                   |                   |             |

|                             | 1 = Interrupt                       | P2 Interrupt Fla             | y bit          |               |                                   |                   |             |

|                             |                                     | is not pending               |                |               |                                   |                   |             |

| Note:                       | Interrupt flag bits a               |                              |                |               |                                   |                   |             |

|                             | condition occurs, its corresponding |                              |                |               |                                   |                   |             |

|                             | Enable bit, GIE,                    |                              |                |               |                                   |                   |             |

|                             | User software                       | should ensu                  | ire the        |               |                                   |                   |             |

|                             | appropriate intern                  |                              | re clear       |               |                                   |                   |             |

|                             | prior to enabling a                 | an interrupt.                |                |               |                                   |                   |             |

# REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

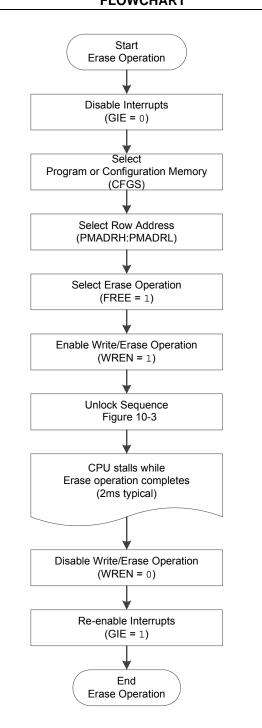

#### 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

# FIGURE 10-4: FLASH PROGRAM

# MEMORY ERASE FLOWCHART

### REGISTER 11-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0                                   | U-0        | R/W-1/1         | R/W-1/1 | U-0                                | U-0           | U-0              | U-0          |  |  |

|---------------------------------------|------------|-----------------|---------|------------------------------------|---------------|------------------|--------------|--|--|

| —                                     | —          | ANSB5           | ANSB4   | _                                  |               | —                | —            |  |  |

| bit 7                                 |            |                 |         |                                    |               |                  | bit C        |  |  |

|                                       |            |                 |         |                                    |               |                  |              |  |  |

| Legend:                               |            |                 |         |                                    |               |                  |              |  |  |

| R = Readable                          | bit        | W = Writable    | bit     | U = Unimplemented bit, read as '0' |               |                  |              |  |  |

| u = Bit is uncha                      | anged      | x = Bit is unkr | nown    | -n/n = Value a                     | at POR and BO | R/Value at all o | other Resets |  |  |

| '1' = Bit is set '0' = Bit is cleared |            |                 | ared    |                                    |               |                  |              |  |  |

|                                       |            |                 |         |                                    |               |                  |              |  |  |

| bit 7-6                               | Unimplemer | nted: Read as ' | 0'      |                                    |               |                  |              |  |  |

- bit 5-4 **ANSB<5:4>**: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled. bit 3-0 **Unimplemented:** Read as '0'

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### REGISTER 11-13: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

# 17.2 Register Definitions: PWM Control

| R/W-0/0          | U-0         | R-0/0             | R/W-0/0         | U-0             | U-0              | U-0              | U-0          |

|------------------|-------------|-------------------|-----------------|-----------------|------------------|------------------|--------------|

| PWMxEN           | —           | PWMxOUT           | PWMxPOL         | —               | —                | —                | —            |

| bit 7            |             | •                 |                 |                 |                  |                  | bit 0        |

|                  |             |                   |                 |                 |                  |                  |              |

| Legend:          |             |                   |                 |                 |                  |                  |              |

| R = Readable     | bit         | W = Writable      | bit             | U = Unimpler    | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged       | x = Bit is unkr   | nown            | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |             | '0' = Bit is clea | ared            |                 |                  |                  |              |

|                  |             |                   |                 |                 |                  |                  |              |

| bit 7            | PWMxEN: PV  | VM Module En      | able bit        |                 |                  |                  |              |

|                  |             | dule is enable    |                 |                 |                  |                  |              |

|                  | 0 = PWM mo  | dule is disable   | d               |                 |                  |                  |              |

| bit 6            | Unimplemen  | ted: Read as '    | 0'              |                 |                  |                  |              |

| bit 5            | PWMxOUT: F  | PWM module o      | utput level whe | en bit is read. |                  |                  |              |

| bit 4            | PWMxPOL: F  | PWMx Output F     | Polarity Select | bit             |                  |                  |              |

|                  |             | tput is active-lo |                 |                 |                  |                  |              |

|                  | 0 = PWM out | tput is active-hi | gh.             |                 |                  |                  |              |

| bit 3-0          | Unimplemen  | ted: Read as '    | 0'              |                 |                  |                  |              |

# REGISTER 17-1: PWMxCON: PWM CONTROL REGISTER

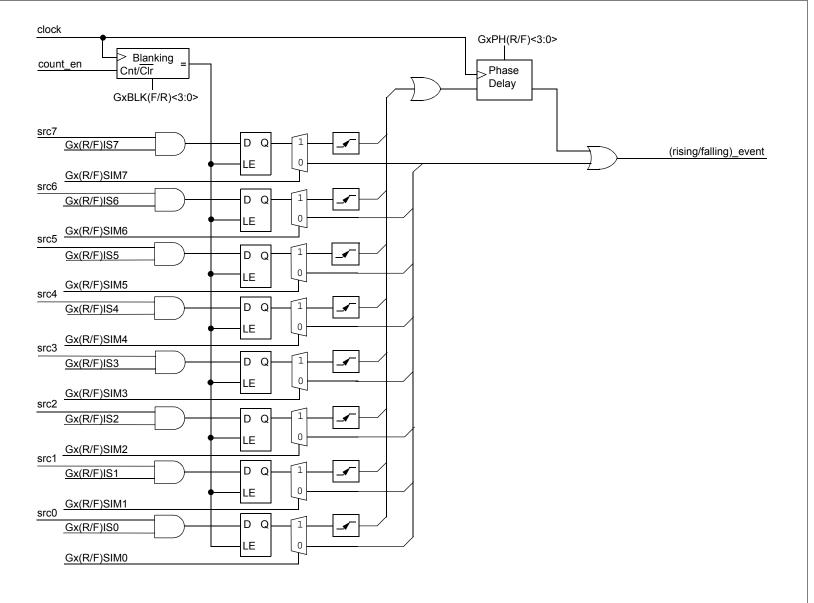

# FIGURE 18-7: COG (RISING/FALLING) INPUT BLOCK

PIC16(L)F1704/8

# 18.13 Register Definitions: COG Control

# REGISTER 18-1: COGxCON0: COG CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                    | U-0                                | R/W-0/0         | R/W-0/0        | R/W-0/0         | R/W-0/0           | R/W-0/0      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|----------------|-----------------|-------------------|--------------|--|--|

| GxEN             | GxLD                                                                                                       | _                                  | GxC             | S<1:0>         |                 | GxMD<2:0>         |              |  |  |

| bit 7            |                                                                                                            |                                    |                 |                |                 |                   | bit C        |  |  |

|                  |                                                                                                            |                                    |                 |                |                 |                   |              |  |  |

| Legend:          |                                                                                                            |                                    |                 |                |                 |                   |              |  |  |

| R = Readable     | bit                                                                                                        | W = Writable                       | bit             | U = Unimpler   | mented bit, rea | d as '0'          |              |  |  |

| u = Bit is unch  | nanged                                                                                                     | x = Bit is unki                    | nown            | -n/n = Value a | at POR and BC   | OR/Value at all o | ther Resets  |  |  |

| '1' = Bit is set |                                                                                                            | '0' = Bit is cle                   | ared            | q = Value de   | pends on cond   | tion              |              |  |  |

|                  |                                                                                                            |                                    |                 |                |                 |                   |              |  |  |

| bit 7            | GxEN: COG                                                                                                  | x Enable bit                       |                 |                |                 |                   |              |  |  |

|                  | 1 = Module i                                                                                               |                                    |                 |                |                 |                   |              |  |  |

|                  | 0 = Module i                                                                                               |                                    |                 |                |                 |                   |              |  |  |

| bit 6            |                                                                                                            | k Load Buffers                     |                 |                |                 |                   |              |  |  |

|                  |                                                                                                            | to buffer transf                   |                 |                | d with register | values on next i  | input events |  |  |

| bit 5            | Unimplemer                                                                                                 | ted: Read as '                     | 0'              |                |                 |                   |              |  |  |

| bit 4-3          | GxCS<1:0>:                                                                                                 | COGx Clock S                       | election bits   |                |                 |                   |              |  |  |

|                  | 11 = Reserved. Do not use.                                                                                 |                                    |                 |                |                 |                   |              |  |  |

|                  | <ul> <li>10 = COG_clock is HFINTOSC (stays active during Sleep)</li> <li>01 = COG clock is Fosc</li> </ul> |                                    |                 |                |                 |                   |              |  |  |

|                  |                                                                                                            | CIOCK IS FOSC                      |                 |                |                 |                   |              |  |  |

| bit 2-0          | _                                                                                                          | COGx Mode S                        | Selection bits  |                |                 |                   |              |  |  |

| 5112 0           |                                                                                                            | ved. Do not us                     |                 |                |                 |                   |              |  |  |

|                  | 101 = COG outputs operate in Push-Pull mode                                                                |                                    |                 |                |                 |                   |              |  |  |

|                  | 100 = COG                                                                                                  | outputs operate                    | e in Half-Bridg | e mode         |                 |                   |              |  |  |

|                  |                                                                                                            | outputs operate                    |                 |                |                 |                   |              |  |  |

|                  |                                                                                                            | outputs operate<br>outputs operate |                 |                |                 |                   |              |  |  |

|                  |                                                                                                            | outputs operate                    |                 |                |                 |                   |              |  |  |

|                  |                                                                                                            |                                    |                 |                |                 |                   |              |  |  |

| R/W-0/0          | U-0           | U-0                 | U-0          | R/W-x/u          | R/W-x/u            | R/W-x/u          | R/W-x/u      |

|------------------|---------------|---------------------|--------------|------------------|--------------------|------------------|--------------|

| LCxPOL           | —             | —                   | —            | LCxG4POL         | LCxG3POL           | LCxG2POL         | LCxG1POL     |

| bit 7            |               |                     |              |                  |                    |                  | bit 0        |

| Logondi          |               |                     |              |                  |                    |                  |              |

| Legend:          | a h:t         |                     | L:1          |                  | a anta d hit waa a | L == '0'         |              |

| R = Readable     |               | W = Writable        |              | •                | nented bit, read   |                  |              |

| u = Bit is unc   | •             | x = Bit is unkr     |              | -n/n = Value a   | at POR and BO      | R/Value at all c | other Resets |

| '1' = Bit is set | t             | '0' = Bit is cle    | ared         |                  |                    |                  |              |

|                  |               |                     |              |                  |                    |                  |              |

| bit 7            |               | OUT Polarity C      |              |                  |                    |                  |              |

|                  |               | out of the logic of |              |                  |                    |                  |              |

|                  |               | out of the logic of |              | erted            |                    |                  |              |

| bit 6-4          | Unimplemen    | ted: Read as '      | 0′           |                  |                    |                  |              |

| bit 3            |               | Gate 4 Output       | •            |                  |                    |                  |              |

|                  |               |                     |              | n applied to the | logic cell         |                  |              |

|                  | -             | out of gate 4 is r  |              |                  |                    |                  |              |

| bit 2            |               | Gate 3 Output       | •            |                  |                    |                  |              |

|                  |               | •                   |              | n applied to the | logic cell         |                  |              |

|                  |               | out of gate 3 is i  |              |                  |                    |                  |              |

| bit 1            |               | Gate 2 Output       | ,            |                  |                    |                  |              |

|                  |               | •                   |              | n applied to the | logic cell         |                  |              |

|                  |               | out of gate 2 is i  |              |                  |                    |                  |              |

| bit 0            |               | Gate 1 Output       | •            |                  |                    |                  |              |

|                  |               | 0                   |              | n applied to the | logic cell         |                  |              |

|                  | 0 = 1 he outp | out of gate 1 is i  | not inverted |                  |                    |                  |              |

### REGISTER 19-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

# 20.3 Register Definitions: ADC Control

# REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| U-0             | R/W-0/0                                                  | R/W-0/0                 | R/W-0/0        | R/W-0/0            | R/W-0/0       | R/W-0/0           | R/W-0/0      |

|-----------------|----------------------------------------------------------|-------------------------|----------------|--------------------|---------------|-------------------|--------------|

| _               |                                                          |                         | CHS<4:0>       |                    |               | GO/DONE           | ADON         |

| oit 7           |                                                          |                         |                |                    |               |                   | bit (        |

|                 |                                                          |                         |                |                    |               |                   |              |

| Legend:         |                                                          |                         |                |                    |               |                   |              |

| R = Readab      |                                                          | W = Writable            | bit            | U = Unimplen       |               |                   |              |

| u = Bit is un   | changed                                                  | x = Bit is unkr         | nown           | -n/n = Value a     | at POR and BO | OR/Value at all o | other Resets |

| '1' = Bit is se | et                                                       | '0' = Bit is cle        | ared           |                    |               |                   |              |

| bit 7           | Unimpleme                                                | nted: Read as '         | 0'             |                    |               |                   |              |

| bit 6-2         | CHS<4:0>:                                                | Analog Channel          | Select bits    |                    |               |                   |              |

|                 |                                                          | R_Buffer1 Outp          | ( <b>a</b> )   |                    |               |                   |              |

|                 | 11110 <b>= DA</b>                                        | C_output <sup>(1)</sup> |                |                    |               |                   |              |

|                 |                                                          | mperature Indica        |                |                    |               |                   |              |

|                 |                                                          | served. No char         |                |                    |               |                   |              |

|                 | 11011 <b>= Re</b>                                        | served. No char         | nnel connecte  | d.                 |               |                   |              |

|                 | •                                                        |                         |                |                    |               |                   |              |

|                 | •                                                        |                         |                |                    |               |                   |              |

|                 | 01100 = Re                                               | served. No cha          | nel connecte   | d                  |               |                   |              |

|                 | 01011 = AN                                               |                         |                | <b>.</b>           |               |                   |              |

|                 | 01010 = AN                                               | 110                     |                |                    |               |                   |              |

|                 | 01001 = AN                                               | 19                      |                |                    |               |                   |              |

|                 | 01000 = AN                                               | 18                      |                |                    |               |                   |              |

|                 | 00111 = AN                                               | 17                      |                |                    |               |                   |              |

|                 | 00110 = AN                                               |                         |                |                    |               |                   |              |

|                 | 00101 = AN                                               | -                       |                |                    |               |                   |              |

|                 | 00100 = AN                                               |                         |                |                    |               |                   |              |

|                 | 00011 = AN<br>00010 = AN                                 | -                       |                |                    |               |                   |              |

|                 | 00001 = AN                                               |                         |                |                    |               |                   |              |

|                 | 00000 = AN                                               |                         |                |                    |               |                   |              |

| bit 1           | GO/DONE:                                                 | ADC Conversion          | n Status bit   |                    |               |                   |              |

|                 | 1 = ADC cor                                              | nversion cycle ir       | n progress. Se | tting this bit sta | rts an ADC co | nversion cycle.   |              |

|                 |                                                          |                         |                |                    | e ADC conver  | sion has comple   | eted.        |

|                 | 0 = ADC cor                                              | nversion comple         | ted/not in pro | gress              |               |                   |              |

| bit 0           | ADON: ADO                                                | Enable bit              |                |                    |               |                   |              |

|                 | 1 = ADC is e                                             |                         |                |                    |               |                   |              |

|                 | 0 = ADC is o                                             | disabled and cor        | nsumes no op   | erating current    |               |                   |              |

| <b>2:</b> S     | See Section 22.0<br>See Section 14.0<br>See Section 15.0 | 0 "Fixed Voltag         | e Reference    | (FVR)" for more    | information.  | more information  | on.          |

| FIGURE 28-9:                          | SPI N            | IODE W                  | /AVEFO                                                                                           | RM (SL                                        | AVE MC                                                                                                | DE WIT           | HCKE                                                                                             | = 0)                                          |                                                                    |                                                                                             |                  |

|---------------------------------------|------------------|-------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------|

|                                       |                  |                         |                                                                                                  |                                               |                                                                                                       |                  |                                                                                                  |                                               |                                                                    |                                                                                             | <br>[            |

| 60%<br>(CRP = 6<br>C%E = 0)           |                  |                         |                                                                                                  |                                               |                                                                                                       |                  |                                                                                                  |                                               |                                                                    |                                                                                             |                  |

|                                       | A<br>:<br>:<br>: |                         |                                                                                                  | ·<br>·                                        | ,<br>,                                                                                                |                  | c                                                                                                |                                               | ,<br>,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                       |                                                                                             | 3<br>            |

| Vorse to<br>Sisterative<br>Vorse      |                  |                         | 8<br>8<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 | *<br>*<br>*<br>*                              | 4<br>5<br>5<br>6<br>6<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | . /              | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2      |                                               | *<br>*<br>*<br>*<br>*                                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ·<br>·<br>·<br>· |

| - 800<br>- 803                        |                  | 1/5<br>;<br>;<br>;<br>; | ,,,,,,,,                                                                                         | X<br>,<br>,<br>,,                             | , ~,<br>,<br>,<br>, , , , , , , , , , , , , , ,                                                       | × 198, 3<br>     | <br>;<br>;;;;;;;;;;;;;;;;;;;;;;;;;;;;                                                            | X                                             |                                                                    | ;;<br>;<br>;<br>//////////////////////////                                                  |                  |

| inorit<br>Særspie                     |                  | 2002 7<br>              | 2<br>2<br>2<br>2<br>4<br>4<br>2<br>2<br>2                                                        | 5<br>5<br>7<br>7<br>7                         | :<br>:<br>:                                                                                           |                  | 2<br>2<br>2<br>5<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 | :<br>;<br>;<br>;                              |                                                                    | 20<br>%<br>                                                                                 |                  |

| SSP4F<br>Interropt<br>Flag            | •<br>•<br>•<br>• | ;<br>;<br>;<br>;        | 6<br>6<br>9<br>9<br>9                                                                            | <<br><<br>:<br>:<br>:<br>:                    | e<br>-<br>-<br>-<br>                                                                                  | :<br>:<br>:<br>: | 5<br>5<br>5<br>5<br>5<br>5<br>7                                                                  |                                               | 2 .<br>2 .<br>2 .<br>2 .<br>2 .<br>2 .<br>2 .<br>2 .<br>2 .<br>2 . | :<br>:<br>:<br>:<br>:<br>:                                                                  |                  |

| 98298 &<br>892802                     | , .<br>, .<br>,  |                         | 2<br>2<br>2<br>2                                                                                 | ><br>;<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | s<br>s                                                                                                |                  | 2<br>2<br>2<br>2                                                                                 | ><br>;<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 4 5<br>4 5<br>4                                                    |                                                                                             |                  |

| Varias Codisson<br>Generation Science |                  |                         |                                                                                                  |                                               | ****                                                                                                  |                  |                                                                                                  |                                               |                                                                    |                                                                                             |                  |

### FIGURE 28-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SS           SCK           (CKP = 0           CKE = 1)           SCK           (CKP = 1           CKE = 1)           Write to           SSPBUF           XxXX |                  |             |                            |                            |                       |                          |                       |                     |                     |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|----------------------------|----------------------------|-----------------------|--------------------------|-----------------------|---------------------|---------------------|----------------|

| SDO ——                                                                                                                                                        | <u></u>          | bit 7       | bit 6                      | bit 5                      | bit 4                 | bit 3                    | bit 2                 | bit 1               | bit 0               |                |

| SDI ——                                                                                                                                                        | 1<br>1<br>1      | bit 7       |                            |                            | $\sim$                |                          | $\sim$                | $\sim$              | bit 0               |                |

| Input<br>Sample                                                                                                                                               | 1<br>1<br>1<br>1 | <u> </u>    | 1                          | 1                          | 1                     | <u>↑</u>                 | <b>†</b>              | 1                   | 1                   | <br> <br> <br> |

| SSPIF<br>Interrupt<br>Flag                                                                                                                                    | 1<br>1<br>1<br>1 |             | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1 | I<br>I<br>I<br>I<br>I | <br> <br> <br> <br> <br> | 1<br>1<br>1<br>1<br>1 | <br> <br> <br> <br> | <br> <br> <br> <br> |                |

| SSPSR to<br>SSPBUF                                                                                                                                            | 1<br>1<br>1      | 1<br>1<br>1 | <br> <br> <br>             | I                          | 1<br>1<br>1           | 1<br>1<br>1<br>1         | 1<br>1<br>1           | 1<br>1<br>1<br>1    |                     | ۱<br>چ.<br>    |

| Witte Collesion<br>Antaction politie                                                                                                                          |                  |             |                            |                            |                       |                          |                       |                     |                     | ۱<br>۱         |

### REGISTER 28-2: SSP1CON1: SSP CONTROL REGISTER 1 (CONTINUED)

- bit 3-0 SSPM<3:0>: Synchronous Serial Port Mode Select bits

- 1111 = I<sup>2</sup>C Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- 1101 = Reserved

- 1100 = Reserved

- $1011 = I^2C$  firmware controlled Master mode (slave idle)

- 1010 = SPI Master mode, clock = Fosc/(4 \* (SSPADD+1))<sup>(5)</sup>

- 1001 = Reserved

- 1000 =  $I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))<sup>(4)</sup>

- 0111 =  $I^2C$  Slave mode, 10-bit address

- 0110 =  $I^2C$  Slave mode, 7-bit address

- 0101 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control disabled,  $\overline{SS}$  can be used as I/O pin

- 0100 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control enabled

- 0011 = SPI Master mode, clock = T2\_match/2

- 0010 = SPI Master mode, clock = Fosc/64

- 0001 = SPI Master mode, clock = Fosc/16

- 0000 = SPI Master mode, clock = Fosc/4

- **Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

- **2:** When enabled, these pins must be properly configured as input or output. Use SSPSSPPS, SSPCLKPPS, SSPDATPPS, and RxyPPS to select the pins.

- **3:** When enabled, the SDA and SCL pins must be configured as inputs. Use SSPCLKPPS, SSPDATPPS, and RxyPPS to select the pins.

- **4:** SSPADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- **5:** SSPADD value of '0' is not supported. Use SSPM = 0000 instead.

# FIGURE 29-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

## FIGURE 29-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

$\Omega^{*}$  . The SUSARY remains is idea while the VCDE bit is set

. .

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |  |  |  |  |  |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                      |  |  |  |  |

|------------------|------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] OPTION                                       |  |  |  |  |

| Operands:        | None                                                 |  |  |  |  |

| Operation:       | (W) $\rightarrow$ OPTION_REG                         |  |  |  |  |

| Status Affected: | None                                                 |  |  |  |  |

| Description:     | Move data from W register to<br>OPTION_REG register. |  |  |  |  |

| Words:           | 1                                                    |  |  |  |  |

| Cycles:          | 1                                                    |  |  |  |  |

| Example:         | OPTION                                               |  |  |  |  |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F  |  |  |  |  |

|                  | After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F   |  |  |  |  |

| RESET            | Software Reset                                                                 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RESET                                                                  |  |  |  |  |

| Operands:        | None                                                                           |  |  |  |  |

| Operation:       | Execute a device Reset. Resets the RI flag of the PCON register.               |  |  |  |  |

| Status Affected: | None                                                                           |  |  |  |  |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |  |  |  |  |

#### TABLE 32-4: I/O PORTS

| Param.<br>No. | Sym.  | Characteristic                       | Min.              | Тур.† | Max.     | Units | Conditions                                                                                                                              |

|---------------|-------|--------------------------------------|-------------------|-------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

|               | VIL   | Input Low Voltage                    | 11                |       |          |       | I.                                                                                                                                      |

|               |       | I/O PORT:                            |                   |       |          |       |                                                                                                                                         |

| D034          |       | with TTL buffer                      | _                 | _     | 0.8      | V     | $4.5V \le V \text{DD} \le 5.5V$                                                                                                         |

| D034A         |       |                                      | —                 | _     | 0.15 Vdd | V     | $1.8V \le V\text{DD} \le 4.5V$                                                                                                          |

| D035          |       | with Schmitt Trigger buffer          | —                 | _     | 0.2 Vdd  | V     | $2.0V \le V\text{DD} \le 5.5V$                                                                                                          |

|               |       | with I <sup>2</sup> C levels         | _                 | _     | 0.3 VDD  | V     |                                                                                                                                         |

|               |       | with SMBus levels                    | —                 | _     | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                                                                                          |

| D036          |       | MCLR, OSC1 (RC mode)                 | _                 | _     | 0.2 Vdd  | V     | (Note 1)                                                                                                                                |

| D036A         |       | OSC1 (HS mode)                       | —                 | _     | 0.3 VDD  | V     |                                                                                                                                         |