Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1704-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3-5: PIC16(L)F1704/8 MEMORY MAP, BANK 8-23

|              | BANK 8                        |              | BANK 9                        |              | BANK 10                       |               | BANK 11                       |              | BANK 12                       |               | BANK 13                       |              | BANK 14                       |              | BANK 15                       |

|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|

| 400h         |                               | 480h         |                               | 500h         |                               | 580h          |                               | 600h         |                               | 680h          |                               | 700h         |                               | 780h         |                               |

|              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |

| 40Bh         |                               | 48Bh         |                               | 50Bh         |                               | 58Bh          |                               | 60Bh         |                               | 68Bh          |                               | 70Bh         |                               | 78Bh         |                               |

| 40Ch         | _                             | 48Ch         | _                             | 50Ch         | _                             | 58Ch          |                               | 60Ch         |                               | 68Ch          | _                             | 70Ch         |                               | 78Ch         |                               |

| 40Dh         |                               | 48Dh         |                               | 50Dh         | _                             | 58Dh          | _                             | 60Dh         | _                             | 68Dh          | _                             | 70Dh         |                               | 78Dh         | _                             |

| 40Eh         | —                             | 48Eh         | —                             | 50Eh         | —                             | 58Eh          | _                             | 60Eh         |                               | 68Eh          |                               | 70Eh         | _                             | 78Eh         |                               |

| 40Fh         | _                             | 48Fh         | _                             | 50Fh         | _                             | 58Fh          | _                             | 60Fh         | _                             | 68Fh          |                               | 70Fh         | _                             | 78Fh         |                               |

| 410h         | _                             | 490h         | _                             | 510h         |                               | 590h          | _                             | 610h         | —                             | 690h          | —                             | 710h         |                               | 790h         |                               |

| 411h         | —                             | 491h         | —                             | 511h         | OPA1CON                       | 591h          |                               | 611h         |                               | 691h          | COG1PHR                       | 711h         | _                             | 791h         |                               |

| 412h         | —                             | 492h         | —                             | 512h         | —                             | 592h          |                               | 612h         | _                             | 692h          | COG1PHF                       | 712h         |                               | 792h         |                               |

| 413h         | _                             | 493h         | —                             | 513h         | _                             | 593h          |                               | 613h         |                               | 693h          | COG1BLKR                      | 713h         |                               | 793h         |                               |

| 414h         |                               | 494h         | _                             | 514h         | -                             | 594h          | —                             | 614h         |                               | 694h          | COG1BLKF<br>COG1DBR           | 714h         |                               | 794h         |                               |

| 415h         | TMR4                          | 495h         | _                             | 515h         | OPA2CON                       | 595h          |                               | 615h         |                               | 695h          | COGIDBR                       | 715h         |                               | 795h         |                               |

| 416h         | PR4                           | 496h         | _                             | 516h         | _                             | 596h          | —                             | 616h         | PWM3DCL                       | 696h          | COG1CON0                      | 716h         |                               | 796h         | —                             |

| 417h         | T4CON                         | 497h<br>498h | _                             | 517h         | —                             | 597h<br>598h  | —                             | 617h         |                               | 697h<br>698h  | COG1CON0                      | 717h         |                               | 797h<br>798h | —                             |

| 418h         | _                             | 498n<br>499h |                               | 518h         |                               | 598n<br>599h  |                               | 618h         | PWM3DCH<br>PWM3CON            | 698n<br>699h  | COG1RIS                       | 718h<br>719h |                               | 798n<br>799h |                               |

| 419h         |                               |              |                               | 519h         |                               |               |                               | 619h         |                               |               | COG1RSIM                      | -            |                               |              |                               |

| 41Ah         |                               | 49Ah<br>49Bh |                               | 51Ah<br>51Bh |                               | 59Ah<br>59Bh  |                               | 61Ah         | PWM4DCL<br>PWM4DCH            | 69Ah<br>69Bh  | COGIFIS                       | 71Ah         |                               | 79Ah<br>79Bh |                               |

| 41Bh         | <br>TMR6                      | 49Bn<br>49Ch |                               | 51Ch         |                               | 59BN          |                               | 61Bh<br>61Ch | PWM4DCH<br>PWM4CON            | 69Ch          | COG1FSIM                      | 71Bh<br>71Ch |                               | 79Bn<br>79Ch |                               |

| 41Ch<br>41Dh | PR6                           | 49Ch<br>49Dh |                               | 51Dh         |                               | 59Ch          |                               | 61Dh         |                               | 69Ch          | COG1ASD0                      | 71Dh         |                               | 79Ch         |                               |

| 41Dh<br>41Eh | T6CON                         | 49Dh<br>49Eh |                               | 51Eh         |                               | 59Eh          |                               | 61Eh         |                               | 69Eh          | COG1ASD1                      | 71Eh         |                               | 79Dh         |                               |

| 41En<br>41Fh | -                             | 49En<br>49Fh |                               | 51En         |                               | 59En          |                               | 61Fh         |                               | 69Eh          | COG1STR                       | 71En         |                               | 79En         |                               |

| 420h         |                               | 4A0h         |                               | 520h         |                               | 5A0h          |                               | 620h         |                               | 6A0h          | 0001011                       | 720h         |                               | 7A0h         |                               |

|              |                               |              |                               |              |                               |               |                               |              |                               |               |                               |              |                               |              |                               |

|              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |               | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |               | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |

| 46Fh         |                               | 4EFh         |                               | 56Fh         |                               | 5EFh          |                               | 66Fh         |                               | 6EFh          |                               | 76Fh         |                               | 7EFh         |                               |

| 470h         |                               | 4F0h         |                               | 570h         |                               | 5F0h          |                               | 670h         |                               | 6F0h          |                               | 770h         |                               | 7F0h         |                               |

| 17 011       | Accesses                      |              | Accesses                      | 07011        | Accesses                      | 01 011        | Accesses                      | 01011        | Accesses                      | 01 011        | Accesses                      | 11011        | Accesses                      |              | Accesses                      |

|              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |

|              | 7011 - 7111                   |              | 7011-7111                     |              | 7011 - 7111                   |               | 7011 - 7111                   | 0751         | 7011-7111                     |               | 7011-7111                     |              | 7011-7111                     |              | 7011 - 7111                   |

| 47Fh         |                               | 4FFh         |                               | 57Fh         |                               | 5FFh          |                               | 67Fh         |                               | 6FFh          |                               | 77Fh         |                               | 7FFh         |                               |

|              | BANK 16                       |              | BANK 17                       |              | BANK 18                       |               | BANK 19                       |              | BANK 20                       |               | BANK 21                       |              | BANK 22                       |              | BANK 23                       |

| 800h         | Core Registers                | 880h         | Core Registers                | 900h         | Core Registers                | 980h          | Core Registers                | A00h         | Core Registers                | A80h          | Core Registers                | B00h         | Core Registers                | B80h         | Core Registers                |

|              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |

| 80Bh         |                               | 88Bh         |                               | 90Bh         |                               | 98Bh          |                               | A0Bh         |                               | A8Bh          |                               | B0Bh         |                               | B8Bh         |                               |

| 80Ch         |                               | 88Ch         |                               | 90Ch         |                               | 98Ch          |                               | A0Ch         |                               | A8Ch          |                               | B0Ch         |                               | B8Ch         |                               |

| 00011        | Unimplemented<br>Read as '0'  | 00011        | Unimplemented<br>Read as '0'  | 00011        | Unimplemented<br>Read as '0'  | 00011         | Unimplemented<br>Read as '0'  | 710011       | Unimplemented<br>Read as '0'  | 7 loon        | Unimplemented<br>Read as '0'  | Doon         | Unimplemented<br>Read as '0'  | Doon         | Unimplemented<br>Read as '0'  |

| 86Fh         |                               | 8EFh         |                               | 96Fh         |                               | 9EFh          |                               | A6Fh         |                               | AEFh          |                               | B6Fh         |                               | BEFh         |                               |

|              |                               | 8EFN<br>8F0h |                               | 96Fn<br>970h |                               | 9EFII<br>9F0h |                               | -            |                               | AEFII<br>AF0h |                               | Born<br>B70h |                               | BF0h         |                               |

| 870h         | A                             | or nu        | A                             | 9/00         | A                             | arou          | A                             | A70h         | A                             | AFUN          | A                             | BION         | A                             | BEON         | A                             |

|              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |

|              | /011-/F11                     |              | /011 – /F11                   |              | /011 – / FN                   |               | /011-/FN                      |              | /011-/FN                      |               | /011-/FN                      |              |                               |              | 7011 – 7FN                    |

| 87Fh         |                               | 8FFh         |                               | 97Fh         |                               | 9FFh          |                               | A7Fh         |                               | AFFh          |                               | B7Fh         |                               | BFFh         |                               |

Legend: = Unimplemented data memory locations, read as '0'.

| IABI              | BLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |             |          |          |          |                              |            |             |          |                      |                                 |

|-------------------|---------------------------------------------------------|-------------|----------|----------|----------|------------------------------|------------|-------------|----------|----------------------|---------------------------------|

| Addr              | Name                                                    | Bit 7       | Bit 6    | Bit 5    | Bit 4    | Bit 3                        | Bit 2      | Bit 1       | Bit 0    | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Banl              | k 30                                                    |             |          |          |          |                              |            |             |          |                      |                                 |

| F0Ch              |                                                         |             |          |          |          |                              |            |             |          |                      |                                 |

| —<br>F0Eh         | _                                                       | Unimplement | ted      |          |          |                              |            |             |          | _                    | _                               |

| F0Fh              | CLCDATA                                                 | _           | _        | _        | _        | _                            | MLC3OUT    | MLC2OUT     | MLC1OUT  | 000                  | 000                             |

| F10h              | CLC1CON                                                 | LC1EN       | _        | LC10UT   | LC1INTP  | LC1INTN                      | l          | _C1MODE<2:0 | )>       | 0-x0 0000            | 0-00 0000                       |

| F11h              | CLC1POL                                                 | LC1POL      | _        | _        | _        | LC1G4POL                     | LC1G3POL   | LC1G2POL    | LC1G1POL | x xxxx               | 0 uuuu                          |

| F12h              | CLC1SEL0                                                | _           | _        | _        |          |                              | LC1D1S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F13h              | CLC1SEL1                                                | _           | _        | -        |          |                              | LC1D2S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F14h              | CLC1SEL2                                                | _           | _        | -        |          |                              | LC1D3S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F15h              | CLC1SEL3                                                | _           | _        | _        |          |                              | LC1D4S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F16h              | CLC1GLS0                                                | LC1G1D4T    | LC1G1D4N | LC1G1D3T | LC1G1D3N | LC1G1D2T                     | LC1G1D2N   | LC1G1D1T    | LC1G1D1N | XXXX XXXX            | uuuu uuuu                       |

| F17h              | CLC1GLS1                                                | LC1G2D4T    | LC1G2D4N | LC1G2D3T | LC1G2D3N | LC1G2D2T                     | LC1G2D2N   | LC1G2D1T    | LC1G2D1N | XXXX XXXX            | uuuu uuuu                       |

| F18h              | CLC1GLS2                                                | LC1G3D4T    | LC1G3D4N | LC1G3D3T | LC1G3D3N | LC1G3D2T                     | LC1G3D2N   | LC1G3D1T    | LC1G3D1N | xxxx xxxx            | uuuu uuuu                       |

| F19h              | CLC1GLS3                                                | LC1G4D4T    | LC1G4D4N | LC1G4D3T | LC1G4D3N | LC1G4D2T                     | LC1G4D2N   | LC1G4D1T    | LC1G4D1N | xxxx xxxx            | uuuu uuuu                       |

| F1Ah              | CLC2CON                                                 | LC2EN       | —        | LC2OUT   | LC2INTP  | LC2INTP LC2INTN LC2MODE<2:0> |            |             |          |                      | 0-00 0000                       |

| F1Bh              | CLC2POL                                                 | LC2POL      | —        |          | —        | LC2G4POL                     | LC2G3POL   | LC2G2POL    | LC2G1POL | 0 xxxx               | 0 uuuu                          |

| F1Ch              | CLC2SEL0                                                | —           | -        |          |          |                              | LC2D1S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F1Dh              | CLC2SEL1                                                | —           | -        |          |          |                              | LC2D2S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F1Eh              | CLC2SEL2                                                | —           | —        |          |          |                              | LC2D3S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F1Fh              | CLC2SEL3                                                | —           | -        |          |          |                              | LC2D4S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F20h              | CLC2GLS0                                                | LC2G1D4T    | LC2G1D4N | LC2G1D3T | LC2G1D3N | LC2G1D2T                     | LC2G1D2N   | LC2G1D1T    | LC2G1D1N | XXXX XXXX            | uuuu uuuu                       |

| F21h              | CLC2GLS1                                                | LC2G2D4T    | LC2G2D4N | LC2G2D3T | LC2G2D3N | LC2G2D2T                     | LC2G2D2N   | LC2G2D1T    | LC2G2D1N | XXXX XXXX            | uuuu uuuu                       |

| F22h              | CLC2GLS2                                                | LC2G3D4T    | LC2G3D4N | LC2G3D3T | LC2G3D3N | LC2G3D2T                     | LC2G3D2N   | LC2G3D1T    | LC2G3D1N | xxxx xxxx            | uuuu uuuu                       |

| F23h              | CLC2GLS3                                                | LC2G4D4T    | LC2G4D4N | LC2G4D3T | LC2G4D3N | LC2G4D2T                     | LC2G4D2N   | LC2G4D1T    | LC2G4D1N | XXXX XXXX            | uuuu uuuu                       |

| F24h              | CLC3CON                                                 | LC3EN       | —        | LC3OUT   | LC3INTP  | LC3INTN                      | l          | _C3MODE<2:  | )>       | 0-00 0000            | 0-00 0000                       |

| F25h              | CLC3POL                                                 | LC3POL      | —        | —        | —        | LC3G4POL                     | LC3G3POL   | LC3G2POL    | LC3G1POL | 0 xxxx               | 0 uuuu                          |

| F26h              | CLC3SEL0                                                | —           | —        |          |          |                              | LC3D1S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F27h              | CLC3SEL1                                                | —           | —        | -        |          |                              | LC3D2S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F28h              | CLC3SEL2                                                | _           | _        | _        |          |                              | LC3D3S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F29h              | CLC3SEL3                                                | _           | _        | _        |          |                              | LC3D4S<4:0 | >           |          | x xxxx               | u uuuu                          |

| F2Ah              | CLC3GLS0                                                | LC3G1D4T    | LC3G1D4N | LC3G1D3T | LC3G1D3N | LC3G1D2T                     | LC3G1D2N   | LC3G1D1T    | LC3G1D1N | XXXX XXXX            | uuuu uuuu                       |

| F2Bh              | CLC3GLS1                                                | LC3G2D4T    | LC3G2D4N | LC3G2D3T | LC3G2D3N | LC3G2D2T                     | LC3G2D2N   | LC3G2D1T    | LC3G2D1N | XXXX XXXX            | uuuu uuuu                       |

| F2Ch              | CLC3GLS2                                                | LC3G3D4T    | LC3G3D4N | LC3G3D3T | LC3G3D3N | LC3G3D2T                     | LC3G3D2N   | LC3G3D1T    | LC3G3D1N | XXXX XXXX            | uuuu uuuu                       |

| F2Dh              | CLC3GLS3                                                | LC3G4D4T    | LC3G4D4N | LC3G4D3T | LC3G4D3N | LC3G4D2T                     | LC3G4D2N   | LC3G4D1T    | LC3G4D1N | XXXX XXXX            | uuuu uuuu                       |

| F2Eh<br>—<br>F6Fh | _                                                       | Unimplement | ted      |          |          |                              |            |             |          | _                    | _                               |

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend: Note

Unimplemented, read as '1'. 1:

2: PIC16(L)F1704 only.

PIC16(L)F1708 only. 3:

Unimplemented on PIC16LF1704/8. 4:

#### 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

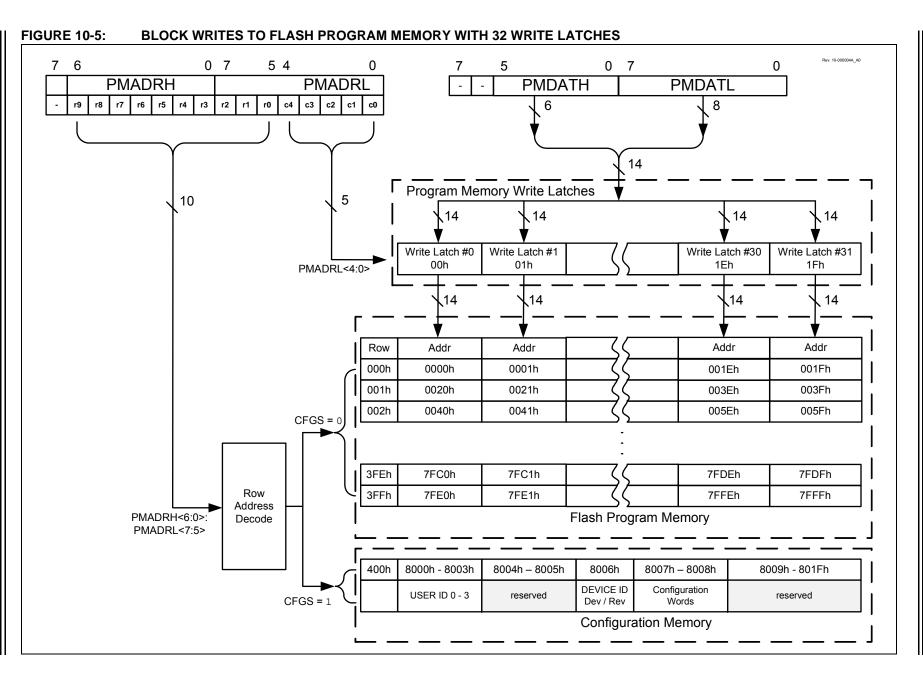

### TABLE 10-1:FLASH MEMORY<br/>ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1704 | 32                   | 32                          |

| PIC16(L)F1708 | 52                   | 52                          |

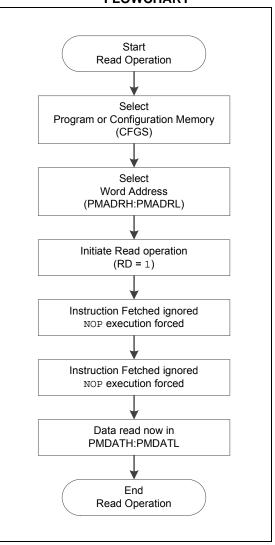

### 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPS.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

#### FIGURE 10-1:

#### FLASH PROGRAM MEMORY READ FLOWCHART

#### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### MEMORY MODIFY FLOWCHART Start Modify Operation **Read Operation** Figure 10-1 An image of the entire row read must be stored in RAM Modify Image The words to be modified are changed in the RAM image Erase Operation Figure 10-4 Write Operation use RAM image Figure 10-6 End Modify Operation

**FLASH PROGRAM**

**FIGURE 10-7:**

#### REGISTER 17-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u           | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u           | R/W-x/u |

|-------------------|---------|----------------------|---------|-----------------|--------------------|-------------------|---------|

|                   |         |                      | PWMxI   | DCH<7:0>        |                    |                   |         |

| bit 7             |         |                      |         |                 |                    |                   | bit 0   |

|                   |         |                      |         |                 |                    |                   |         |

| Legend:           |         |                      |         |                 |                    |                   |         |

| R = Readable bi   | it      | W = Writable bit     |         | U = Unimpleme   | ented bit, read as | <b>'</b> 0'       |         |

| u = Bit is unchar | nged    | x = Bit is unknow    | 'n      | -n/n = Value at | POR and BOR/V      | alue at all other | Resets  |

| '1' = Bit is set  |         | '0' = Bit is cleared | d       |                 |                    |                   |         |

bit 7-0

**PWMxDCH<7:0>:** PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 17-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u          | R/W-x/u  | U-0                | U-0 | U-0             | U-0                | U-0               | U-0    |

|------------------|----------|--------------------|-----|-----------------|--------------------|-------------------|--------|

| PWMxD            | )CL<7:6> | _                  | —   | —               | _                  | —                 | —      |

| bit 7            |          |                    | •   | •               |                    |                   | bit 0  |

|                  |          |                    |     |                 |                    |                   |        |

| Legend:          |          |                    |     |                 |                    |                   |        |

| R = Readable b   | pit      | W = Writable bi    | t   | U = Unimpleme   | ented bit, read as | ʻ0'               |        |

| u = Bit is uncha | nged     | x = Bit is unkno   | wn  | -n/n = Value at | POR and BOR/V      | alue at all other | Resets |

| '1' = Bit is set |          | '0' = Bit is clear | ed  |                 |                    |                   |        |

bit 5-0 Unimplemented: Read as '0'

#### TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name    | Bit 7             | Bit 6                  | Bit 5   | Bit 4           | Bit 3           | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|---------|-------------------|------------------------|---------|-----------------|-----------------|--------|---------|---------|---------------------|

| CCPTMRS | P4TSE             | L<1:0>                 | P3TSE   | EL<1:0>         | C2TSE           | L<1:0> | C1TSE   | 260     |                     |

| PR2     |                   |                        | -       | Timer2 module I | Period Register |        |         |         | 256                 |

| PWM3CON | PWM3EN            | _                      | PWM3OUT | PWM3POL         | _               | _      | _       | _       | 167                 |

| PWM3DCH |                   | PWM3DCH<7:0>           |         |                 |                 |        |         |         |                     |

| PWM3DCL | PWM3D             | CL<7:6>                | _       | _               | _               | _      | _       | _       | 168                 |

| PWM4CON | PWM4EN            | _                      | PWM4OUT | PWM4POL         | _               | _      | _       | _       | 167                 |

| PWM4DCH |                   |                        |         | PWM4D0          | CH<7:0>         |        |         |         | 168                 |

| PWM4DCL | PWM4D             | CL<7:6>                | _       | _               | _               | _      | _       | _       | 168                 |

| RxyPPS  | — — — RxyPPS<4:0> |                        |         |                 |                 |        |         | 140     |                     |

| T2CON   | _                 | TOUTPS3                | TOUTPS2 | TOUTPS1         | TOUTPS0         | TMR2ON | T2CKPS1 | T2CKPS0 | 258                 |

| TMR2    |                   | Timer2 module Register |         |                 |                 |        |         |         |                     |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

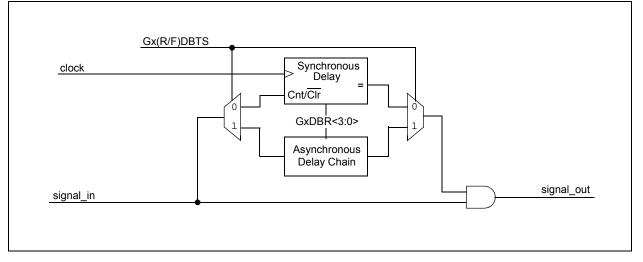

#### FIGURE 18-8: COG (RISING/FALLING) DEAD-BAND BLOCK

When the phase-delay count value is zero, phase delay is disabled and the phase-delay counter output is true, thereby, allowing the event signal to pass straight through to the complementary output driver flop.

#### 18.7.1 CUMULATIVE UNCERTAINTY

It is not possible to create more than one COG clock of uncertainty by successive stages. Consider that the phase-delay stage comes after the blanking stage, the dead-band stage comes after either the blanking or phase-delay stages, and the blanking stage comes after the dead-band stage. When the preceding stage is enabled, the output of that stage is necessarily synchronous with the COG clock, which removes any possibility of uncertainty in the succeeding stage.

#### EQUATION 18-1: PHASE, DEAD-BAND, AND BLANKING TIME CALCULATION

| $T_{\min} = \frac{Cc}{Fc}$                                 | ount<br>COG_clock |  |  |  |  |  |

|------------------------------------------------------------|-------------------|--|--|--|--|--|

| $T_{\max} = \frac{\text{Count} + 1}{F_{COG\_clock}}$       |                   |  |  |  |  |  |

| $T_{\text{uncertainty}} = T_{\text{max}} - T_{\text{min}}$ |                   |  |  |  |  |  |

| Also:<br>$T_{\text{uncertainty}} = \frac{1}{F_{Q}}$        | 1<br>COG_clock    |  |  |  |  |  |

| Where:                                                     |                   |  |  |  |  |  |

| т                                                          | Count             |  |  |  |  |  |

| Rising Phase Delay                                         | COGyPHR           |  |  |  |  |  |

| Count    |  |  |  |  |

|----------|--|--|--|--|

| COGxPHR  |  |  |  |  |

| COGxPHF  |  |  |  |  |

| COGxDBR  |  |  |  |  |

| COGxDBF  |  |  |  |  |

| COGxBLKR |  |  |  |  |

| COGxBLKF |  |  |  |  |

|          |  |  |  |  |

#### TIMER UNCERTAINTY **EXAMPLE 18-1:**

Given: Count = Ah = 10d $F_{COG, Clock} = 8 MHz$ Therefore: fore:  $T_{\text{uncertainty}} = \frac{1}{F_{COG\_clock}}$  $= \frac{1}{8MHz} = 125ns$ Proof:  $T_{\min} = \frac{Count}{F_{COG\_clock}}$  $= 125ns \bullet 10d = 1.25 \mu s$  $T_{\text{max}} = \frac{Count + 1}{F_{COG} \operatorname{clock}}$  $= 125ns \bullet (10d + 1)$  $= 1.375 \mu s$

Therefore:

$$T_{\text{uncertainty}} = T_{\text{max}} - T_{\text{min}}$$

$$= 1.375 \,\mu s - 1.25 \,\mu s$$

$$= 125 ns$$

#### 23.9 Register Definitions: ZCD Control

#### REGISTER 23-1: ZCDxCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-0/0                                                                                            | U-0                                                                      | R-x/x                             | R/W-0/0         | U-0              | U-0              | R/W-0/0          | R/W-0/0      |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|-----------------|------------------|------------------|------------------|--------------|

| ZCDxEN                                                                                             | —                                                                        | ZCDxOUT                           | ZCDxPOL         | —                | —                | ZCDxINTP         | ZCDxINTN     |

| bit 7                                                                                              | ·                                                                        |                                   |                 |                  |                  |                  | bit 0        |

|                                                                                                    |                                                                          |                                   |                 |                  |                  |                  |              |

| Legend:                                                                                            |                                                                          |                                   |                 |                  |                  |                  |              |

| R = Readabl                                                                                        | le bit                                                                   | W = Writable                      | bit             | U = Unimpler     | mented bit, read | l as '0'         |              |

| u = Bit is und                                                                                     | changed                                                                  | x = Bit is unkr                   | nown            | -n/n = Value a   | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                    | et                                                                       | '0' = Bit is cle                  | ared            | q = value dep    | ends on config   | uration bits     |              |

|                                                                                                    |                                                                          |                                   |                 |                  |                  |                  |              |

| oit 7                                                                                              |                                                                          | ro-Cross Detec                    |                 |                  |                  |                  |              |

|                                                                                                    |                                                                          |                                   |                 |                  | utput to source  |                  |              |

|                                                                                                    |                                                                          |                                   | •               | n operates acc   | ording to PPS a  | and TRIS contr   | OIS.         |

| oit 6                                                                                              | •                                                                        | Unimplemented: Read as '0'        |                 |                  |                  |                  |              |

| oit 5                                                                                              |                                                                          | ero-Cross Dete                    | ection Logic Le | evel bit         |                  |                  |              |

|                                                                                                    | ZCDxPOL bit                                                              | <u> = 0</u> :<br>is sinking curre | nt              |                  |                  |                  |              |

|                                                                                                    |                                                                          | is sourcing cure                  |                 |                  |                  |                  |              |

|                                                                                                    | ZCDxPOL bit                                                              |                                   |                 |                  |                  |                  |              |

|                                                                                                    |                                                                          | is sourcing cur                   |                 |                  |                  |                  |              |

|                                                                                                    | 0 = ZCD pin is sinking current                                           |                                   |                 |                  |                  |                  |              |

| bit 4                                                                                              |                                                                          | ero-Cross Dete                    |                 | utput Polarity b | Dit              |                  |              |

| <ul> <li>1 = ZCD logic output is inverted</li> <li>0 = ZCD logic output is not inverted</li> </ul> |                                                                          |                                   |                 |                  |                  |                  |              |

| bit 3-2                                                                                            | 0                                                                        | Unimplemented: Read as '0'        |                 |                  |                  |                  |              |

| bit 1                                                                                              | -                                                                        | ero-Cross Pos                     |                 | errupt Enable b  | bit              |                  |              |

|                                                                                                    |                                                                          | t is set on low-                  | •               | •                |                  |                  |              |

|                                                                                                    | 0 = ZCDIF bit is unaffected by low-to-high ZCDx_output transition        |                                   |                 |                  |                  |                  |              |

| pit 0                                                                                              | ZCDxINTN: Z                                                              | Zero-Cross Neg                    | ative Edge In   | terrupt Enable   | bit              |                  |              |

|                                                                                                    |                                                                          | t is set on high                  |                 |                  |                  |                  |              |

|                                                                                                    | 0 = ZCDIF bit is unaffected by high-to-low ZCDx_output transition        |                                   |                 |                  |                  |                  |              |

| Note 1: T                                                                                          | e ZCDxEN bit has no effect when the ZCDDIS Configuration bit is cleared. |                                   |                 |                  |                  |                  |              |

| TABLE 23-1: SU | JMMARY OF REGISTERS | <b>ASSOCIATED WITH</b> | THE ZCD MODULE |

|----------------|---------------------|------------------------|----------------|

|----------------|---------------------|------------------------|----------------|

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|-------|---------|---------|-------|-------|----------|----------|---------------------|

| PIE3    | —      | —     | COGIE   | ZCDIE   | _     | —     | —        | —        | 88                  |

| PIR3    | —      | _     | CWGIF   | ZCDIF   | _     | _     | —        | _        | 91                  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL |       |       | ZCD1INTP | ZCD1INTN | 241                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | —       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 51                  |

|         | 7:0  | ZCDDIS  | _       | _        | _        | _        | _        | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

#### 25.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 25.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Secondary oscillator will continue to operate in Sleep regardless of the  $\overline{T1SYNC}$  bit setting.

#### 25.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

For more information, see Section 27.0 "Capture/Compare/PWM Modules".

#### 25.10 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger an auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of Timer1 can cause an Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with an Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see **Section 27.2.4** "Auto-Conversion Trigger".

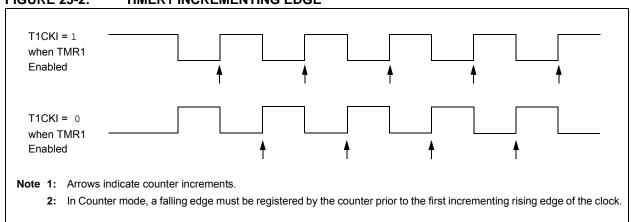

#### FIGURE 25-2: TIMER1 INCREMENTING EDGE

#### 27.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 27.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See **Section 25.0 "Timer1 Module with Gate Control"** for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 27.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 27.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1. Refer to **Section 20.2.5** "Auto-Conversion Trigger" for more information.

- Note 1: The Auto-conversion Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 27.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 27.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 27-3 shows a typical waveform of the PWM signal.

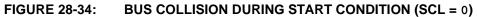

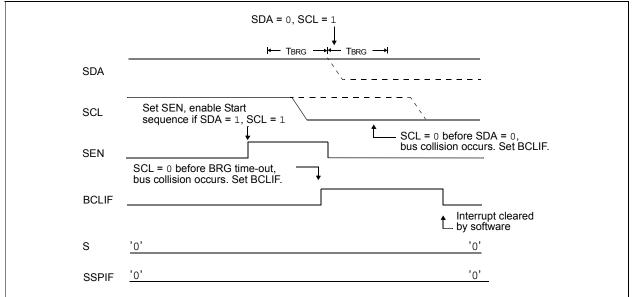

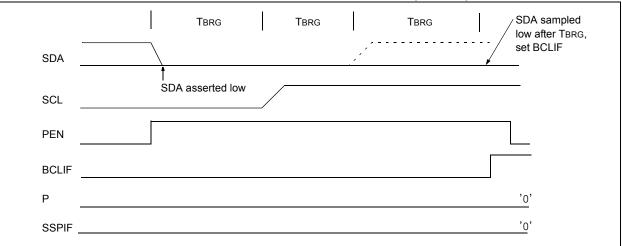

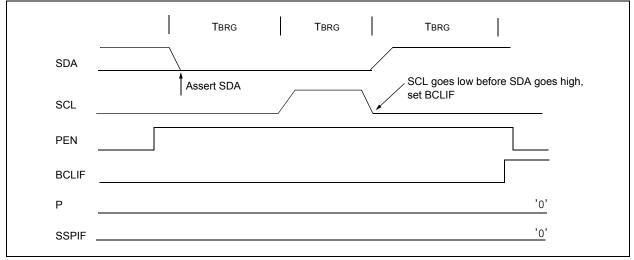

#### 28.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 28-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 28-39).

#### FIGURE 28-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 28-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### REGISTER 28-2: SSP1CON1: SSP CONTROL REGISTER 1

| REGISTER 2       | 8-2: SSP10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CON1: SSP C                                                                                                    | ONTROL R                                                                                         | EGISTER 1                                                                                                 |                                                                                                       |                                                          |                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|

| R/C/HS-0/0       | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0/0                                                                                                        | R/W-0/0                                                                                          | R/W-0/0                                                                                                   | R/W-0/0                                                                                               | R/W-0/0                                                  | R/W-0/0                                           |

| WCOL             | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SSPEN                                                                                                          | CKP                                                                                              |                                                                                                           | SSPN                                                                                                  | 1<3:0>                                                   |                                                   |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |                                                                                                  |                                                                                                           |                                                                                                       |                                                          | bit C                                             |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |                                                                                                  |                                                                                                           |                                                                                                       |                                                          |                                                   |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable                                                                                                   | bit                                                                                              | U = Unimpler                                                                                              | nented bit, read                                                                                      | d as '0'                                                 |                                                   |

| u = Bit is uncha | anged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unk                                                                                                 | nown                                                                                             | -n/n = Value a                                                                                            | at POR and BO                                                                                         | R/Value at all o                                         | other Resets                                      |

| '1' = Bit is set | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cle                                                                                               | ared                                                                                             | HS = Bit is se                                                                                            | et by hardware                                                                                        | C = User clea                                            | ared                                              |

| bit 7            | Master mode<br>1 = A write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |                                                                                                  | attempted while                                                                                           | the I <sup>2</sup> C condition                                                                        | ons were not va                                          | alid for a trans                                  |

|                  | 0 = No collisi<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ion<br>BUF register is v                                                                                       | vritten while it is                                                                              | s still transmitting                                                                                      | the previous wo                                                                                       | rd (must be clea                                         | red in software                                   |

| bit 6            | $\frac{\text{In SPI mode:}}{1 = \text{A new by}}$ the data i the SSPE is not set (must be 0 = No overfil In I <sup>2</sup> C mode: 1 = A byte is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n SSPSR is los<br>BUF, even if only<br>since each nev<br>cleared in softv<br>low<br>received while             | hile the SSPBI<br>t. Overflow car<br>/ transmitting c<br>v reception (ar<br>vare).<br>the SSPBUF | JF register is stil<br>n only occur in S<br>lata, to avoid set<br>nd transmission)<br>register is still l | I holding the pre-<br>lave mode. In SI<br>tting overflow. In<br>is initiated by w<br>holding the prev | lave mode, the u<br>Master mode, t<br>rriting to the SSI | user must reac<br>he overflow bi<br>PBUF register |