Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1704t-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.7** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

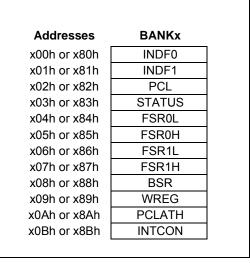

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-9.

#### TABLE 3-2: CORE REGISTERS

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 31.0 "Instruction Set Summary").

Note: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

#### 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 5-2.

#### 5.14 Register Definitions: Power Control

#### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |     |            |            |            |            | bit 0      |

| Legend:                           |                |                                                        |                                                                   |  |  |  |  |

|-----------------------------------|----------------|--------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| HC = Bit is cle                   | ared by hardwa | are                                                    | HS = Bit is set by hardware                                       |  |  |  |  |

| R = Readable bit W = Writable bit |                |                                                        | U = Unimplemented bit, read as '0'                                |  |  |  |  |

| u = Bit is unch                   | anged          | x = Bit is unknown                                     | -m/n = Value at POR and BOR/Value at all other Resets             |  |  |  |  |

| '1' = Bit is set                  |                | '0' = Bit is cleared                                   | q = Value depends on condition                                    |  |  |  |  |

|                                   |                |                                                        |                                                                   |  |  |  |  |

| bit 7                             |                | ack Overflow Flag bit                                  |                                                                   |  |  |  |  |

|                                   |                | Overflow occurred<br>Overflow has not occurrec         | l or cleared by firmware                                          |  |  |  |  |

| bit 6                             | STKUNF: Sta    | ack Underflow Flag bit                                 |                                                                   |  |  |  |  |

|                                   |                | Underflow occurred<br>Underflow has not occurre        | ed or cleared by firmware                                         |  |  |  |  |

| bit 5                             | Unimplemer     | nted: Read as '0'                                      |                                                                   |  |  |  |  |

| bit 4                             | RWDT: Watc     | hdog Timer Reset Flag bit                              |                                                                   |  |  |  |  |

|                                   |                |                                                        | ccurred or set to '1' by firmware<br>rred (cleared by hardware)   |  |  |  |  |

| bit 3                             | RMCLR: MC      | LR Reset Flag bit                                      |                                                                   |  |  |  |  |

|                                   |                | Reset has not occurred or<br>Reset has occurred (clear |                                                                   |  |  |  |  |

| bit 2                             | RI: RESET IN   | struction Flag bit                                     |                                                                   |  |  |  |  |

|                                   |                |                                                        | executed or set to '1' by firmware<br>cuted (cleared by hardware) |  |  |  |  |

| bit 1                             | POR: Power-    | -on Reset Status bit                                   |                                                                   |  |  |  |  |

|                                   |                | r-on Reset occurred<br>on Reset occurred (must         | be set in software after a Power-on Reset occurs)                 |  |  |  |  |

| bit 0                             | BOR: Brown     | -out Reset Status bit                                  |                                                                   |  |  |  |  |

|                                   |                | n-out Reset occurred<br>out Reset occurred (must       | be set in software after a Power-on Reset or Brown-out Rese       |  |  |  |  |

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL or EXTRC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The oscillator module can be configured in one of the following clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. EXTRC External Resistor-Capacitor

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The EXTRC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these three clock sources.

| R-1/q                                                                                                                         | R-0/q                                                                     | R-q/q                                                     | R-0/q              | R-0/q           | R-q/q                             | R-0/0              | R-0/q        |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------|--------------------|-----------------|-----------------------------------|--------------------|--------------|

| SOSCR                                                                                                                         | PLLR                                                                      | OSTS                                                      | HFIOFR             | HFIOFL          | MFIOFR                            | LFIOFR             | HFIOFS       |

| bit 7                                                                                                                         |                                                                           |                                                           |                    |                 |                                   |                    | bit 0        |

|                                                                                                                               |                                                                           |                                                           |                    |                 |                                   |                    |              |

| Legend:                                                                                                                       | L 14                                                                      |                                                           | L 14               |                 |                                   | l = = (0)          |              |

| R = Readable                                                                                                                  |                                                                           | W = Writable                                              |                    | •               | mented bit, read<br>at POR and BO |                    | athar Daaata |

| u = Bit is unch<br>'1' = Bit is set                                                                                           | •                                                                         | x = Bit is unk<br>'0' = Bit is cle                        |                    | q = Condition   |                                   | rk/ value at all i | Uner Resels  |

|                                                                                                                               |                                                                           |                                                           | aleu               |                 | Idi                               |                    |              |

| bit 7                                                                                                                         | If T1OSCEN           1 = Second           0 = Second           If T1OSCEN | lary oscillator is<br>lary oscillator is                  | ready<br>not ready | ady             |                                   |                    |              |

| bit 6                                                                                                                         | <b>PLLR</b> 4x PL<br>1 = 4x PLL<br>0 = 4x PLL                             | L Ready bit<br>is ready                                   |                    |                 |                                   |                    |              |

| bit 5                                                                                                                         | 1 = Runnin                                                                | llator Start-up T<br>g from the clocl<br>g from an interr | c defined by the   | e FOSC<2:0>     | bits of the Confi<br>00)          | guration Word      | s            |

| bit 4                                                                                                                         | 1 = HFINTC                                                                | gh-Frequency Ii<br>SC is ready<br>SC is not read          |                    | or Ready bit    |                                   |                    |              |

| bit 3                                                                                                                         | 1 = HFINTC                                                                | gh-Frequency Ir<br>DSC is at least 2<br>DSC is not 2% a   | 2% accurate        | or Locked bit   |                                   |                    |              |

| bit 2                                                                                                                         | 1 = MFINTC                                                                | edium-Frequen<br>DSC is ready<br>DSC is not read          | -                  | illator Ready b | it                                |                    |              |

| bit 1                                                                                                                         | 1 = LFINTO                                                                | w-Frequency In<br>SC is ready<br>SC is not ready          |                    | or Ready bit    |                                   |                    |              |

| bit 0 HFIOFS: High-Frequency Internal Oscillat<br>1 = HFINTOSC is at least 0.5% accurate<br>0 = HFINTOSC is not 0.5% accurate |                                                                           |                                                           |                    | or Stable bit   |                                   |                    |              |

#### REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

#### 8.2 Low-Power Sleep Mode

The PIC16F1704/8 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1704/8 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

# 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use only with the following peripherals:

- Brown-Out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-on-change pins

- Timer1 (with external clock source<100 kHz)

Note: The PIC16LF1704/8 does not have a configurable Low-Power Sleep mode. PIC16LF1704/8 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F1704/8. See Section 32.0 "Electrical Specifications" for more information.

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

- ; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$   $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>MOVWF | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary<br>; Load upper 6 bits of erase address boundary                                                                                                                                                                                             |

|----------------------|--------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | BCF<br>BSF<br>BSF                                | PMADKH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN            | ; Not configuration space<br>; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                             |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP     | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                       | PMCON1,WREN<br>INTCON,GIE                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                  |

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

### 11.3 PORTB Registers (PIC16(L)F1708 only)

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 32-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions may continue to control the pin when it is in Analog mode.

#### 18.5.4 RISING EVENT DEAD-BAND

Rising event dead band delays the turn-on of the primary outputs from when complementary outputs are turned off. The rising event dead-band time starts when the rising\_ event output goes true.

See Section 18.5.1, Asynchronous delay chain dead-band delay and Section 18.5.2, Synchronous counter dead-band delay for more information on setting the rising edge dead-band time.

#### 18.5.5 FALLING EVENT DEAD-BAND

Falling event dead band delays the turn-on of complementary outputs from when the primary outputs are turned off. The falling event dead-band time starts when the falling\_ event output goes true.

See Section 18.5.1, Asynchronous delay chain dead-band delay and Section 18.5.2, Synchronous counter dead-band delay for more information on setting the rising edge dead-band time.

#### 18.5.6 DEAD-BAND OVERLAP

There are two cases of dead-band overlap:

- Rising-to-falling

- Falling-to-rising

#### 18.5.6.1 Rising-to-Falling Overlap

In this case, the falling event occurs while the rising event dead-band counter is still counting. When this happens, the primary drives are suppressed and the dead-band extends by the falling event dead-band time. At the termination of the extended dead-band time, the complementary drive goes true.

#### 18.5.6.2 Falling-to-Rising Overlap

In this case, the rising event occurs while the falling event dead-band counter is still counting. When this happens, the complementary drive is suppressed and the dead-band extends by the rising event dead-band time. At the termination of the extended dead-band time, the primary drive goes true.

#### 18.6 Blanking Control

Input blanking is a function, whereby, the event inputs can be masked or blanked for a short period of time. This is to prevent electrical transients caused by the turn-on/off of power components from generating a false input event.

The COG contains two blanking counters: one triggered by the rising event and the other triggered by the falling event. The counters are cross coupled with the events they are blanking. The falling event blanking counter is used to blank rising input events and the rising event blanking counter is used to blank

falling input events. Once started, blanking extends for the time specified by the corresponding blanking counter.

Blanking is timed by counting COG\_clock periods from zero up to the value in the blanking count register. Use Equation 18-1 to calculate blanking times.

#### 18.6.1 FALLING EVENT BLANKING OF RISING EVENT INPUTS

The falling event blanking counter inhibits rising event inputs from triggering a rising event. The falling event blanking time starts when the rising event output drive goes false.

The falling event blanking time is set by the value contained in the COGxBLKF register (Register 18-13). Blanking times are calculated using the formula shown in Equation 18-1.

When the COGxBLKF value is zero, falling event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.2 RISING EVENT BLANKING OF FALLING EVENT INPUTS

The rising event blanking counter inhibits falling event inputs from triggering a falling event. The rising event blanking time starts when the falling event output drive goes false.

The rising event blanking time is set by the value contained in the COGxBLKR register (Register 18-12).

When the COGxBLKR value is zero, rising event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.3 BLANKING TIME UNCERTAINTY

When the rising and falling sources that trigger the blanking counters are asynchronous to the COG\_clock, it creates uncertainty in the blanking time. The maximum uncertainty is equal to one COG\_clock period. Refer to Equation 18-1 and Example 18-1 for more detail.

#### 18.7 Phase Delay

It is possible to delay the assertion of either or both the rising event and falling events. This is accomplished by placing a non-zero value in COGxPHR or COGxPHF phase-delay count register, respectively (Register 18-14 and Register 18-15). Refer to Figure 18-10 for COG operation with CCP1 and phase delay. The delay from the input rising event signal switching to the actual assertion of the events is calculated the same as the dead-band and blanking delays. Refer to Equation 18-1.

| U-0              | U-0                                               | U-0              | U-0               | R/W-0/0         | R/W-0/0         | R/W-0/0           | R/W-0/0    |  |

|------------------|---------------------------------------------------|------------------|-------------------|-----------------|-----------------|-------------------|------------|--|

| _                | -                                                 | —                | —                 | GxAS3E          | GxAS2E          | GxAS1E            | GxAS0E     |  |

| bit 7            |                                                   |                  |                   |                 |                 |                   | bit 0      |  |

|                  |                                                   |                  |                   |                 |                 |                   |            |  |

| Legend:          |                                                   |                  |                   |                 |                 |                   |            |  |

| R = Readable     | e bit                                             | W = Writable     | bit               | U = Unimplem    | ented bit, read | as '0'            |            |  |

| u = Bit is unc   | hanged                                            | x = Bit is unki  | nown              | -n/n = Value at | POR and BOF     | R/Value at all of | her Resets |  |

| '1' = Bit is set | t                                                 | '0' = Bit is cle | ared              | q = Value depe  |                 |                   |            |  |

|                  |                                                   |                  |                   |                 |                 |                   |            |  |

| bit 7-4          | Unimplemer                                        | nted: Read as    | ʻ0'               |                 |                 |                   |            |  |

| bit 3            | GxAS3E: CO                                        | OGx Auto-shuto   | down Source Er    | nable bit 3     |                 |                   |            |  |

|                  |                                                   |                  | en CLC2 output    |                 |                 |                   |            |  |

|                  | 0 = CLC2 output has no effect on shutdown         |                  |                   |                 |                 |                   |            |  |

| bit 2            | GxAS2E: COGx Auto-shutdown Source Enable bit 2    |                  |                   |                 |                 |                   |            |  |

|                  |                                                   |                  | en Comparator     | -               |                 |                   |            |  |

|                  | 0 = Comparator 2 output has no effect on shutdown |                  |                   |                 |                 |                   |            |  |

| bit 1            | GxAS1E: CO                                        | OGx Auto-shuto   | down Source Er    | nable bit 1     |                 |                   |            |  |

|                  |                                                   |                  | en Comparator     | •               |                 |                   |            |  |

|                  | •                                                 | •                | as no effect on a |                 |                 |                   |            |  |

| hit 0            | GYASOF: COGY Auto-shutdown Source Enable bit 0    |                  |                   |                 |                 |                   |            |  |

#### REGISTER 18-8: COGxASD1: COG AUTO-SHUTDOWN CONTROL REGISTER 1

| bit 0 | GxAS0E: COGx Auto-shutdown Source Enable bit 0 |

|-------|------------------------------------------------|

| bit 0 | GxAS0E: COGx Auto-shutdown Source Enable bit 0 |

- 1 = COGx is shutdown when Pin selected with COGxPPS control is low

- 0 = Pin selected with COGxPPS control has no effect on shutdown

#### 20.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

|         |                                          |

2: The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

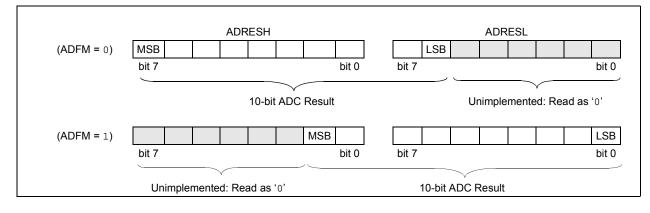

#### 20.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 20-3 shows the two output formats.

#### FIGURE 20-3: 10-BIT ADC CONVERSION RESULT FORMAT

# PIC16(L)F1704/8

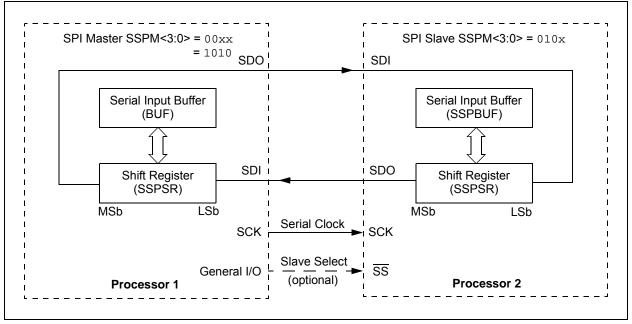

#### FIGURE 28-5: SPI MASTER/SLAVE CONNECTION

# PIC16(L)F1704/8

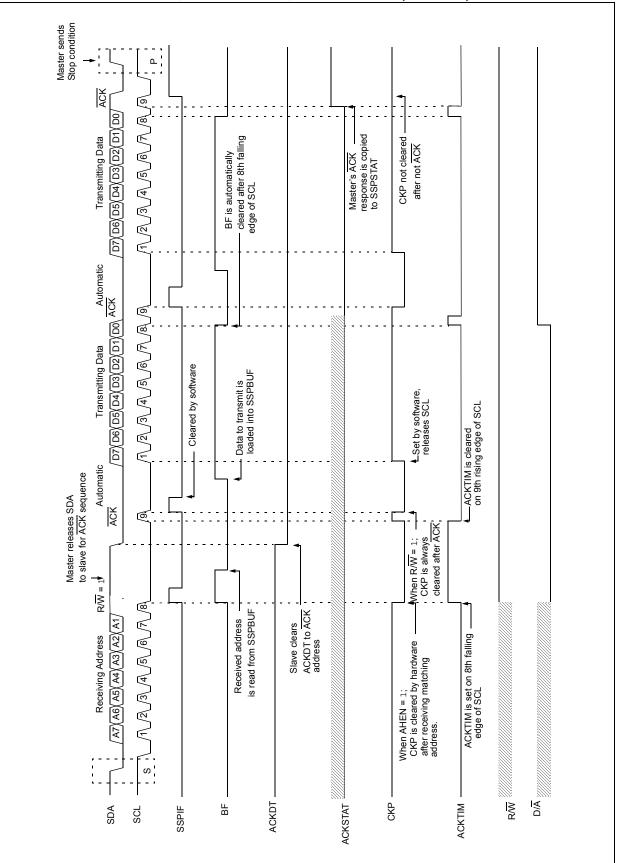

FIGURE 28-19: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, TRANSMISSION (AHEN = 1)

#### 28.8 Register Definitions: MSSP Control

#### REGISTER 28-1: SSP1STAT: SSP STATUS REGISTER R/W-0/0 R-0/0 R/W-0/0 R-0/0 R-0/0 R-0/0 R-0/0 R-0/0 D/A Ρ R/W SMP CKE S UA BF bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged -n/n = Value at POR and BOR/Value at all other Resets x = Bit is unknown '0' = Bit is cleared '1' = Bit is set bit 7 SMP: SPI Data Input Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in Slave mode In I<sup>2</sup>C Master or Slave mode: 1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for High-Speed mode (400 kHz) bit 6 CKE: SPI Clock Edge Select bit (SPI mode only) In SPI Master or Slave mode: 1 = Transmit occurs on transition from active to Idle clock state 0 = Transmit occurs on transition from Idle to active clock state In I<sup>2</sup>C<sup>™</sup> mode only: 1 = Enable input logic so that thresholds are compliant with SMBus specification 0 = Disable SMBus specific inputs bit 5 **D/A:** Data/Address bit (I<sup>2</sup>C mode only) 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address bit 4 P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset) 0 = Stop bit was not detected last S: Start bit bit 3 (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset) 0 = Start bit was not detected last bit 2 **R/W:** Read/Write bit information ( $I^2C$ mode only) This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit, or not ACK bit. In I<sup>2</sup>C Slave mode: 1 = Read 0 = Write In I<sup>2</sup>C Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress OR-ing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Idle mode. **UA:** Update Address bit (10-bit I<sup>2</sup>C mode only) bit 1 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated

#### 29.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 29-3 contains the formulas for determining the baud rate. Example 29-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 29-5. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

#### EXAMPLE 29-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPBRGH:SPBRGL:

C

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $= \frac{\frac{16000000}{9600}}{64} - 1$                                |

| $= [25.042] = 25$ Calculated Baud Rate $= \frac{16000000}{64(25+1)}$    |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

# PIC16(L)F1704/8

| Mnen     | nonic, | Description                   | Cycles       | 14-Bit Opcode |      |      |      | Status   | Notes |

|----------|--------|-------------------------------|--------------|---------------|------|------|------|----------|-------|

| Operands |        | Description                   | Cycles       | MSb           |      |      | LSb  | Affected | Notes |

|          |        | BYTE-ORIENTED FILE F          | REGISTER OPE | RATIC         | NS   |      |      |          |       |

| ADDWF    | f, d   | Add W and f                   | 1            | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC   | f, d   | Add with Carry W and f        | 1            | 11            | 1101 |      | ffff | C, DC, Z | 2     |

| ANDWF    | f, d   | AND W with f                  | 1            | 00            |      | dfff |      | Z        | 2     |

| ASRF     | f, d   | Arithmetic Right Shift        | 1            | 11            |      | dfff |      | C, Z     | 2     |

| LSLF     | f, d   | Logical Left Shift            | 1            | 11            |      | dfff |      | C, Z     | 2     |

| LSRF     | f, d   | Logical Right Shift           | 1            | 11            | 0110 | dfff |      | C, Z     | 2     |

| CLRF     | f      | Clear f                       | 1            | 00            |      | lfff |      | Z        | 2     |

| CLRW     | -      | Clear W                       | 1            | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF     | f, d   | Complement f                  | 1            | 00            |      | dfff |      | Z        | 2     |

| DECF     | f, d   | Decrement f                   | 1            | 00            |      | dfff |      | Z        | 2     |

| INCF     | f, d   | Increment f                   | 1            | 00            | 1010 |      | ffff | Z        | 2     |

| IORWF    | f, d   | Inclusive OR W with f         | 1            | 00            | 0100 | dfff |      | Z        | 2     |

| MOVF     | f, d   | Move f                        | 1            | 00            | 1000 |      | ffff | Z        | 2     |

| MOVWF    | f      | Move W to f                   | 1            | 00            | 0000 | 1fff | ffff |          | 2     |

| RLF      | f, d   | Rotate Left f through Carry   | 1            | 00            |      | dfff |      | С        | 2     |

| RRF      | f, d   | Rotate Right f through Carry  | 1            | 00            | 1100 |      | ffff | С        | 2     |

| SUBWF    | f, d   | Subtract W from f             | 1            | 00            | 0010 | dfff |      | C, DC, Z | 2     |

| SUBWFB   | f, d   | Subtract with Borrow W from f | 1            | 11            | 1011 | dfff |      | C, DC, Z | 2     |

| SWAPF    | f, d   | Swap nibbles in f             | 1            | 00            | 1110 | dfff | ffff |          | 2     |

| XORWF    | f, d   | Exclusive OR W with f         | 1            | 00            | 0110 | dfff | ffff | Z        | 2     |

|          |        | BYTE ORIENTED S               |              | ONS           |      |      |      |          |       |

| DECFSZ   | f, d   | Decrement f, Skip if 0        | 1(2)         | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ   | f, d   | Increment f, Skip if 0        | 1(2)         | 00            | 1111 | dfff | ffff |          | 1, 2  |

|          |        | BIT-ORIENTED FILE RE          |              | RATIO         | IS   |      |      | L        | •     |

| BCF      | f, b   | Bit Clear f                   | 1            | 01            | 00bb | bfff | ffff |          | 2     |

| BSF      | f, b   | Bit Set f                     | 1            | 01            | 01bb | bfff | ffff |          | 2     |

|          | •      | BIT-ORIENTED SI               | KIP OPERATIO | NS            |      |      |      | L        | •     |

| BTFSC    | f, b   | Bit Test f, Skip if Clear     | 1 (2)        | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS    | f, b   | Bit Test f, Skip if Set       | 1 (2)        | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL  |        |                               |              | T             |      |      |      | n        | 1     |

| ADDLW    | k      | Add literal and W             | 1            | 11            | 1110 | kkkk |      | C, DC, Z |       |

| ANDLW    | k      | AND literal with W            | 1            | 11            |      | kkkk |      | Z        |       |

| IORLW    | k      | Inclusive OR literal with W   | 1            | 11            |      | kkkk |      | Z        |       |

| MOVLB    | k      | Move literal to BSR           | 1            | 00            | 0000 | 001k |      |          |       |

| MOVLP    | k      | Move literal to PCLATH        | 1            | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW    | k      | Move literal to W             | 1            | 11            | 0000 | kkkk | kkkk |          |       |

| SUBLW    | k      | Subtract W from literal       | 1            | 11            | 1100 | kkkk |      | C, DC, Z |       |

| XORLW    | k      | Exclusive OR literal with W   | 1            | 11            | 1010 | kkkk | kkkk | Z        |       |

#### TABLE 31-3: PIC16(L)F1704/8 INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

#### TABLE 32-15: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2)</sup>:

|               | ing toin | perature: Tested at 25°C                          |      |       |      |       |                                                                           |

|---------------|----------|---------------------------------------------------|------|-------|------|-------|---------------------------------------------------------------------------|

| Param.<br>No. | Sym.     | Characteristic                                    | Min. | Тур.† | Max. | Units | Conditions                                                                |

| AD01          | NR       | Resolution                                        | _    | —     | 10   | bit   |                                                                           |

| AD02          | EIL      | Integral Error                                    | —    | —     | ±1.7 | LSb   | VREF = 3.0V                                                               |

| AD03          | Edl      | Differential Error                                | _    | —     | ±1   | LSb   | No missing codes, VREF = 3.0V                                             |

| AD04          | EOFF     | Offset Error                                      | _    | —     | ±2.5 | LSb   | VREF = 3.0V                                                               |

| AD05          | Egn      | Gain Error                                        | _    | —     | ±2.0 | LSb   | VREF = 3.0V                                                               |

| AD06          | VREF     | Reference Voltage <sup>(3)</sup>                  | 1.8  | —     | Vdd  | V     | VREF = (VREF+ minus VREF-)                                                |

| AD07          | VAIN     | Full-Scale Range                                  | Vss  | —     | VREF | V     |                                                                           |

| AD08          | Zain     | Recommended Impedance of<br>Analog Voltage Source | -    | —     | 10   | kΩ    | Can go higher if external 0.01 $\mu$ F capacitor is present on input pin. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: VREF = (VREF+ VREF-); ADCREF+ may be VDD, VREF+ pin or FVR1\_buffer. The ADCREF- may be VSS or VREF- pin. If selecting the FVR1\_buffer, the buffers output voltage must be 2.048V or 4.096V.

#### TABLE 32-16: ADC CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |      |                                                                    |      |                 |      |       |                                           |  |

|---------------------------------------------------------|------|--------------------------------------------------------------------|------|-----------------|------|-------|-------------------------------------------|--|

| Param.<br>No.                                           | Sym. | Characteristic                                                     | Min. | Тур.†           | Max. | Units | Conditions                                |  |

| AD130*                                                  | TAD  | ADC Clock Period (TADC)                                            | 1.0  | —               | 9.0  | μS    | Fosc-based                                |  |

|                                                         |      | FRC Oscillator Period (TFRC)                                       | 1.0  | 2               | 6.0  | μS    | ADCS<1:0> = 11 (ADC FRC mode)             |  |

| AD131                                                   | TCNV | Conversion Time (not including<br>Acquisition Time) <sup>(1)</sup> | —    | 11              | -    | Tad   | Set GO/DONE bit to conversion<br>complete |  |

| AD132*                                                  | TACQ | Acquisition Time                                                   | _    | 5.0             | _    | μS    |                                           |  |

| AD133*                                                  | THCD | Holding Capacitor Disconnect Time                                  | _    | 0.5 Tad         |      |       | ADCS<2:0> $\neq$ x11 (Fosc based)         |  |

|                                                         |      |                                                                    | _    | 1/2 TAD + 1 TCY | _    |       | ADCS<2:0> = x11 (FRC based)               |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

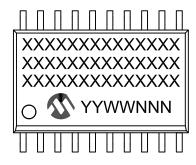

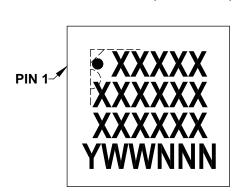

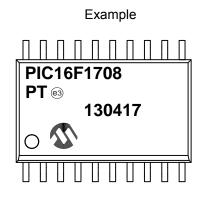

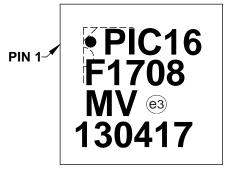

### Package Marking Information (Continued)

20-Lead SOIC (7.50 mm)

20-Lead QFN (4x4x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator (e3)<br>can be found on the outer packaging for this package. |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it w<br>be carried over to the next line, thus limiting the number of availab<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                                        |

### THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15