# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1708-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3: PIC16(L)F1708 PIN OUT DESCRIPTION

| RA0<br>AN0<br>VREF-<br>C1IN+<br>DAC1OUT<br>ICSPDAT<br>RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD<br>T0CKI | TTL/ST<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN | CMOS<br>—<br>AN<br>CMOS<br>CMOS<br>—<br>—<br>—<br>—<br>—<br>CMOS                                                                                                       | General purpose I/O.         ADC Channel 0 input.         ADC Negative Voltage Reference input.         Comparator C1 positive input.         Digital-to-Analog Converter output.         ICSP™ Data I/O.         General purpose I/O.         ADC Channel 1 input.         ADC Voltage Reference input.         Comparator C2 negative input.         Comparator C3 negative input.         Serial Programming Clock.         General purpose I/O. |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF-<br>C1IN+<br>DAC1OUT<br>ICSPDAT<br>RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                        | AN<br>AN<br>ST<br>TTL/ST<br>AN<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN           | <br>AN<br>CMOS<br>CMOS<br><br><br><br><br><br>                                                                                                                         | ADC Negative Voltage Reference input.<br>Comparator C1 positive input.<br>Digital-to-Analog Converter output.<br>ICSP™ Data I/O.<br>General purpose I/O.<br>ADC Channel 1 input.<br>ADC Voltage Reference input.<br>Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                     |

| C1IN+<br>DAC1OUT<br>ICSPDAT<br>RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                 | AN<br>—<br>ST<br>TTL/ST<br>AN<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN            | <br>AN<br>CMOS<br>CMOS<br><br><br><br><br><br>                                                                                                                         | Comparator C1 positive input.         Digital-to-Analog Converter output.         ICSP™ Data I/O.         General purpose I/O.         ADC Channel 1 input.         ADC Voltage Reference input.         Comparator C2 negative input.         Comparator C3 negative input.         Serial Programming Clock.                                                                                                                                      |

| DAC1OUT<br>ICSPDAT<br>RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                          | <br>ST<br>TTL/ST<br>AN<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN                   | AN<br>CMOS<br>CMOS<br>—<br>—<br>—<br>—                                                                                                                                 | Digital-to-Analog Converter output.         ICSP™ Data I/O.         General purpose I/O.         ADC Channel 1 input.         ADC Voltage Reference input.         Comparator C2 negative input.         Comparator C3 negative input.         Serial Programming Clock.                                                                                                                                                                            |

| ICSPDAT<br>RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                                     | TTL/ST<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN                                   | CMOS<br>CMOS<br>—<br>—<br>—<br>—<br>—                                                                                                                                  | ICSP™ Data I/O.<br>General purpose I/O.<br>ADC Channel 1 input.<br>ADC Voltage Reference input.<br>Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                      |

| RA1<br>AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                                                | TTL/ST<br>AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN                                   | CMOS<br>—<br>—<br>—<br>—                                                                                                                                               | General purpose I/O.<br>ADC Channel 1 input.<br>ADC Voltage Reference input.<br>Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                                         |

| AN1<br>VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC10UT2<br>ZCD                                                                       | AN<br>AN<br>AN<br>ST<br>TTL/ST<br>AN                                             |                                                                                                                                                                        | ADC Channel 1 input.<br>ADC Voltage Reference input.<br>Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                                                                 |

| VREF+<br>C1IN0-<br>C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC10UT2<br>ZCD                                                                              | AN<br>AN<br>ST<br>TTL/ST<br>AN                                                   |                                                                                                                                                                        | ADC Voltage Reference input.<br>Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                                                                                         |

| C1INO-<br>C2INO-<br>ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                                                                       | AN<br>AN<br>ST<br>TTL/ST<br>AN                                                   |                                                                                                                                                                        | Comparator C2 negative input.<br>Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                                                                                                                         |

| C2IN0-<br>ICSPCLK<br>RA2<br>AN2<br>AC10UT2<br>ZCD                                                                                                 | AN<br>ST<br>TTL/ST<br>AN                                                         |                                                                                                                                                                        | Comparator C3 negative input.<br>Serial Programming Clock.                                                                                                                                                                                                                                                                                                                                                                                          |

| ICSPCLK<br>RA2<br>AN2<br>AC1OUT2<br>ZCD                                                                                                           | ST<br>TTL/ST<br>AN                                                               | —<br>—<br>CMOS                                                                                                                                                         | Serial Programming Clock.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RA2<br>AN2<br>AC1OUT2<br>ZCD                                                                                                                      | TTL/ST<br>AN                                                                     | —<br>CMOS                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AN2<br>AC1OUT2<br>ZCD                                                                                                                             | AN                                                                               | CMOS                                                                                                                                                                   | General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AC1OUT2<br>ZCD                                                                                                                                    | AN                                                                               |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ZCD                                                                                                                                               |                                                                                  | —                                                                                                                                                                      | ADC Channel 2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                                                                                                                                                 |                                                                                  | AN                                                                                                                                                                     | Digital-to-Analog Converter output.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TOCKI                                                                                                                                             | _                                                                                | AN                                                                                                                                                                     | Zero-Cross Detection Current Source/Sink.                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                   | ST                                                                               | _                                                                                                                                                                      | Timer0 clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| COGIN                                                                                                                                             | ST                                                                               | CMOS                                                                                                                                                                   | Complementary Output Generator input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT                                                                                                                                               | ST                                                                               | _                                                                                                                                                                      | External interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RA3                                                                                                                                               | TTL/ST                                                                           | CMOS                                                                                                                                                                   | General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MCLR                                                                                                                                              | ST                                                                               | _                                                                                                                                                                      | Master Clear with internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Vpp                                                                                                                                               | HV                                                                               | _                                                                                                                                                                      | Programming voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA4                                                                                                                                               | TTL/ST                                                                           | CMOS                                                                                                                                                                   | General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AN3                                                                                                                                               | AN                                                                               | _                                                                                                                                                                      | ADC Channel 3 input.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| T1G                                                                                                                                               | ST                                                                               | _                                                                                                                                                                      | Timer1 gate input.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SOSCO                                                                                                                                             | XTAL                                                                             | XTAL                                                                                                                                                                   | Secondary Oscillator Connection.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OSC2                                                                                                                                              | _                                                                                | XTAL                                                                                                                                                                   | Crystal/Resonator (LP, XT, HS modes).                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLKOUT                                                                                                                                            | _                                                                                | CMOS                                                                                                                                                                   | Fosc/4 output.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RA5                                                                                                                                               | TTL/ST                                                                           | CMOS                                                                                                                                                                   | General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| T1CKI                                                                                                                                             | ST                                                                               | _                                                                                                                                                                      | Timer1 clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                   |                                                                                  | XTAL                                                                                                                                                                   | Secondary Oscillator Connection.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLCIN3                                                                                                                                            | ST                                                                               | _                                                                                                                                                                      | Configurable Logic Cell source input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| OSC1                                                                                                                                              |                                                                                  | XTAL                                                                                                                                                                   | Crystal/Resonator (LP, XT, HS modes).                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                   |                                                                                  | _                                                                                                                                                                      | External clock input (EC mode).                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                   |                                                                                  | CMOS                                                                                                                                                                   | General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                   |                                                                                  | _                                                                                                                                                                      | ADC Channel 10 input.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                   |                                                                                  |                                                                                                                                                                        | Operational Amplifier 1 inverting input.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                   |                                                                                  | CMOS                                                                                                                                                                   | SPI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ·                                                                                                                                                 |                                                                                  |                                                                                                                                                                        | I <sup>2</sup> C data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (                                                                                                                                                 | OSC2<br>CLKOUT<br>RA5<br>T1CKI<br>SOSCI                                          | OSC2 —<br>CLKOUT —<br>RA5 TTL/ST<br>T1CKI ST<br>SOSCI XTAL<br>CLCIN3 ST<br>OSC1 —<br>CLKIN ST<br>RB4 TTL/ST<br>AN10 AN<br>DPA1IN- AN<br>SCK ST<br>SDA I <sup>2</sup> C | OSC2 – XTAL<br>CLKOUT – CMOS<br>RA5 TTL/ST CMOS<br>T1CKI ST –<br>SOSCI XTAL XTAL<br>CLCIN3 ST –<br>OSC1 – XTAL<br>CLKIN ST –<br>RB4 TTL/ST CMOS<br>AN10 AN –<br>DPA1IN- AN –<br>SCK ST CMOS                                                                                                                                                                                                                                                         |

Legend: AN = Analog input or output

CMOS = CMOS compatible input or output

OD

= Open Drain

TTL = TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

Crystal levels

I

I

I

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-3.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

#### 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.7** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

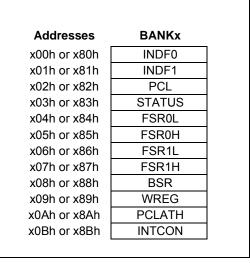

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-9.

#### TABLE 3-2: CORE REGISTERS

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 31.0 "Instruction Set Summary").

Note: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name            | Bit 7                                                                                   | Bit 6                                                         | Bit 5 | Bit 4         | Bit 3       | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|-----------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|-------|---------------|-------------|-------|-----------|-----------|----------------------|---------------------------------|

| Bank               | c 31            |                                                                                         |                                                               |       |               |             |       |           |           |                      |                                 |

| F8Ch<br>to<br>FE3h |                 | Unimplemented —                                                                         |                                                               |       |               |             |       |           |           | _                    |                                 |

| FE4h               | STATUS_<br>SHAD | —                                                                                       | —                                                             | —     | —             | —           | Z     | DC        | С         | xxx                  | uuu                             |

| FE5h               | WREG_<br>SHAD   | Working Register Shadow xxxx xx                                                         |                                                               |       |               |             |       |           | XXXX XXXX | uuuu uuuu            |                                 |

| FE6h               | BSR_SHAD        | _                                                                                       |                                                               |       |               |             |       |           |           | u uuuu               |                                 |

| FE7h               | PCLATH_<br>SHAD | -                                                                                       | Program Counter Latch High Register Shadow     -xxx xxxx uuuu |       |               |             |       |           |           | uuuu uuuu            |                                 |

| FE8h               | FSR0L_<br>SHAD  | Indirect Data Memory Address 0 Low Pointer Shadow 2000 2000 2000 2000 2000 2000 2000 20 |                                                               |       |               |             |       |           | uuuu uuuu |                      |                                 |

| FE9h               | FSR0H_<br>SHAD  | Indirect Data Memory Address 0 High Pointer Shadow xxxx xxxx uu                         |                                                               |       |               |             |       | uuuu uuuu |           |                      |                                 |

| FEAh               | FSR1L_<br>SHAD  | Indirect Data Memory Address 1 Low Pointer Shadow xxxx xxxx u                           |                                                               |       |               |             |       |           | uuuu uuuu |                      |                                 |

| FEBh               | FSR1H_<br>SHAD  | Indirect Data Memory Address 1 High Pointer Shadow uu                                   |                                                               |       |               |             |       |           | uuuu uuuu |                      |                                 |

| FECh               | _               | Unimplemented —                                                                         |                                                               |       |               |             |       |           | _         |                      |                                 |

| FEDh               | STKPTR          | _                                                                                       | _                                                             | —     | Current Stack | <pre></pre> |       |           |           | 1 1111               | 1 1111                          |

| FEEh               | TOSL            | Top of Stack                                                                            | Low byte                                                      |       |               |             |       |           |           | xxxx xxxx            | uuuu uuuu                       |

| FEFh               | TOSH            | Top of Stack High byte     -xxx xxxx -                                                  |                                                               |       |               |             |       |           | -uuu uuuu |                      |                                 |

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

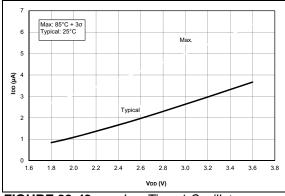

2: PIC16(L)F1704 only.

**3:** PIC16(L)F1708 only.

4: Unimplemented on PIC16LF1704/8.

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

### TABLE 10-1:FLASH MEMORY<br/>ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |  |

|---------------|----------------------|-----------------------------|--|

| PIC16(L)F1704 | 32                   | 32                          |  |

| PIC16(L)F1708 | 52                   | 52                          |  |

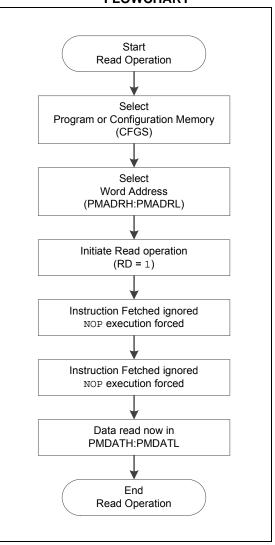

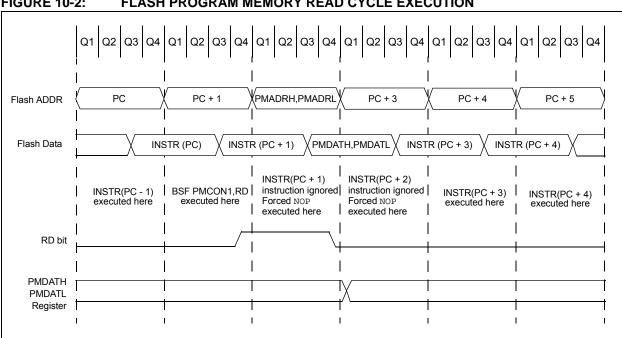

### 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | memory read are required to be NOPS.        |  |  |  |  |  |  |

|       | This prevents the user from executing a     |  |  |  |  |  |  |

|       | 2-cycle instruction on the next instruction |  |  |  |  |  |  |

|       | after the RD bit is set.                    |  |  |  |  |  |  |

#### FIGURE 10-1:

#### FLASH PROGRAM MEMORY READ FLOWCHART

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL                  | PMADRL                   | ; Select Bank for PMCON registers                                                                              |

|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|

| MOVLW                    | PROG_ADDR_LO             | ;                                                                                                              |

| MOVWF                    | PMADRL                   | ; Store LSB of address                                                                                         |

| MOVLW                    | PROG_ADDR_HI             | ;                                                                                                              |

| MOVWF                    | PMADRH                   | ; Store MSB of address                                                                                         |

| BCF<br>BSF<br>NOP<br>NOP | PMCON1,CFGS<br>PMCON1,RD | <pre>; Do not select Configuration Space ; Initiate read ; Ignored (Figure 10-1) ; Ignored (Figure 10-1)</pre> |

| MOVF                     | PMDATL,W                 | ; Get LSB of word                                                                                              |

| MOVWF                    | PROG_DATA_LO             | ; Store in user location                                                                                       |

| MOVF                     | PMDATH,W                 | ; Get MSB of word                                                                                              |

| MOVWF                    | PROG_DATA_HI             | ; Store in user location                                                                                       |

#### **FIGURE 10-2:** FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (l<sup>2</sup>C)

| Note: | The I <sup>2</sup> C default input pins are I <sup>2</sup> C and |

|-------|------------------------------------------------------------------|

|       | SMBus compatible and are the only pins                           |

|       | on the device with this compatibility.                           |

#### 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

### EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

| ; suspend interrupts                     |

|------------------------------------------|

| bcf INTCON,GIE                           |

| ; BANKSEL PPSLOCK ; set bank             |

| ; required sequence, next 5 instructions |

| movlw 0x55                               |

| movwf PPSLOCK                            |

| movlw 0xAA                               |

| movwf PPSLOCK                            |

| ; Set PPSLOCKED bit to disable writes or |

| ; Clear PPSLOCKED bit to enable writes   |

| bsf PPSLOCK, PPSLOCKED                   |

| ; restore interrupts                     |

| bsf INTCON,GIE                           |

|                                          |

#### 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

#### 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

#### 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in pin allocation Table 1 and Table 2.

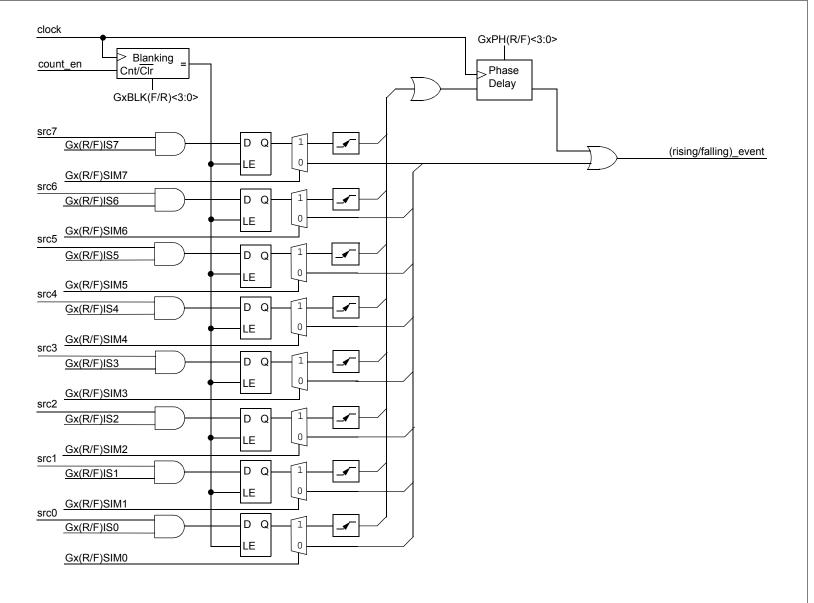

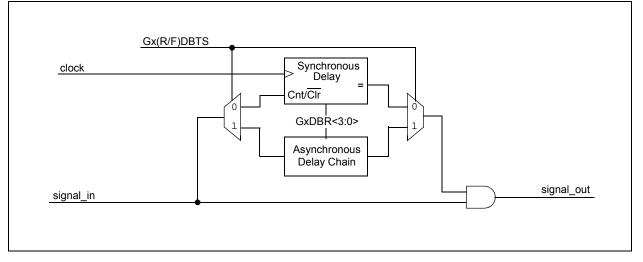

#### FIGURE 18-7: COG (RISING/FALLING) INPUT BLOCK

PIC16(L)F1704/8

#### FIGURE 18-8: COG (RISING/FALLING) DEAD-BAND BLOCK

| R/W-x/u          | R/W-x/u                                                              | R/W-x/u                                  | R/W-x/u         | R/W-x/u           | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |

|------------------|----------------------------------------------------------------------|------------------------------------------|-----------------|-------------------|------------------|------------------|--------------|--|--|--|

| LCxG4D4T         | LCxG4D4N                                                             | LCxG4D3T                                 | LCxG4D3N        | LCxG4D2T          | LCxG4D2N         | LCxG4D1T         | LCxG4D1N     |  |  |  |

| bit 7            |                                                                      |                                          |                 |                   |                  |                  | bit 0        |  |  |  |

|                  |                                                                      |                                          |                 |                   |                  |                  |              |  |  |  |

| Legend:          |                                                                      |                                          |                 |                   |                  |                  |              |  |  |  |

| R = Readable I   |                                                                      | W = Writable                             |                 | •                 | mented bit, read |                  |              |  |  |  |

| u = Bit is uncha | anged                                                                | x = Bit is unkr                          |                 | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                                                                      | '0' = Bit is cle                         | ared            |                   |                  |                  |              |  |  |  |

| bit 7            | LCxG4D4T:                                                            | Gate 4 Data 4 1                          | Frue (non-inver | rted) bit         |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcxo                          | ,               | ···· <b>,</b> · · |                  |                  |              |  |  |  |

|                  | 0 = Icxd4T is                                                        | not gated into                           | lcxg4           |                   |                  |                  |              |  |  |  |

| bit 6            | LCxG4D4N:                                                            | Gate 4 Data 4                            | Negated (inver  | rted) bit         |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcx                           |                 |                   |                  |                  |              |  |  |  |

|                  |                                                                      | not gated into                           | 0               |                   |                  |                  |              |  |  |  |

| bit 5            |                                                                      | Gate 4 Data 3 1                          | -               | rted) bit         |                  |                  |              |  |  |  |

|                  | 1 = lcxd3T is gated into lcxg4<br>0 = lcxd3T is not gated into lcxg4 |                                          |                 |                   |                  |                  |              |  |  |  |

| bit 4            |                                                                      | -                                        | -               | tod) bit          |                  |                  |              |  |  |  |

| DIL 4            |                                                                      | Gate 4 Data 3                            | 0 (             | ted) bit          |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcxg4<br>not gated into lcxg4 |                 |                   |                  |                  |              |  |  |  |

| bit 3            |                                                                      | Gate 4 Data 2 1                          | •               | rted) bit         |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcxo                          | ,               | ,                 |                  |                  |              |  |  |  |

|                  |                                                                      | not gated into                           | •               |                   |                  |                  |              |  |  |  |

| bit 2            | LCxG4D2N:                                                            | Gate 4 Data 2                            | Negated (inver  | ted) bit          |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcx                           |                 |                   |                  |                  |              |  |  |  |

|                  | 0 = Icxd2N is                                                        | not gated into                           | lcxg4           |                   |                  |                  |              |  |  |  |

| bit 1            |                                                                      | Sate 4 Data 1 1                          | · ·             | rted) bit         |                  |                  |              |  |  |  |

|                  |                                                                      | gated into lcxg                          |                 |                   |                  |                  |              |  |  |  |

|                  |                                                                      | not gated into                           | •               |                   |                  |                  |              |  |  |  |

| bit 0            |                                                                      | Gate 4 Data 1                            | •               | ted) bit          |                  |                  |              |  |  |  |

|                  | 1 = Icxd1N is<br>0 = Icxd1N is                                       | gated into lcx                           |                 |                   |                  |                  |              |  |  |  |

#### REGISTER 19-10: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

| Note: | The Timer postscaler (see Section 26.1 |

|-------|----------------------------------------|

|       | "Timer2 Operation") is not used in the |

|       | determination of the PWM frequency.    |

#### 27.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 27-2 is used to calculate the PWM pulse width.

Equation 27-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 27-2: PULSE WIDTH

$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

### EQUATION 27-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 27-4).

#### 27.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 27-4.

#### EQUATION 27-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + I)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### 28.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 28-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 28-6, Figure 28-8, Figure 28-9 and Figure 28-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 28-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

Note: In Master mode the clock signal output to the SCK pin is also the clock signal input to the peripheral. The pin selected for output with the RxyPPS register must also be selected as the peripheral input with the SSPCLKPPS register.

### 28.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

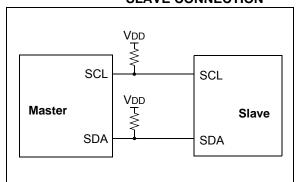

Figure 28-11 shows the block diagram of the MSSP module when operating in  $I^2C$  mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 28-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 28-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an ACK bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 29.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 6.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 29.4.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### 29.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 29.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 29.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|----------------------|--------------|--------|--------|--------|---------------------|

| ANSELA                | _                     | —                     |          | ANSA4                |              | ANSA2  | ANSA1  | ANSA0  | 122                 |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5    | ANSB4                | _            | _      | _      | _      | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2) | ANSC4 <sup>(2)</sup> | ANSC3        | ANSC2  | ANSC1  | ANSC0  | 133                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | _        | SCKP                 | BRG16        | _      | WUE    | ABDEN  | 336                 |

| CKPPS                 | _                     | —                     | _        |                      | CKPPS<4:0>   |        |        |        |                     |

| INTCON                | GIE                   | PEIE                  | TMR0IE   | INTE                 | IOCIE        | TMR0IF | INTF   | IOCIF  | 85                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE     | TXIE                 | SSP1IE       | CCP1IE | TMR2IE | TMR1IE | 86                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF     | TXIF                 | SSP1IF       | CCP1IF | TMR2IF | TMR1IF | 89                  |

| RC1REG                |                       |                       | EUS      | ART Receiv           | e Data Regis | ter    |        |        | 329*                |

| RC1STA                | SPEN                  | RX9                   | SREN     | CREN                 | ADDEN        | FERR   | OERR   | RX9D   | 335                 |

| RXPPS                 | _                     | —                     | _        |                      | RXPPS<4:0>   |        |        |        |                     |

| TRISA                 | _                     | _                     | TRISA5   | TRISA4               | _(3)         | TRISA2 | TRISA1 | TRISA0 | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4               | _            | _      | _      | _      | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4               | TRISC3       | TRISC2 | TRISC1 | TRISA0 | 132                 |

| TX1STA                | CSRC                  | TX9                   | TXEN     | SYNC                 | SENDB        | BRGH   | TRMT   | TX9D   | 334                 |

### TABLE 29-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

### FIGURE 31-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |

|---------------------------------------------------------------------------------------|

| OPCODE d f (FILE #)                                                                   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |

| Bit-oriented file register operations                                                 |

| 13 10 9 7 6 0<br>OPCODE b (BIT #) f (FILE #)                                          |

| b = 3-bit bit address<br>f = 7-bit file register address                              |

| Literal and control operations                                                        |

| General                                                                               |

| 13 8 7 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 8-bit immediate value                                                             |

| CALL and GOTO instructions only                                                       |

| 13 11 10 0                                                                            |

| OPCODE k (literal)                                                                    |

| k = 11-bit immediate value                                                            |

|                                                                                       |

| 13 7 6 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 7-bit immediate value                                                             |

|                                                                                       |

| MOVLB instruction only<br>13 5 4 0                                                    |

| OPCODE k (literal)                                                                    |

| k = 5-bit immediate value                                                             |

|                                                                                       |

| BRA instruction only<br>13 9 8 0                                                      |

| OPCODE k (literal)                                                                    |

| k = 9-bit immediate value                                                             |

|                                                                                       |