Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1708-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1704/8

| PC<14:0>            |                     |       |  |  |  |  |  |  |

|---------------------|---------------------|-------|--|--|--|--|--|--|

| CALL, CALLW 15      |                     |       |  |  |  |  |  |  |

|                     | L, CALLW 15         |       |  |  |  |  |  |  |

| Interrup            | t, RETFIE           |       |  |  |  |  |  |  |

|                     | Stack Level 0       |       |  |  |  |  |  |  |

|                     | Stack Level 1       |       |  |  |  |  |  |  |

|                     | •                   |       |  |  |  |  |  |  |

|                     | •<br>Stack Level 15 | - 1   |  |  |  |  |  |  |

|                     | Slack Level 15      |       |  |  |  |  |  |  |

|                     | Depart Ventor       |       |  |  |  |  |  |  |

|                     | Reset Vector        | 0000h |  |  |  |  |  |  |

|                     | :                   |       |  |  |  |  |  |  |

|                     | Interrupt Vector    | 0004h |  |  |  |  |  |  |

| ſ                   | -                   | 0005h |  |  |  |  |  |  |

| <b>A</b> 1.         | Page 0              |       |  |  |  |  |  |  |

| On-chip             | C                   | 07FFh |  |  |  |  |  |  |

| Program <<br>Memory |                     | 0800h |  |  |  |  |  |  |

| wentery             | Page 1              |       |  |  |  |  |  |  |

| l                   | 6                   | 0FFFh |  |  |  |  |  |  |

|                     | Bollover to Bago 0  | 1000h |  |  |  |  |  |  |

|                     | Rollover to Page 0  |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     | •                   |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     | •                   |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     | Rollover to Page 1  |       |  |  |  |  |  |  |

|                     |                     | 7FFFh |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

|                     |                     |       |  |  |  |  |  |  |

# 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

| constants       |                     |

|-----------------|---------------------|

| BRW             | ;Add Index in W to  |

| BRW             |                     |

|                 | ;program counter to |

|                 | ;select data        |

| RETLW DATA0     | ;Index0 data        |

| RETLW DATA1     | ;Index1 data        |

| RETLW DATA2     |                     |

| RETLW DATA3     |                     |

|                 |                     |

|                 |                     |

| my_function     |                     |

| ; LOTS OF CODE. |                     |

| MOVLW DATA      | _INDEX              |

| call constants  |                     |

| ; THE CONSTANT  | IS IN W             |

|                 |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

# 11.3 PORTB Registers (PIC16(L)F1708 only)

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 32-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |

#### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions may continue to control the pin when it is in Analog mode.

| U-0              | R/W-0/0                                                                                                                                                                              | R/W-0/0                            | R/W-0/0        | R/W-0/0        | R/W-0/0            | R/W-0/0          | R/W-0/0      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|--------------------|------------------|--------------|

|                  | GxRIS6                                                                                                                                                                               | GxRIS5                             | GxRIS4         | GxRIS3         | GxRIS2             | GxRIS1           | GxRIS0       |

| bit 7            |                                                                                                                                                                                      |                                    |                |                |                    |                  | bit 0        |

|                  |                                                                                                                                                                                      |                                    |                |                |                    |                  |              |

| Legend:          |                                                                                                                                                                                      |                                    |                |                |                    |                  |              |

| R = Readable     | bit                                                                                                                                                                                  | W = Writable                       | bit            | U = Unimpler   | mented bit, read   | as '0'           |              |

| u = Bit is unch  | nanged                                                                                                                                                                               | x = Bit is unk                     | nown           | -n/n = Value   | at POR and BO      | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                                                                                                                                      | '0' = Bit is cle                   | ared           | q = Value de   | pends on condit    | ion              |              |

|                  |                                                                                                                                                                                      |                                    |                |                |                    |                  |              |

| bit 7            | Unimplemen                                                                                                                                                                           | ted: Read as '                     | 0'             |                |                    |                  |              |

| bit 6            |                                                                                                                                                                                      | Gx Rising Ever                     | •              |                |                    |                  |              |

|                  |                                                                                                                                                                                      | utput is enable<br>as no effect on | 0              |                |                    |                  |              |

| bit 5            |                                                                                                                                                                                      |                                    | •              |                |                    |                  |              |

| DIL 5            |                                                                                                                                                                                      | Gx Rising Ever                     | •              |                |                    |                  |              |

|                  |                                                                                                                                                                                      | tput has no eff                    |                |                |                    |                  |              |

| bit 4            | GxRIS4: CO                                                                                                                                                                           | Gx Rising Ever                     | t Input Source | e 4 Enable bit |                    |                  |              |

|                  |                                                                                                                                                                                      | enabled as a r                     |                |                |                    |                  |              |

|                  |                                                                                                                                                                                      | as no effect on                    | •              |                |                    |                  |              |

| bit 3            | GxRIS3: COGx Rising Event Input Source 3 Enable bit                                                                                                                                  |                                    |                |                |                    |                  |              |

|                  | <ul> <li>1 = CLC1 output is enabled as a rising event input</li> <li>0 = CLC1 output has no effect on the rising event</li> </ul>                                                    |                                    |                |                |                    |                  |              |

| bit 2            |                                                                                                                                                                                      |                                    |                |                |                    |                  |              |

| DIL Z            | <b>GxRIS2:</b> COGx Rising Event Input Source 2 Enable bit<br>1 = Comparator 2 output is enabled as a rising event input                                                             |                                    |                |                |                    |                  |              |

|                  | <ul> <li>0 = Comparator 2 output has no effect on the rising event</li> </ul>                                                                                                        |                                    |                |                |                    |                  |              |

| bit 1            | <b>GxRIS1:</b> COGx Rising Event Input Source 1 Enable bit                                                                                                                           |                                    |                |                |                    |                  |              |

|                  | 1 = Comparator 1 output is enabled as a rising event input                                                                                                                           |                                    |                |                |                    |                  |              |

|                  |                                                                                                                                                                                      | ator 1 output ha                   |                | •              | nt                 |                  |              |

| bit 0            |                                                                                                                                                                                      | Gx Rising Ever                     | •              |                |                    |                  |              |

|                  | <ul> <li>1 = Pin selected with COGxPPS control register is enabled as rising event input</li> <li>0 = Pin selected with COGxPPS control has no effect on the rising event</li> </ul> |                                    |                |                |                    |                  |              |

|                  |                                                                                                                                                                                      |                                    |                |                | in the fising ever | IL               |              |

|                  |                                                                                                                                                                                      |                                    |                |                |                    |                  |              |

## REGISTER 18-3: COGxRIS: COG RISING EVENT INPUT SELECTION REGISTER

| U-0              | U-0                                                  | U-0              | U-0  | R/W-0/0         | R/W-0/0           | R/W-0/0           | R/W-0/0    |

|------------------|------------------------------------------------------|------------------|------|-----------------|-------------------|-------------------|------------|

| _                | -                                                    | —                | —    | GxAS3E          | GxAS2E            | GxAS1E            | GxAS0E     |

| bit 7            |                                                      |                  |      |                 |                   |                   | bit 0      |

|                  |                                                      |                  |      |                 |                   |                   |            |

| Legend:          |                                                      |                  |      |                 |                   |                   |            |

| R = Readable     | e bit                                                | W = Writable     | bit  | U = Unimplem    | ented bit, read   | as '0'            |            |

| u = Bit is unc   | hanged                                               | x = Bit is unki  | nown | -n/n = Value at | POR and BOF       | R/Value at all of | her Resets |

| '1' = Bit is set | t                                                    | '0' = Bit is cle | ared | q = Value depe  | ends on condition | on                |            |

|                  |                                                      |                  |      |                 |                   |                   |            |

| bit 7-4          | Unimplemer                                           | nted: Read as    | ʻ0'  |                 |                   |                   |            |

| bit 3            | bit 3 GxAS3E: COGx Auto-shutdown Source Enable bit 3 |                  |      |                 |                   |                   |            |

|                  | 1 = COGx is shutdown when CLC2 output is low         |                  |      |                 |                   |                   |            |

|                  | 0 = CLC2 output has no effect on shutdown            |                  |      |                 |                   |                   |            |

| bit 2            | it 2 GxAS2E: COGx Auto-shutdown Source Enable bit 2  |                  |      |                 |                   |                   |            |

|                  | 1 = COGx is shutdown when Comparator 2 output is low |                  |      |                 |                   |                   |            |

|                  | 0 = Comparator 2 output has no effect on shutdown    |                  |      |                 |                   |                   |            |

| bit 1            | it 1 GxAS1E: COGx Auto-shutdown Source Enable bit 1  |                  |      |                 |                   |                   |            |

|                  | 1 = COGx is shutdown when Comparator 1 output is low |                  |      |                 |                   |                   |            |

|                  | 0 = Comparator 1 output has no effect on shutdown    |                  |      |                 |                   |                   |            |

| hit 0            | GxAS0E: COGx Auto-shutdown Source Enable bit 0       |                  |      |                 |                   |                   |            |

# REGISTER 18-8: COGxASD1: COG AUTO-SHUTDOWN CONTROL REGISTER 1

| bit 0 | GxAS0E: COGx Auto-shutdown Source Enable bit 0 |

|-------|------------------------------------------------|

| bit 0 | GxAS0E: COGx Auto-shutdown Source Enable bit 0 |

- 1 = COGx is shutdown when Pin selected with COGxPPS control is low

- 0 = Pin selected with COGxPPS control has no effect on shutdown

# 19.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- · Data gating

- Logic function selection

- · Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 19.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 19-2. Data inputs in the figure are identified by a generic numbered input name.

Table 19-1 correlates the generic input name to the actual signal for each CLC module. The column labeled lcxdy indicates the MUX selection code for the selected data input. DxS is an abbreviation for the MUX select input codes: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 19-3 through Register 19-6).

**Note:** Data selections are undefined at power-up.

#### TABLE 19-1: CLCx DATA INPUT SELECTION

| Data Input | lcxdy<br>DxS | CLCx                                               |  |

|------------|--------------|----------------------------------------------------|--|

| LCx_in[31] | 11111        | Fosc                                               |  |

| LCx_in[30] | 11110        | HFINTOSC                                           |  |

| LCx_in[29] | 11101        | LFINTOSC                                           |  |

| LCx_in[28] | 11100        | ADC FRC                                            |  |

| LCx_in[27] | 11011        | IOCIF set signal (bit?)                            |  |

| LCx_in[26] | 11010        | T2_match                                           |  |

| LCx_in[25] | 11001        | T1_overflow                                        |  |

| LCx_in[24] | 11000        | T0_overflow                                        |  |

| LCx_in[23] | 10111        | T6_match                                           |  |

| LCx_in[22] | 10110        | T4_match                                           |  |

| LCx_in[21] | 10101        | DT from EUSART                                     |  |

| LCx_in[20] | 10100        | TX/CK from EUSART                                  |  |

| LCx_in[19] | 10011        | ZCDx_out from Zero-Cross Detect                    |  |

| LCx_in[18] | 10010        | SDO from MSSP                                      |  |

| LCx_in[17] | 10001        | Reserved                                           |  |

| LCx_in[16] | 10000        | SCK from MSSP                                      |  |

| LCx_in[15] | 01111        | PWM4_out                                           |  |

| LCx_in[14] | 01110        | PWM3_out                                           |  |

| LCx_in[13] | 01101        | CCP2 output                                        |  |

| LCx_in[12] | 01100        | CCP1 output                                        |  |

| LCx_in[11] | 01011        | COG1B                                              |  |

| LCx_in[10] | 01010        | COG1A                                              |  |

| LCx_in[9]  | 01001        | C2OUT                                              |  |

| LCx_in[8]  | 01000        | C1OUT                                              |  |

| LCx_in[7]  | 00111        | Reserved                                           |  |

| LCx_in[6]  | 00110        | LC3_out from the CLC3                              |  |

| LCx_in[5]  | 00101        | LC2_out from the CLC2                              |  |

| LCx_in[4]  | 00100        | LC1_out from the CLC1                              |  |

| LCx_in[3]  | 00011        | CLCIN3 pin input selected in<br>CLCIN3PPS register |  |

| LCx_in[2]  | 00010        | CLCIN2 pin input selected in<br>CLCIN2PPS register |  |

| LCx_in[1]  | 00001        | CLCIN1 pin input selected in<br>CLCIN1PPS register |  |

| LCx_in[0]  | 00000        | CLCIN0 pin input selected in<br>CLCIN0PPS register |  |

# 19.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 19-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- · Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

# 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## **19.3 Output Mirror Copies**

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

# 19.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 19.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

| R/W-x/u          | R/W-x/u                                                                          | R/W-x/u                           | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|----------------------------------------------------------------------------------|-----------------------------------|----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N                                                                         | LCxG3D3T                          | LCxG3D3N       | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |                                                                                  |                                   |                |                |                  |                  | bit 0       |

|                  |                                                                                  |                                   |                |                |                  |                  |             |

| Legend:          |                                                                                  |                                   |                |                |                  |                  |             |

| R = Readable I   |                                                                                  | W = Writable                      |                | •              | nented bit, read |                  |             |

| u = Bit is uncha | anged                                                                            | x = Bit is unkn                   |                | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                                                                                  | '0' = Bit is clea                 | ared           |                |                  |                  |             |

| hit 7            |                                                                                  | Noto 2 Doto 4 T                   | rue (nen inver | tod) bit       |                  |                  |             |

| bit 7            |                                                                                  | Sate 3 Data 4 T                   |                | ted) bit       |                  |                  |             |

|                  |                                                                                  | gated into lcxg<br>not gated into |                |                |                  |                  |             |

| bit 6            |                                                                                  | Gate 3 Data 4 N                   |                | ted) bit       |                  |                  |             |

|                  |                                                                                  | gated into lcxc                   | •              | ,              |                  |                  |             |

|                  |                                                                                  | not gated into                    |                |                |                  |                  |             |

| bit 5            | LCxG3D3T: 0                                                                      | Gate 3 Data 3 T                   | rue (non-inver | ted) bit       |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   |                |                |                  |                  |             |

|                  | 0 = Icxd3T is                                                                    | not gated into                    | lcxg3          |                |                  |                  |             |

| bit 4            |                                                                                  | Gate 3 Data 3 N                   | •              | ted) bit       |                  |                  |             |

|                  |                                                                                  | gated into loxo                   |                |                |                  |                  |             |

|                  |                                                                                  | not gated into                    | •              |                |                  |                  |             |

| bit 3            | LCxG3D2T: Gate 3 Data 2 True (non-inverted) bit                                  |                                   |                |                |                  |                  |             |

|                  |                                                                                  | gated into lcxg                   |                |                |                  |                  |             |

| bit 2            | 0 = 1 cx c2 D2 N                                                                 |                                   |                |                |                  |                  |             |

| bit 2            | LCxG3D2N: Gate 3 Data 2 Negated (inverted) bit<br>1 = lcxd2N is gated into lcxg3 |                                   |                |                |                  |                  |             |

|                  | 0 = Icxd2N is not gated into Icxg3                                               |                                   |                |                |                  |                  |             |

| bit 1            | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit                                  |                                   |                |                |                  |                  |             |

|                  | 1 = lcxd1T is gated into lcxg3                                                   |                                   |                |                |                  |                  |             |

|                  | 0 = lcxd1T is not gated into lcxg3                                               |                                   |                |                |                  |                  |             |

| bit 0            | LCxG3D1N:                                                                        | Gate 3 Data 1 N                   | Negated (inver | ted) bit       |                  |                  |             |

|                  | 1 = lcxd1N is gated into lcxg3                                                   |                                   |                |                |                  |                  |             |

|                  | 0 = Icxd1N is                                                                    | not gated into                    | leva3          |                |                  |                  |             |

# REGISTER 19-9: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

# 20.2 ADC Operation

#### 20.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 20.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 20.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 20.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 20.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 20.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The Auto-conversion Trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Table 20-2 for auto-conversion sources. TABLE 20-2: AUTO-CONVERSION SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CCP1              |             |

| CCP2              |             |

| Timer0            | T0_overflow |

| Timer1            | T1_overflow |

| Timer2            | T2_match    |

| Timer4            | T4_match    |

| Timer6            | T6_match    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

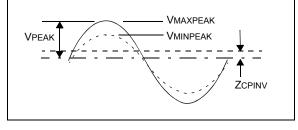

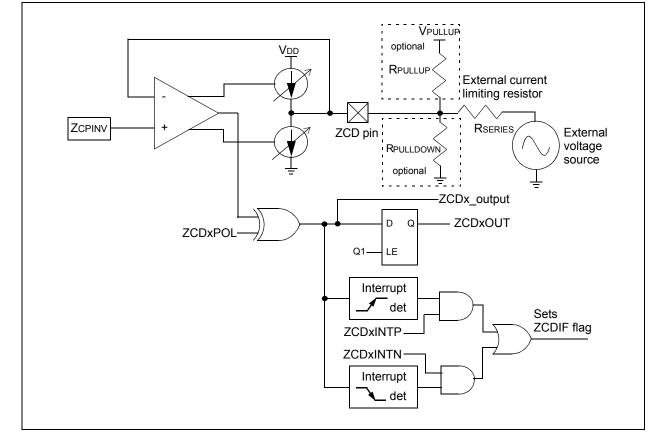

# 23.0 ZERO-CROSS DETECTION (ZCD) MODULE

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, ZCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage. The ZCD module is shown in the simplified block diagram Figure 23-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- · Low EMI cycle switching

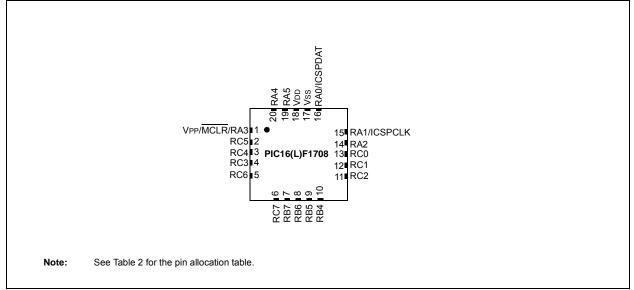

# 23.1 External Resistor Selection

The ZCD module requires a current limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A (refer to Equation 23-1 and Figure 23-1). Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

# FIGURE 23-2: SIMPLIFIED ZCD BLOCK DIAGRAM

# 24.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|

|       | independent prescaler.                |  |  |  |  |  |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

## 24.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |

#### 24.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in Table 32-12: Timer0 and Timer1 External Clock Requirements.

# 24.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

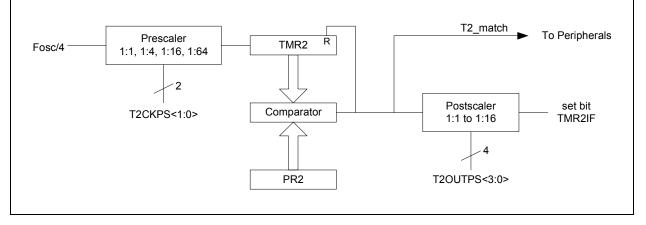

# 26.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2, respectively

- Optional use as the shift clock for the MSSP module

See Figure 26-1 for a block diagram of Timer2.

Three identical Timer2 modules are implemented on this device. To maintain consistency with earlier devices, the timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

# 28.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

# 28.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

# 28.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 28.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 28.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 28.4.3 SDA AND SCL PINS

Selection of any  $l^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

| Note 1: | Data is tied to output zero when an $I^2C$ mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | Any device pin can be selected for SDA<br>and SCL functions with the PPS peripheral.<br>These functions are bidirectional. The SDA<br>input is selected with the SSPDATPPS<br>registers. The SCL input is selected with<br>the SSPCLKPPS registers. Outputs are<br>selected with the RxyPPS registers. It is the<br>user's responsibility to make the selections<br>so that both the input and the output for<br>each function is on the same pin. |

#### 28.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

# TABLE 28-2: I<sup>2</sup>C BUS TERMS

| TABLE 28-2:         | I <sup>2</sup> C BUS TERMS                                                                                                                                                            |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TERM                | Description                                                                                                                                                                           |  |  |  |  |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |  |  |  |  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |  |  |  |  |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                              |  |  |  |  |

| Slave               | The device addressed by the master.                                                                                                                                                   |  |  |  |  |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |  |  |  |  |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |  |  |  |  |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |  |  |  |  |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |  |  |  |  |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |  |  |  |  |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |  |  |  |  |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                    |  |  |  |  |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                            |  |  |  |  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |  |  |  |  |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |  |  |  |  |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |  |  |  |  |

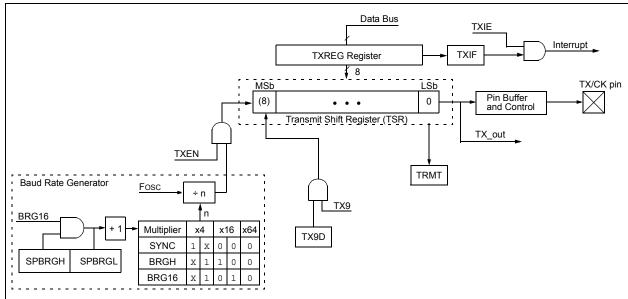

# 29.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 29-1 and Figure 29-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

# FIGURE 29-1: EUSART TRANSMIT BLOCK DIAGRAM

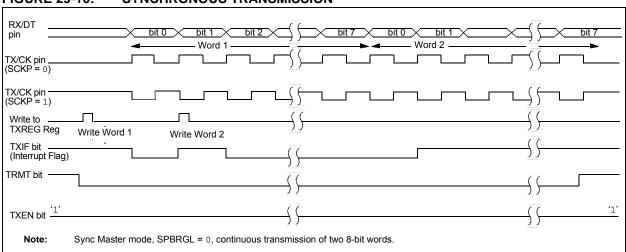

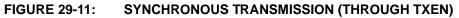

#### FIGURE 29-10: SYNCHRONOUS TRANSMISSION

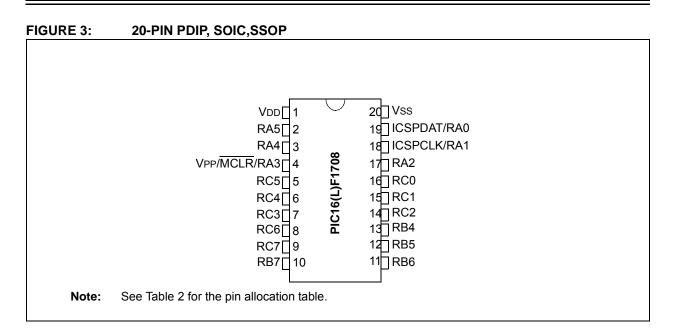

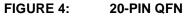

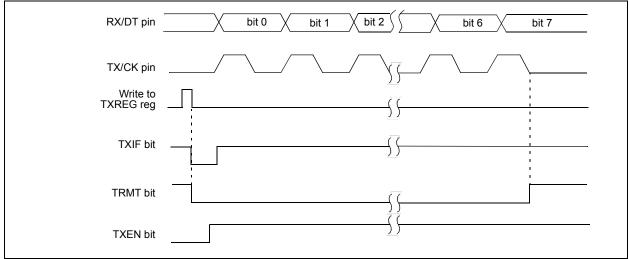

# 30.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16(L)F170X Memory Programming Specification*" (DS41683).

## 30.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

## 30.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 5.5 "MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

# **30.3 Common Programming Interfaces**

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 30-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 30-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 30-3 for more information.

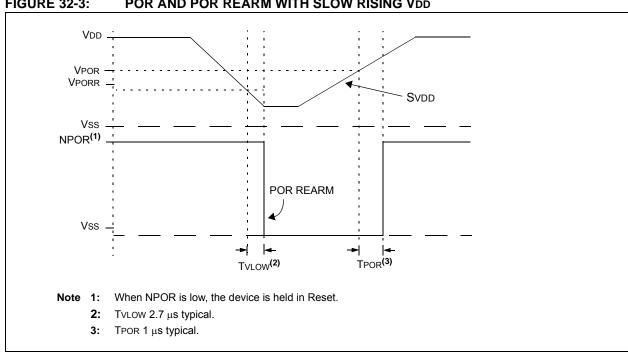

**FIGURE 32-3:** POR AND POR REARM WITH SLOW RISING VDD

# TABLE 32-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No.  | Symbol  | Characteristic             |              | Min.       | Max. | Units | Conditions                                  |

|----------------|---------|----------------------------|--------------|------------|------|-------|---------------------------------------------|

| SP100*         | Тнідн   | Clock high time            | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|                |         |                            | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|                |         |                            | SSP module   | 1.5 TCY    |      |       |                                             |

| SP101* TLOW    | TLOW    | ow Clock low time          | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|                |         |                            | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|                |         |                            | SSP module   | 1.5 TCY    | _    | —     |                                             |

| SP102* Tr      | TR      | SDA and SCL rise time      | 100 kHz mode | _          | 1000 | ns    |                                             |

|                |         |                            | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103* TF      | TF      | SDA and SCL fall time      | 100 kHz mode | —          | 250  | ns    |                                             |

|                |         |                            | 400 kHz mode | 20 + 0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106* THD:DAT | THD:DAT |                            | 100 kHz mode | 0          | _    | ns    |                                             |

|                |         |                            | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| SP107*         | TSU:DAT | Data input setup           | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|                |         | time                       | 400 kHz mode | 100        | _    | ns    |                                             |

| SP109*         | ΤΑΑ     | Output valid from<br>clock | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|                |         |                            | 400 kHz mode | —          | _    | ns    |                                             |

| SP110*         | TBUF    | Bus free time              | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |

|                |         |                            | 400 kHz mode | 1.3        | _    | μS    | before a new transmission<br>can start      |

| SP111          | Св      | Bus capacitive loading     |              |            | 400  | pF    |                                             |

\* These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TSU:DAT  $\geq$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

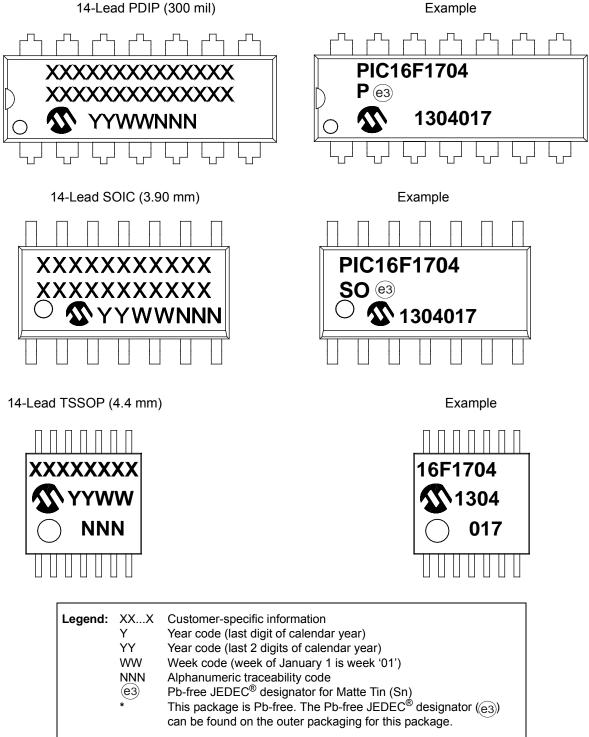

# 35.0 PACKAGING INFORMATION

# 35.1 Package Marking Information

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.