Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

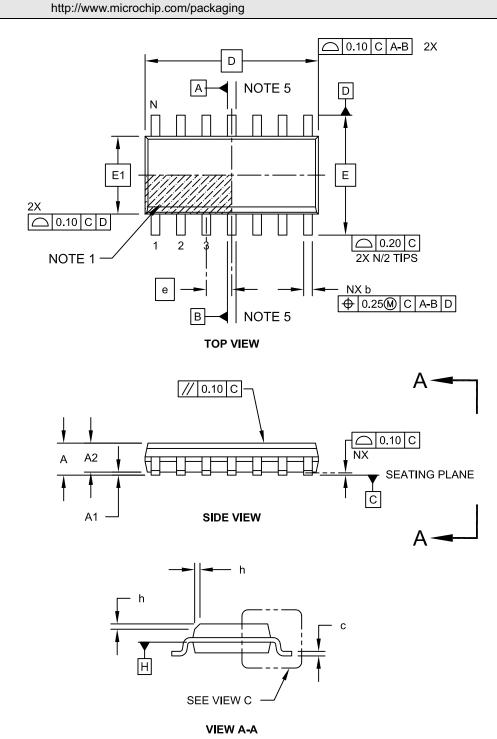

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-QFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1708t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

#### Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device          | Program Memory Space | Last Program Memory | High-Endurance Flash                |  |

|-----------------|----------------------|---------------------|-------------------------------------|--|

|                 | (Words)              | Address             | Memory Address Range <sup>(1)</sup> |  |

| PIC16(L)F1704/8 | 4,096                | 0FFFh               | 0F80h - 0FFFh                       |  |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1704/8 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

## 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.7** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

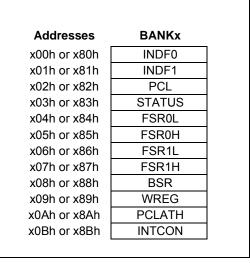

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-9.

#### TABLE 3-2: CORE REGISTERS

## 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 31.0 "Instruction Set Summary").

Note: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

## TABLE 3-4: PIC16(L)1708 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h | Core Registers<br>(Table 3-2) | 080h | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h | Core Registers<br>(Table 3-2) | 280h | Core Registers<br>(Table 3-2) | 300h | Core Registers<br>(Table 3-2) | 380h | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | WPUA                          | 28Ch | ODCONA                        | 30Ch | SLRCONA                       | 38Ch | INLVLA                        |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | ODCONB                        | 30Dh | SLRCONB                       | 38Dh | INLVLB                        |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | WPUC                          | 28Eh | ODCONC                        | 30Eh | SLRCONC                       | 38Eh | INLVLC                        |

| 00Fh | —                             | 08Fh | —                             | 10Fh | —                             | 18Fh | _                             | 20Fh | —                             | 28Fh | —                             | 30Fh | —                             | 38Fh | —                             |

| 010h | —                             | 090h | —                             | 110h | —                             | 190h | —                             | 210h | —                             | 290h | —                             | 310h | —                             | 390h | —                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h | SSP1BUF                       | 291h | CCPR1L                        | 311h | —                             | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h | SSP1ADD                       | 292h | CCPR1H                        | 312h |                               | 392h | IOCAN                         |

| 013h | PIR3                          | 093h | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h | SSP1MSK                       | 293h | CCP1CON                       | 313h |                               | 393h | IOCAF                         |

| 014h | —                             | 094h | —                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h | SSP1STAT                      | 294h | —                             | 314h |                               | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h | SSP1CON                       | 295h | —                             | 315h | _                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h | SSP1CON2                      | 296h | —                             | 316h | —                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h | SSP1CON3                      | 297h | —                             | 317h | —                             | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | DAC1CON0                      | 198h | _                             | 218h | —                             | 298h | CCPR2L                        | 318h | _                             | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | DAC1CON1                      | 199h | RC1REG                        | 219h | —                             | 299h | CCPR2H                        | 319h | —                             | 399h | IOCCF                         |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TX1REG                        | 21Ah | —                             | 29Ah | CCP2CON                       | 31Ah | —                             | 39Ah | —                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | —                             | 19Bh | SP1BRGL                       | 21Bh | —                             | 29Bh | —                             | 31Bh | —                             | 39Bh |                               |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | ZCD1CON                       | 19Ch | SP1BRGH                       | 21Ch | —                             | 29Ch | —                             | 31Ch | —                             | 39Ch |                               |

| 01Dh | —                             | 09Dh | ADCON0                        | 11Dh | —                             | 19Dh | RC1STA                        | 21Dh | —                             | 29Dh | —                             | 31Dh | —                             | 39Dh | —                             |

| 01Eh | —                             | 09Eh | ADCON1                        | 11Eh | —                             | 19Eh | TX1STA                        | 21Eh | —                             | 29Eh | CCPTMRS                       | 31Eh |                               | 39Eh | —                             |

| 01Fh |                               | 09Fh | ADCON2                        | 11Fh | —                             | 19Fh | BAUD1CON                      | 21Fh | —                             | 29Fh | _                             | 31Fh | _                             | 39Fh | _                             |

| 020h |                               | 0A0h | 0                             | 120h | 0                             | 1A0h | 0                             | 220h | 0                             | 2A0h |                               | 320h | General Purpose<br>Register   | 3A0h |                               |

|      | General<br>Purpose            | 32Fh | 16 Bytes                      |      | Unimplemented                 |

|      | Register                      | 330h |                               |      | Read as '0'                   |

|      | 80 Bytes                      |      | Unimplemented<br>Read as '0'  |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h |                               | 170h |                               | 1F0h |                               | 270h |                               | 2F0h |                               | 370h |                               | 3F0h |                               |

|      | Common RAM<br>70h – 7Fh       |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                               | 27Fh |                               | 2FFh |                               | 37Fh |                               | 3FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1708.

#### **TABLE 3-10:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr        | Name                  |             |       |       |       | I     |             |       |       |                      |                                 |

|-------------|-----------------------|-------------|-------|-------|-------|-------|-------------|-------|-------|----------------------|---------------------------------|

|             |                       | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank        | 29                    |             |       |       |       |       |             |       |       |                      |                                 |

| E8Ch        |                       |             |       |       |       |       |             |       |       |                      |                                 |

| <br>E8Fh    | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | _                               |

| E90h        | RA0PPS                | _           | _     | _     |       |       | RA0PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E91h        | RA1PPS                | _           | —     | _     |       |       | RA1PPS<4:02 | >     |       | 0 0000               | u uuuu                          |

| E92h        | RA2PPS                | _           | —     | _     |       |       | RA2PPS<4:02 | >     |       | 0 0000               | u uuuu                          |

| E93h -      |                       | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E94h        | RA4PPS                | _           | _     | _     |       |       | RA4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E95h        | RA5PPS                | _           | _     | _     |       |       | RA5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E96h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E97h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E98h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E99h -      | _                     | Unimplement | ed    |       |       |       |             |       |       | —                    | —                               |

| E9Ah -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E9Bh -      | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | —                               |

| E9Ch        | RB4PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Dh        | RB5PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Eh        | RB6PPS <sup>(4)</sup> | _           | _     | _     |       |       | RB6PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| E9Fh        | RB7PPS <sup>(3)</sup> | _           | _     | _     |       |       | RB7PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA0h        | RC0PPS                | _           | _     | _     |       |       | RC0PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA1h        | RC1PPS                | _           | _     | _     |       |       | RC1PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA2h        | RC2PPS                | _           | _     | _     |       |       | RC2PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA3h        | RC3PPS                | _           | _     | _     |       |       | RC3PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA4h        | RC4PPS                | _           | _     | _     |       |       | RC4PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA5h        | RC5PPS                | _           | _     | _     |       |       | RC5PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA6h        | RC6PPS <sup>(4)</sup> | _           | _     | _     |       |       | RC6PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA7h        | RC7PPS <sup>(4)</sup> | _           | _     | _     |       |       | RC7PPS<4:0  | >     |       | 0 0000               | u uuuu                          |

| EA8h        |                       |             |       |       |       |       |             |       |       |                      |                                 |

| —<br>EEFh - | _                     | Unimplement | ed    |       |       |       |             |       |       | _                    | _                               |

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

PIC16(L)F1704 only. 2:

3:

PIC16(L)F1708 only. Unimplemented on PIC16LF1704/8. 4:

## 11.5 PORTC Registers

#### 11.5.1 DATA REGISTER

PORTC is a 6-bit wide bidirectional port in the PIC16(L)F1704 device and 8-bit wide bidirectional port in the PIC16(L)F1708 device. The corresponding data direction register is TRISC (Register 11-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

## 11.5.2 DIRECTION CONTROL

The TRISC register (Register 11-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 11.5.3 INPUT THRESHOLD CONTROL

The INLVLC register (Register 11-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 32-4: I/O Ports for more information on threshold levels.

| Note: | Changing the input threshold selection<br>should be performed while all peripheral<br>modules are disabled. Changing the<br>threshold level during the time a module is<br>active may inadvertently generate a |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | transition associated with an input pin,<br>regardless of the actual voltage level on<br>that pin.                                                                                                             |

## 11.5.4 OPEN-DRAIN CONTROL

The ODCONC register (Register 11-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 11.5.5 SLEW RATE CONTROL

The SLRCONC register (Register 11-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 11.5.6 ANALOG CONTROL

The ANSELC register (Register 11-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |

#### 11.5.7 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELC register. Digital output functions may continue to control the pin when it is in Analog mode.

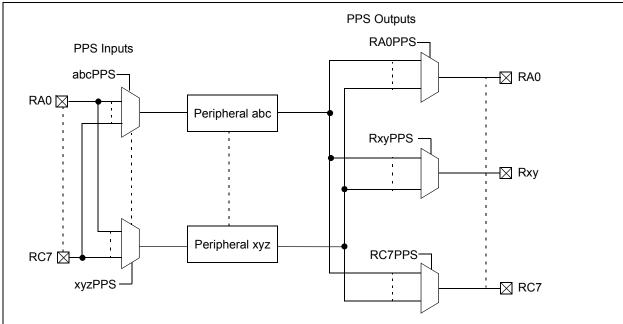

## 12.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 12-1.

## 12.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has associated analog functions, the ANSEL bit for that pin must be cleared to enable the digital input buffer. Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 12-1 for PIC16(L)F1704 devices and Register 12-2 for PIC16(L)F1708 devices.

| Note: | The notation "xxx" in the register name is    |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | a place holder for the peripheral identifier. |  |  |  |  |  |  |  |

|       | For example, CLC1PPS.                         |  |  |  |  |  |  |  |

## 12.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- · COG (auto-shutdown)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 12-3.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

## FIGURE 12-1: SIMPLIFIED PPS BLOCK DIAGRAM

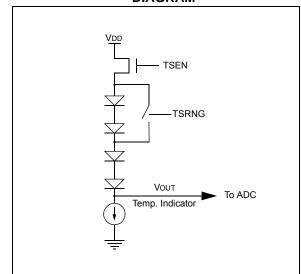

## 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between  $-40^{\circ}$ C and  $+85^{\circ}$ C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

## 15.1 Circuit Operation

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

## EQUATION 15-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

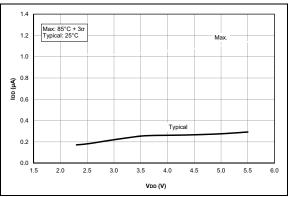

## 15.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

#### TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## 15.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for detailed information.

## 18.13 Register Definitions: COG Control

## REGISTER 18-1: COGxCON0: COG CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0        | U-0                                | R/W-0/0         | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0      |

|------------------|----------------|------------------------------------|-----------------|------------------|-----------------|-------------------|--------------|

| GxEN             | GxLD           | _                                  | GxC             | S<1:0>           |                 | GxMD<2:0>         |              |

| bit 7            |                |                                    |                 |                  |                 |                   | bit C        |

|                  |                |                                    |                 |                  |                 |                   |              |

| Legend:          |                |                                    |                 |                  |                 |                   |              |

| R = Readable     | bit            | W = Writable                       | bit             | U = Unimpler     | mented bit, rea | d as '0'          |              |

| u = Bit is unch  | nanged         | x = Bit is unki                    | nown            | -n/n = Value a   | at POR and BC   | OR/Value at all o | ther Resets  |

| '1' = Bit is set |                | '0' = Bit is cle                   | ared            | q = Value de     | pends on cond   | tion              |              |

|                  |                |                                    |                 |                  |                 |                   |              |

| bit 7            | GxEN: COG      | x Enable bit                       |                 |                  |                 |                   |              |

|                  | 1 = Module i   |                                    |                 |                  |                 |                   |              |

|                  | 0 = Module i   |                                    |                 |                  |                 |                   |              |

| bit 6            |                | k Load Buffers                     |                 |                  |                 |                   |              |

|                  |                | to buffer transf                   |                 |                  | d with register | values on next i  | input events |

| bit 5            | Unimplemer     | ted: Read as '                     | 0'              |                  |                 |                   |              |

| bit 4-3          | GxCS<1:0>:     | COGx Clock S                       | election bits   |                  |                 |                   |              |

|                  |                | ed. Do not use                     |                 |                  |                 |                   |              |

|                  |                | clock is HFINTC                    | OSC (stays ac   | tive during Slee | ep)             |                   |              |

|                  | $01 = COG_{0}$ | CIOCK IS FOSC                      |                 |                  |                 |                   |              |

| bit 2-0          | _              | COGx Mode S                        | Selection bits  |                  |                 |                   |              |

| 5112 0           |                | ved. Do not us                     |                 |                  |                 |                   |              |

|                  |                | outputs operate                    |                 | mode             |                 |                   |              |

|                  | 100 = COG      | outputs operate                    | e in Half-Bridg | e mode           |                 |                   |              |

|                  |                | outputs operate                    |                 |                  |                 |                   |              |

|                  |                | outputs operate<br>outputs operate |                 |                  |                 |                   |              |

|                  |                | outputs operate                    |                 |                  |                 |                   |              |

|                  |                |                                    |                 |                  |                 |                   |              |

#### REGISTER 18-12: COGxBLKR: COG RISING EVENT BLANKING COUNT REGISTER

| U-0                                     | U-0 | R/W-x/u | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-----------------------------------------|-----|---------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

|                                         |     |         |         | GxBLk                                                 | (R<5:0> |         |         |  |  |  |

| bit 7                                   |     |         |         |                                                       |         |         | bit 0   |  |  |  |

|                                         |     |         |         |                                                       |         |         |         |  |  |  |

| Legend:                                 |     |         |         |                                                       |         |         |         |  |  |  |

| R = Readable bit W = Writable bit       |     |         | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |     |         | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |     |         |         | q = Value depends on condition                        |         |         |         |  |  |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0

GxBLKR<5:0>: Rising Event Blanking Count Value bits

= Number of COGx clock periods to inhibit falling event inputs

#### REGISTER 18-13: COGxBLKF: COG FALLING EVENT BLANKING COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|--|--|--|

|       |     |         | GxBLKF<5:0> |         |         |         |         |  |  |  |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 GxBLKF<5:0>: Falling Event Blanking Count Value bits

= Number of COGx clock periods to inhibit rising event inputs

| R/W-x/u          | R/W-x/u                                                              | R/W-x/u                           | R/W-x/u        | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u     |  |  |

|------------------|----------------------------------------------------------------------|-----------------------------------|----------------|--------------|------------------|----------|-------------|--|--|

| LCxG2D4T         | LCxG2D4N                                                             | LCxG2D3T                          | LCxG2D3N       | LCxG2D2T     | LCxG2D2N         | LCxG2D1T | LCxG2D1N    |  |  |

| bit 7            |                                                                      |                                   |                |              |                  |          | bit         |  |  |

| Legend:          |                                                                      |                                   |                |              |                  |          |             |  |  |

| R = Readable     | bit                                                                  | W = Writable                      | bit            | U = Unimpler | nented bit, read | l as '0' |             |  |  |

| u = Bit is uncha |                                                                      | x = Bit is unkr                   |                | •            | at POR and BO    |          | ther Resets |  |  |

| '1' = Bit is set |                                                                      | '0' = Bit is cle                  |                |              |                  |          |             |  |  |

|                  |                                                                      |                                   |                |              |                  |          |             |  |  |

| bit 7            |                                                                      | Sate 2 Data 4 1                   | ,              | rted) bit    |                  |          |             |  |  |

|                  |                                                                      | gated into lcxg<br>not gated into |                |              |                  |          |             |  |  |

| bit 6            |                                                                      | Gate 2 Data 4                     | •              | ted) bit     |                  |          |             |  |  |

|                  |                                                                      | gated into Icx                    |                |              |                  |          |             |  |  |

|                  | 0 = Icxd4N is                                                        | not gated into                    | lcxg2          |              |                  |          |             |  |  |

| bit 5            |                                                                      | Gate 2 Data 3 1                   |                | rted) bit    |                  |          |             |  |  |

|                  | 1 = lcxd3T is gated into lcxg2<br>0 = lcxd3T is not gated into lcxg2 |                                   |                |              |                  |          |             |  |  |

| bit 4            |                                                                      | •                                 | •              | tod) bit     |                  |          |             |  |  |

| DIL 4            |                                                                      | Gate 2 Data 3                     |                | ted) bit     |                  |          |             |  |  |

|                  |                                                                      | not gated into                    |                |              |                  |          |             |  |  |

| bit 3            |                                                                      | Gate 2 Data 2 1                   |                | rted) bit    |                  |          |             |  |  |

|                  | 1 = Icxd2T is                                                        | gated into lcxg                   | j2             |              |                  |          |             |  |  |

|                  | 0 = Icxd2T is                                                        | not gated into                    | lcxg2          |              |                  |          |             |  |  |

| bit 2            | LCxG2D2N:                                                            | Gate 2 Data 2                     | Negated (inver | ted) bit     |                  |          |             |  |  |

|                  |                                                                      | gated into lcx                    | •              |              |                  |          |             |  |  |

|                  |                                                                      | not gated into                    | •              |              |                  |          |             |  |  |

| bit 1            |                                                                      | Sate 2 Data 1 7                   | · ·            | rted) bit    |                  |          |             |  |  |

|                  |                                                                      | gated into lcxg<br>not gated into |                |              |                  |          |             |  |  |

| bit 0            |                                                                      | Gate 2 Data 1                     | •              | rted) bit    |                  |          |             |  |  |

|                  |                                                                      | gated into lcx                    | •              |              |                  |          |             |  |  |

|                  |                                                                      | not gated into                    |                |              |                  |          |             |  |  |

## REGISTER 19-8: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

## 20.2 ADC Operation

#### 20.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 20.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 20.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 20.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

## 20.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 20.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The Auto-conversion Trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Table 20-2 for auto-conversion sources. TABLE 20-2: AUTO-CONVERSION SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CCP1              |             |

| CCP2              |             |

| Timer0            | T0_overflow |

| Timer1            | T1_overflow |

| Timer2            | T2_match    |

| Timer4            | T4_match    |

| Timer6            | T6_match    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

## 28.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 28.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 28.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 28.4.3 SDA AND SCL PINS

Selection of any  $l^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

| Note 1: | Data is tied to output zero when an $I^2C$ mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | Any device pin can be selected for SDA<br>and SCL functions with the PPS peripheral.<br>These functions are bidirectional. The SDA<br>input is selected with the SSPDATPPS<br>registers. The SCL input is selected with<br>the SSPCLKPPS registers. Outputs are<br>selected with the RxyPPS registers. It is the<br>user's responsibility to make the selections<br>so that both the input and the output for<br>each function is on the same pin. |

#### 28.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 28-2: I<sup>2</sup>C BUS TERMS

| TABLE 28-2:         | I <sup>2</sup> C BUS TERMS                                                                                                                                                            |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TERM                | Description                                                                                                                                                                           |  |  |  |  |  |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |  |  |  |  |  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |  |  |  |  |  |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                              |  |  |  |  |  |

| Slave               | The device addressed by the master.                                                                                                                                                   |  |  |  |  |  |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |  |  |  |  |  |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |  |  |  |  |  |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |  |  |  |  |  |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |  |  |  |  |  |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |  |  |  |  |  |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |  |  |  |  |  |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                    |  |  |  |  |  |

| Write Request       | Slave receives <u>a</u> matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                     |  |  |  |  |  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |  |  |  |  |  |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |  |  |  |  |  |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |  |  |  |  |  |

#### 28.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 28.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the  $R/\overline{W}$  bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the ninth falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 28.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 28.5.6.3 Byte NACKing

When AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSPCON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

#### 28.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 28-23).

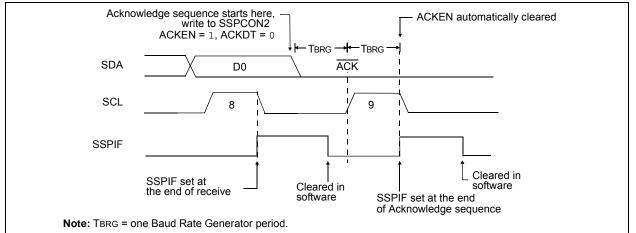

#### 28.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 28-30).

#### 28.6.8.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

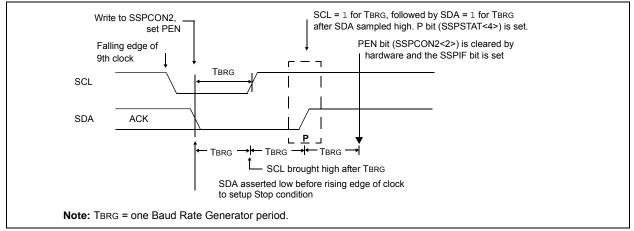

#### 28.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 28-31).

## 28.6.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## FIGURE 28-30: ACKNOWLEDGE SEQUENCE WAVEFORM

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)                   | bit 0         bit 2         bit 3         bit 4         bit 5         bit 6         bit 7 |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|

| TX/CK pin                                                 |                                                                                           |

| SREN bit                                                  | . <sup>0</sup> ,                                                                          |

| CREN bit <u><sup>0</sup></u><br>RCIF bit<br>(Interrupt) — |                                                                                           |

| Read<br>RCREG<br>Note: Timing diag                        | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0.                    |

| Note: I iming diag                                        | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = 0.                  |

## FIGURE 29-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## TABLE 29-8: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION RECEPTION

| Name                  | Bit 7                 | Bit 6                 | Bit 5                | Bit 4                | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------------------|----------------------|--------------|------------|--------|--------|---------------------|

| ANSELA                | _                     | —                     |                      | ANSA4                | _            | ANSA2      | ANSA1  | ANSA0  | 122                 |

| ANSELB <sup>(1)</sup> | _                     | —                     | ANSB5                | ANSB4                | -            | _          | -      | —      | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5 <sup>(2)</sup> | ANSC4 <sup>(2)</sup> | ANSC3        | ANSC2      | ANSC1  | ANSC0  | 133                 |

| BAUD1CON              | ABDOVF                | RCIDL                 |                      | SCKP                 | BRG16        | —          | WUE    | ABDEN  | 336                 |

| CKPPS                 | _                     | —                     | —                    |                      |              | CKPPS<4:0> |        |        | 138, 139            |

| INTCON                | GIE                   | PEIE                  | TMR0IE               | INTE                 | IOCIE        | TMR0IF     | INTF   | IOCIF  | 85                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE                 | TXIE                 | SSP1IE       | CCP1IE     | TMR2IE | TMR1IE | 86                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF                 | TXIF                 | SSP1IF       | CCP1IF     | TMR2IF | TMR1IF | 89                  |

| RC1REG                |                       |                       | EUS                  | SART Receiv          | e Data Regis | ter        |        |        | 329*                |

| RC1STA                | SPEN                  | RX9                   | SREN                 | CREN                 | ADDEN        | FERR       | OERR   | RX9D   | 335                 |

| RXPPS                 | _                     | _                     |                      |                      |              | RXPPS<4:0> |        |        | 138, 139            |

| RxyPPS                | _                     | —                     |                      | RxyPPS<4:0>          |              |            | 140    |        |                     |

| SP1BRGL               |                       | BRG<7:0>              |                      |                      | 337*         |            |        |        |                     |

| SP1BRGH               | BRG<15:8>             |                       |                      |                      | 337*         |            |        |        |                     |

| TRISA                 | _                     | —                     | TRISA5               | TRISA4               | (3)          | TRISA2     | TRISA1 | TRISA0 | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5               | TRISB4               | —            | —          | —      | —      | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5               | TRISC4               | TRISC3       | TRISC2     | TRISC1 | TRISA0 | 132                 |

| TX1STA                | CSRC                  | TX9                   | TXEN                 | SYNC                 | SENDB        | BRGH       | TRMT   | TX9D   | 334                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception. \* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

**3:** Unimplemented, read as '1'.

## 29.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 29.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 29.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|----------------------|--------------|------------|--------|--------|---------------------|

| ANSELA                | _                     | —                     |          | ANSA4                |              | ANSA2      | ANSA1  | ANSA0  | 122                 |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5    | ANSB4                | _            | _          | _      | _      | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5(2) | ANSC4 <sup>(2)</sup> | ANSC3        | ANSC2      | ANSC1  | ANSC0  | 133                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | _        | SCKP                 | BRG16        | _          | WUE    | ABDEN  | 336                 |

| CKPPS                 | _                     | —                     | _        |                      |              | CKPPS<4:0> |        |        | 138, 139            |

| INTCON                | GIE                   | PEIE                  | TMR0IE   | INTE                 | IOCIE        | TMR0IF     | INTF   | IOCIF  | 85                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE     | TXIE                 | SSP1IE       | CCP1IE     | TMR2IE | TMR1IE | 86                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF     | TXIF                 | SSP1IF       | CCP1IF     | TMR2IF | TMR1IF | 89                  |

| RC1REG                |                       |                       | EUS      | ART Receiv           | e Data Regis | ter        |        |        | 329*                |

| RC1STA                | SPEN                  | RX9                   | SREN     | CREN                 | ADDEN        | FERR       | OERR   | RX9D   | 335                 |

| RXPPS                 | _                     | —                     | _        |                      |              | RXPPS<4:0> |        |        | 138, 139            |

| TRISA                 | _                     | _                     | TRISA5   | TRISA4               | _(3)         | TRISA2     | TRISA1 | TRISA0 | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4               | _            | _          | _      | _      | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4               | TRISC3       | TRISC2     | TRISC1 | TRISA0 | 132                 |

| TX1STA                | CSRC                  | TX9                   | TXEN     | SYNC                 | SENDB        | BRGH       | TRMT   | TX9D   | 334                 |

## TABLE 29-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

Note 1: PIC16(L)F1708 only.

2: PIC16(L)F1704 only.

3: Unimplemented, read as '1'.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract W from literal                                                                                                           |                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                          |                 |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                 |                 |  |  |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                                 |                 |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                          |                 |  |  |  |  |  |

| Description:     | The W register is subtracted (2's<br>complement method) from the 8-bit<br>literal 'k'. The result is placed in the W<br>register. |                 |  |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                      | W > k           |  |  |  |  |  |

|                  | C = 1                                                                                                                             | $W \leq k$      |  |  |  |  |  |

|                  | DC = 0                                                                                                                            | W<3:0> > k<3:0> |  |  |  |  |  |

**DC =** 1

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                 |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT} \text{ prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                        |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |  |  |  |  |