#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8SX                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SmartCard, USB                            |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 92                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 40K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f61665d50fpv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 30.9  | Power-On Reset Circuit and Voltage-Detection Circuit Characteristics<br>(H8SX/1665M Group) |      |

|-------|--------------------------------------------------------------------------------------------|------|

| Appe  | ndix                                                                                       |      |

| A.    | Port States in Each Pin State                                                              |      |

| B.    | Product Lineup                                                                             |      |

| C.    | Package Dimensions                                                                         |      |

| D.    | Treatment of Unused Pins                                                                   |      |

| Main  | Revisions and Additions in this Edition                                                    |      |

| Index | ۲                                                                                          | 1447 |

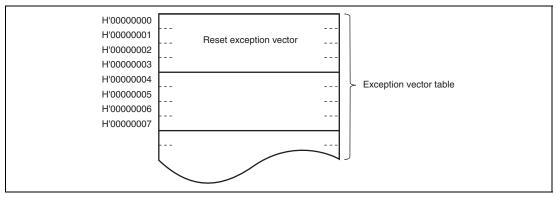

Figure 2.6 Exception Vector Table (Maximum Modes)

The memory indirect (@@aa:8) and extended memory indirect (@@vec:7) addressing modes are used in the JMP and JSR instructions. An 8-bit absolute address included in the instruction code specifies a memory location. Execution branches to the contents of the memory location. In maximum mode, an operand is a 32-bit (longword) operand, providing a 32-bit branch address.

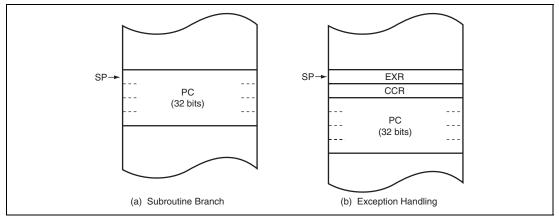

Stack Structure

The stack structure of PC at a subroutine branch and that of PC and CCR at an exception handling are shown in figure 2.7. The PC contents are saved or restored in 32-bit units. The EXR contents are saved or restored regardless of whether or not EXR is in use.

Figure 2.7 Stack Structure (Maximum Mode)

# 2.8 Addressing Modes and Effective Address Calculation

The H8SX CPU supports the 11 addressing modes listed in table 2.12. Each instruction uses a subset of these addressing modes.

Bit manipulation instructions use register direct, register indirect, or absolute addressing mode to specify an operand, and register direct (BSET, BCLR, BNOT, and BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

| No. | Addressing Mode                              | Symbol                                    |

|-----|----------------------------------------------|-------------------------------------------|

| 1   | Register direct                              | Rn                                        |

| 2   | Register indirect                            | @ERn                                      |

| 3   | Register indirect with displacement          | @(d:2,ERn)/@(d:16,ERn)/@(d:32,ERn)        |

| 4   | Index register indirect with displacement    | @(d:16, RnL.B)/@(d:16,Rn.W)/@(d:16,ERn.L) |

|     |                                              | @(d:32, RnL.B)/@(d:32,Rn.W)/@(d:32,ERn.L) |

| 5   | Register indirect with post-increment        | @ERn+                                     |

|     | Register indirect with pre-decrement         | @-ERn                                     |

|     | Register indirect with pre-increment         | @+ERn                                     |

|     | Register indirect with post-decrement        | @ERn-                                     |

| 6   | Absolute address                             | @aa:8/@aa:16/@aa:24/@aa:32                |

| 7   | Immediate                                    | #xx:3/#xx:4/#xx:8/#xx:16/#xx:32           |

| 8   | Program-counter relative                     | @(d:8,PC)/@(d:16,PC)                      |

| 9   | Program-counter relative with index register | @(RnL.B,PC)/@(Rn.W,PC)/@(ERn.L,PC)        |

| 10  | Memory indirect                              | @@aa:8                                    |

| 11  | Extended memory indirect                     | @ @ vec:7                                 |

### Table 2.12 Addressing Modes

# 2.8.1 Register Direct—Rn

The operand value is the contents of an 8-, 16-, or 32-bit general register which is specified by the register field in the instruction code.

R0H to R7H and R0L to R7L can be specified as 8-bit registers.

R0 to R7 and E0 to E7 can be specified as 16-bit registers.

ER0 to ER7 can be specified as 32-bit registers.

|                |                         |                  | vector Address Offset*                      | -                |          |                   |                    |

|----------------|-------------------------|------------------|---------------------------------------------|------------------|----------|-------------------|--------------------|

| Classification | Interrupt Source        | Vector<br>Number | Advanced Mode, Middle<br>Mode, Maximum Mode | IPR              | Priority | DTC<br>Activation | DMAC<br>Activation |

| TPU_11         | TGI11A                  | 188              | H'02F0                                      | IPRO10 to IPRO8  | High     | 0                 | 0                  |

|                | TGI11B                  | 189              | H'02F4                                      | -                | 1        | 0                 | _                  |

|                | TCI11V                  | 190              | H'02F8                                      | IPRO6 to IPRO4   |          | _                 | _                  |

|                | TCI11U                  | 191              | H'02FC                                      | -                |          | _                 | _                  |

| _              | Reserved for            | 192              | H'0300                                      | _                | -        | _                 | _                  |

|                | system use              | I                | I                                           |                  |          | I                 | I                  |

|                |                         | 215              | H'035C                                      |                  |          | _                 | _                  |

| IIC2_0         | IICI0                   | 216              | H'0360                                      | IPRQ6 to IPRQ4   | -        | _                 | _                  |

|                | Reserved for system use | 217              | H'0364                                      | -                |          | _                 | _                  |

| IIC2_1         | IICI1                   | 218              | H'0368                                      | -                |          | _                 | _                  |

|                | Reserved for system use | 219              | H'036C                                      | -                |          | _                 | _                  |

| SCI_5          | RXI5                    | 220              | H'0370                                      | IPRQ2 to IPRQ0   | -        | _                 | 0                  |

|                | TXI5                    | 221              | H'0374                                      | -                |          | _                 | 0                  |

|                | ERI5                    | 222              | H'0378                                      | -                |          | _                 | _                  |

|                | TEI5                    | 223              | H'037C                                      | -                |          | _                 | _                  |

| SCI_6          | RXI6                    | 224              | H'0380                                      | IPRR14 to IPRR12 | -        | _                 | 0                  |

|                | TXI6                    | 225              | H'0384                                      | -                |          | _                 | 0                  |

|                | ERI6                    | 226              | H'0388                                      | -                |          | _                 | _                  |

|                | TEI6                    | 227              | H'038C                                      | -                |          | _                 | _                  |

| TMR_4          | CMIA4 or CMIB4          | 228              | H'0390                                      | IPRR10 to IPRR8  | -        | _                 | _                  |

| TMR_5          | CMIA5 or CMIB5          | 229              | H'0394                                      | -                |          | _                 | _                  |

| TMR_6          | CMIA6 or CMIB6          | 230              | H'0398                                      | -                |          | _                 | _                  |

| TMR_7          | CMIA7 or CMIB7          | 231              | H'039C                                      | -                | Low      | _                 | _                  |

|                |                         |                  |                                             |                  |          |                   |                    |

RENESAS

#### Vector Address Offset\*1

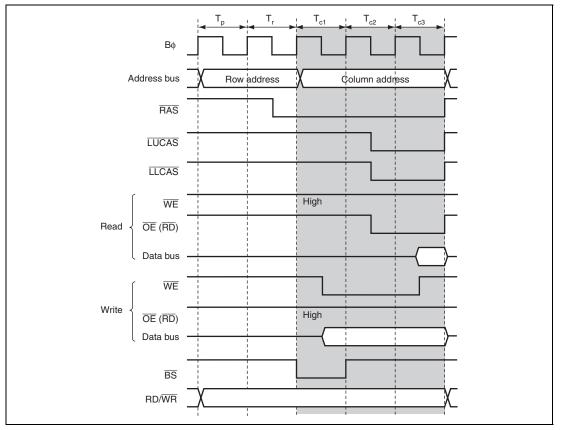

# 9.10.6 Controlling Column Address Output Cycle

The number of column address output cycles can be changed from two to three clock cycles by setting the CAST bit in DRAMCR. Set the bit according to the DRAM to be used and the frequency of this LSI so that the  $\overline{CAS}$  pulse width can be optimal.

Figure 9.39 shows a timing example when the number of column address output cycles is set to three clock cycles.

Figure 9.39 Access Timing Example of Column Address Output Cycles for 3 Clock Cycles (RAST = 0)

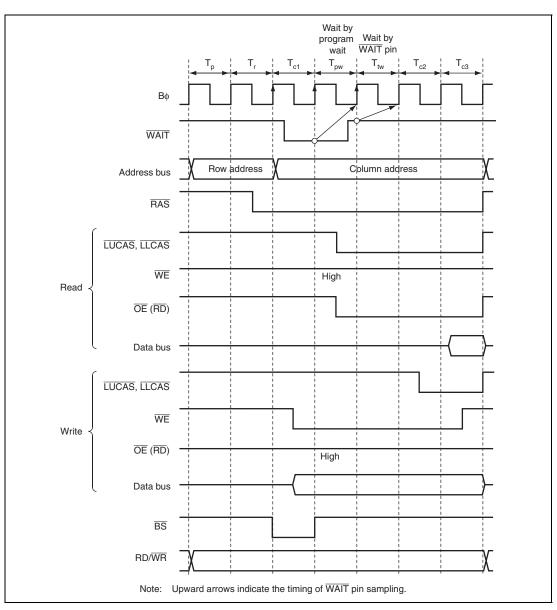

Figure 9.44 Example of Wait Cycle Insertion Timing for 3-Cycle Column Address Output

# 10.3.7 DMA Address Control Register (DACR)

| Bit           | 31    | 30   | 29   | 28    | 27    | 26    | 25    | 24    |

|---------------|-------|------|------|-------|-------|-------|-------|-------|

| Bit Name      | AMS   | DIRS | _    | _     | _     | RPTIE | ARS1  | ARS0  |

| Initial Value | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| R/W           | R/W   | R/W  | R    | R     | R     | R/W   | R/W   | R/W   |

| Bit           | 23    | 22   | 21   | 20    | 19    | 18    | 17    | 16    |

| Bit Name      | —     |      | SAT1 | SAT0  | —     | —     | DAT1  | DAT0  |

| Initial Value | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| R/W           | R     | R    | R/W  | R/W   | R     | R     | R/W   | R/W   |

| Bit           | 15    | 14   | 13   | 12    | 11    | 10    | 9     | 8     |

| Bit Name      | SARIE | —    | _    | SARA4 | SARA3 | SARA2 | SARA1 | SARA0 |

| Initial Value | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| R/W           | R/W   | R    | R    | R/W   | R/W   | R/W   | R/W   | R/W   |

| Bit           | 7     | 6    | 5    | 4     | 3     | 2     | 1     | 0     |

| Bit Name      | DARIE |      | _    | DARA4 | DARA3 | DARA2 | DARA1 | DARA0 |

| Initial Value | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| R/W           | R/W   | R    | R    | R/W   | R/W   | R/W   | R/W   | R/W   |

DACR specifies the operating mode and transfer method.

| <b>D</b> :4 | Dit Name | Initial | DAV | Description                                                                                                                                            |

|-------------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Bit Name | Value   | R/W | Description                                                                                                                                            |

| 31          | AMS      | 0       | R/W | Address Mode Select                                                                                                                                    |

|             |          |         |     | Selects address mode from single or dual address mode. In single address mode, the $\overline{\text{DACK}}$ pin is enabled according to the DACKE bit. |

|             |          |         |     | 0: Dual address mode                                                                                                                                   |

|             |          |         |     | 1: Single address mode                                                                                                                                 |

| 30          | DIRS     | 0       | R/W | Single Address Direction Select                                                                                                                        |

|             |          |         |     | Specifies the data transfer direction in single address mode. This bit s ignored in dual address mode.                                                 |

|             |          |         |     | 0: Specifies DSAR as source address                                                                                                                    |

|             |          |         |     | 1: Specifies DDAR as destination address                                                                                                               |

| 29 to 27    | _        | All 0   | R   | Reserved                                                                                                                                               |

|             |          |         |     | These bits are always read as 0 and cannot be modified.                                                                                                |

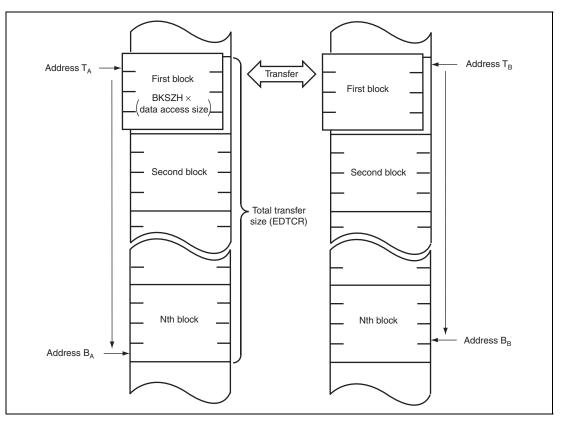

Figure 11.12 Block Transfer Mode Operation in Dual Address Mode (without Block Area Specified)

Table 14.15 TIORL\_0

|               |               |               |               |                                     | Description                                   |

|---------------|---------------|---------------|---------------|-------------------------------------|-----------------------------------------------|

| Bit 7<br>IOD3 | Bit 6<br>IOD2 | Bit 5<br>IOD1 | Bit 4<br>IOD0 | TGRD_0<br>Function                  | TIOCD0 Pin Function* <sup>3</sup>             |

| 0             | 0             | 0             | 0             | Output                              | Output disabled                               |

| 0             | 0             | 0             | 1             | compare<br>register* <sup>2</sup>   | Initial output is 0 output                    |

|               |               |               |               | register                            | 0 output at compare match                     |

| 0             | 0             | 1             | 0             | _                                   | Initial output is 0 output                    |

|               |               |               |               |                                     | 1 output at compare match                     |

| 0             | 0             | 1             | 1             | _                                   | Initial output is 0 output                    |

|               |               |               |               |                                     | Toggle output at compare match                |

| 0             | 1             | 0             | 0             | _                                   | Output disabled                               |

| 0             | 1             | 0             | 1             | _                                   | Initial output is 1 output                    |

|               |               |               |               |                                     | 0 output at compare match                     |

| 0             | 1             | 1             | 0             |                                     | Initial output is 1 output                    |

|               |               |               |               |                                     | 1 output at compare match                     |

| 0             | 1             | 1             | 1             |                                     | Initial output is 1 output                    |

|               |               |               |               |                                     | Toggle output at compare match                |

| 1             | 0             | 0             | 0             | Input                               | Capture input source is TIOCD0 pin            |

|               |               |               |               | capture<br>– register* <sup>2</sup> | Input capture at rising edge                  |

| 1             | 0             | 0             | 1             |                                     | Capture input source is TIOCD0 pin            |

|               |               |               |               |                                     | Input capture at falling edge                 |

| 1             | 0             | 1             | х             | _                                   | Capture input source is TIOCD0 pin            |

|               |               |               |               |                                     | Input capture at both edges                   |

| 1             | 1             | х             | х             | _                                   | Capture input source is channel 1/count clock |

|               |               |               |               |                                     | Input capture at TCNT_1 count-up/count-down*1 |

Description

### [Legend]

x: Don't care

Notes: 1. When bits TPSC2 to TPSC0 in TCR\_1 are set to B'000 and  $P\phi/1$  is used as the TCNT\_1 count clock, this setting is invalid and input capture is not generated.

- 2. When the BFB bit in TMDR\_0 is set to 1 and TGRD\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

- 3. In PWM mode 1, the IOD3 to IOD0 settings control output of the TIOCC0 pin functions.

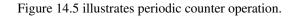

### 14.3.6 Timer Counter (TCNT)

TCNT is a 16-bit readable/writable counter. The TPU has six TCNT counters, one for each channel.

TCNT is initialized to H'0000 by a reset or in hardware standby mode.

TCNT cannot be accessed in 8-bit units. TCNT must always be accessed in 16-bit units.

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit Name      |     |     |     |     |     |     |     |     |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Bit Name      |     |     |     |     |     |     |     |     |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

# 14.3.7 Timer General Register (TGR)

TGR is a 16-bit readable/writable register with a dual function as output compare and input capture registers. The TPU has 16 TGR registers, four each for channels 0 and 3 and two each for channels 1, 2, 4, and 5. TGRC and TGRD for channels 0 and 3 can also be designated for operation as buffer registers. The TGR registers cannot be accessed in 8-bit units; they must always be accessed in 16-bit units. TGR and buffer register combinations during buffer operations are TGRA–TGRC and TGRB–TGRD.

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit Name      |     |     |     |     |     |     |     |     |

| Initial Value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Bit Name      |     |     |     |     |     |     |     |     |

| Initial Value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

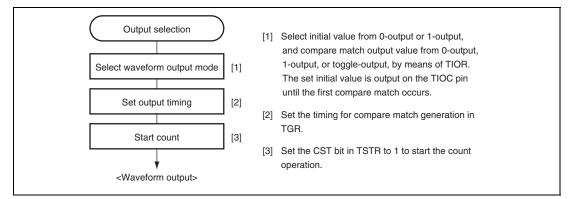

#### (2) Waveform Output by Compare Match

The TPU can perform 0, 1, or toggle output from the corresponding output pin using a compare match.

#### (a) Example of setting procedure for waveform output by compare match

Figure 14.6 shows an example of the setting procedure for waveform output by a compare match.

Figure 14.6 Example of Setting Procedure for Waveform Output by Compare Match

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                            |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | CMIEA    | 0                | R/W | Compare Match Interrupt Enable A                                                                                                                                                                       |

|     |          |                  |     | Selects whether CMFA interrupt requests (CMIA) are enabled or disabled when the CMFA flag in TCSR is set to 1. $*^2$                                                                                   |

|     |          |                  |     | 0: CMFA interrupt requests (CMIA) are disabled                                                                                                                                                         |

|     |          |                  |     | 1: CMFA interrupt requests (CMIA) are enabled                                                                                                                                                          |

| 5   | OVIE     | 0                | R/W | Timer Overflow Interrupt Enable*3                                                                                                                                                                      |

|     |          |                  |     | Selects whether OVF interrupt requests (OVI) are enabled or disabled when the OVF flag in TCSR is set to 1.                                                                                            |

|     |          |                  |     | 0: OVF interrupt requests (OVI) are disabled                                                                                                                                                           |

|     |          |                  |     | 1: OVF interrupt requests (OVI) are enabled                                                                                                                                                            |

| 4   | CCLR1    | 0                | R/W | Counter Clear 1 and 0*1                                                                                                                                                                                |

| 3   | CCLR0    | 0                | R/W | These bits select the method by which TCNT is cleared.                                                                                                                                                 |

|     |          |                  |     | 00: Clearing is disabled                                                                                                                                                                               |

|     |          |                  |     | 01: Cleared by compare match A                                                                                                                                                                         |

|     |          |                  |     | 10: Cleared by compare match B                                                                                                                                                                         |

|     |          |                  |     | <ul> <li>11: Cleared at rising edge (TMRIS in TCCR is cleared to</li> <li>0) of the external reset input or when the external reset input is high (TMRIS in TCCR is set to 1) *<sup>3</sup></li> </ul> |

| 2   | CKS2     | 0                | R/W | Clock Select 2 to 0*1                                                                                                                                                                                  |

| 1   | CKS1     | 0                | R/W | These bits select the clock input to TCNT and count                                                                                                                                                    |

| 0   | CKS0     | 0                | R/W | condition. See table 16.2.                                                                                                                                                                             |

Notes: 1. To use an external reset or external clock, the DDR and ICR bits in the corresponding pin should be set to 0 and 1, respectively. For details, see section 13, I/O Ports.

2. In unit 2 and unit 3, one interrupt signal is used for CMIEB or CMIEA. For details, see section 16.7, Interrupt Sources.

3. Available only in unit 0 and unit 1.

### 19.3.11 Serial Extended Mode Register 5 and 6 (SEMR\_5 and SEMR\_6)

SEMR\_5 and SEMR\_6 select the clock source in asynchronous mode of SCI\_5 and SCI\_6. The base clock is automatically specified when the average transfer rate operation is selected. TMO output in TMR unit 2 and unit 3 can also be set as the serial transfer base clock. Figure 19.3 describes the examples of base clock features when the average transfer rate operation is selected. Figure 19.4 describes the examples of base clock features when the TMO output in TMR is selected.

| Bit        | 7             | 6         | 5         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3            | 2             | 1           | 0                |

|------------|---------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-------------|------------------|

| Bit Nam    | e —           | _         | _         | ABCS ACS3 ACS2 ACS1 ACS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |               |             |                  |

| Initial Va | lue Undefined | Undefined | Undefined | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0            | 0             | 0           | 0                |

| R/W        | R             | R         | R         | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W          | R/W           | R/W         | R/W              |

|            |               | Initial   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |               |             |                  |

| Bit        | Bit Name      | Value     | R/W       | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | n            |               |             |                  |

| 7 to 5     | _             | Undefined | R         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |               |             |                  |

|            |               |           |           | These bits modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | are always   | read as ur    | ndefined ar | nd cannot be     |

| 4          | ABCS          | 0         | R/W       | Asynchrono<br>asynchrono                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | Base Clock    | Select (va  | lid only in      |

|            |               |           |           | Selects the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | base cloci   | k for a 1-bit | t period.   |                  |

|            |               |           |           | 0: The base<br>rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e clock has  | a frequen     | cy 16 times | the transfer     |

|            |               |           |           | 1: The base<br>rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e clock has  | a frequen     | cy 8 times  | the transfer     |

| 3          | ACS3          | 0         | R/W       | Asynchron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ous Mode (   | Clock Sour    | ce Select   |                  |

| 2          | ACS2          | 0         | R/W       | These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |               |             |                  |

| 1          | ACS1          | 0         | 11/ • •   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |               |             | node. When       |

| 0          | ACS0          | 0         | R/W       | the average transfer rate function is enabled, the base clock is automatically specified regardless of the ABCS bit value. The average transfer rate only corresponds to 8MHz, 10.667MHz, 12MHz, 16MHz, 24MHz, and 32MHz. No other clock is available. Setting of ACS3 to ACS0 must be done in the asynchronous mode (the $C/\overline{A}$ bit in SMR = 0) and the external clock input mode (the CKE bit I SCR = 1). The setting examples are in figures 19.3 and 19.4. (Each number in the four-digit number below |              |               |             |                  |

|            |               |           |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ls to the va | lue in the b  |             | w<br>o ACS0 from |

# 20.3.5 Interrupt Select Register 1 (ISR1)

ISR1 selects the vector numbers of the interrupt requests indicated in interrupt flag register 1 (IFR1). If the USB issues an interrupt request to the INTC when a bit in ISR1 is cleared to 0, the interrupt corresponding to the bit will be USBINTN2. If the USB issues an interrupt request to the INTC when a bit in ISR1 is set to 1, the corresponding interrupt will be USBINTN3.

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     |

|---------------|---|---|---|---|---|--------|--------|-------|

| Bit Name      | _ | — | — | — | — | EP3 TR | EP3 TS | VBUSF |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 1      | 1      | 1     |

| R/W           | R | R | R | R | R | R/W    | R/W    | R/W   |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                      |

|-----|----------|------------------|-----|--------------------------------------------------|

| 7   | _        | 0                | R   | Reserved                                         |

| 6   |          | 0                | R   | These bits are always read as 0. The write value |

| 5   |          | 0                | R   | should always be 0.                              |

| 4   | _        | 0                | R   |                                                  |

| 3   |          | 0                | R   |                                                  |

| 2   | EP3 TR   | 1                | R/W | EP3 Transfer Request                             |

| 1   | EP3 TS   | 1                | R/W | EP3 Transmission Complete                        |

| 0   | VBUSF    | 1                | R/W | USB Bus Connect                                  |

# (b) Programming

FPFR indicates the return value of the programming result.

| Bit     |          | 7                | 6  | 5                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                   | 2                                                     | 1                                        | 0                                                                              |  |

|---------|----------|------------------|----|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|--|

| Bit Nar | Bit Name |                  | MD | EE                                  | FK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                   | WD                                                    | WA                                       | SF                                                                             |  |

| Bit     | Bit N    | Init<br>Name Val |    | W D                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |                                                       |                                          |                                                                                |  |

| 7       | —        | _                | _  | - U                                 | nused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                                                       |                                          |                                                                                |  |

|         |          |                  |    | R                                   | eturns 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |                                                       |                                          |                                                                                |  |

| 6       | MD       | _                | R/ | W P                                 | rogrammin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | g Mode R                                            | elated Set                                            | ting Error I                             | Detect                                                                         |  |

|         |          |                  |    | W<br>to<br>ca<br>co                 | hen the er<br>1. Whethe<br>an be confi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ror protec<br>er the erro<br>rmed with<br>enter the | tion state i<br>r protectio<br>the FLER<br>error prot | s entered,<br>n state is e<br>bit in FCC | ns the result.<br>this bit is set<br>entered or not<br>S. For<br>e see section |  |

|         |          |                  |    | 0:                                  | Normal op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | peration (F                                         | ELER = 0                                              |                                          |                                                                                |  |

|         |          |                  |    | 1:                                  | Error prote<br>performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |                                                       | gramming                                 | cannot be                                                                      |  |

| 5       | EE       | —                | R/ | W P                                 | rogrammin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | g Executio                                          | on Error D                                            | etect                                    |                                                                                |  |

|         |          |                  |    | w<br>is<br>ha<br>th<br>H<br>w<br>us | Writes 1 to this bit when the specified data could not be<br>written because the user MAT was not erased. If this bit<br>is set to 1, there is a high possibility that the user MAT<br>has been written to partially. In this case, after removing<br>the error factor, erase the user MAT. If FMATS is set to<br>H'AA and the user boot MAT is selected, an error occurs<br>when programming is performed. In this case, both the<br>user MAT and user boot MAT have not been written to.<br>Programming the user boot MAT should be performed in<br>boot mode or programmer mode. |                                                     |                                                       |                                          |                                                                                |  |

|         |          |                  |    | 0:                                  | Programm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ning has e                                          | nded norn                                             | nally                                    |                                                                                |  |

|         |          |                  |    | 1:                                  | Programm<br>result is n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |                                                       | ormally (pr                              | ogramming                                                                      |  |

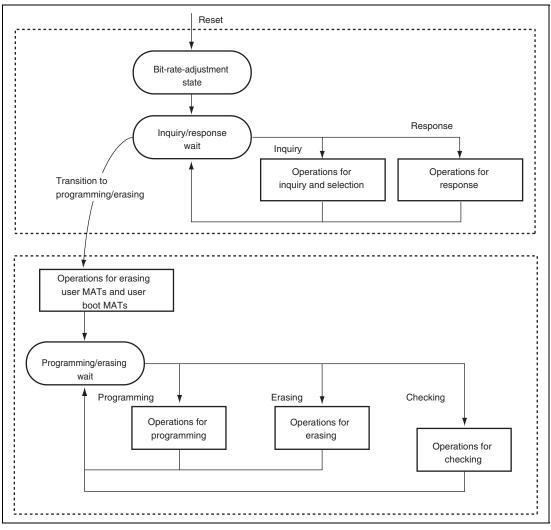

3. Programming/erasing state

Programming and erasure by the boot program take place in this state. The boot program is made to transfer the programming/erasing programs to the on-chip RAM by commands from the host. Sum checks and blank checks are executed by sending these commands from the host.

These boot program states are shown in figure 25.23.

Figure 25.23 Boot Program States

- 12. A programming/erasing program for the flash memory used in a conventional F-ZTAT H8, H8S microcomputer which does not support download of the on-chip program by setting the SCO bit in FCCS to 1 cannot run in this LSI. Be sure to download the on-chip program to execute programming/erasure of the flash memory in this F-ZTAT H8SX microcomputer.

- 13. Unlike a conventional F-ZTAT H8 or H8S microcomputers, measures against a program crash are not taken by WDT while programming/erasing and downloading a programming/erasing program. When needed, measures should be taken by user. A periodic interrupt generated by the WDT can be used as the measures, as an example. In this case, the interrupt generation period should take into consideration time to program/erase the flash memory.

- 14. When downloading the programming/erasing program, do not clear the SCO bit in FCCS to 0 immediately after setting it to 1. Otherwise, download cannot be performed normally. Immediately after executing the instruction to set the SCO bit to 1, dummy read of the FCCS must be executed twice.

- 15. The contents of general registers ER0 and ER1 are not saved during download of an on-chip program, initialization, programming, or erasure. When needed, save the general registers before a download request or before execution of initialization, programming, or erasure using the procedure program.

Note: \* The oscillation settling time, which includes a period where the oscillation by an oscillator is not stable, depends on the resonator characteristics. The above figures are for reference.

### 28.8.6 Deep Software Standby Mode Application Example

#### (1) Transition to and Exit from Deep Software Standby Mode

Figure 28.4 shows an example where the transition to deep software standby mode is initiated by a falling edge on the NMI pin and exit from deep software standby mode is initiated by a rising edge on the NMI pin.

In this example, falling-edge sensing of NMI interrupts has been specified by clearing the NMIEG bit in INTCR to 0 (not shown). After an NMI interrupt has been sensed, rising-edge sensing is specified by setting the DNMIEG bit to 1, the SSBY and DPSBY bits are set to 1, and the transition to deep software standby mode is triggered by execution of a SLEEP instruction.

After that, deep software standby mode is canceled at the rising edge on the NMI pin.

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--------|

| SSR_0*1                  | TDRE              | RDRF              | ORER              | FER<br>(ERS)      | PER               | TEND              | MPB              | MPBT             | SCI_0  |

| RDR_0                    |                   |                   |                   |                   |                   |                   |                  |                  | _      |

| SCMR_0                   | _                 | _                 | _                 | _                 | SDIR              | SINV              | _                | SMIF             | -      |

| SMR_1*1                  | C/Ā<br>(GM)       | CHR<br>(BLK)      | PE<br>(PE)        | O/Ē<br>(O/Ē)      | STOP<br>(BCP1)    | MP<br>(BCP0)      | CKS1             | CKS0             | SCI_1  |

| BRR_1                    |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| SCR_1*1                  | TIE               | RIE               | TE                | RE                | MPIE              | TEIE              | CKE1             | CKE0             | -      |

| TDR_1                    |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| SSR_1*1                  | TDRE              | RDRF              | ORER              | FER<br>(ERS)      | PER               | TEND              | MPB              | MPBT             | _      |

| RDR_1                    |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| SCMR_1                   | _                 | _                 | _                 | _                 | SDIR              | SINV              | _                | SMIF             | -      |

| ADDRA_0                  | _                 |                   |                   |                   |                   |                   |                  |                  | A/D_0  |

| ADDRB_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRC_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRD_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRE_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRF_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRG_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| ADDRH_0                  |                   |                   |                   |                   |                   |                   |                  |                  | -      |

| Item                                      | Page       | e Revision (See Manual for Details)                                                                                                                        |  |  |  |  |

|-------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Section 22 A/D                            | 1082       | Note amended                                                                                                                                               |  |  |  |  |

| Converter                                 |            | (1) Continuous Scan Mode                                                                                                                                   |  |  |  |  |

| 22.4 Operation                            |            |                                                                                                                                                            |  |  |  |  |

| 22.4.2 Scan Mode                          |            | Notes: 1. Only possible in unit 0.                                                                                                                         |  |  |  |  |

|                                           |            | <ol> <li>As conversion start trigger, units 0 and 1 of TMR, and<br/>units 2 and 3 of TMR are available in unit 0, and unit<br/>1, respectively.</li> </ol> |  |  |  |  |

|                                           |            | <ol> <li>Unit 0: The full-spec emulator (E6000H) should not be<br/>used, but the on-chip emulator (E10A-USB) is usable.</li> </ol>                         |  |  |  |  |

| 22.4.3 Input Sampling                     | 1086       | The following tables replaced                                                                                                                              |  |  |  |  |

| and A/D Conversion<br>Time                | to<br>1088 | Table 22.3 Characteristics of A/D Conversion (Unit 0: when EXCKS* = 0, ICKSEL = 0, and $ADSSTR^* = H'0F$ ) (1)                                             |  |  |  |  |

|                                           |            | Table 22.3 Characteristics of A/D Conversion (Unit 0: when EXCKS* = 1, ICKSEL = 0, and $ADSSTR^* = H'0F$ ) (2)                                             |  |  |  |  |

|                                           |            | Table 22.4 Characteristics of A/D Conversion (Unit 1: when EXCKS = 0, ICKSEL = 0, and ADSSTR* = H'0F) (1)                                                  |  |  |  |  |

|                                           |            | Table 22.4 Characteristics of A/D Conversion (Unit 1: when EXCKS = 1, ICKSEL = 0, and $ADSSTR^* = H'0F$ ) (2)                                              |  |  |  |  |

|                                           |            | Table 22.5 Characteristics of A/D Conversion (When EXCKS* <sup>1</sup> : 1, ICKSEL* <sup>1</sup> = 0, and ADSSTR* <sup>2</sup> = H'19)                     |  |  |  |  |

| Table 22.6 Period of A/D                  |            | Note deleted                                                                                                                                               |  |  |  |  |

| Conversion (Scan Mode)<br>(Units 0 and 1) |            | Notes: 1. Make the sampling setting15 (ADSSRT = D'15).                                                                                                     |  |  |  |  |

|                                           |            | 2. When $P\phi = I\phi/2$ , make the sampling setting 25 (ADSSRT = D'25).                                                                                  |  |  |  |  |

|                                           |            | <ol> <li>Unit 0: The full-spec emulator (E6000H) should not be<br/>used, but the on-chip emulator (E10A-USB) is usable.</li> </ol>                         |  |  |  |  |

|                                           |            | <ol> <li>Unit 0: The full spee emulator (E6000H) should not be<br/>used, but the on chip emulator (E10A USB) is usable.</li> </ol>                         |  |  |  |  |

|                                           |            | Unit 1: Access to the full-spec emulator (E6000H) is prohibited but the on-chip emulator (E10A-USB) is usable.                                             |  |  |  |  |