Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                             |

| Core Processor             | H8SX                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SmartCard, USB                            |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 92                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 40K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 145-TFLGA                                                                       |

| Supplier Device Package    | 145-TFLGA (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f61665n50lgv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.3.2 Reset Control/Status Register (RSTCSR)

RSTCSR controls an internal reset signal generated by the watchdog timer and selects the internal reset signal type. RSTCSR is initialized to H'1F by a pin reset or a deep software standby reset, but not by the internal reset signal generated by a WDT overflow.

| Bit            | 7      | 6    | 5   | 4 | 3 | 2 | 1 | 0 |

|----------------|--------|------|-----|---|---|---|---|---|

| Bit name       | WOVF   | RSTE | _   | — | — | — | — | — |

| Initial value: | 0      | 0    | 0   | 1 | 1 | 1 | 1 | 1 |

| R/W:           | R/(W)* | R/W  | R/W | R | R | R | R | R |

Note: \* Only 0 can be written to clear the flag.

|        |            | Initial  |              |                                                                                                                                                                   |

|--------|------------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name   | Value    | R/W          | Description                                                                                                                                                       |

| 7      | WOVF       | 0        | R/(W)*       | Watchdog Timer Overflow Flag                                                                                                                                      |

|        |            |          |              | This bit is set when TCNT overflows in watchdog timer mode,<br>but not set in interval timer mode. Only 0 can be written to.                                      |

|        |            |          |              | [Setting condition]                                                                                                                                               |

|        |            |          |              | When TCNT overflows (H'FF $\rightarrow$ H'00) in watchdog timer mode.                                                                                             |

|        |            |          |              | [Clearing condition]                                                                                                                                              |

|        |            |          |              | When this bit is read as 1 and then written by 0.                                                                                                                 |

| 6      | RSTE       | 0        | R/W          | Reset Enable                                                                                                                                                      |

|        |            |          |              | Selects whether or not the LSI internal state is reset by a TCNT overflow in watchdog timer mode.                                                                 |

|        |            |          |              | <ol> <li>Internal state is not reset when TCNT overflows. (Although<br/>this LSI internal state is not reset, TCNT and TCSR of the<br/>WDT are reset.)</li> </ol> |

|        |            |          |              | 1: Internal state is reset when TCNT overflows.                                                                                                                   |

| 5      |            | 0        | R/W          | Reserved                                                                                                                                                          |

|        |            |          |              | Although this bit is readable/writable, operation is not affected by this bit.                                                                                    |

| 4 to 0 |            | 1        | R            | Reserved                                                                                                                                                          |

|        |            |          |              | These are read-only bits but cannot be modified.                                                                                                                  |

| Note:  | * Only 0 ( | ran ho w | ritten to cl | ear the flag                                                                                                                                                      |

Note: \* Only 0 can be written to clear the flag.

## (3) Refresh and All-Module Clock Stop Mode

This LSI is entered in all-module clock stop mode by the following operation: Stop the clocks of all on-chip peripheral modules by setting the ACSE bit in MSTPCR to 1 (MSTPCRA, MSTPCRB = H'FFFFFFF) or run only the 8-bit timer (MSTPCRA, MSTPCRB = H'F[C to F]FFFFFF), then execute the SLEEP instruction to enter the sleep mode.

In all-module clock stop mode, clocks for the bus controller and I/O ports are stopped. Since the clock for the bus controller is stopped, a CBR refresh cycle cannot be performed. When external DRAM is used and the contents of the DRAM in sleep mode should be held, clear the ACSE bit in MSTPCE to 0.

For details, see section 28.2.2, Module Stop Control Registers A and B (MSTPCRA and MSTPCRB).

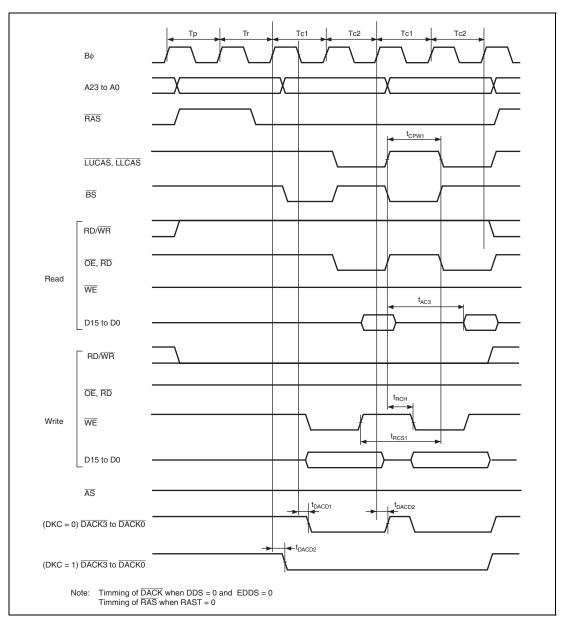

## 9.10.13 DRAM Interface and Single Address Transfer by DMAC and EXDMAC

When fast-page mode (BE = 1) is set for the DRAM space, either fast-page access or full access can be selected, by the setting of bits DDS and EDDS in DRAMCR, for the single address transfer by the DMAC or EXDMAC where the DRAM space is specified as the transfer source or destination. At the same time, the output timings of the DACK, EDACK and BS signals are changed. When BE = 0, full access to the DRAM space is performed by single address transfer regardless of the setting of bits DDS and EDDS. However, the output timing of the DACK, EDACK and BS signals can be changed by the setting of bits DDS and EDDS.

The assertion timing of the  $\overline{DACK}$  and  $\overline{EDACK}$  signal can be changed by bits DKC and EDKC in BCR1.

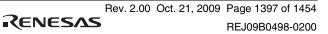

Figure 9.73 Word Read Timing in 8-Bit Access Space (BE = 1, RCDM = 0, CAS Latency = 2)

## 9.15.2 Write Data Buffer Function for Peripheral Modules

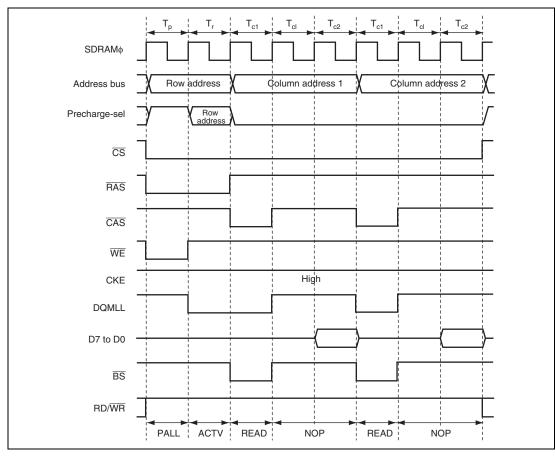

This LSI has a write data buffer function for the peripheral module access. Using the write data buffer function enables peripheral module writes and on-chip memory or external access to be executed in parallel. The write data buffer function is made available by setting the PWDBE bit in BCR2 to 1. For details on the on-chip peripheral module registers, see table 9.34, Number of Access Cycles for Registers of On-Chip Peripheral Modules in section 9.14, Internal Bus.

Figure 9.105 shows an example of the timing when the write data buffer function is used. When this function is used, if an internal I/O register write continues for two cycles or longer and then there is an on-chip RAM, an on-chip ROM, or an external access, internal I/O register write only is performed in the first two cycles. However, from the next cycle onward an internal memory or an external access and internal I/O register write are executed in parallel rather than waiting until it ends.

Figure 9.105 Example of Timing when Peripheral Module Write Data Buffer Function is Used

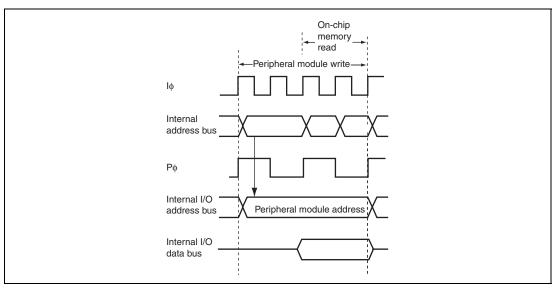

## (3) **EDREQ** Pin Low Level Activation Timing

Figure 11.63 shows an example of cluster transfer mode transfer activated by the  $\overline{\text{EDREQ}}$  pin low level.

$\overline{\text{EDREQ}}$  pin sampling is performed in each cycle starting at the next rise of B $\phi$  after the end of the DTE bit write cycle.

When a low level is sampled at the  $\overline{\text{EDREQ}}$  pin while acceptance of a transfer request via the  $\overline{\text{EDREQ}}$  pin is possible, the request is held within the EXDMAC. Then when activation is initiated within the EXDMAC, the request is cleared. At the end of the last cluster write cycle, acceptance resumes and  $\overline{\text{EDREQ}}$  pin low level sampling is performed again. This sequence of operations is repeated until the end of the transfer.

When NRD bit = 0 in EDMDR, acceptance resumes at the end of the last cluster write cycle and  $\overline{\text{EDREQ}}$  pin low level sampling is performed again. This sequence of operations is repeated until the end of the transfer.

When NRD bit = 1 in EDMDR, acceptance resumes after one cycle from the end of the last cluster write cycle, and  $\overline{\text{EDREQ}}$  pin low level sampling is performed again. This sequence of operations is repeated until the end of the transfer.

Figure 11.63 Example of Cluster Transfer Mode Transfer Activated by EDREQ Pin Low Level

RENESAS

| Port |   | Output<br>Specification<br>Signal Name | Output<br>Signal<br>Name | Signal Selection<br>Register Settings | Peripheral Module Settings                                            |

|------|---|----------------------------------------|--------------------------|---------------------------------------|-----------------------------------------------------------------------|

| PA   | 1 | BACK_OE                                | BACK                     |                                       | SYSCR.EXPE = 1,BCR1.BRLE = 1                                          |

|      |   | (RD/WR-<br>A)_OE                       | RD/WR                    | PFCR2.RDWRS = 0                       | SYSCR.EXPE = 1, PFCR2.RDWRE = 1 or<br>SRAMCR.BCSELn = 1               |

|      | 0 | BSA_OE                                 | BS                       | PFCR2.BSS = 0                         | SYSCR.EXPE = 1, PFCR2.BSE = 1                                         |

|      |   | BREQO_OE                               | BREQO                    |                                       | SYSCR.EXPE = 1, BCR1.BRLE = 1,<br>BCR1.BREQOE = 1                     |

| PB   | 7 | SDRAMø_OE                              | SDRAMø                   |                                       | MDCR.MDS7 = 1                                                         |

|      | 6 | (RD/WR)-B_OE                           | RD/WR                    | PFCR2.RDWRS = 1                       | SYSCR.EXPE=1, PFCR2.RDWRE = 1 or<br>ASRAMCR.BCSELn = 1                |

|      |   | CS6D_OE                                | CS6                      | PFCR1.CS6S[A,B] =<br>11               | SYSCR.EXPE = 1, PFCR0.CS6E = 1                                        |

|      | 5 | CKE_OE                                 | CKE                      |                                       | SYSCR.EXPE = 1, DRAMCR.DRAME = 1,<br>DRAMCR.DTYPE = 1, DRAMCR.OEE = 1 |

|      |   | OE_OE                                  | ŌĒ                       |                                       | SYSCR.EXPE = 1, DRAMCR.DRAME = 1,<br>DRAMCR.DTYPE = 0, DRAMCR.OEE = 1 |

|      |   | CS5D_OE                                | CS5                      | PFCR1.CS5S[A,B] =<br>11               | SYSCR.EXPE = 1, PFCR0.CS5E = 1                                        |

|      | 4 | WE_OE                                  | WE                       |                                       | SYSCR.EXPE = 1, DRAMCR.DRAME = 1                                      |

|      |   | CS4B_OE                                | CS4                      | PFCR1.CS4S[A,B] =<br>01               | SYSCR.EXPE = 1, PFCR0.CS4E = 1                                        |

|      | 3 | CAS_OE                                 | CAS                      |                                       | SYSCR.EXPE = 1, DRAMCR.DRAME = 1,<br>DRAMCR.DTYPE = 1                 |

|      |   | CS3_OE                                 | CS3                      |                                       | SYSCR.EXPE = 1, PFCR0.CS3E = 1                                        |

|      |   | CS7A_OE                                | CS7                      | PFCR1.CS7S[A,B] = 00                  | SYSCR.EXPE = 1, PFCR0.CS7E = 1                                        |

|      | 2 | RAS_OE                                 | RAS                      |                                       | SYSCR.EXPE = 1, DRAMCR.DRAME = 1                                      |

|      |   | CS2A_OE                                | CS2                      | PFCR2.CS2S = 0                        | SYSCR.EXPE = 1, PFCR0.CS2E = 1                                        |

|      |   | CS6A_OE                                | CS6                      | PFCR1.CS6S[A,B] =<br>00               | SYSCR.EXPE = 1, PFCR0.CS6E = 1                                        |

RENESAS

## 13.3.10 Port Function Control Register B (PFCRB)

PFCRB selects the LVD interrupt\*, and the input pins for IRQ11 to IRQ8.

| Bit           | 7   | 6      | 5   | 4   | 3     | 2     | 1    | 0    |

|---------------|-----|--------|-----|-----|-------|-------|------|------|

| Bit Name      |     | ITS14* | _   | _   | ITS11 | ITS10 | ITS9 | ITS8 |

| Initial Value | 0   | 0      | 0   | 0   | 0     | 0     | 0    | 0    |

| R/W           | R/W | R/W    | R/W | R/W | R/W   | R/W   | R/W  | R/W  |

Note: \* Supported only by the H8SX/1665M Group.

### • H8SX/1665 Group

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------|

| 7 to 4 | _        | All 0            | R/W | Reserved                                                             |

| _      |          |                  |     | These bits are always read as 0. The write value should always be 0. |

#### • H8SX/1665M Group

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                          |

|------|----------|------------------|-----|----------------------------------------------------------------------|

| 7    | _        | 0                | R/W | Reserved                                                             |

|      |          |                  |     | This bit is always read as 0. The write value should always be 0.    |

| 6    | ITS14    | 0                | R/W | LVD Interrupt Select                                                 |

|      |          |                  |     | This bit allows or prohibits LVD interrupt.                          |

|      |          |                  |     | 0: Prohibits LVD interrupt                                           |

|      |          |                  |     | 1: Allows LVD interrupt                                              |

| 5, 4 |          | All 0            | R/W | Reserved                                                             |

|      |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 3    | ITS11    | 0                | R/W | IRQ11 Pin Select                                                     |

|      |          |                  |     | Selects an input pin for IRQ11.                                      |

|      |          |                  |     | 0: Selects pin P23 as IRQ11-A input                                  |

|      |          |                  |     | 1: Selects pin P63 as IRQ11-B input                                  |

| Item                            | Channel 0                                                    | Channel 1                                                    | Channel 2                                                    | Channel 3                                                    | Channel 4                                         | Channel 5                                         |

|---------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| DMAC activation                 | TGRA_0<br>compare<br>match or<br>input<br>capture            | TGRA_1<br>compare<br>match or<br>input<br>capture            | TGRA_2<br>compare<br>match or<br>input<br>capture            | TGRA_3<br>compare<br>match or<br>input<br>capture            | TGRA_4<br>compare<br>match or<br>input<br>capture | TGRA_5<br>compare<br>match or<br>input<br>capture |

| A/D conversion start<br>trigger | TGRA_0<br>compare<br>match or<br>input<br>capture            | TGRA_1<br>compare<br>match or<br>input<br>capture            | TGRA_2<br>compare<br>match or<br>input<br>capture            | TGRA_3<br>compare<br>match or<br>input<br>capture            | TGRA_4<br>compare<br>match or<br>input<br>capture | TGRA_5<br>compare<br>match or<br>input<br>capture |

| PPG trigger                     | TGRA_0/<br>TGRB_0<br>compare<br>match or<br>input<br>capture | TGRA_1/<br>TGRB_1<br>compare<br>match or<br>input<br>capture | TGRA_2/<br>TGRB_2<br>compare<br>match or<br>input<br>capture | TGRA_3/<br>TGRB_3<br>compare<br>match or<br>input<br>capture |                                                   | _                                                 |

| Interrupt sources               | 5 sources                                                    | 4 sources                                                    | 4 sources                                                    | 5 sources                                                    | 4 sources                                         | 4 sources                                         |

|                                 | Compare<br>match or<br>input<br>capture 0A                   | Compare<br>match or<br>input<br>capture 1A                   | Compare<br>match or<br>input<br>capture 2A                   | Compare<br>match or<br>input<br>capture 3A                   | Compare<br>match or<br>input<br>capture 4A        | Compare<br>match or<br>input<br>capture 5A        |

|                                 | Compare<br>match or<br>input<br>capture 0B                   | Compare<br>match or<br>input<br>capture 1B                   | Compare<br>match or<br>input<br>capture 2B                   | Compare<br>match or<br>input<br>capture 3B                   | Compare<br>match or<br>input<br>capture 4B        | Compare<br>match or<br>input<br>capture 5B        |

|                                 | Compare<br>match or<br>input<br>capture 0C                   |                                                              |                                                              | Compare<br>match or<br>input<br>capture 3C                   |                                                   |                                                   |

|                                 | Compare<br>match or<br>input<br>capture 0D                   |                                                              |                                                              | Compare<br>match or<br>input<br>capture 3D                   |                                                   |                                                   |

|                                 | Overflow                                                     | Overflow                                                     | Overflow                                                     | Overflow                                                     | Overflow                                          | Overflow                                          |

|                                 |                                                              | Underflow                                                    | Underflow                                                    |                                                              | Underflow                                         | Underflow                                         |

[Legend]

O: Possible

--: Not possible

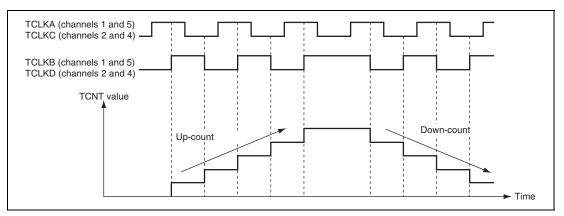

## (2) Examples of Phase Counting Mode Operation

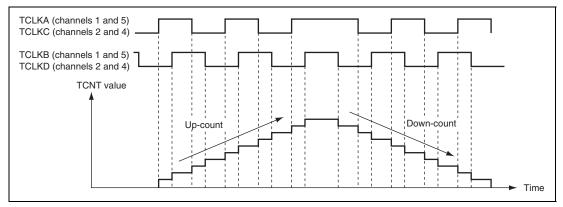

In phase counting mode, TCNT counts up or down according to the phase difference between two external clocks. There are four modes, according to the count conditions.

#### (a) Phase counting mode 1

Figure 14.26 shows an example of phase counting mode 1 operation, and table 14.34 summarizes the TCNT up/down-count conditions.

Figure 14.26 Example of Phase Counting Mode 1 Operation

#### Table 14.34 Up/Down-Count Conditions in Phase Counting Mode 1

| TCLKA (Channels 1 and 5)<br>TCLKC (Channels 2 and 4) | TCLKB (Channels 1 and 5)<br>TCLKD (Channels 2 and 4) | Operation  |

|------------------------------------------------------|------------------------------------------------------|------------|

| High level                                           | _                                                    | Up-count   |

| Low level                                            | T.                                                   |            |

| <u> </u>                                             | Low level                                            |            |

| ₹.                                                   | High level                                           |            |

| High level                                           | Ť.                                                   | Down-count |

| Low level                                            | _                                                    |            |

| <u> </u>                                             | High level                                           |            |

| ₹.                                                   | Low level                                            |            |

| [Legend]<br>. Isising edge                           |                                                      |            |

RENESAS

L: Falling edge

## (d) Phase counting mode 4

Figure 14.29 shows an example of phase counting mode 4 operation, and table 14.37 summarizes the TCNT up/down-count conditions.

| Table 14.37 | Up/Down-Count | <b>Conditions in</b> | Phase | Counting Mode 4 |

|-------------|---------------|----------------------|-------|-----------------|

|-------------|---------------|----------------------|-------|-----------------|

| TCLKA (Channels 1 and 5)<br>TCLKC (Channels 2 and 4) | TCLKB (Channels 1 and 5)<br>TCLKD (Channels 2 and 4) | Operation  |

|------------------------------------------------------|------------------------------------------------------|------------|

| High level                                           | _ <b>_</b>                                           | Up-count   |

| Low level                                            | T.                                                   |            |

| <u> </u>                                             | Low level                                            | Don't care |

| ₹_                                                   | High level                                           |            |

| High level                                           | T.                                                   | Down-count |

| Low level                                            | _ <b>_</b>                                           |            |

| <u> </u>                                             | High level                                           | Don't care |

| ₹.                                                   | Low level                                            |            |

| [legend]                                             |                                                      |            |

[Legend]

: Rising edge

L: Falling edge

Table 19.1 lists the functions of each channel.

|                                    |                          | SCI_0, 1, 4 | SCI_2        | SCI_5, SCI_6 |  |

|------------------------------------|--------------------------|-------------|--------------|--------------|--|

| Clocked synchronous mode           |                          | 0           | 0            | —            |  |

| Asynchronous mode                  |                          | 0           | 0            | 0            |  |

| TMR clock input                    |                          | —           | _            | 0            |  |

| When average                       | $P\phi = 8 MHz$          | —           | _            | 460.784 kbps |  |

| transfer rate<br>generator is used | Pφ = 10.667              | _           | 460.784 kbps | 460.606 kbps |  |

| generator is used                  | MHz                      |             | 115.192 kbps | 115.152 kbps |  |

|                                    | $P\phi = 12 \text{ MHz}$ |             | _            | 460.526 kbps |  |

|                                    |                          |             |              | 230.263 kbps |  |

|                                    | $P\phi = 16 \text{ MHz}$ |             | 720 kbps     | 921.569 kbps |  |

|                                    |                          |             | 460 784kbps  | 720 kbps     |  |

|                                    |                          |             | 115.192 kbps | 460.784 kbps |  |

|                                    |                          |             |              | 115.196 kbps |  |

|                                    | $P\phi = 24 \text{ MHz}$ | _           | _            | 921.053 kbps |  |

|                                    |                          |             |              | 720 kbps     |  |

|                                    |                          |             |              | 460.526 kbps |  |

|                                    |                          |             |              | 115.132 kbps |  |

|                                    | $P\phi = 32 \text{ MHz}$ |             | 720 kbps     | 720 kbps     |  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3   | ACS3     | 0                | R/W | 0000: Average transfer rate generator is not used.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 2   | ACS2     | 0                | R/W | 0001: 115.152 kbps of average transfer rate specific to $P\phi = 10.667$ MHz is selected (operated using the base clock with a frequency 16 times the transfer                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 1   | ACS1     | 0                | R/W |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 0   | ACS0     | 0                | R/W | rate)                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|     |          |                  |     | <ul> <li>0010: 460.606 kbps of average transfer rate specific to Pφ = 10.667 MHz is selected (operated using the base clock with a frequency 8 times the transfer rate)</li> <li>0011: 921.569 kbps of average transfer rate specific to Pφ = 16 MHz is selected or 460.784 kbps of average transfer rate specific to Pφ = 8MHz is selected (operated using the base clock with a frequency 8 times the transfer rate)</li> </ul> |  |  |  |  |  |  |

|     |          |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|     |          |                  |     | 0100: TMR clock input<br>This setting allows the TMR compare match output<br>to be used as the base clock. The table below<br>shows the correspondence between the SCI<br>channels and the compare match output.                                                                                                                                                                                                                  |  |  |  |  |  |  |

|     |          |                  |     | Compare Match<br>SCI Channel TMR Unit Output                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|     |          |                  |     | SCI_5 Unit 2 TMO4, TMO5                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|     |          |                  |     | SCI_6 Unit 3 TMO6, TMO7                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|     |          |                  |     | 0101: 115.196 kbps of average transfer rate specific to<br>$P\phi = 16 \text{ MHz}$ is selected (operated using the base<br>clock with a frequency 16 times the transfer rate)                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|     |          |                  |     | 0110: 460.784 kbps of average transfer rate specific to $P\phi = 16$ MHz is selected (operated using the base clock with a frequency 16 times the transfer rate)                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|     |          |                  |     | 0111: 720 kbps of average transfer rate specific to $P\phi =$<br>16 MHz is selected (operated using the base clock<br>with a frequency 8 times the transfer rate)                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

## 20.3.6 Interrupt Select Register 2 (ISR2)

ISR2 selects the vector numbers of the interrupt requests indicated in interrupt flag register 2 (IFR2). If the USB issues an interrupt request to the INTC when a bit in ISR2 is cleared to 0, the interrupt corresponding to the bit will be USBINTN2. If the USB issues an interrupt request to the INTC when a bit in ISR2 is set to 1, the corresponding interrupt will be USBINTN3.

| Bit           | 7 | 6 | 5 | 4     | 3    | 2 | 1     | 0     |

|---------------|---|---|---|-------|------|---|-------|-------|

| Bit Name      | — | — | _ | SURSE | CFDN | — | SETCE | SETIE |

| Initial Value | 0 | 0 | 0 | 1     | 1    | 1 | 1     | 1     |

| R/W           | R | R | R | R/W   | R/W  | R | R/W   | R/W   |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |  |  |  |

|-----|----------|------------------|-----|-------------------------------------------------------------------|--|--|--|

| 7   | _        | 0                | R   | Reserved                                                          |  |  |  |

| 6   | _        | 0                | R   | These bits are always read as 0. The write value                  |  |  |  |

| 5   | —        | 0                | R   | should always be 0.                                               |  |  |  |

| 4   | SURSE    | 1                | R/W | Suspend/Resume Detection                                          |  |  |  |

| 3   | CFDN     | 1                | R/W | End Point Information Load End                                    |  |  |  |

| 2   | —        | 1                | R   | Reserved                                                          |  |  |  |

|     |          |                  |     | This bit is always read as 1. The write value should always be 1. |  |  |  |

| 1   | SETCE    | 1                | R/W | Set_Configuration Command Detection                               |  |  |  |

| 0   | SETIE    | 1                | R/W | Set_Interface Command Detection                                   |  |  |  |

# Section 21 I<sup>2</sup>C Bus Interface 2 (IIC2)

This LSI has a two-channel I<sup>2</sup>C bus interface.

The I<sup>2</sup>C bus interface conforms to and provides a subset of the Philips I<sup>2</sup>C bus (inter-IC bus) interface functions. The register configuration that controls the I<sup>2</sup>C bus differs partly from the Philips configuration, however.

Figure 21.1 shows the block diagram of the  $I^2C$  bus interface 2.

Figure 21.2 shows an example of I/O pin connections to external circuits.

## 21.1 Features

- Continuous transmission/reception Since the shift register, transmit data register, and receive data register are independent from each other, the continuous transmission/reception can be performed.

- Start and stop conditions generated automatically in master mode

- Selection of acknowledge output levels when receiving

- Automatic loading of acknowledge bit when transmitting

- Bit synchronization/wait function

In master mode, the state of SCL is monitored per bit, and the timing is synchronized automatically. If transmission or reception is not yet possible, drive the SCL signal low until preparations are completed

• Six interrupt sources

Transmit-data-empty (including slave-address match), transmit-end, receive-data-full (including slave-address match), arbitration lost, NACK detection, and stop condition detection

• Direct bus drive

Two pins, the SCL and SDA pins function as NMOS open-drain outputs.

• Module stop state can be set.

|     |          | Initial |     |                                                                                                                                                            |

|-----|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                |

| 5   | RDRF     | 0       | R/W | Receive Data Register Full                                                                                                                                 |

|     |          |         |     | [Setting condition]                                                                                                                                        |

|     |          |         |     | <ul> <li>When receive data is transferred from ICDRS to<br/>ICDRR</li> </ul>                                                                               |

|     |          |         |     | [Clearing conditions]                                                                                                                                      |

|     |          |         |     | • When 0 is written to this bit after reading RDRF = 1                                                                                                     |

|     |          |         |     | (When the CPU is used to clear this flag by writing 0 while the corresponding interrupt is enabled, be sure to read the flag after writing 0 to it.)       |

| _   |          |         |     | When data is read from ICDRR                                                                                                                               |

| 4   | NACKF    | 0       | R/W | No Acknowledge Detection Flag                                                                                                                              |

|     |          |         |     | [Setting condition]                                                                                                                                        |

|     |          |         |     | <ul> <li>When no acknowledge is detected from the receive<br/>device in transmission while the ACKE bit in ICIER<br/>is set to 1</li> </ul>                |

|     |          |         |     | [Clearing condition]                                                                                                                                       |

|     |          |         |     | <ul> <li>When 0 is written to this bit after reading NACKF =<br/>1</li> </ul>                                                                              |

|     |          |         |     | (When the CPU is used to clear this flag by writing 0 while the corresponding interrupt is enabled, be sure to read the flag after writing 0 to it.)       |

| 3   | STOP     | 0       | R/W | Stop Condition Detection Flag                                                                                                                              |

|     |          |         |     | [Setting condition]                                                                                                                                        |

|     |          |         |     | <ul> <li>When a stop condition is detected after frame<br/>transfer</li> </ul>                                                                             |

|     |          |         |     | [Clearing condition]                                                                                                                                       |

|     |          |         |     | <ul> <li>When 0 is written to this bit after reading STOP = 1</li> </ul>                                                                                   |

|     |          |         |     | (When the CPU is used to clear this flag by writing<br>0 while the corresponding interrupt is enabled, be<br>sure to read the flag after writing 0 to it.) |

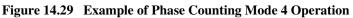

## 25.8.1 Boot Mode

SCI Boot mode executes programming/erasure of the user MAT or user boot MAT by means of the control command and program data transmitted from the externally connected host via the on-chip SCI\_4.

In SCI boot mode, the tool for transmitting the control command and program data, and the program data must be prepared in the host. The serial communications mode is set to asynchronous mode. The system configuration in boot mode is shown in figure 25.6. Interrupts are ignored in SCI boot mode. Configure the user system so that interrupts do not occur.

Figure 25.6 System Configuration in Boot Mode

|                                               |              | Number  |         |        | Data  | Access<br>Cycles |

|-----------------------------------------------|--------------|---------|---------|--------|-------|------------------|

| Register Name                                 | Abbreviation | of Bits | Address | Module | Width | (Read/Write)     |

| IRQ sense control register L                  | ISCRL        | 16      | H'FFD6A | INTC   | 16    | 2lø/3lø          |

| DTC vector base register                      | DTCVBR       | 32      | H'FFD80 | BSC    | 16    | 2lø/3lø          |

| Bus width control register                    | ABWCR        | 16      | H'FFD84 | BSC    | 16    | 2lø/3lø          |

| Access state control register                 | ASTCR        | 16      | H'FFD86 | BSC    | 16    | 2lø/3lø          |

| Wait control register A                       | WTCRA        | 16      | H'FFD88 | BSC    | 16    | 2lø/3lø          |

| Wait control register B                       | WTCRB        | 16      | H'FFD8A | BSC    | 16    | 2lø/3lø          |

| Read strobe timing control register           | RDNCR        | 16      | H'FFD8C | BSC    | 16    | 2lø/3lø          |

| CS assertion period control register          | CSACR        | 16      | H'FFD8E | BSC    | 16    | 2lø/3lø          |

| Idle control register                         | IDLCR        | 16      | H'FFD90 | BSC    | 16    | 2lø/3lø          |

| Bus control register 1                        | BCR1         | 16      | H'FFD92 | BSC    | 16    | 2lø/3lø          |

| Bus control register 2                        | BCR2         | 8       | H'FFD94 | BSC    | 16    | 2lø/3lø          |

| Endian control register                       | ENDIANCR     | 8       | H'FFD95 | BSC    | 16    | 2lø/3lø          |

| SRAM mode control register                    | SRAMCR       | 16      | H'FFD98 | BSC    | 16    | 2lø/3lø          |

| Burst ROM interface control register          | BROMCR       | 16      | H'FFD9A | BSC    | 16    | 21¢/31¢          |

| Address/data multiplexed I/O control register | MPXCR        | 16      | H'FFD9C | BSC    | 16    | 2lø/3lø          |

| DRAM control register                         | DRAMCR       | 16      | H'FFDA0 | BSC    | 16    | 2lø/3lø          |

| DRAM access control register                  | DRACCR       | 16      | H'FFDA2 | BSC    | 16    | 2lø/3lø          |

| Synchronous DRAM control register             | SDCR         | 16      | H'FFDA4 | BSC    | 16    | 2lø/3lø          |

| Refresh control register                      | REFCR        | 16      | H'FFDA6 | BSC    | 16    | 2lø/3lø          |

| Refresh timer counter                         | RTCNT        | 8       | H'FFDA8 | BSC    | 16    | 2lø/3lø          |

| Refresh time constant register                | RTCOR        | 8       | H'FFDA9 | BSC    | 16    | 2lø/3lø          |

| RAM emulation register                        | RAMER        | 8       | H'FFD9E | BSC    | 16    | 2lø/3lø          |

| Mode control register                         | MDCR         | 16      | H'FFDC0 | SYSTEM | 16    | 2lø/3lø          |

| System control register                       | SYSCR        | 16      | H'FFDC2 | SYSTEM | 16    | 2lø/3lø          |

| System clock control register                 | SCKCR        | 16      | H'FFDC4 | SYSTEM | 16    | 2lø/3lø          |

| Standby control register                      | SBYCR        | 16      | H'FFDC6 | SYSTEM | 16    | 2lø/3lø          |

| Module stop control register A                | MSTPCRA      | 16      | H'FFDC8 | SYSTEM | 16    | 2lø/3lø          |

| Module stop control register B                | MSTPCRB      | 16      | H'FFDCA | SYSTEM | 16    | 2lø/3lø          |

| Module stop control register C                | MSTPCRC      | 16      | H'FFDCC | SYSTEM | 16    | 2lø/3lø          |

| Subclock control register                     | SUBCKCR      | 8       | H'FFDCF | SYSTEM | 16    | 2lø/3lø          |

| Flash code control/status register            | FCCS         | 8       | H'FFDE8 | FLASH  | 16    | 2lø/2lø          |

Figure 30.21 DRAM Access Timing: Two-State Burst Access