Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f882-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

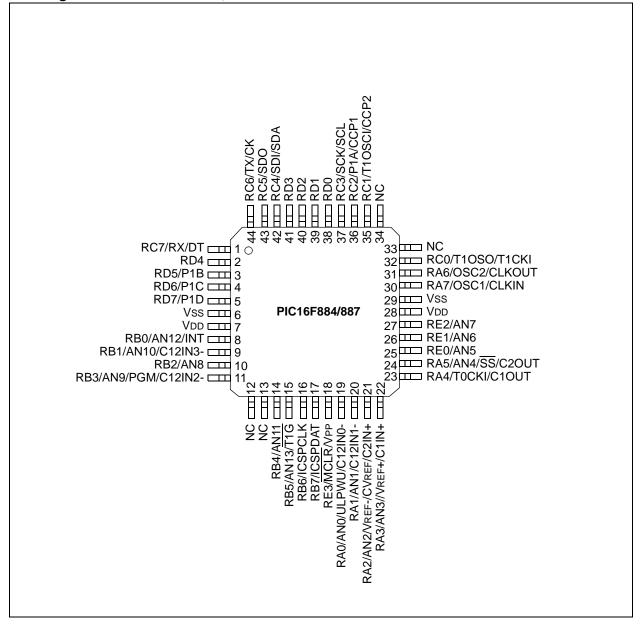

#### Pin Diagrams - PIC16F884/887, 44-Pin TQFP

#### 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

## **REGISTER DEFINITIONS: TIMER1 CONTROL**

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                 | R/W-0                 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|-----------------------|---------|---------|---------|--------|--------|--------|

| T1GINV <sup>(1)</sup> | TMR1GE <sup>(2)</sup> | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7                 |                       |         |         |         |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | T1GINV: Timer1 Gate Invert bit <sup>(1)</sup>                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> </ul> |

| bit 6   | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup>                                                                                                                |

|         | $\frac{\text{If TMR1ON} = 0}{1000}$                                                                                                                          |

|         | This bit is ignored<br>If TMR1ON = 1:                                                                                                                        |

|         | 1 = Timer1 counting is controlled by the Timer1 Gate function                                                                                                |

|         | 0 = Timer1 is always counting                                                                                                                                |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                         |

|         | 11 = 1:8 Prescale Value                                                                                                                                      |

|         | 10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value                                                                                                           |

|         | 00 = 1:1 Prescale Value                                                                                                                                      |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit                                                                                                                    |

|         | 1 = LP oscillator is enabled for Timer1 clock                                                                                                                |

|         | 0 = LP oscillator is off                                                                                                                                     |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                                              |

|         | <u>TMR1CS = 1:</u><br>1 = Do not synchronize external clock input                                                                                            |

|         | 0 = Synchronize external clock input                                                                                                                         |

|         | $\underline{TMR1CS} = 0:$                                                                                                                                    |

| 1 1 4   | This bit is ignored. Timer1 uses the internal clock                                                                                                          |

| bit 1   | TMR1CS: Timer1 Clock Source Select bit                                                                                                                       |

|         | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                                        |

| bit 0   | TMR10N: Timer1 On bit                                                                                                                                        |

|         | 1 = Enables Timer1                                                                                                                                           |

|         | 0 = Stops Timer1                                                                                                                                             |

| Note 1: | T1GINV bit inverts the Timer1 gate logic, regardless of source.                                                                                              |

| 2.      | TMR1GE bit must be set to use either $\overline{116}$ pip or C20UT as selected by the T1GSS bit of the CM2CON1                                               |

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CM2CON1 register, as a Timer1 gate source.

## **REGISTER DEFINITIONS: TIMER2 CONTROL**

#### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER

| U-0                   | R/                                             | /W-0                 | R/W-0            | R/W-0         | R/W-0          | ) R       | /W-0        | R/W-0           | R/W-0   |

|-----------------------|------------------------------------------------|----------------------|------------------|---------------|----------------|-----------|-------------|-----------------|---------|

| —                     | TOL                                            | JTPS3                | TOUTPS2          | TOUTPS1       | TOUTP          | S0 TN     | IR2ON       | T2CKPS1         | T2CKPS0 |

| bit 7                 |                                                |                      |                  |               |                |           |             |                 | bit 0   |

| Lowende               |                                                |                      |                  |               |                |           |             |                 |         |

| Legend:<br>R = Readab | la hit                                         |                      | W = Writable     | hit           | II – I Inin    | nplemente | d hit road  | 1 as 'O'        |         |

| -n = Value a          |                                                |                      | '1' = Bit is set | UIL           |                | s cleared | a bit, read | x = Bit is unkr | nwn     |

|                       |                                                |                      |                  |               | 0 – Dit i      | s cleared |             |                 |         |

| bit 7                 | Unim                                           | plement              | ed: Read as '    | 0'            |                |           |             |                 |         |

| bit 6-3               | TOUT                                           | TPS<3:0>             | -: Timer2 Outp   | out Postscale | er Select bits | 5         |             |                 |         |

|                       |                                                | = 1:1 Po             | -                |               |                |           |             |                 |         |

|                       | 0001                                           | = 1:2 Po             | stscaler         |               |                |           |             |                 |         |

|                       | 0010                                           | = 1:3 Po             | stscaler         |               |                |           |             |                 |         |

|                       |                                                | = 1:4 Po             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:5 Po             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:6 Po             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:7 Po<br>= 1:8 Po |                  |               |                |           |             |                 |         |

|                       |                                                | = 1.0 P0             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:10 P             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:11 P             |                  |               |                |           |             |                 |         |

|                       |                                                | = 1:12 P             |                  |               |                |           |             |                 |         |

|                       | 1100                                           | = 1:13 P             | ostscaler        |               |                |           |             |                 |         |

|                       | 1101                                           | = 1:14 P             | ostscaler        |               |                |           |             |                 |         |

|                       |                                                | = 1:15 P             |                  |               |                |           |             |                 |         |

|                       | 1111                                           | = 1:16 P             | ostscaler        |               |                |           |             |                 |         |

| bit 2                 | TMR                                            | 20N: Tim             | er2 On bit       |               |                |           |             |                 |         |

|                       | 1 = T                                          | Fimer2 is            | on               |               |                |           |             |                 |         |

|                       | 0 = <b>T</b>                                   | Fimer2 is            | off              |               |                |           |             |                 |         |

| bit 1-0               | T2CKPS<1:0>: Timer2 Clock Prescale Select bits |                      |                  |               |                |           |             |                 |         |

|                       | 00 =                                           | Prescaler            | r is 1           |               |                |           |             |                 |         |

|                       | 01 =                                           | Prescaler            | is 4             |               |                |           |             |                 |         |

|                       | 1x =                                           | Prescaler            | r is 16          |               |                |           |             |                 |         |

|                       | . פוו                                          |                      |                  |               |                |           |             |                 |         |

| TABLE 7-1             | . 30                                           | ININAR Y             | ' OF ASSOC       |               | IER2 REG       | ISTERS    |             |                 |         |

| Name   | Bit 7                                        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------------------------------------------|---------|---------|---------|---------|--------|---------|---------|---------------------|

| INTCON | GIE                                          | PEIE    | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 32                  |

| PIE1   | —                                            | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 33                  |

| PIR1   | —                                            | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 35                  |

| PR2    | Timer2 Module Period Register                |         |         |         |         |        |         | 83      |                     |

| TMR2   | Holding Register for the 8-bit TMR2 Register |         |         |         |         |        | 83      |         |                     |

| T2CON  | —                                            | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 84                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

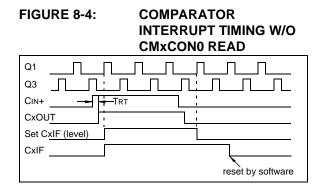

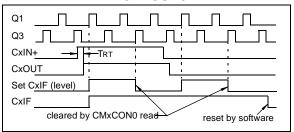

### 8.4 Comparator Interrupt Operation

The comparator interrupt flag can be set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusiveor gate (see Figures 8-2 and 8-3). One latch is updated with the comparator output level when the CMxCON0 register is read. This latch retains the value until the next read of the CMxCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. At this point the two mismatch latches have opposite output levels which is detected by the exclusive-or gate and fed to the interrupt circuitry. The mismatch condition persists until either the CMxCON0 register is read or the comparator output returns to the previous state.

- Note 1: A write operation to the CMxCON0 register will also clear the mismatch condition because all writes include a read operation at the beginning of the write cycle.

- **2:** Comparator interrupts will operate correctly regardless of the state of CxOE.

The comparator interrupt is set by the mismatch edge and not the mismatch level. This means that the interrupt flag can be reset without the additional step of reading or writing the CMxCON0 register to clear the mismatch registers. When the mismatch registers are cleared, an interrupt will occur upon the comparator's return to the previous state, otherwise no interrupt will be generated.

Software will need to maintain information about the status of the comparator output, as read from the CMxCON0 register, or CM2CON1 register, to determine the actual change that has occurred.

The CxIF bit of the PIR2 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, an interrupt can be generated.

The CxIE bit of the PIE2 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR2 register will still be set if an interrupt condition occurs.

COMPARATOR INTERRUPT TIMING WITH CMxCON0 READ

- Note 1: If a change in the CMxCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF of the PIR2 register interrupt flag may not get set.

- 2: When either comparator is first enabled, bias circuitry in the comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1  $\mu$ s for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

#### 8.8 Additional Comparator Features

There are three additional comparator features:

- Timer1 count enable (gate)

- Synchronizing output with Timer1

- Simultaneous read of comparator outputs

#### 8.8.1 COMPARATOR C2 GATING TIMER1

This feature can be used to time the duration or interval of analog events. Clearing the T1GSS bit of the CM2CON1 register will enable Timer1 to increment based on the output of Comparator C2. This requires that Timer1 is on and gating is enabled. See **Section 6.0 "Timer1 Module with Gate Control"** for details.

It is recommended to synchronize the comparator with Timer1 by setting the C2SYNC bit when the comparator is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if the comparator changes during an increment.

#### 8.8.2 SYNCHRONIZING COMPARATOR C2 OUTPUT TO TIMER1

The Comparator C2 output can be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 register. When enabled, the C2 output is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figures 8-2 and 8-3) and the Timer1 Block Diagram (Figure 6-1) for more information.

#### 8.8.3 SIMULTANEOUS COMPARATOR OUTPUT READ

The MC1OUT and MC2OUT bits of the CM2CON1 register are mirror copies of both comparator outputs. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

Note 1: Obtaining the status of C1OUT or C2OUT by reading CM2CON1 does not affect the comparator interrupt mismatch registers.

#### REGISTER 8-3: CM2CON1: COMPARATOR C2 CONTROL REGISTER 1

| R-0     | R-0    | R/W-0  | R/W-0  | U-0 | U-0 | R/W-1 | R/W-0  |

|---------|--------|--------|--------|-----|-----|-------|--------|

| MC1OUT  | MC2OUT | C1RSEL | C2RSEL | —   |     | T1GSS | C2SYNC |

| bit 7 b |        |        |        |     |     |       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | MC10UT: Mirror Copy of C10UT bit                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                         |

| bit 6   | MC2OUT: Mirror Copy of C2OUT bit                                                                                                                        |

| bit 5   | C1RSEL: Comparator C1 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C1VREF input of Comparator C1                                                                                                       |

|         | <ul> <li>0 = Absolute voltage reference (0.6) routed to C1VREF input of Comparator C1 (or 1.2V precision<br/>reference on parts so equipped)</li> </ul> |

| bit 4   | C2RSEL: Comparator C2 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C2VREF input of Comparator C2                                                                                                       |

|         | 0 = Absolute voltage reference (0.6) routed to C2VREF input of Comparator C2 (or 1.2V precision                                                         |

|         | reference on parts so equipped)                                                                                                                         |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                              |

| bit 1   | T1GSS: Timer1 Gate Source Select bit                                                                                                                    |

|         | 1 = Timer1 gate source is $\overline{T1G}$                                                                                                              |

|         | 0 = Timer1 gate source is SYNCC2OUT.                                                                                                                    |

| bit 0   | C2SYNC: Comparator C2 Output Synchronization bit                                                                                                        |

|         | 1 = Output is synchronous to falling edge of Timer1 clock                                                                                               |

|         | 0 = Output is asynchronous                                                                                                                              |

|         |                                                                                                                                                         |

### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 9-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

5.0V VDD

$$T_{ACQ} = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 2µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for Tc can be approximated with the following equations:

$$V_{APPLIED} \left( 1 - \frac{1}{(2^{n+1}) - 1} \right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb

V_{APPLIED} \left( 1 - \frac{1}{(2^{n+1}) - 1} \right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}

$$V_{APPLIED} \left( 1 - e^{\frac{-TC}{RC}} \right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}

V_{APPLIED} \left( 1 - e^{\frac{-TC}{RC}} \right) = V_{APPLIED} \left( 1 - \frac{1}{(2^{n+1}) - 1} \right) \qquad ;combining [1] and [2]$$

Solving for TC:

$$T_{C} = -C_{HOLD} (RIC + RSS + RS) ln(1/2047) = -10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.0004885) = 1.37µs$$

Therefore:

$$T_{ACQ} = 2MS + 1.37MS + [(50°C - 25°C)(0.05MS/°C)] = 4.67MS$$$$$$

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

© 2006-2015 Microchip Technology Inc.

| P1M<′    | 1.0>                      | Signal        |              | Width       | — Period —           |            |

|----------|---------------------------|---------------|--------------|-------------|----------------------|------------|

| 00       | (Single Output)           | P1A Modulated |              |             |                      |            |

|          |                           | P1A Modulated | <br>Dela     |             | Delay <sup>(1)</sup> | į          |

| 10       | (Half-Bridge)             | P1B Modulated |              | y(')        |                      |            |

|          |                           | P1A Active    | _ ;          |             |                      |            |

| 01       | (Full-Bridge,<br>Forward) | P1B Inactive  | - :          |             | <br> <br>            | <br>1<br>1 |

|          | Forward)                  | P1C Inactive  |              |             |                      |            |

|          |                           | P1D Modulated | = — <u> </u> |             |                      | <br>       |

|          |                           | P1A Inactive  | _ !          |             | i                    | <u> </u>   |

| 11       | (Full-Bridge,             | P1B Modulated |              |             |                      |            |

| Reverse) | P1C Active                |               |              | ·<br>·<br>· |                      |            |

|          |                           | P1D Inactive  | ;            |             |                      | <br> <br>  |

#### FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

Delay = 4 \* Tosc \* (PWM1CON<6:0>)

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 11.6.6 "Programmable Dead-Band Delay Mode").

| R-0           | R-1                                                                                                     | U-0                                                                                                       | R/W-0           | R/W-0             | U-0             | R/W-0           | R/W-0 |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| ABDOVF        | RCIDL                                                                                                   |                                                                                                           | SCKP            | BRG16             | _               | WUE             | ABDEN |  |  |  |  |

| bit 7         |                                                                                                         |                                                                                                           |                 | 1                 |                 |                 | bit 0 |  |  |  |  |

|               |                                                                                                         |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| Legend:       |                                                                                                         |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| R = Readable  | e bit                                                                                                   | W = Writable                                                                                              | bit             | U = Unimplem      | nented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value at | POR                                                                                                     | '1' = Bit is se                                                                                           | t               | '0' = Bit is clea | ared            | x = Bit is unki | nown  |  |  |  |  |

|               |                                                                                                         |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| bit 7         | -                                                                                                       | uto-Baud Deteo                                                                                            | ct Overflow bit | :                 |                 |                 |       |  |  |  |  |

|               | Asynchrono                                                                                              |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | ud timer overflo<br>ud timer did not                                                                      |                 |                   |                 |                 |       |  |  |  |  |

|               | <u>Synchronou</u>                                                                                       |                                                                                                           | overnow         |                   |                 |                 |       |  |  |  |  |

|               | Don't care                                                                                              |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| bit 6         | RCIDL: Rec                                                                                              | eive Idle Flag b                                                                                          | it              |                   |                 |                 |       |  |  |  |  |

|               | <u>Asynchrono</u>                                                                                       | <u>us mode</u> :                                                                                          |                 |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | 1 = Receiver is Idle                                                                                      |                 |                   |                 |                 |       |  |  |  |  |

|               | <ul> <li>0 = Start bit has been received and the receiver is receiving<br/>Synchronous mode:</li> </ul> |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | Don't care                                                                                              | <u>s mode</u> .                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| bit 5         | Unimpleme                                                                                               | Unimplemented: Read as '0'                                                                                |                 |                   |                 |                 |       |  |  |  |  |

| bit 4         | SCKP: Synchronous Clock Polarity Select bit                                                             |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | Asynchronous mode:                                                                                      |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | 1 = Transmit inverted data to the RB7/TX/CK pin                                                         |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | t non-inverted d                                                                                          | ata to the RB   | 7/TX/CK pin       |                 |                 |       |  |  |  |  |

|               | Synchronou                                                                                              |                                                                                                           | n odgo of tho   | alaak             |                 |                 |       |  |  |  |  |

|               |                                                                                                         | clocked on rising                                                                                         |                 |                   |                 |                 |       |  |  |  |  |

| bit 3         |                                                                                                         | bit Baud Rate C                                                                                           | • •             |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | aud Rate Gene                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

|               | 0 = 8-bit Ba                                                                                            | ud Rate Generation                                                                                        | ator is used    |                   |                 |                 |       |  |  |  |  |

| bit 2         | Unimpleme                                                                                               | nted: Read as                                                                                             | ʻ0'             |                   |                 |                 |       |  |  |  |  |

| bit 1         | WUE: Wake                                                                                               | -up Enable bit                                                                                            |                 |                   |                 |                 |       |  |  |  |  |

|               | Asynchronous mode:                                                                                      |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | 1 = Receiver is waiting for a falling edge. No character will be received byte RCIF will be set. WUE will |                 |                   |                 |                 |       |  |  |  |  |

|               |                                                                                                         | tically clear afte                                                                                        |                 |                   |                 |                 |       |  |  |  |  |

|               | <ul> <li>0 = Receiver is operating normally</li> <li>Synchronous mode:</li> </ul>                       |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | Don't care                                                                                              | <u>s mode</u> .                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| bit 0         |                                                                                                         | to-Baud Detect                                                                                            | Enable bit      |                   |                 |                 |       |  |  |  |  |

|               | Abden. Auto-Baud Delect Enable bit<br>Asynchronous mode:                                                |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | -                                                                                                       |                                                                                                           | e is enabled (  | clears when aut   | o-baud is con   | nplete)         |       |  |  |  |  |

|               |                                                                                                         | aud Detect mod                                                                                            |                 |                   |                 | . ,             |       |  |  |  |  |

|               | <u>Synchronou</u>                                                                                       | <u>s mode</u> :                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

|               | Don't care                                                                                              |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

### REGISTER 12-3: BAUDCTL: BAUD RATE CONTROL REGISTER

© 2006-2015 Microchip Technology Inc.

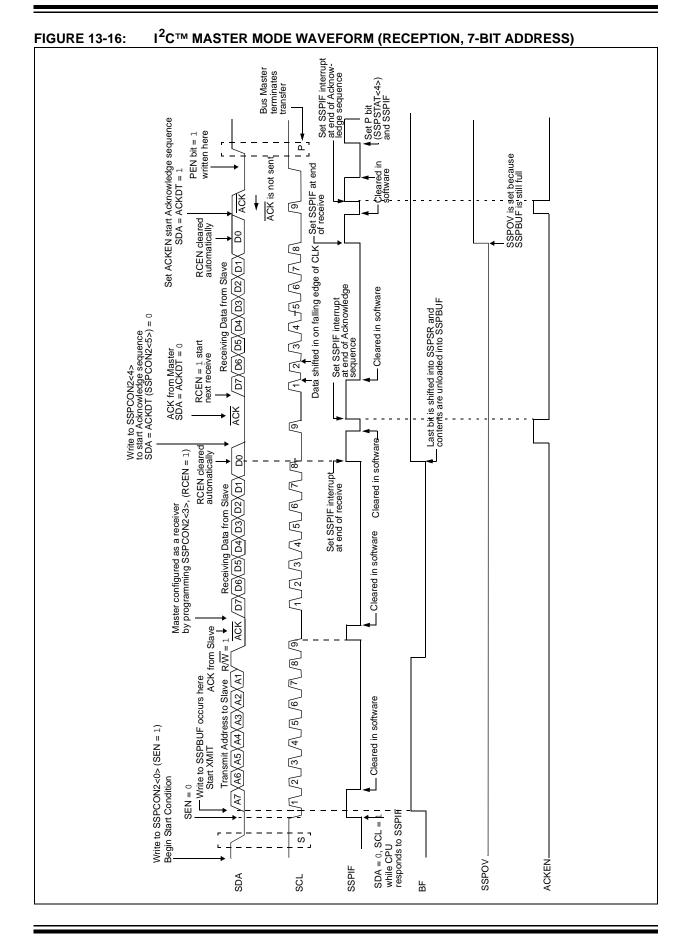

### 13.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 13.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call).

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode.

#### 13.2 Control Registers

The MSSP module has three associated registers. These include a STATUS register and two control registers.

Register 13-1 shows the MSSP STATUS register (SSPSTAT), Register 13-2 shows the MSSP Control Register 1 (SSPCON), and Register 13-3 shows the MSSP Control Register 2 (SSPCON2).

| TABLE 14-4: | INITIALIZATION CONDITION FOR REGISTER (CONTINUED) |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

| Register              | Address  | Power-on<br>Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out (Continued) |

|-----------------------|----------|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| CCPR2H                | 1Ch      | xxxx xxxx         | uuuu uuuu                                                             | uuuu uuuu                                                                                         |

| CCP2CON               | 1Dh      | 00 0000           | 00 0000                                                               | uu uuuu                                                                                           |

| ADRESH                | 1Eh      | xxxx xxxx         | uuuu uuuu                                                             | uuuu uuuu                                                                                         |

| ADCON0                | 1Fh      | 00-0 0000         | 00-0 0000                                                             | uu-u uuuu                                                                                         |

| OPTION_REG            | 81h/181h | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| TRISA                 | 85h      | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| TRISB                 | 86h/186h | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| TRISC                 | 87h      | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| TRISD                 | 88h      | 1111 1111         | 1111 1111                                                             | սսսս սսսս                                                                                         |

| TRISE                 | 89h      | 1111              | 1111                                                                  | uuuu                                                                                              |

| PIE1                  | 8Ch      | 0000 0000         | 0000 0000                                                             | սսսս սսսս                                                                                         |

| PIE2                  | 8Dh      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| PCON                  | 8Eh      | 010x              | 0uuu <b>(1, 5)</b>                                                    | uuuu                                                                                              |

| OSCCON                | 8Fh      | -110 q000         | -110 q000                                                             | -uuu uuuu                                                                                         |

| OSCTUNE               | 90h      | 0 0000            | u uuuu                                                                | u uuuu                                                                                            |

| SSPCON2               | 91h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| PR2                   | 92h      | 1111 1111         | 1111 1111                                                             | 1111 1111                                                                                         |

| SSPADD <sup>(6)</sup> | 93h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| SSPMSK <sup>(6)</sup> | 93h      | 1111 1111         | 1111 1111                                                             | 1111 1111                                                                                         |

| SSPSTAT               | 94h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| WPUB                  | 95h      | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| IOCB                  | 96h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| VRCON                 | 97h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| TXSTA                 | 98h      | 0000 -010         | 0000 -010                                                             | uuuu –uuu                                                                                         |

| SPBRG                 | 99h      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| SPBRGH                | 9Ah      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| PWM1CON               | 9Bh      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| ECCPAS                | 9Ch      | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| PSTRCON               | 9Dh      | 0 0001            | 0 0001                                                                | u uuuu                                                                                            |

| ADRESL                | 9Eh      | xxxx xxxx         | uuuu uuuu                                                             | uuuu uuuu                                                                                         |

| ADCON1                | 9Fh      | 0-00              | 0-00                                                                  | u-uu                                                                                              |

| WDTCON                | 105h     | 0 1000            | 0 1000                                                                | u uuuu                                                                                            |

| CM1CON0               | 107h     | 0000 0-00         | 0000 0-00                                                             | uuuu u-uu                                                                                         |

| CM2CON0               | 108h     | 0000 0-00         | 0000 0-00                                                             | uuuu u-uu                                                                                         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

**5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPCON register bits SSPM<3:0 > = 1001.

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |  |

|                  | Before Instruction<br>REG1 = 1110 0110<br>C = 0                                                                                                                                                                      |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | REG1 = 1110 0110<br>W = 1100 1100                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                       |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |  |  |  |

| Operands:        | None                                                                                                                                                                                                                               |  |  |  |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \text{PD} \end{array}$                                                         |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |  |  |  |

| Description:     | The power-down Status bit, $\overline{PD}$<br>is cleared. Time-out Status bit,<br>$\overline{TO}$ is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                               |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

|                  | C = 0 $W > k$                                                                                                            |  |  |  |  |

| <b>C</b> = 0 | W > k                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq k$                |

| DC = 0       | W<3:0> > k<3:0>           |

| DC = 1       | $W < 3:0 > \le k < 3:0 >$ |

| SUBWF            | Subtract W from f                                                                                                                                                                           |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                          |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| <b>C</b> = 0 | W > f                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq f$                |

| DC = 0       | W<3:0> > f<3:0>           |

| DC = 1       | $W < 3:0 > \le f < 3:0 >$ |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                         |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in the W<br>register. If 'd' is '1', the result is<br>placed in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] XORWF f,d                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

#### TABLE 17-10: PIC16F882/883/884/886/887 A/D CONVERTER (ADC) CHARACTERISTICS

|               | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                      |            |      |          |       |                                                                     |

|---------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|

| Param<br>No.  | Sym.                                                                                                                     | Characteristic                                       | Min.       | Тур† | Max.     | Units | Conditions                                                          |

| AD01          | NR                                                                                                                       | Resolution                                           | —          |      | 10 bits  | bit   |                                                                     |

| AD02          | EIL                                                                                                                      | Integral Error                                       |            | —    | ±1       | LSb   | VREF = 5.12V                                                        |

| AD03          | Edl                                                                                                                      | Differential Error                                   |            | _    | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |

| AD04          | EOFF                                                                                                                     | Offset Error                                         | 0          | +1.5 | +3.0     | LSb   | VREF = 5.12V                                                        |

| AD07          | Egn                                                                                                                      | Gain Error                                           | _          | _    | ±1       | LSb   | VREF = 5.12V                                                        |

| AD06<br>AD06A | Vref                                                                                                                     | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.7 |      | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |

| AD07          | VAIN                                                                                                                     | Full-Scale Range                                     | Vss        | _    | Vref     | V     |                                                                     |

| AD08          | ZAIN                                                                                                                     | Recommended<br>Impedance of Analog<br>Voltage Source | _          | _    | 10       | kΩ    |                                                                     |

| AD09*         | IREF                                                                                                                     | VREF Input Current <sup>(3)</sup>                    | 10         | _    | 1000     | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|               |                                                                                                                          |                                                      | _          | _    | 50       | μA    | During A/D conversion cycle.                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

© 2006-2015 Microchip Technology Inc.

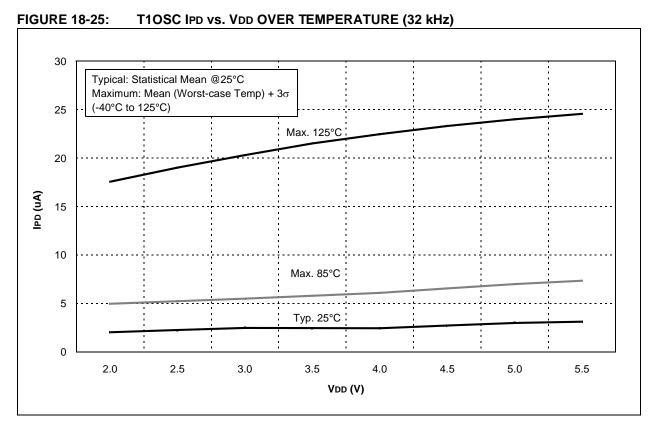

FIGURE 18-34: LFINTOSC FREQUENCY vs. V dd OVER TEMPERATURE (31 kHz)

¤ 2006-2015 Microchip Technology Inc.

### APPENDIX A: DATA SHEET REVISION HISTORY

#### Revision A (5/2006)

Initial release of this data sheet.

### Revision B (7/2006)

Pin Diagrams (44-Pin QFN drawing); Revised Table 2-1, Addr. 1DH (CCP2CON); Section 3.0, 3.1; Section 3.4.4.6; Table 3; Table 3-1 (ANSEL); Table 3-3 (CCP2CON); Register 3-1; Register 3.2; Register 3-3; Register 3-4; Register 3-9; Register 3-10; Register 3-11; Register 3-12; Register 3-14; Table 3-5 (ANSEL); Figure 3-5; Figure 3-11; Figure 8-2; Figure 8-3; Figure 9-1; Register 9-1; Section 9.1.4; Example 10-4; Figure 11-5; Table 11-5 (P1M); Section 11.5.2; Section 11.5.7, Number 4; Table 11-7 (CCP2CON); Section 12.3.1 (Para. 3); Figure 12-6 (Title); Sections 14.2, 14.3 and 14.4 DC Characteristics (Max); Table 14-4 (OSCCON); Section 14.3 (TMR0); Section 14.3.2 (TMR0).

#### **Revision C**

Section 19.0 Packaging Information: Replaced package drawings and added note. Added PIC16F882 part number. Replaced PICmicro with PIC.

#### **Revision D**

Replaced Package Drawings (Rev. AM); Replaced Development Support Section; Revised Product ID Section.

#### **Revision E (01/2008)**

Added Char Data; Removed Preliminary status; Revised Device Table (PIC16F882, I/O); Revised the following: Pin Diagram 44 TQFP, pin 30; Table 5, I/O RA7; Table 1-1, RA1 and RA4; Section 2.2.1; Register 2-3, INTCON; Example 3-1; Section 3.2.2; Example 3-2; Figure 6-1; Section 6.2.2; Section 6.6; Section 8.10.3; Table 9-1; Equation 11-1; Added Figure 11-14 and renumbered remaining Figures; Register 11-3; Register 13-3; Section 14.0; Section 14.1; Section 14.9; Section 14.10; Section 17.0; Updated Package Drawings.

#### Revision F (04/2009)

Revised Product ID: Removed 'F' (std. voltage range) from part numbers; Revised Figure 6-1: Timer1 Block Diagram; Revised Figure 8-3, Comparator C2 Block Diagram; Added note to Section 8.10.3; Revised Section 8.10.7.

#### **Revision G (10/2012)**

Updated data sheet to new format; Updated Register 13-1 and Register 13-2; Updated the Packaging Information section; Updated the Product Identification System section; Other minor corrections.

### Revision H (04/2015)

Added Section 17.9: High Temperature Operation in the Electrical Specifications section.

### APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC16F88X Family of devices.

#### B.1 PIC16F87X to PIC16F88X

| TABLE B-1: FE/ | ATURE COMPARISON |

|----------------|------------------|

|----------------|------------------|

| Feature                               | PIC16F87X | PIC16F88X               |

|---------------------------------------|-----------|-------------------------|

| Max Operating Speed                   | 20 MHz    | 20 MHz                  |

| Max Program<br>Memory (Words)         | 8192      | 8192                    |

| SRAM (bytes)                          | 368       | 368                     |

| A/D Resolution                        | 10-bit    | 10-bit                  |

| Data EEPROM (Bytes)                   | 256       | 256                     |

| Timers (8/16-bit)                     | 2/1       | 2/1                     |

| Oscillator Modes                      | 4         | 8                       |

| Brown-out Reset                       | Y         | Y (2.1V/4V)             |

| Software Control Option<br>of WDT/BOR | Ν         | Y                       |

| Internal Pull-ups                     | RB<7:4>   | RB<7:0>,<br>MCLR        |

| Interrupt-on-change                   | RB<7:4>   | RB<7:0>                 |

| Comparator                            | 2         | 2                       |

| References                            | CVREF     | CVREF and<br>VP6        |

| ECCP/CCP                              | 0/2       | 1/1                     |

| Ultra Low-Power<br>Wake-Up            | Ν         | Y                       |

| Extended WDT                          | N         | Y                       |

| INTOSC Frequencies                    | N         | 32 kHz-8 MHz            |

| Clock Switching                       | N         | Y                       |