Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f883-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 3-10). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 3-4 shows how to initialize PORTC.

Reading the PORTC register (Register 3-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 3-10) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 3-4: INITIALIZING PORTC

| BANKSEL | PORTC       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTC       | ;Init PORTC            |

| BANKSEL | TRISC       | ;                      |

| MOVLW   | B`00001100′ | ;Set RC<3:2> as inputs |

| MOVWF   | TRISC       | ;and set RC<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

#### REGISTER 3-9: PORTC: PORTC REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

RC<7:0>: PORTC General Purpose I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

REGISTER 3-10: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> |

|--------|--------|--------|--------|--------|--------|----------------------|----------------------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1               | TRISC0               |

| bit 7  |        |        |        |        |        |                      | bit 0                |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bit

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

**Note 1:** TRISC<1:0> always reads '1' in LP Oscillator mode.

# PIC16F882/883/884/886/887

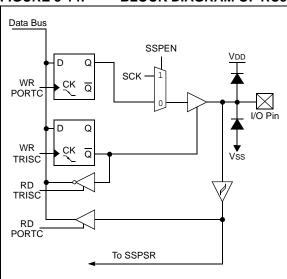

#### 3.5.4 RC3/SCK/SCL

Figure 3-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C<sup>™</sup> clock

#### FIGURE 3-14: BLOCK DIAGRAM OF RC3

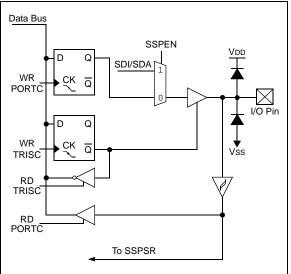

#### 3.5.5 RC4/SDI/SDA

Figure 3-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data I/O

- an I<sup>2</sup>C data I/O

### FIGURE 3-15: BLOCK DIAGRAM OF RC4

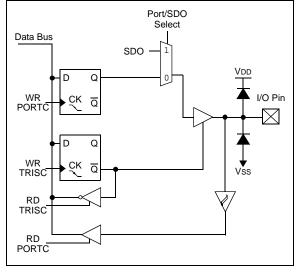

## 3.5.6 RC5/SDO

Figure 3-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a serial data output

# 4.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 4.1 Overview

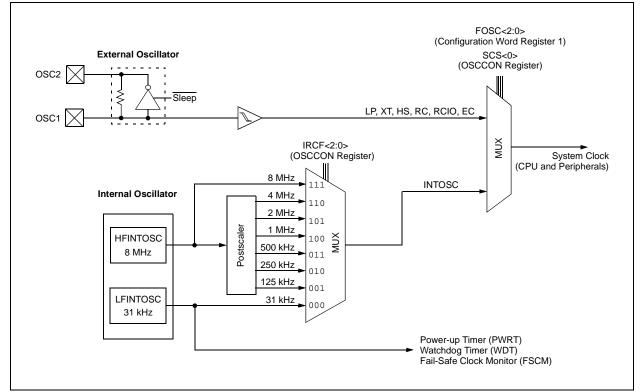

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured from one of two internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

The oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1). The internal clock can be generated from two internal oscillators. The HFINTOSC is a calibrated highfrequency oscillator. The LFINTOSC is an uncalibrated low-frequency oscillator.

#### FIGURE 4-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

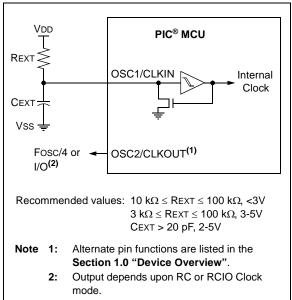

#### 4.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 4-5 shows the external RC mode connections.

FIGURE 4-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 4.5 Internal Clock Modes

The oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 4-2).

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 4.6** "**Clock Switching**" for more information.

#### 4.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1).

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

#### 4.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 4-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See **Section 4.5.4 "Frequency Select Bits (IRCF)"** for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word Register 1 (CONFIG1) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

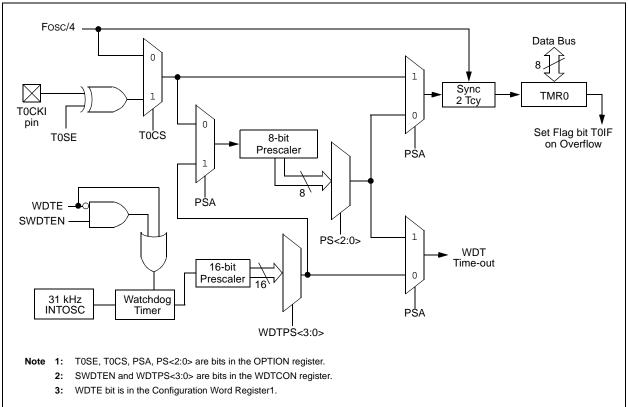

# 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

### 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

#### FIGURE 5-1: TIMER0/WDT PRESCALER BLOCK DIAGRAM

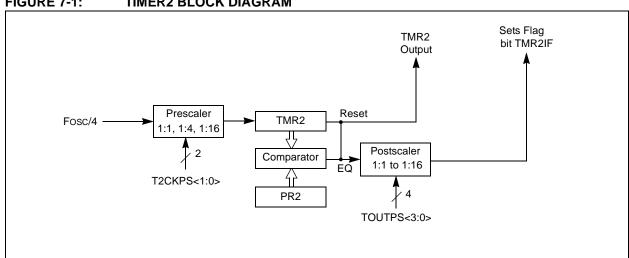

#### **TIMER2 MODULE** 7.0

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 7-1 for a block diagram of Timer2.

#### 7.1 **Timer2 Operation**

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR) Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

| IADLE | 0-2.  |                        |                        | ULIAGE KEF           |                      |      |      | _    | -    |

|-------|-------|------------------------|------------------------|----------------------|----------------------|------|------|------|------|

| RA3   | RA2   | Comp.<br>Reference (+) | Comp.<br>Reference (-) | ADC<br>Reference (+) | ADC<br>Reference (-) | CFG1 | CFG0 | VRSS | VROE |

| I/O   | I/O   | AVdd                   | AVss                   | AVdd                 | AVss                 | 0    | 0    | 0    | 0    |

| I/O   | CVREF | AVdd                   | AVss                   | AVdd                 | AVss                 | 0    | 0    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | AVdd                 | AVss                 | 0    | 0    | 1    | 0    |

| VREF+ | CVREF | Vref+                  | AVss                   | AVdd                 | AVss                 | 0    | 0    | 1    | 1    |

| VREF+ | I/O   | AVDD                   | AVss                   | Vref+                | AVss                 | 0    | 1    | 0    | 0    |

| VREF+ | CVREF | AVdd                   | AVss                   | Vref+                | AVss                 | 0    | 1    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | Vref+                | AVss                 | 0    | 1    | 1    | 0    |

| VREF+ | CVREF | Vref+                  | AVss                   | Vref+                | AVss                 | 0    | 1    | 1    | 1    |

| I/O   | Vref- | AVDD                   | AVss                   | AVDD                 | Vref-                | 1    | 0    | 0    | 0    |

| I/O   | VREF- | AVdd                   | AVss                   | AVdd                 | Vref-                | 1    | 0    | 0    | 1    |

| VREF+ | Vref- | Vref+                  | VREF-                  | AVDD                 | Vref-                | 1    | 0    | 1    | 0    |

| VREF+ | VREF- | Vref+                  | VREF-                  | AVdd                 | VREF-                | 1    | 0    | 1    | 1    |

| VREF+ | VREF- | AVdd                   | AVss                   | Vref+                | Vref-                | 1    | 1    | 0    | 0    |

| VREF+ | VREF- | AVdd                   | AVss                   | Vref+                | VREF-                | 1    | 1    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | Vref+                | VREF-                | 1    | 1    | 1    | 0    |

| VREF+ | VREF- | VREF+                  | Vref-                  | Vref+                | VREF-                | 1    | 1    | 1    | 1    |

#### TABLE 8-2: COMPARATOR AND ADC VOLTAGE REFERENCE PRIORITY

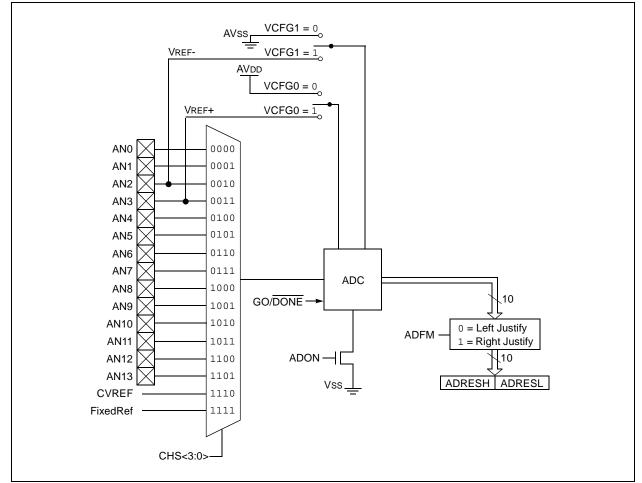

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 9-1 shows the block diagram of the ADC.

#### FIGURE 9-1: ADC BLOCK DIAGRAM

# PIC16F882/883/884/886/887

#### 11.5.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 11-4.

#### EQUATION 11-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 11-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 11-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

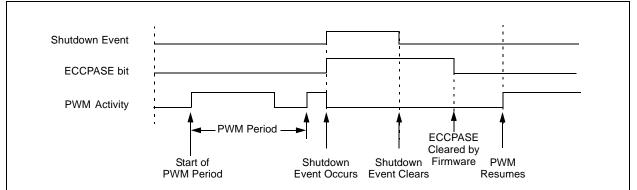

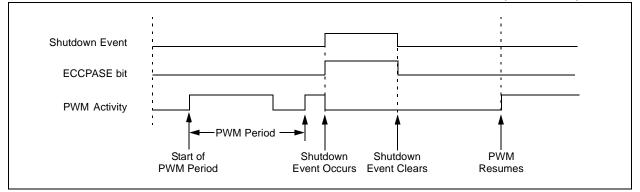

#### 11.6.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 11-16: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

| R/W-0         | R/W-0                | R/W-0                            | R/W-0               | R/W-0            | R-0               | R-0             | R-x      |

|---------------|----------------------|----------------------------------|---------------------|------------------|-------------------|-----------------|----------|

| SPEN          | RX9                  | SREN                             | CREN                | ADDEN            | FERR              | OERR            | RX9D     |

| bit 7         |                      |                                  |                     |                  |                   |                 | bit 0    |

|               |                      |                                  |                     |                  |                   |                 |          |

| Legend:       |                      |                                  |                     |                  |                   |                 |          |

| R = Readabl   |                      | W = Writable                     |                     | -                | mented bit, read  |                 |          |

| -n = Value at | POR                  | '1' = Bit is set                 |                     | '0' = Bit is cle | ared              | x = Bit is unkr | nown     |

| bit 7         | SPEN Serial          | Port Enable bit                  | ŀ                   |                  |                   |                 |          |

| Sit I         |                      |                                  |                     | T and TX/CK p    | ins as serial por | t pins)         |          |

|               |                      | rt disabled (hel                 |                     |                  |                   | /               |          |

| bit 6         | <b>RX9:</b> 9-bit Re | ceive Enable b                   | it                  |                  |                   |                 |          |

|               | 1 = Selects 9        | -                                |                     |                  |                   |                 |          |

| h:4 C         | 0 = Selects 8        | -                                | la h:t              |                  |                   |                 |          |

| bit 5         | Asynchronous         | Receive Enab                     | ne dit              |                  |                   |                 |          |

|               | Don't care           | <u>s mode</u> .                  |                     |                  |                   |                 |          |

|               | Synchronous          | mode – Maste                     | <u>r</u> :          |                  |                   |                 |          |

|               | 1 = Enables          |                                  |                     |                  |                   |                 |          |

|               |                      | single receive                   |                     |                  |                   |                 |          |

|               |                      | ared after recep<br>mode – Slave | btion is comp       | lete.            |                   |                 |          |

|               | Don't care           |                                  |                     |                  |                   |                 |          |

| bit 4         | CREN: Contir         | nuous Receive                    | Enable bit          |                  |                   |                 |          |

|               | Asynchronous         | <u>s mode</u> :                  |                     |                  |                   |                 |          |

|               | 1 = Enables          |                                  |                     |                  |                   |                 |          |

|               | 0 = Disables         |                                  |                     |                  |                   |                 |          |

|               | <u>Synchronous</u>   |                                  | oivo until ono      |                  | s cleared (CREN   | Lovorridos SP   |          |

|               |                      | continuous rec                   |                     |                  |                   | overnues SK     |          |

| bit 3         | ADDEN: Add           | ress Detect En                   | able bit            |                  |                   |                 |          |

|               | Asynchronous         | <u>s mode 9-bit (R</u>           | X9 = 1):            |                  |                   |                 |          |

|               |                      |                                  |                     |                  | d the receive bu  |                 |          |

|               |                      | address detect                   |                     | are received a   | nd ninth bit can  | be used as pa   | rity bit |

|               | Don't care           |                                  | <u>.//3 = 0 j</u> . |                  |                   |                 |          |

| bit 2         | FERR: Frami          | na Error bit                     |                     |                  |                   |                 |          |

|               |                      | -                                | pdated by rea       | ading RCREG I    | register and rec  | eive next valid | byte)    |

|               | 0 = No framir        |                                  |                     | -                | -                 |                 | - /      |

| bit 1         | OERR: Overr          | un Error bit                     |                     |                  |                   |                 |          |

|               |                      |                                  | eared by clea       | aring bit CREN   | )                 |                 |          |

| h:+ 0         | 0 = No overro        |                                  | Data                |                  |                   |                 |          |

| bit 0         |                      | bit of Received                  |                     | t and must be    |                   | or firmulara    |          |

|               | This can be a        | uuress/data bit                  | or a parity bi      | t and must de (  | calculated by us  | er innware.     |          |

# REGISTER 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

| R-0           | R-1                                         | U-0                                  | R/W-0           | R/W-0              | U-0             | R/W-0             | R/W-0          |  |  |

|---------------|---------------------------------------------|--------------------------------------|-----------------|--------------------|-----------------|-------------------|----------------|--|--|

| ABDOVF        | RCIDL                                       |                                      | SCKP            | BRG16              | _               | WUE               | ABDEN          |  |  |

| bit 7         |                                             |                                      |                 | 1                  |                 |                   | bit 0          |  |  |

|               |                                             |                                      |                 |                    |                 |                   |                |  |  |

| Legend:       |                                             |                                      |                 |                    |                 |                   |                |  |  |

| R = Readable  | e bit                                       | W = Writable                         | bit             | U = Unimplem       | nented bit, rea | ad as '0'         |                |  |  |

| -n = Value at | POR                                         | '1' = Bit is se                      | t               | '0' = Bit is clea  | ared            | x = Bit is unki   | nown           |  |  |

|               |                                             |                                      |                 |                    |                 |                   |                |  |  |

| bit 7         | -                                           | uto-Baud Deteo                       | ct Overflow bit | :                  |                 |                   |                |  |  |

|               | Asynchrono                                  |                                      |                 |                    |                 |                   |                |  |  |

|               |                                             | ud timer overflo<br>ud timer did not |                 |                    |                 |                   |                |  |  |

|               | <u>Synchronou</u>                           |                                      | overnow         |                    |                 |                   |                |  |  |

|               | Don't care                                  |                                      |                 |                    |                 |                   |                |  |  |

| bit 6         | RCIDL: Rec                                  | eive Idle Flag b                     | it              |                    |                 |                   |                |  |  |

|               | <u>Asynchrono</u>                           | <u>us mode</u> :                     |                 |                    |                 |                   |                |  |  |

|               | 1 = Receive                                 |                                      |                 |                    |                 |                   |                |  |  |

|               | 0 = Start bit<br>Synchronou                 |                                      | ed and the re   | eceiver is receivi | ng              |                   |                |  |  |

|               | Don't care                                  | <u>s mode</u> .                      |                 |                    |                 |                   |                |  |  |

| bit 5         | Unimpleme                                   | nted: Read as                        | ʻ0'             |                    |                 |                   |                |  |  |

| bit 4         | SCKP: Synchronous Clock Polarity Select bit |                                      |                 |                    |                 |                   |                |  |  |

|               | Asynchronous mode:                          |                                      |                 |                    |                 |                   |                |  |  |

|               |                                             | t inverted data t                    |                 |                    |                 |                   |                |  |  |

|               |                                             | t non-inverted d                     | ata to the RB   | 7/TX/CK pin        |                 |                   |                |  |  |

|               | Synchronou                                  |                                      | n odgo of tho   | alaak              |                 |                   |                |  |  |

|               |                                             | clocked on rising                    |                 |                    |                 |                   |                |  |  |

| bit 3         |                                             | bit Baud Rate C                      | • •             |                    |                 |                   |                |  |  |

|               |                                             | aud Rate Gene                        |                 |                    |                 |                   |                |  |  |

|               | 0 = 8-bit Ba                                | ud Rate Generation                   | ator is used    |                    |                 |                   |                |  |  |

| bit 2         | Unimpleme                                   | nted: Read as                        | ʻ0'             |                    |                 |                   |                |  |  |

| bit 1         | WUE: Wake                                   | -up Enable bit                       |                 |                    |                 |                   |                |  |  |

|               | <u>Asynchrono</u>                           | <u>us mode</u> :                     |                 |                    |                 |                   |                |  |  |

|               |                                             |                                      |                 | No character wil   | l be received l | byte RCIF will be | e set. WUE wil |  |  |

|               |                                             | tically clear afte                   |                 |                    |                 |                   |                |  |  |

|               | 0 = Receive<br>Synchronou                   | r is operating no                    | ormally         |                    |                 |                   |                |  |  |

|               | Don't care                                  | <u>s mode</u> .                      |                 |                    |                 |                   |                |  |  |

| bit 0         |                                             | to-Baud Detect                       | Enable bit      |                    |                 |                   |                |  |  |

|               | Asynchrono                                  |                                      |                 |                    |                 |                   |                |  |  |

|               | -                                           |                                      | e is enabled (  | clears when aut    | o-baud is con   | nplete)           |                |  |  |

|               |                                             | aud Detect mod                       |                 |                    |                 | . ,               |                |  |  |

|               | <u>Synchronou</u>                           | <u>s mode</u> :                      |                 |                    |                 |                   |                |  |  |

|               | Don't care                                  |                                      |                 |                    |                 |                   |                |  |  |

## REGISTER 12-3: BAUDCTL: BAUD RATE CONTROL REGISTER

© 2006-2015 Microchip Technology Inc.

#### 12.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 12.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 12.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 12.4.1.8 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

# 12.4.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGH, SPBRG register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 7. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### REGISTER 13-1: SSPSTAT: SSP STATUS REGISTER

| R/W-0                   | R/W-0                                                      | R-0                                             | R-0                          | R-0                | R-0                   | R-0                  | R-0             |

|-------------------------|------------------------------------------------------------|-------------------------------------------------|------------------------------|--------------------|-----------------------|----------------------|-----------------|

| SMP                     | CKE                                                        | D/A                                             | Р                            | S                  | R/W                   | UA                   | BF              |

| bit 7                   |                                                            |                                                 |                              |                    |                       | •                    | bit (           |

|                         |                                                            |                                                 |                              |                    |                       |                      |                 |

| Legend:<br>R = Readable | hit                                                        | W = Writable bit                                |                              | LI – Unimplomo     | ented bit, read as    | <u>ن</u> ٥'          |                 |

| -n = Value at P         |                                                            | '1' = Bit is set                                |                              | '0' = Bit is clear | -                     | x = Bit is unknov    |                 |

|                         | UK                                                         |                                                 |                              |                    | eu                    |                      | WII             |

| bit 7                   | SMP: Sample                                                | bit                                             |                              |                    |                       |                      |                 |

|                         | SPI Master mo                                              |                                                 |                              |                    |                       |                      |                 |

|                         | •                                                          | sampled at end of<br>sampled at middle          | •                            |                    |                       |                      |                 |

|                         | SPI Slave mod                                              |                                                 |                              |                    |                       |                      |                 |

|                         |                                                            | cleared when SPI                                | is used in Slave             | e mode             |                       |                      |                 |

|                         | $\frac{\ln I^2 C \text{ Master } c}{1 = \text{Slew rate}}$ | o <u>r Slave mode:</u><br>control disabled fo   | r standard sne               | ed mode (100 kH:   | z and 1 MHz)          |                      |                 |

|                         |                                                            | control enabled fo                              | •                            | ,                  | - 4.14 - 11112)       |                      |                 |

| bit 6                   | CKE: SPI Cloc                                              | k Edge Select bit                               |                              |                    |                       |                      |                 |

|                         | $\frac{CKP = 0}{1  Data transmiss}$                        | nitted on falling ed                            | las of SCK                   |                    |                       |                      |                 |

|                         |                                                            | nitted on rising ed                             |                              |                    |                       |                      |                 |

|                         | <u>CKP = 1:</u>                                            |                                                 |                              |                    |                       |                      |                 |

|                         |                                                            | mitted on rising ed<br>mitted on falling ed     | 0                            |                    |                       |                      |                 |

| bit 5                   | _                                                          | ress bit (I <sup>2</sup> C mode                 | -                            |                    |                       |                      |                 |

|                         | 1 = Indicates th                                           | nat the last byte re                            | ceived or trans              |                    |                       |                      |                 |

|                         |                                                            | nat the last byte re                            | ceived or trans              | mitted was addre   | SS                    |                      |                 |

| bit 4                   | P: Stop bit                                                | . This bit is cleared                           | d when the MS                | SP modulo is disa  | bled SSPEN is         | cleared )            |                 |

|                         |                                                            | hat a Stop bit has I                            |                              |                    |                       | cicarcu.)            |                 |

|                         | 0 = Stop bit wa                                            | s not detected las                              | t                            |                    | ,                     |                      |                 |

| bit 3                   | S: Start bit                                               |                                                 |                              |                    |                       |                      |                 |

|                         |                                                            | r. This bit is cleared<br>nat a Start bit has l |                              |                    |                       | cleared.)            |                 |

|                         |                                                            | is not detected las                             |                              |                    | on Resel)             |                      |                 |

| bit 2                   | <b>R/W</b> : Read/Wr                                       | ite bit information                             | (I <sup>2</sup> C mode only) | )                  |                       |                      |                 |

|                         | This bit holds the                                         | he R/W bit informa                              | tion following th            | ne last address m  | atch. This bit is o   | nly valid from the a | ddress match to |

|                         | In I <sup>2</sup> C Slave m                                |                                                 | ACK DIL                      |                    |                       |                      |                 |

|                         | 1 = Read                                                   |                                                 |                              |                    |                       |                      |                 |

|                         | 0 = Write<br>In I <sup>2</sup> C Master r                  | node:                                           |                              |                    |                       |                      |                 |

|                         | 1 = Transmit                                               | is in progress                                  |                              |                    |                       |                      |                 |

|                         |                                                            | is not in progress                              | SEN, PEN, RC                 | EN. or ACKEN w     | ill indicate if the N | ISSP is in Idle mod  | de.             |

| bit 1                   | -                                                          | dress bit (10-bit l <sup>2</sup>                |                              |                    |                       |                      |                 |

|                         | 1 = Indicates the                                          | nat the user needs                              | to update the a              | address in the SS  | PADD register         |                      |                 |

| <b>h</b> it 0           |                                                            | bes not need to be                              | updated                      |                    |                       |                      |                 |

| bit 0                   | BF: Buffer Full<br>Receive (SPL a                          | Status bit<br>ind I <sup>2</sup> C modes):      |                              |                    |                       |                      |                 |

|                         | 1 = Receive co                                             | mplete, SSPBUF                                  |                              |                    |                       |                      |                 |

|                         |                                                            | ot complete, SSPB                               | UF is empty                  |                    |                       |                      |                 |

|                         | <u>Transmit (I<sup>2</sup>C r</u><br>1 = Data transi       | <u>node only):</u><br>nit in progress (do       | es not include               | the ACK and Stor   | bits), SSPBUF i       | s full               |                 |

|                         | 0 = Data transi                                            |                                                 |                              |                    |                       |                      |                 |

#### 13.4.1.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit BF is set.

- c) An ACK pulse is generated.

- MSSP interrupt flag bit, SSPIF of the PIR1 register, is set on the falling edge of the ninth SCL pulse (interrupt is generated, if enabled).

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSb) of the first address byte specify if this is a 10-bit address. The R/W bit (SSPSTAT register) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal `1111 0 A9 A8 0', where A9 and A8 are the two MSb's of the address.

The sequence of events for 10-bit addressing is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bit SSPIF of the PIR1 register and bits BF and UA of the SSPSTAT register are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### 13.4.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT register) is set, or bit SSPOV (SSPCON register) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF of the PIR1 register must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 13.4.1.3 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON register). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 13-8).

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. When the ACK is latched by the slave, the slave logic is reset and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Pin RC3/SCK/SCL should be enabled by setting bit CKP.

### 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

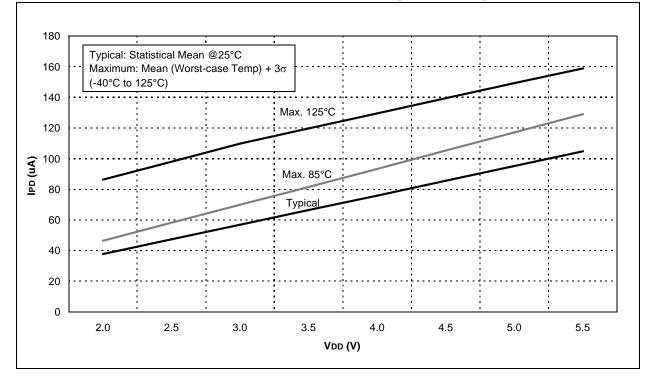

#### 17.2 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHARACTERISTICS |                                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |            |                                    |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|------------------------------------|

| Param<br>No.       | Device Characteristics                 | Min.                                                                                                                                                                                    | Тур† | Max. | Units | Conditions |                                    |

|                    |                                        |                                                                                                                                                                                         |      |      |       | Vdd        | Note                               |

| D010               | Supply Current (IDD) <sup>(1, 2)</sup> | _                                                                                                                                                                                       | 13   | 19   | μA    | 2.0        | Fosc = 32 kHz                      |

|                    |                                        |                                                                                                                                                                                         | 22   | 30   | μΑ    | 3.0        | LP Oscillator mode                 |

|                    |                                        |                                                                                                                                                                                         | 33   | 60   | μΑ    | 5.0        |                                    |

| D011*              |                                        | _                                                                                                                                                                                       | 180  | 250  | μΑ    | 2.0        | Fosc = 1 MHz<br>XT Oscillator mode |

|                    |                                        |                                                                                                                                                                                         | 290  | 400  | μΑ    | 3.0        |                                    |

|                    |                                        |                                                                                                                                                                                         | 490  | 650  | μΑ    | 5.0        |                                    |

| D012               |                                        | _                                                                                                                                                                                       | 280  | 380  | μΑ    | 2.0        | Fosc = 4 MHz<br>XT Oscillator mode |

|                    |                                        |                                                                                                                                                                                         | 480  | 670  | μΑ    | 3.0        |                                    |

|                    |                                        |                                                                                                                                                                                         | 0.9  | 1.4  | mA    | 5.0        |                                    |

| D013*              |                                        |                                                                                                                                                                                         | 170  | 295  | μΑ    | 2.0        | Fosc = 1 MHz<br>EC Oscillator mode |

|                    |                                        | _                                                                                                                                                                                       | 280  | 480  | μΑ    | 3.0        |                                    |

|                    |                                        |                                                                                                                                                                                         | 470  | 690  | μΑ    | 5.0        |                                    |

| D014               |                                        |                                                                                                                                                                                         | 290  | 450  | μΑ    | 2.0        | Fosc = 4 MHz                       |

|                    |                                        |                                                                                                                                                                                         | 490  | 720  | μΑ    | 3.0        | EC Oscillator mode                 |

|                    |                                        |                                                                                                                                                                                         | 0.85 | 1.3  | mA    | 5.0        |                                    |

| D015               |                                        |                                                                                                                                                                                         | 8    | 20   | μΑ    | 2.0        | Fosc = 31 kHz                      |

|                    |                                        |                                                                                                                                                                                         | 16   | 40   | μΑ    | 3.0        | LFINTOSC mode                      |

|                    |                                        |                                                                                                                                                                                         | 31   | 65   | μΑ    | 5.0        |                                    |

| D016*              |                                        |                                                                                                                                                                                         | 416  | 520  | μΑ    | 2.0        | Fosc = 4 MHz                       |

|                    |                                        |                                                                                                                                                                                         | 640  | 840  | μΑ    | 3.0        | HFINTOSC mode                      |

|                    |                                        |                                                                                                                                                                                         | 1.13 | 1.6  | mA    | 5.0        |                                    |

| D017               |                                        |                                                                                                                                                                                         | 0.65 | 0.9  | mA    | 2.0        | Fosc = 8 MHz                       |

|                    |                                        |                                                                                                                                                                                         | 1.01 | 1.3  | mA    | 3.0        | HFINTOSC mode                      |

|                    |                                        | —                                                                                                                                                                                       | 1.86 | 2.3  | mA    | 5.0        |                                    |

| D018               |                                        | _                                                                                                                                                                                       | 340  | 580  | μΑ    | 2.0        | Fosc = 4 MHz                       |

|                    |                                        |                                                                                                                                                                                         | 550  | 900  | μΑ    | 3.0        | EXTRC mode <sup>(3)</sup>          |

|                    |                                        |                                                                                                                                                                                         | 0.92 | 1.4  | mA    | 5.0        |                                    |

| D019               |                                        |                                                                                                                                                                                         | 3.8  | 4.7  | mA    | 4.5        | Fosc = 20 MHz                      |

|                    |                                        | _                                                                                                                                                                                       | 4.0  | 4.8  | mA    | 5.0        | HS Oscillator mode                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

# PIC16F882/883/884/886/887

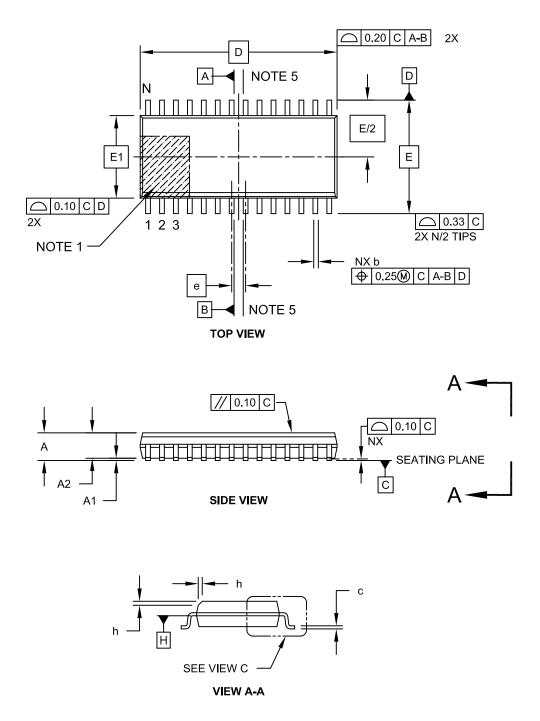

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support