#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f883-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                      | File                      |                                 | File        |                                 | File         |                       | File         |

|----------------------|---------------------------|---------------------------------|-------------|---------------------------------|--------------|-----------------------|--------------|

|                      | Address                   |                                 | Address     |                                 | Address      |                       | Addres       |

| Indirect addr. (1)   | 00h                       | Indirect addr. (1)              | 80h         | Indirect addr. (1)              | 100h         | Indirect addr. (1)    | 180h         |

| TMR0                 | 01h                       | OPTION_REG                      | 81h         | TMR0                            | 101h         | OPTION_REG            | 181h         |

| PCL                  | 02h                       | PCL                             | 82h         | PCL                             | 102h         | PCL                   | 182h         |

| STATUS               | 03h                       | STATUS                          | 83h         | STATUS                          | 103h         | STATUS                | 183h         |

| FSR                  | 04h                       | FSR                             | 84h         | FSR                             | 104h         | FSR                   | 184h         |

| PORTA                | 05h                       | TRISA                           | 85h         | WDTCON                          | 105h         | SRCON                 | 185h         |

| PORTB                | 06h                       | TRISB                           | 86h         | PORTB                           | 106h         | TRISB                 | 186h         |

| PORTC                | 07h                       | TRISC                           | 87h         | CM1CON0                         | 107h         | BAUDCTL               | 187h         |

| PORTD <sup>(2)</sup> | 08h                       | TRISD <sup>(2)</sup>            | 88h         | CM2CON0                         | 108h         | ANSEL                 | 188h         |

| PORTE                | 09h                       | TRISE                           | 89h         | CM2CON1                         | 109h         | ANSELH                | 189h         |

| PCLATH               | 0Ah                       | PCLATH                          | 8Ah         | PCLATH                          | 10Ah         | PCLATH                | 18Ah         |

| INTCON               | 0Bh                       | INTCON                          | 8Bh         | INTCON                          | 10Bh         | INTCON                | 18Bh         |

| PIR1                 | 0Ch                       | PIE1                            | 8Ch         | EEDAT                           | 10Ch         | EECON1                | 18Ch         |

| PIR2                 | 0Dh                       | PIE2                            | 8Dh         | EEADR                           | 10Dh         | EECON2 <sup>(1)</sup> | 18Dh         |

| TMR1L                | 0Eh                       | PCON                            | 8Eh         | EEDATH                          | 10Eh         | Reserved              | 18Eh         |

| TMR1H                | 0Fh                       | OSCCON                          | 8Fh         | EEADRH                          | 10Fh         | Reserved              | 18Fh         |

| T1CON                | 10h                       | OSCTUNE                         | 90h         |                                 | 110h         | - Hoborrou            | 190h         |

| TMR2                 | 11h                       | SSPCON2                         | 91h         |                                 | 111h         |                       | 191h         |

| T2CON                | 12h                       | PR2                             | 92h         |                                 | 112h         |                       | 192h         |

| SSPBUF               | 13h                       | SSPADD                          | 93h         |                                 | 112h         |                       | 193h         |

| SSPCON               | 14h                       | SSPSTAT                         | 94h         |                                 | 114h         |                       | 194h         |

| CCPR1L               | 15h                       | WPUB                            | 95h         |                                 | 115h         |                       | 195h         |

| CCPR1H               | 16h                       | IOCB                            | 96h         |                                 | 116h         |                       | 196h         |

| CCP1CON              | 17h                       | VRCON                           | 97h         |                                 | 117h         |                       | 197h         |

| RCSTA                | 18h                       | TXSTA                           | 98h         |                                 | 118h         |                       | 198h         |

| TXREG                | 19h                       | SPBRG                           | 99h         |                                 | 119h         |                       | 199h         |

| RCREG                | 1Ah                       | SPBRGH                          | 9Ah         |                                 | 11Ah         |                       | 19Ah         |

| CCPR2L               | 1Bh                       | PWM1CON                         | 9Bh         |                                 | 11Bh         |                       | 19Bh         |

| CCPR2H               | 1Ch                       | ECCPAS                          | 9Ch         |                                 | 11Ch         |                       | 19Ch         |

| CCP2CON              | 1Dh                       | PSTRCON                         | 9Dh         |                                 | 11Dh         |                       | 19Dh         |

| ADRESH               | 1Eh                       | ADRESL                          | 9Eh         |                                 | 11Eh         |                       | 19Eh         |

| ADCON0               | 1Fh                       | ADICON1                         | 9Eh         |                                 | 11Fh         |                       | 19Eh         |

| ADOONO               | 20h                       | ADOONT                          | A0h         |                                 | 120h         |                       | 1A0h         |

| General<br>Purpose   | 2011                      | General<br>Purpose<br>Registers | 71011       | General<br>Purpose<br>Registers | 12011        |                       |              |

| Registers            |                           | 80 Bytes                        |             | 80 Bytes                        |              |                       |              |

| 96 Bytes             |                           |                                 | EFh         |                                 | 16Fh         |                       | 1EFh         |

|                      | 7Fh                       | accesses<br>70h-7Fh             | F0h<br>FFh  | accesses<br>70h-7Fh             | 170h<br>17Fh | accesses<br>70h-7Fh   | 1F0h<br>1FFh |

| Bank 0               | ı                         | Bank 1                          |             | Bank 2                          |              | Bank 3                |              |

|                      | ed data me<br>physical re | emory locations, re<br>gister.  | ead as '0'. |                                 |              |                       |              |

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (GPR and SFR)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 15.0 "Instruction Set Summary"

| Note 1: | The C and DC bits operate as a Borrow      |

|---------|--------------------------------------------|

|         | and Digit Borrow out bit, respectively, in |

|         | subtraction.                               |

## **REGISTER DEFINITIONS: STATUS**

#### REGISTER 2-1: STATUS: STATUS REGISTER

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

|-------|-------|-------|-----|-----|-------|-------------------|------------------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |       |       |     |     |       |                   | bit 0            |

| Legend:                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7       | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h-1FFh)<br>C = Bank 0, 4 (00h - 1FFh) |

|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 1.1.0.5     | 0 = Bank 0, 1 (00h-FFh)                                                                                                 |

| bit 6-5     | <b>RP&lt;1:0&gt;:</b> Register Bank Select bits (used for direct addressing)                                            |

|             | 00 = Bank 0 (00h-7Fh)<br>01 = Bank 1 (80h-FFh)                                                                          |

|             | 10 = Bank  2 (100h-17Fh)                                                                                                |

|             | 11 = Bank 3 (180h-1FFh)                                                                                                 |

| bit 4       | TO: Time-out bit                                                                                                        |

|             | 1 = After power-up, CLRWDT instruction or SLEEP instruction                                                             |

|             | 0 = A WDT time-out occurred                                                                                             |

| bit 3       | PD: Power-down bit                                                                                                      |

|             | 1 = After power-up or by the CLRWDT instruction                                                                         |

|             | 0 = By execution of the SLEEP instruction                                                                               |

| bit 2       | Z: Zero bit                                                                                                             |

|             | 1 = The result of an arithmetic or logic operation is zero                                                              |

|             | 0 = The result of an arithmetic or logic operation is not zero                                                          |

| bit 1       | DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                     |

|             | 1 = A carry-out from the 4th low-order bit of the result occurred                                                       |

|             | 0 = No carry-out from the 4th low-order bit of the result                                                               |

| bit 0       | C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                            |

|             | 1 = A carry-out from the Most Significant bit of the result occurred                                                    |

|             | 0 = No carry-out from the Most Significant bit of the result occurred                                                   |

| Note 1: For | Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of th                        |

|             | erand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order l                 |

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

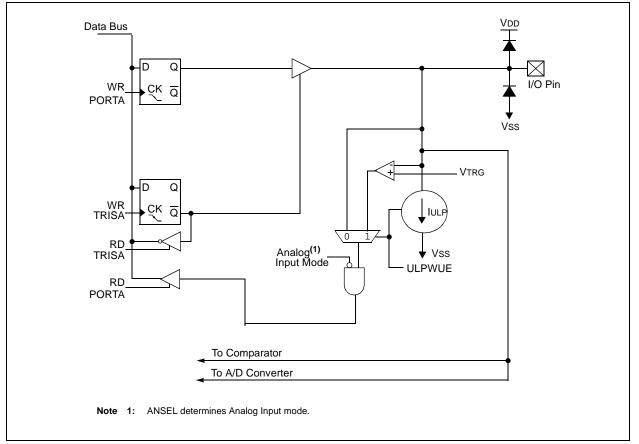

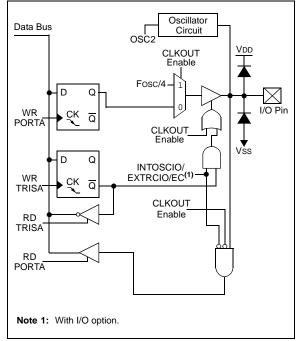

## 3.2.3 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D Converter (ADC), refer to the appropriate section in this data sheet.

### 3.2.3.1 RA0/AN0/ULPWU/C12IN0-

Figure 3-1 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a negative analog input to Comparator C1 or C2

- an analog input for the Ultra Low-Power Wake-up

FIGURE 3-1: BLOCK DIAGRAM OF RA0

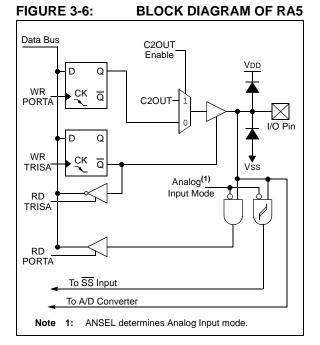

## 3.2.3.6 RA5/AN4/SS/C2OUT

Figure 3-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a slave select input

- a digital output from Comparator C2

### 3.2.3.7 RA6/OSC2/CLKOUT

Figure 3-7 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- a clock output

## 8.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in the **Section 17.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE2 register

and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 8.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their Off states.

## **REGISTER DEFINITIONS: COMPARATOR C1**

#### REGISTER 8-1: CM1CON0: COMPARATOR C1 CONTROL REGISTER 0

| R/W-0       | R-0   | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-----|-------|-------|-------|

| C10N        | C1OUT | C10E  | C1POL | —   | C1R   | C1CH1 | C1CH0 |

| bit 7 bit 0 |       |       |       |     |       |       |       |

| Legend:           |                                                                     |                                                                                                                                                                                                                    |                               |                    |

|-------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|

| R = Reada         | able bit                                                            | W = Writable bit                                                                                                                                                                                                   | U = Unimplemented bit         | , read as '0'      |

| -n = Value at POR |                                                                     | '1' = Bit is set                                                                                                                                                                                                   | '0' = Bit is cleared          | x = Bit is unknown |

| bit 7             | 1 = Com                                                             | Comparator C1 Enable bit<br>parator C1 is enabled<br>parator C1 is disabled                                                                                                                                        |                               |                    |

| oit 6             | <u>If C1POI</u><br>C1OUT :<br>C1OUT :<br><u>If C1POI</u><br>C1OUT : | Comparator C1 Output bit<br><u>= 1 (inverted polarity):</u><br>= 0 when C1VIN+ > C1VIN-<br>= 1 when C1VIN+ < C1VIN-<br><u>= 0 (non-inverted polarity):</u><br>= 1 when C1VIN+ > C1VIN-<br>= 0 when C1VIN+ < C1VIN- |                               |                    |

| oit 5             | 1 = C1O                                                             | Comparator C1 Output Enable<br>UT is present on the C1OUT<br>UT is internal only                                                                                                                                   |                               |                    |

| bit 4             | 1 = C1O                                                             | Comparator C1 Output Pola<br>UT logic is inverted<br>UT logic is not inverted                                                                                                                                      | rity Select bit               |                    |

| oit 3             | Unimple                                                             | mented: Read as '0'                                                                                                                                                                                                |                               |                    |

| bit 2             | 1 = C1V                                                             | mparator C1 Reference Sele<br>N+ connects to C1VREF outp<br>N+ connects to C1IN+ pin                                                                                                                               | · · · · ·                     |                    |

| bit 1-0           | 00 = C12<br>01 = C12<br>10 = C12                                    | :0>: Comparator C1 Channe<br>2IN0- pin of C1 connects to C<br>2IN1- pin of C1 connects to C<br>2IN2- pin of C1 connects to C<br>2IN2- pin of C1 connects to C                                                      | C1 Vin-<br>C1 Vin-<br>C1 Vin- |                    |

Note 1: Comparator output requires the following three conditions: C1OE = 1, C1ON = 1 and corresponding port TRIS bit = 0.

| R/W-0                                                                | U-0                                                                                              | R/W-0            | R/W-0 | U-0              | U-0  | U-0             | U-0   |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|-------|------------------|------|-----------------|-------|--|

| ADFM                                                                 |                                                                                                  | VCFG1            | VCFG0 | —                | —    | —               | —     |  |

| bit 7                                                                |                                                                                                  |                  |       |                  |      |                 | bit 0 |  |

| r                                                                    |                                                                                                  |                  |       |                  |      |                 |       |  |

| Legend:                                                              |                                                                                                  |                  |       |                  |      |                 |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                  |                  |       |                  |      |                 |       |  |

| -n = Value at F                                                      | POR                                                                                              | '1' = Bit is set |       | '0' = Bit is cle | ared | x = Bit is unkr | nown  |  |

| bit 7                                                                | bit 7 ADFM: A/D Conversion Result Format Select bit<br>1 = Right justified<br>0 = Left justified |                  |       |                  |      |                 |       |  |

| bit 6                                                                | Unimplemen                                                                                       | ted: Read as '   | 0'    |                  |      |                 |       |  |

| bit 5                                                                | VCFG1: Volta                                                                                     | ge Reference     | bit   |                  |      |                 |       |  |

|                                                                      | 1 = VREF- pin<br>0 = VSS                                                                         |                  |       |                  |      |                 |       |  |

| bit 4                                                                | VCFG0: Volta                                                                                     | ge Reference     | bit   |                  |      |                 |       |  |

|                                                                      | 1 = VREF+ pin<br>0 = VDD                                                                         | 1                |       |                  |      |                 |       |  |

| bit 3-0                                                              | Unimplemen                                                                                       | ted: Read as '   | 0'    |                  |      |                 |       |  |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

An example of the complete 8-word write sequence is shown in Example 10-4. The initial address is loaded into the EEADRH and EEADR register pair; the eight words of data are loaded using indirect addressing.

#### EXAMPLE 10-4: WRITING TO FLASH PROGRAM MEMORY

```

*****

; This write routine assumes the following:

A valid starting address (the least significant bits = '000')

;

is loaded in ADDRH:ADDRL

;

;

ADDRH, ADDRL and DATADDR are all located in data memory

;

BANKSEL EEADRH

MOVF

ADDRH,W

; Load initial address

MOVWF

EEADRH

MOVF

ADDRL,W

MOVWF

EEADR

DATAADDR,W ; Load initial data address

MOVF

MOVWF FSR

LOOP

MOVF

INDF,W

; Load first data byte into lower

;

MOVWF EEDATA

; Next byte

INCE

FSR,F

; Load second data byte into upper

MOVF

INDF,W

MOVWF

EEDATH

INCF

FSR,F

BANKSEL EECON1

EECON1, EEPGD ; Point to program memory

BSF

EECON1,WREN ; Enable writes

BSF

BCF

INTCON,GIE ; Disable interrupts (if using)

BTFSC INTCON, GIE ; See AN576

GOTO

$-2

Required Sequence

;

MOVLW

55h

; Start of required write sequence:

EECON2

MOVWF

; Write 55h

0AAh

MOVLW

;

MOVWF EECON2

; Write OAAh

BSF

EECON1,WR ; Set WR bit to begin write

NOP

; Required to transfer data to the buffer

NOP

; registers

BCF

EECON1,WREN ; Disable writes

BSF

INTCON,GIE ; Enable interrupts (comment out if not using interrupts)

BANKSEL EEADR

EEADR, W

MOVF

; Increment address

INCF

EEADR, F

; Indicates when sixteen words have been programmed

ANDLW

0x0F

SUBLW

; 0x0F = 16 words

0x0F

; 0x0B = 12 words (PIC16F884/883/882 only)

; 0x07 = 8 words

0x03 = 4 \text{ words}(\text{PIC16F884}/883/882 \text{ only})

;

BTFSS

STATUS,Z

; Exit on a match,

GOTO

LOOP

; Continue if more data needs to be written

```

#### 11.6.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Table 11-5.

| Note: | The associated TRIS bits must be set to      |

|-------|----------------------------------------------|

|       | output ('0') to enable the pin output driver |

|       | in order to see the PWM signal on the pin.   |

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.6.4** "**Enhanced PWM Auto-Shutdown Mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

## **REGISTER DEFINITIONS: PULSE STEERING CONTROL**

### REGISTER 11-5: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>

| U-0         | U-0 | U-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------------|-----|-----|---------|-------|-------|-------|-------|

| —           | —   | —   | STRSYNC | STRD  | STRC  | STRB  | STRA  |

| bit 7 bit 0 |     |     |         |       |       |       |       |

|             |     |     |         |       |       |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| hit 7 E | Unimplemented, Dood op (0)                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 7-5 | Unimplemented: Read as '0'                                                               |

| bit 4   | STRSYNC: Steering Sync bit                                                               |

|         | 1 = Output steering update occurs on next PWM period                                     |

|         | 0 = Output steering update occurs at the beginning of the instruction cycle boundary     |

| bit 3   | STRD: Steering Enable bit D                                                              |

|         | 1 = P1D pin has the PWM waveform with polarity control from CCPxM<1:0>                   |

|         | 0 = P1D pin is assigned to port pin                                                      |

| bit 2   | STRC: Steering Enable bit C                                                              |

|         | 1 = P1C pin has the PWM waveform with polarity control from CCPxM<1:0>                   |

|         | 0 = P1C pin is assigned to port pin                                                      |

| bit 1   | STRB: Steering Enable bit B                                                              |

|         | 1 = P1B pin has the PWM waveform with polarity control from CCPxM<1:0>                   |

|         | 0 = P1B pin is assigned to port pin                                                      |

| bit 0   | STRA: Steering Enable bit A                                                              |

|         | 1 = P1A pin has the PWM waveform with polarity control from CCPxM<1:0>                   |

|         | 0 = P1A pin is assigned to port pin                                                      |

| Note 1. | The DWM Steering mode is evoluble only when the CCD4CON register bits CCD4M (2:2) 11 and |

## Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

Logondi

## 12.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

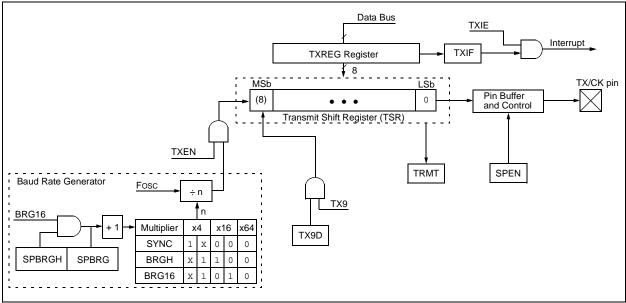

Block diagrams of the EUSART transmitter and receiver are shown in Figure 12-1 and Figure 12-2.

#### FIGURE 12-1: EUSART TRANSMIT BLOCK DIAGRAM

### 12.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 12-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 12.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 12-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 12.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

- Note 1: When the SPEN bit is set the RX/DT I/O pin is automatically configured as an input, regardless of the state of the corresponding TRIS bit and whether or not the EUSART receiver is enabled. The RX/DT pin data can be read via a normal PORT read but PORT latch data output is precluded.

- 2: The TXIF transmitter interrupt flag is set when the TXEN enable bit is set.

#### 12.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 12.1.1.3 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

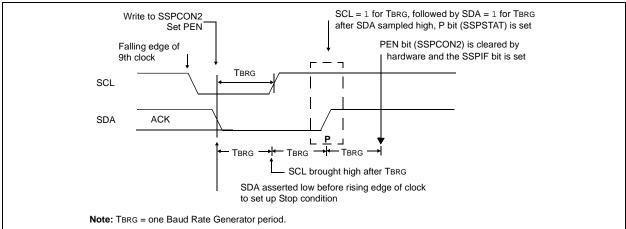

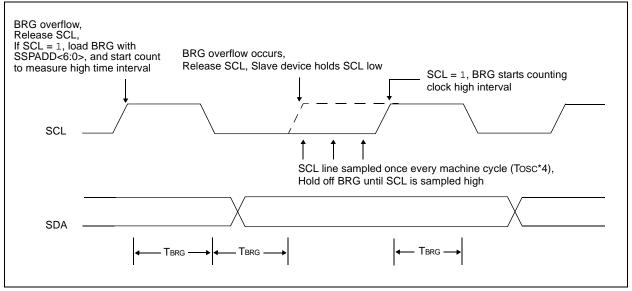

#### 13.4.12 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 13-19).

#### 13.4.13 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 13.4.14 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### FIGURE 13-19: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

#### 13.4.17 SSP MASK REGISTER

An SSP Mask (SSPMSK) register is available in  $I^2C$ Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit in the SSPSR register a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

This register must be initiated prior to setting SSPM<3:0> bits to select the  $I^2C$  Slave mode (7-bit or 10-bit address).

This register can only be accessed when the appropriate mode is selected by bits (SSPM<3:0> of SSPCON).

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

| R/W-1        | R/W-1                                                                                            | R/W-1                          | R/W-1           | R/W-1                         | R/W-1                                         | R/W-1         | R/W-1               |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------|--------------------------------|-----------------|-------------------------------|-----------------------------------------------|---------------|---------------------|--|--|--|--|--|

| MSK7         | MSK6                                                                                             | MSK5                           | MSK4            | MSK3                          | MSK2                                          | MSK1          | MSK0 <sup>(2)</sup> |  |  |  |  |  |

| bit 7        |                                                                                                  |                                |                 |                               |                                               |               | bit 0               |  |  |  |  |  |

|              |                                                                                                  |                                |                 |                               |                                               |               |                     |  |  |  |  |  |

| Legend:      |                                                                                                  |                                |                 |                               |                                               |               |                     |  |  |  |  |  |

| R = Readat   | ole bit                                                                                          | W = Writable                   | bit             | U = Unimpler                  | mented bit, read                              | as '0'        |                     |  |  |  |  |  |

| -n = Value a | at POR                                                                                           | '1' = Bit is set               |                 | '0' = Bit is cle              | x = Bit is unkr                               | nown          |                     |  |  |  |  |  |

|              |                                                                                                  |                                |                 |                               |                                               |               |                     |  |  |  |  |  |

| bit 7-1      | MSK<7:1>: N                                                                                      | lask bits                      |                 |                               |                                               |               |                     |  |  |  |  |  |

|              |                                                                                                  |                                |                 |                               | <n> to detect I<sup>2</sup> address match</n> | C address mat | tch                 |  |  |  |  |  |

| bit 0        | <b>MSK&lt;0&gt;:</b> Ma:                                                                         | sk bit for I <sup>2</sup> C SI | ave mode, 10    | 0-bit Address <sup>(2)</sup>  | )                                             |               |                     |  |  |  |  |  |

|              | I <sup>2</sup> C Slave mode, 10-bit Address (SSPM<3:0> = 0111):                                  |                                |                 |                               |                                               |               |                     |  |  |  |  |  |

|              | 1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match |                                |                 |                               |                                               |               |                     |  |  |  |  |  |

|              | 0 = The rece                                                                                     | ived address bi                | it 0 is not use | ed to detect I <sup>2</sup> C | address match                                 |               |                     |  |  |  |  |  |

#### REGISTER 13-4: SSPMSK: SSP MASK REGISTER<sup>(1)</sup>

**Note 1:** When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register.

2: In all other SSP modes, this bit has no effect.

#### 14.2.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired, then OST is activated after the PWRT time-out has expired. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in EC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figures 14-4, 14-5 and 14-6 depict time-out sequences. The device can execute code from the INTOSC while OST is active by enabling Two-Speed Start-up or Fail-Safe Monitor (see Section 4.7.2 "Two-Speed Start-up Sequence" and Section 4.8 "Fail-Safe Clock Monitor").

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then, bringing MCLR high will begin execution immediately (see Figure 14-5). This is useful for testing purposes or to synchronize more than one PIC16F882/883/884/886/887 device operating in parallel.

Table 14-5 shows the Reset conditions for some special registers, while Table 14-4 shows the Reset conditions for all the registers.

#### 14.2.6 POWER CONTROL (PCON) REGISTER

The Power Control register PCON (address 8Eh) has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out Reset).  $\overline{\text{BOR}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word Register 1).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.2.2 "Ultra Low-Power Wake-up" and Section 14.2.4 "Brown-out Reset (BOR)".

| Occillator Configuration | Powe                   | er-up            | Brown-o                | ut Reset    | Wake-up from |

|--------------------------|------------------------|------------------|------------------------|-------------|--------------|

| Oscillator Configuration | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0       | PWRTE = 1   | Sleep        |

| XT, HS, LP               | TPWRT +<br>1024 • Tosc | 1024 • Tosc      | TPWRT +<br>1024 • Tosc | 1024 • Tosc | 1024 • Tosc  |

| LP, T1OSCIN = 1          | TPWRT                  | —                | TPWRT                  | _           | —            |

| RC, EC, INTOSC           | TPWRT                  | —                | TPWRT                  | _           | —            |

#### TABLE 14-1: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 14-2: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|--|

| 0   | х   | 1  | 1  | Power-on Reset                     |  |  |  |  |

| u   | 0   | 1  | 1  | Brown-out Reset                    |  |  |  |  |

| u   | u   | 0  | u  | WDT Reset                          |  |  |  |  |

| u   | u   | 0  | 0  | WDT Wake-up                        |  |  |  |  |

| u   | u   | u  | u  | MCLR Reset during normal operation |  |  |  |  |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |  |  |  |

**Legend:** u = unchanged, x = unknown

#### TABLE 14-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on<br>Page |

|--------|-------|-------|--------|--------|-------|-------|-------|-------|---------------------|

| PCON   |       | _     | ULPWUE | SBOREN | _     | _     | POR   | BOR   | 37                  |

| STATUS | IRP   | RP1   | RPO    | TO     | PD    | Z     | DC    | С     | 30                  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by BOR.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

## **15.0 INSTRUCTION SET SUMMARY**

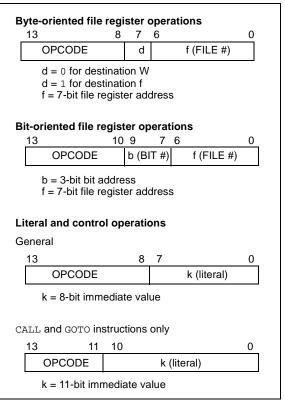

The PIC16F882/883/884/886/887 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 15.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

### 17.1 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHA                    | ARACTER | RISTICS                                                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |      |                                                        |  |

|---------------------------|---------|------------------------------------------------------------------|------------------------------------------------------|-----|-----|------|--------------------------------------------------------|--|

| Param Sym. Characteristic |         |                                                                  | Min. Typ† Max. Units Con                             |     |     |      | Conditions                                             |  |

|                           | Vdd     | Supply Voltage                                                   | 2.0                                                  | —   | 5.5 | V    | Fosc < = 8 MHz: HFINTOSC, EC                           |  |

| D001                      |         |                                                                  | 2.0                                                  | —   | 5.5 | V    | Fosc < = 4 MHz                                         |  |

| D001C                     |         |                                                                  | 3.0                                                  | —   | 5.5 | V    | Fosc < = 10 MHz                                        |  |

| D001D                     |         |                                                                  | 4.5                                                  | —   | 5.5 | V    | Fosc < = 20 MHz                                        |  |

| D002*                     | Vdr     | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                                  | —   | —   | V    | Device in Sleep mode                                   |  |

| D003                      | VPOR    | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                    | Vss | —   | V    | See Section 14.2.1 "Power-on Reset (POR)" for details. |  |

| D004*                     |         |                                                                  | 0.05                                                 |     | _   | V/ms | See Section 14.2.1 "Power-on Reset (POR)" for details. |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

### 17.5 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended) (Continued)

| DC CH        | ARACTE | RISTICS                                                             | Standard Ope<br>Operating tem | nditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |      |       |                                                                                                     |

|--------------|--------|---------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.   | Characteristic                                                      | Min.                          | Тур†                                                                                                                            | Max. | Units | Conditions                                                                                          |

| D100         | IULP   | Ultra Low-Power Wake-Up<br>Current                                  | _                             | 200                                                                                                                             | _    | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |

|              |        | Capacitive Loading Specs<br>on Output Pins                          |                               |                                                                                                                                 |      |       |                                                                                                     |

| D101*        | COSC2  | OSC2 pin                                                            | _                             | -                                                                                                                               | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                              |

| D101A<br>*   | Сю     | All I/O pins                                                        | _                             | —                                                                                                                               | 50   | pF    |                                                                                                     |

|              |        | Data EEPROM Memory                                                  |                               |                                                                                                                                 |      |       |                                                                                                     |

| D120         | ED     | Byte Endurance                                                      | 100K                          | 1M                                                                                                                              | _    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

| D120A        | ED     | Byte Endurance                                                      | 10K                           | 100K                                                                                                                            | _    | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |

| D121         | Vdrw   | VDD for Read/Write                                                  | VMIN                          | -                                                                                                                               | 5.5  | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage                                   |

| D122         | TDEW   | Erase/Write Cycle Time                                              | _                             | 5                                                                                                                               | 6    | ms    |                                                                                                     |

| D123         | Tretd  | Characteristic Retention                                            | 40                            | —                                                                                                                               | —    | Year  | Provided no other specifications are violated                                                       |

| D124         | Tref   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup> | 1M                            | 10M                                                                                                                             | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

|              |        | Program Flash Memory                                                |                               |                                                                                                                                 |      |       |                                                                                                     |

| D130         | Eр     | Cell Endurance                                                      | 10K                           | 100K                                                                                                                            | —    | E/W   | $-40^{\circ}C \leq TA \leq +85^{\circ}C$                                                            |

| D130A        | ED     | Cell Endurance                                                      | 1K                            | 10K                                                                                                                             | _    | E/W   | +85°C $\leq$ TA $\leq$ +125°C                                                                       |

| D131         | Vpr    | VDD for Read                                                        | Vmin                          | —                                                                                                                               | 5.5  | V     | VMIN = Minimum operating<br>voltage                                                                 |

| D132         | VPEW   | VDD for Row Erase/Write                                             | VMIN                          |                                                                                                                                 | 5.5  | V     |                                                                                                     |

|              |        | VDD for Bulk Erase Opera-<br>tions                                  | 4.5                           |                                                                                                                                 | 5.5  | V     |                                                                                                     |

| D133         | TPEW   | Erase/Write cycle time                                              | —                             | 2                                                                                                                               | 2.5  | ms    |                                                                                                     |

| D134         | Tretd  | Characteristic Retention                                            | 40                            | -                                                                                                                               | —    | Year  | Provided no other specifications are violated                                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.3.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

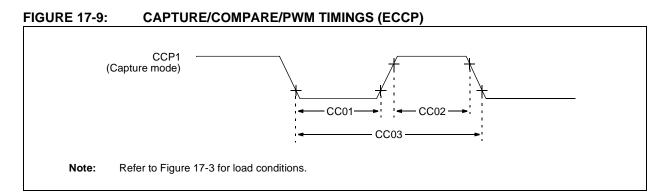

## TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |      |       |                                       |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|--|--|--|--|

| Param<br>No. | Sym.                                                                                                                 | Character            | ristic         | Min.                  | Тур† | Max. | Units | Conditions                            |  |  |  |  |

| CC01*        | TccL                                                                                                                 | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                       |  |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    |      | —    | ns    |                                       |  |  |  |  |

| CC02*        | TccH                                                                                                                 | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           |      | —    | ns    |                                       |  |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    |      | —    | ns    |                                       |  |  |  |  |

| CC03*        | TccP                                                                                                                 | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale<br>value (1, 4 or<br>16) |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 17-19: DC CHARACTERISTICS FOR IDD SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param | Device          | Min. | Тур. | Max. | Units |     | Condition                       |

|-------|-----------------|------|------|------|-------|-----|---------------------------------|

| No.   | Characteristics |      | тур. |      | Units | Vdd | Note                            |

| D001  | Vdd             | 2.1  | _    | 5.5  | V     | _   | Fosc $\leq$ 8 MHz: HFINTOSC, EC |

|       |                 | 2.1  | _    | 5.5  | V     |     | $Fosc \le 4 MHz$                |

## TABLE 17-20: DC CHARACTERISTICS FOR IPD SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param  | Device          |       |      | _    |      |     | Condition                                       |

|--------|-----------------|-------|------|------|------|-----|-------------------------------------------------|

| No.    | Characteristics | Units | Min. | Тур. | Max. | Vdd | Note                                            |

| D020E  | Power Down Base | _     | _    | 27   |      | 2.1 | IPD Base: WDT, BOR,                             |

|        | Current (IPD)   | —     |      | 29   | μA   | 3.0 | Comparators, VREF and                           |

|        |                 | —     | —    | 32   |      | 5.0 | T1osc disabled                                  |

| D021E  |                 | —     |      | 55   |      | 2.1 |                                                 |

|        |                 | —     |      | 59   | μA   | 3.0 | WDT Current                                     |

|        |                 | —     | _    | 69   |      | 5.0 |                                                 |

| D022E  |                 | _     | _    | 75   |      | 3.0 | BOR Current                                     |

|        |                 | _     | _    | 147  | μA   | 5.0 | BOR Current                                     |

| D023E  |                 | _     | _    | 73   |      | 2.1 |                                                 |

|        |                 | _     | _    | 117  | μΑ   | 3.0 | Comparator current, both<br>comparators enabled |

|        |                 | _     | _    | 235  |      | 5.0 |                                                 |

| D024E  |                 | _     | _    | 102  |      | 2.1 |                                                 |

|        |                 | _     | _    | 128  | μA   | 3.0 | CVREF current, high range                       |

|        |                 | —     |      | 170  |      | 5.0 |                                                 |

| D024AE |                 | —     | —    | 133  |      | 2.1 |                                                 |

|        |                 | —     |      | 167  | μA   | 3.0 | CVREF current, low range                        |

|        |                 | —     |      | 222  |      | 5.0 |                                                 |

| D025E  |                 | —     | _    | 36   |      | 2.1 |                                                 |

|        |                 | —     |      | 41   | μA   | 3.0 | T1osc current, 32 kHz                           |

|        |                 | —     |      | 47   |      | 5.0 |                                                 |

| D026E  |                 | —     | —    | 22   | ۸    | 3.0 | Analog-to-Digital current,                      |

|        |                 | _     |      | 24   | μA   | 5.0 | no conversion in progress                       |

| D027E  |                 | _     |      | 189  |      | 3.0 | VP6 current (Fixed Voltage                      |

|        |                 | —     | —    | 250  | μA   | 5.0 | Reference)                                      |

## TABLE 17-21: LEAKAGE CURRENT SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym Characteristic                                          |                                                            | Min. | Тур. | Max. | Units | Conditions                               |

|--------------|-------------------------------------------------------------|------------------------------------------------------------|------|------|------|-------|------------------------------------------|

| D061         | 0061 IIL Input Leakage Current <sup>(1)</sup><br>(RA3/MCLR) |                                                            | _    | ±0.5 | ±5.0 | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$ |

| D062         | lı∟                                                         | Input <u>Leaka</u> ge Current <sup>(2)</sup><br>(RA3/MCLR) | 50   | 250  | 400  | μA    | VDD = 5.0V                               |

**Note 1:** This specification applies when RA3/MCLR is configured as an input with the pull-up disabled. The leakage current for the RA3/MCLR pin is higher than for the standard I/O port pins.

2: This specification applies when RA3/MCLR is configured as the MCLR reset pin function with the weak pull-up enabled.

## 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

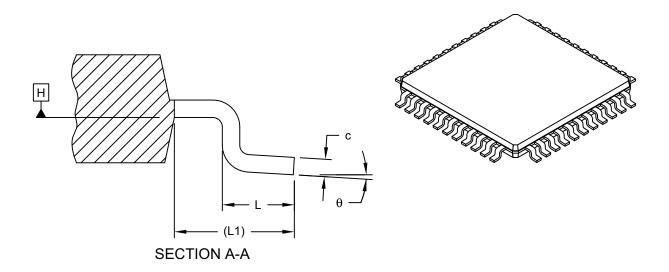

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Number of Leads          | N  | 44          |      |      |

| Lead Pitch               | е  | 0.80 BSC    |      |      |

| Overall Height           | Α  | -           | -    | 1.20 |

| Standoff                 | A1 | 0.05        | -    | 0.15 |

| Molded Package Thickness | A2 | 0.95        | 1.00 | 1.05 |

| Overall Width            | E  | 12.00 BSC   |      |      |

| Molded Package Width     | E1 | 10.00 BSC   |      |      |

| Overall Length           | D  | 12.00 BSC   |      |      |