Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f883-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F882/883/884/886/887

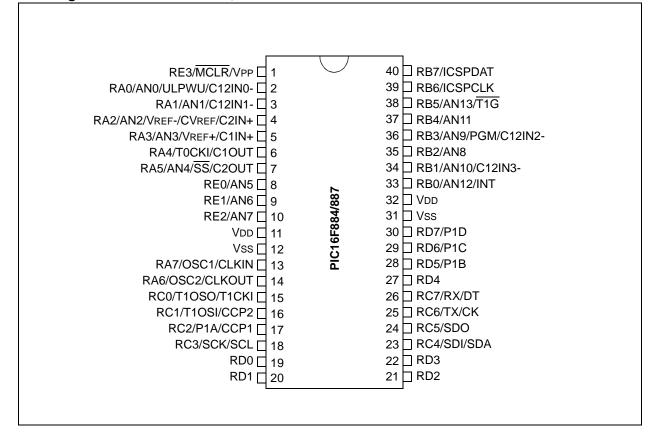

#### Pin Diagrams - PIC16F884/887, 40-Pin PDIP

© 2006-2015 Microchip Technology Inc.

### TABLE 1-2: PIC16F884/887 PINOUT DESCRIPTION (CONTINUED)

| Name                                                      | Function                         | Input<br>Type      | Output<br>Type  | Description                                                                                       |

|-----------------------------------------------------------|----------------------------------|--------------------|-----------------|---------------------------------------------------------------------------------------------------|

| RB4/AN11                                                  | RB4                              | TTL                | CMOS            | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                           | AN11                             | AN                 | _               | A/D Channel 11.                                                                                   |

| RB5/AN13/T1G                                              | RB5                              | TTL                | CMOS            | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                           | AN13                             | AN                 | _               | A/D Channel 13.                                                                                   |

|                                                           | T1G                              | ST                 | _               | Timer1 Gate input.                                                                                |

| RB6/ICSPCLK                                               | RB6                              | TTL                | CMOS            | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                           | ICSPCLK                          | ST                 | —               | Serial Programming Clock.                                                                         |

| RB7/ICSPDAT                                               | RB7                              | TTL                | CMOS            | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                           | ICSPDAT                          | ST                 | TTL             | ICSP™ Data I/O.                                                                                   |

| RC0/T1OSO/T1CKI                                           | RC0                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | T1OSO                            |                    | XTAL            | Timer1 oscillator output.                                                                         |

|                                                           | T1CKI                            | ST                 | _               | Timer1 clock input.                                                                               |

| RC1/T1OSI/CCP2                                            | RC1                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | T1OSI                            | XTAL               | _               | Timer1 oscillator input.                                                                          |

|                                                           | CCP2                             | ST                 | CMOS            | Capture/Compare/PWM2.                                                                             |

| RC2/P1A/CCP1                                              | RC2                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | P1A                              | ST                 | CMOS            | PWM output.                                                                                       |

|                                                           | CCP1                             |                    | CMOS            | Capture/Compare/PWM1.                                                                             |

| RC3/SCK/SCL                                               | RC3                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | SCK                              | ST                 | CMOS            | SPI clock.                                                                                        |

|                                                           | SCL                              | ST                 | OD              | I <sup>2</sup> C <sup>™</sup> clock.                                                              |

| RC4/SDI/SDA                                               | RC4                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | SDI                              | ST                 | —               | SPI data input.                                                                                   |

|                                                           | SDA                              | ST                 | OD              | I <sup>2</sup> C data input/output.                                                               |

| RC5/SDO                                                   | RC5                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | SDO                              | _                  | CMOS            | SPI data output.                                                                                  |

| RC6/TX/CK                                                 | RC6                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | ТХ                               | _                  | CMOS            | EUSART asynchronous transmit.                                                                     |

|                                                           | СК                               | ST                 | CMOS            | EUSART synchronous clock.                                                                         |

| RC7/RX/DT                                                 | RC7                              | ST                 | CMOS            | General purpose I/O.                                                                              |

|                                                           | RX                               | ST                 | —               | EUSART asynchronous input.                                                                        |

|                                                           | DT                               | ST                 | CMOS            | EUSART synchronous data.                                                                          |

| RD0                                                       | RD0                              | TTL                | CMOS            | General purpose I/O.                                                                              |

| RD1                                                       | RD1                              | TTL                | CMOS            | General purpose I/O.                                                                              |

| RD2                                                       | RD2                              | TTL                | CMOS            | General purpose I/O.                                                                              |

| RD3                                                       | RD3                              | TTL                | CMOS            | General purpose I/O.                                                                              |

| RD4                                                       | RD4                              | TTL                | CMOS            | General purpose I/O.                                                                              |

| RD5/P1B                                                   | RD5                              | TTL                | CMOS            | General purpose I/O.                                                                              |

|                                                           | P1B                              | _                  | CMOS            | PWM output.                                                                                       |

| RD6/P1C                                                   | RD6                              | TTL                | CMOS            | General purpose I/O.                                                                              |

|                                                           | P1C                              | _                  | CMOS            | PWM output.                                                                                       |

| Legend: AN = Analog ir<br>TTL = TTL com<br>HV = High Volt | nput or output<br>apatible input | CMOS<br>ST<br>XTAL | = CMO<br>= Schm | S compatible input or output OD = Open-Drain<br>itt Trigger input with CMOS levels                |

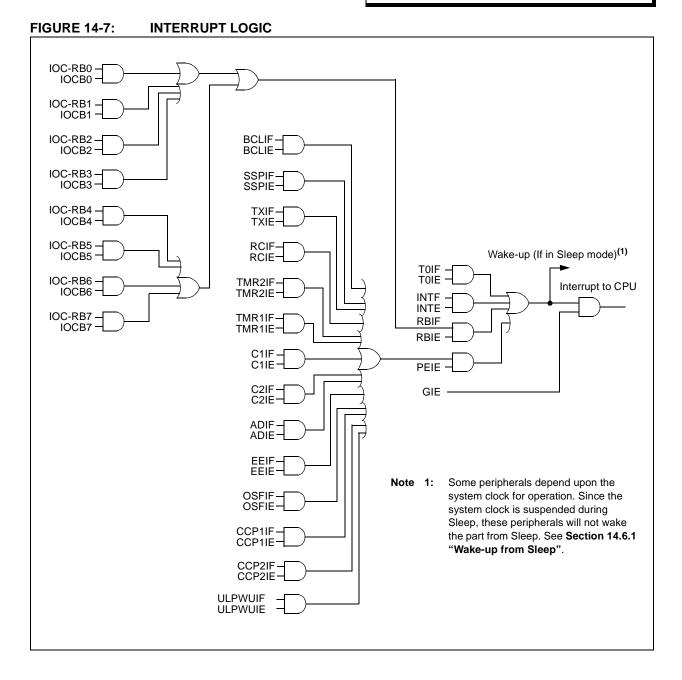

#### 2.2.2.3 INTCON Register

The INTCON register, shown in Register 2-3, is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### **REGISTER DEFINITIONS: INTERRUPT CONTROL** REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0               | R/W-0 | R/W-x |  |  |  |

|-------------|-------|-------|-------|---------------------|---------------------|-------|-------|--|--|--|

| GIE         | PEIE  | TOIE  | INTE  | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF  | RBIF  |  |  |  |

| bit 7 bit 0 |       |       |       |                     |                     |       |       |  |  |  |

|             |       |       |       |                     |                     |       |       |  |  |  |

| Legend:          |                                                                            |                       |                                          |                                      |

|------------------|----------------------------------------------------------------------------|-----------------------|------------------------------------------|--------------------------------------|

| R = Readable b   | it VV =                                                                    | Writable bit          | U = Unimplemented bit,                   | read as '0'                          |

| -n = Value at PC | DR '1'=                                                                    | Bit is set            | '0' = Bit is cleared                     | x = Bit is unknown                   |

| bit 7            | <b>GIE:</b> Global Interru<br>1 = Enables all unn<br>0 = Disables all inte | nasked interrupts     |                                          |                                      |

| bit 6            | <b>PEIE:</b> Peripheral In<br>1 = Enables all unn<br>0 = Disables all per  | nasked peripheral ir  | nterrupts                                |                                      |

| bit 5            | <b>TOIE:</b> Timer0 Overf<br>1 = Enables the Tim<br>0 = Disables the Tim   | ner0 interrupt        | e bit                                    |                                      |

| bit 4            | INTE: INT External<br>1 = Enables the IN<br>0 = Disables the IN            | F external interrupt  |                                          |                                      |

| bit 3            | <b>RBIE:</b> PORTB Cha<br>1 = Enables the PC<br>0 = Disables the PC        | RTB change interr     | upt                                      |                                      |

| bit 2            | <b>T0IF:</b> Timer0 Overf<br>1 = TMR0 register<br>0 = TMR0 register        |                       |                                          |                                      |

| bit 1            | INTF: INT External<br>1 = The INT extern<br>0 = The INT extern             | al interrupt occurred | d (must be cleared in software)<br>occur |                                      |

| bit 0            |                                                                            | one of the PORTB g    |                                          | d state (must be cleared in software |

**Note 1:** IOCB register must also be enabled.

2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

### 3.2 Additional Pin Functions

RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

#### 3.2.1 ANSEL REGISTER

The ANSEL register (Register 3-3) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 3-3: ANSEL: ANALOG SELECT REGISTER

| R/W-1               | R/W-1               | R/W-1               | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------------------|---------------------|---------------------|-------|-------|-------|-------|-------|

| ANS7 <sup>(2)</sup> | ANS6 <sup>(2)</sup> | ANS5 <sup>(2)</sup> | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7               |                     |                     |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 ANS<7:0>: Analog Select bits

Analog select between analog or digital function on pins AN<7:0>, respectively.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>.

- 0 = Digital I/O. Pin is assigned to port or special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: Not implemented on MemHigh.

# PIC16F882/883/884/886/887

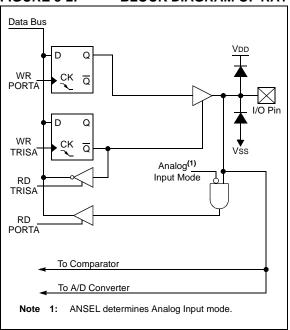

### 3.2.3.2 RA1/AN1/C12IN1-

Figure 3-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a negative analog input to Comparator C1 or C2

#### FIGURE 3-2: BLOCK DIAGRAM OF RA1

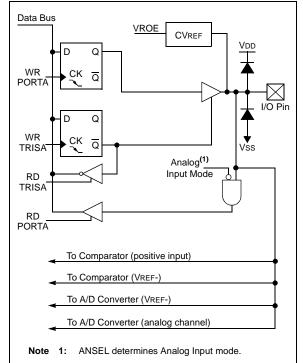

#### 3.2.3.3 RA2/AN2/VREF-/CVREF/C2IN+

Figure 3-3 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a negative voltage reference input for the ADC and CVREF

- a comparator voltage reference output

- a positive analog input to Comparator C2

#### FIGURE 3-3: BLOCK DIAGRAM OF RA2

### 4.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

4.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

# 4.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

### 4.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

**Note:** Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 4.4.1 "Oscillator Start-up Timer (OST)**"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

#### 4.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word Register 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Twospeed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

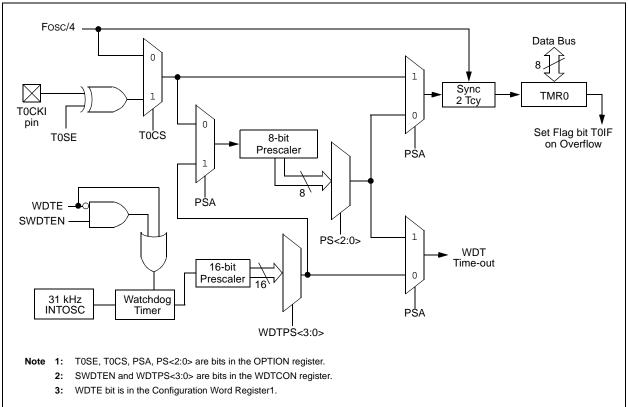

### 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

### 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

#### FIGURE 5-1: TIMER0/WDT PRESCALER BLOCK DIAGRAM

#### 8.8 Additional Comparator Features

There are three additional comparator features:

- Timer1 count enable (gate)

- Synchronizing output with Timer1

- Simultaneous read of comparator outputs

#### 8.8.1 COMPARATOR C2 GATING TIMER1

This feature can be used to time the duration or interval of analog events. Clearing the T1GSS bit of the CM2CON1 register will enable Timer1 to increment based on the output of Comparator C2. This requires that Timer1 is on and gating is enabled. See **Section 6.0 "Timer1 Module with Gate Control"** for details.

It is recommended to synchronize the comparator with Timer1 by setting the C2SYNC bit when the comparator is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if the comparator changes during an increment.

#### 8.8.2 SYNCHRONIZING COMPARATOR C2 OUTPUT TO TIMER1

The Comparator C2 output can be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 register. When enabled, the C2 output is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figures 8-2 and 8-3) and the Timer1 Block Diagram (Figure 6-1) for more information.

#### 8.8.3 SIMULTANEOUS COMPARATOR OUTPUT READ

The MC1OUT and MC2OUT bits of the CM2CON1 register are mirror copies of both comparator outputs. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

Note 1: Obtaining the status of C1OUT or C2OUT by reading CM2CON1 does not affect the comparator interrupt mismatch registers.

#### REGISTER 8-3: CM2CON1: COMPARATOR C2 CONTROL REGISTER 1

| R-0    | R-0    | R/W-0  | R/W-0  | U-0 | U-0 | R/W-1 | R/W-0  |

|--------|--------|--------|--------|-----|-----|-------|--------|

| MC1OUT | MC2OUT | C1RSEL | C2RSEL | —   |     | T1GSS | C2SYNC |

| bit 7  |        |        |        |     |     |       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | MC10UT: Mirror Copy of C10UT bit                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                         |

| bit 6   | MC2OUT: Mirror Copy of C2OUT bit                                                                                                                        |

| bit 5   | C1RSEL: Comparator C1 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C1VREF input of Comparator C1                                                                                                       |

|         | <ul> <li>0 = Absolute voltage reference (0.6) routed to C1VREF input of Comparator C1 (or 1.2V precision<br/>reference on parts so equipped)</li> </ul> |

| bit 4   | C2RSEL: Comparator C2 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C2VREF input of Comparator C2                                                                                                       |

|         | 0 = Absolute voltage reference (0.6) routed to C2VREF input of Comparator C2 (or 1.2V precision                                                         |

|         | reference on parts so equipped)                                                                                                                         |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                              |

| bit 1   | T1GSS: Timer1 Gate Source Select bit                                                                                                                    |

|         | 1 = Timer1 gate source is $\overline{T1G}$                                                                                                              |

|         | 0 = Timer1 gate source is SYNCC2OUT.                                                                                                                    |

| bit 0   | C2SYNC: Comparator C2 Output Synchronization bit                                                                                                        |

|         | 1 = Output is synchronous to falling edge of Timer1 clock                                                                                               |

|         | 0 = Output is asynchronous                                                                                                                              |

|         |                                                                                                                                                         |

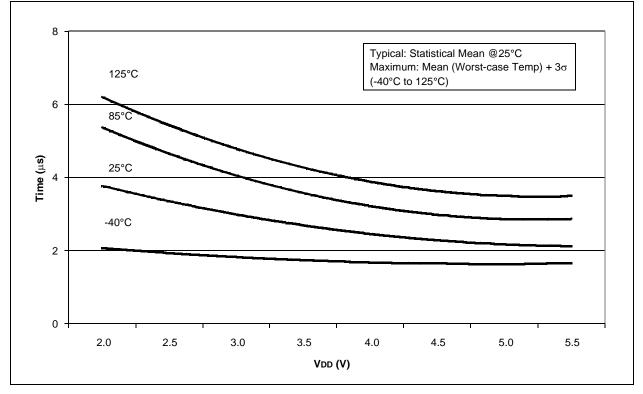

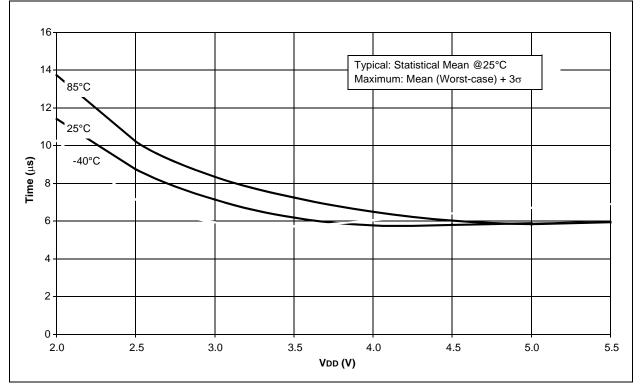

#### TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V)

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |                         |                         |                               |  |  |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------------|--|--|

| ADC Clock Source | ADCS<1:0>    | 20 MHz                  | 20 MHz 8 MHz            |                         | 1 MHz                         |  |  |

| Fosc/2           | 00           | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                        |  |  |

| Fosc/8           | 01           | 400 ns <sup>(2)</sup>   | 1.0 μs <b>(2)</b>       | 2.0 μs                  | 8.0 μs <b>(3)</b>             |  |  |

| Fosc/32          | 10           | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <b><sup>(3)</sup></b> |  |  |

| FRC              | 11           | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup>       |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

#### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| TCY to TAD TAD1               | TAD2      | TAD3    | TAD4   | TAD5   | TAD6   | TAD7          | TAD8                  | TAD9         | TAD10 | TAD11 |                                  |

|-------------------------------|-----------|---------|--------|--------|--------|---------------|-----------------------|--------------|-------|-------|----------------------------------|

| $\uparrow \uparrow  \uparrow$ | b9        | b8      | b7     | b6     | b5     | b4            | b3                    | b2           | b1    | b0    |                                  |

| Conver                        | sion St   | arts    |        |        |        |               |                       |              |       |       |                                  |

| Holding Capa                  | acitor is | s Disco | nnecte | d from | Analog | g Input       | (typica               | lly 100      | ns)   |       |                                  |

| <br>Set GO/DONE               | bit       |         |        |        |        | GO bi<br>ADIF | it is cle<br>bit is s | ared,<br>et, |       | •     | l<br>are loaded,<br>analog input |

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

**Note:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

Please see **Section 14.3 "Interrupts"** for more information.

# 10.1.4 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must write the Least and Most Significant address bits to the EEADR and EEADRH registers, set the EEPGD control bit of the EECON1 register, and then set control bit RD. Once the read control bit is set, the program memory Flash controller will use the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDAT and EEDATH registers; therefore, it can be read as two bytes in the following instructions.

## EEDAT and EEDATH registers will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

- If the WR bit is set when EEPGD = 1, it will be immediately reset to '0' and no operation will take place.

#### EXAMPLE 10-3: FLASH PROGRAM READ

|                      | BANKSEL | EEADR           | ;                                                        |

|----------------------|---------|-----------------|----------------------------------------------------------|

|                      | MOVLW   | MS_PROG_EE_ADDR | ;                                                        |

|                      | MOVWF   | EEADRH          | ;MS Byte of Program Address to read                      |

|                      | MOVLW   | LS_PROG_EE_ADDR | ;                                                        |

|                      | MOVWF   | EEADR           | ;LS Byte of Program Address to read                      |

|                      | BANKSEL | EECON1          | ;                                                        |

|                      | BSF     | EECON1, EEPGD   | ;Point to PROGRAM memory                                 |

| pa eo                | BSF     | EECON1, RD      | ;EE Read                                                 |

| Required<br>Sequence | NOP     |                 | ;First instruction after BSF EECON1,RD executes normally |

|                      | NOP     |                 | ;Any instructions here are ignored as program            |

| <b></b>              |         |                 | ;memory is read in second cycle after BSF EECON1,RD      |

| ;                    |         |                 |                                                          |

|                      | BANKSEL |                 | ;                                                        |

|                      | MOVF    | EEDAT, W        | ;W = LS Byte of Program Memory                           |

|                      | MOVWF   | LOWPMBYTE       | i                                                        |

|                      | MOVF    | EEDATH, W       | ;W = MS Byte of Program EEDAT                            |

|                      | MOVWF   | HIGHPMBYTE      | ;                                                        |

|                      | BCF     | STATUS, RP1     | ;Bank 0                                                  |

|                      |         |                 |                                                          |

An example of the complete 8-word write sequence is shown in Example 10-4. The initial address is loaded into the EEADRH and EEADR register pair; the eight words of data are loaded using indirect addressing.

#### EXAMPLE 10-4: WRITING TO FLASH PROGRAM MEMORY

```

*****

; This write routine assumes the following:

A valid starting address (the least significant bits = '000')

;

is loaded in ADDRH:ADDRL

;

;

ADDRH, ADDRL and DATADDR are all located in data memory

;

BANKSEL EEADRH

MOVF

ADDRH,W

; Load initial address

MOVWF

EEADRH

MOVF

ADDRL,W

MOVWF

EEADR

DATAADDR,W ; Load initial data address

MOVF

MOVWF FSR

LOOP

MOVF

INDF,W

; Load first data byte into lower

;

MOVWF EEDATA

; Next byte

INCE

FSR,F

; Load second data byte into upper

MOVF

INDF,W

MOVWF

EEDATH

INCF

FSR,F

BANKSEL EECON1

EECON1, EEPGD ; Point to program memory

BSF

EECON1,WREN ; Enable writes

BSF

BCF

INTCON,GIE ; Disable interrupts (if using)

BTFSC INTCON, GIE ; See AN576

GOTO

$-2

Required Sequence

;

MOVLW

55h

; Start of required write sequence:

EECON2

MOVWF

; Write 55h

0AAh

MOVLW

;

MOVWF EECON2

; Write OAAh

BSF

EECON1,WR ; Set WR bit to begin write

NOP

; Required to transfer data to the buffer

NOP

; registers

BCF

EECON1,WREN ; Disable writes

BSF

INTCON,GIE ; Enable interrupts (comment out if not using interrupts)

BANKSEL EEADR

EEADR, W

MOVF

; Increment address

INCF

EEADR, F

; Indicates when sixteen words have been programmed

ANDLW

0x0F

SUBLW

; 0x0F = 16 words

0x0F

; 0x0B = 12 words (PIC16F884/883/882 only)

; 0x07 = 8 words

0x03 = 4 \text{ words}(\text{PIC16F884}/883/882 \text{ only})

;

BTFSS

STATUS,Z

; Exit on a match,

GOTO

LOOP

; Continue if more data needs to be written

```

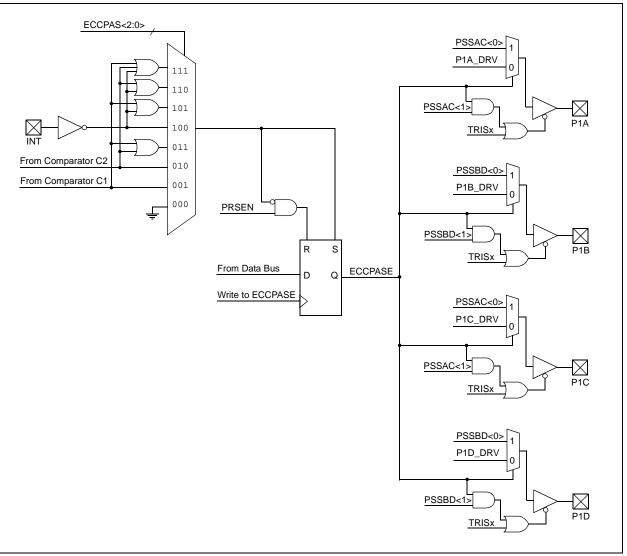

#### 11.6.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPAS<2:0> bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator C1

- Comparator C2

- Setting the ECCPASE bit in firmware

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see Section 11.6.5 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSSAC and PSSBD bits of the ECCPAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### FIGURE 11-14: AUTO-SHUTDOWN BLOCK DIAGRAM

### **REGISTER DEFINITIONS: PWM CONTROL**

#### REGISTER 11-4: PWM1CON: ENHANCED PWM CONTROL REGISTER

| R/W-0                             | R/W-0            | R/W-0     | R/W-0                                                 | R/W-0                                                                           | R/W-0                                                                                                   | R/W-0                                                                         |  |  |

|-----------------------------------|------------------|-----------|-------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| PDC6                              | PDC5             | PDC4      | PDC3                                                  | PDC2                                                                            | PDC1                                                                                                    | PDC0                                                                          |  |  |

|                                   | ·                |           | ·                                                     | •                                                                               |                                                                                                         | bit 0                                                                         |  |  |

|                                   |                  |           |                                                       |                                                                                 |                                                                                                         |                                                                               |  |  |

|                                   |                  |           |                                                       |                                                                                 |                                                                                                         |                                                                               |  |  |

| R = Readable bit W = Writable bit |                  |           | U = Unimplemented bit, read as '0'                    |                                                                                 |                                                                                                         |                                                                               |  |  |

| OR                                | '1' = Bit is set |           | '0' = Bit is cle                                      | '0' = Bit is cleared                                                            |                                                                                                         | x = Bit is unknown                                                            |  |  |

| OR                                | '1' = Bit is set |           | '0' = Bit is cle                                      | ared                                                                            | x = Bit is unknown                                                                                      |                                                                               |  |  |

|                                   | PDC6             | PDC6 PDC5 | PDC6     PDC5     PDC4       Dit     W = Writable bit | PDC6     PDC5     PDC4     PDC3       Dit     W = Writable bit     U = Unimpler | PDC6     PDC5     PDC4     PDC3     PDC2       Dit     W = Writable bit     U = Unimplemented bit, real | PDC6PDC5PDC4PDC3PDC2PDC1DitW = Writable bitU = Unimplemented bit, read as '0' |  |  |

bit 7 PRSEN: PWM Restart Enable bit

1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM

#### bit 6-0 PDC<6:0>: PWM Delay Count bits

PDCn = Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal **should** transition active and the **actual** time it transitions active.

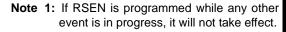

### 13.4.7 I<sup>2</sup>C<sup>™</sup> MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2 register) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG, while SCL is high. Following this, the RSEN bit (SSPCON2 register) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT register) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 13.4.7.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queuing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 13-14: REPEAT START CONDITION WAVEFORM

#### 14.3.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. See **Section 5.0 "Timer0 Module"** for operation of the Timer0 module.

#### 14.3.3 PORTB INTERRUPT

An input change on PORTB change sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<3>) bit. Plus, individual pins can be configured through the IOCB register.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set. See Section 3.4.3 "Interrupt-on-Change" for more information.

#### 17.1 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHARACTERISTICS |      |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |       |                                                        |  |

|--------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------------|--|

| Param<br>No.       | Sym. | Characteristic                                                   | Min.                                                                                                                                                                                                                                                            | Тур† | Max. | Units | Conditions                                             |  |

|                    | Vdd  | Supply Voltage                                                   | 2.0                                                                                                                                                                                                                                                             | —    | 5.5  | V     | Fosc < = 8 MHz: HFINTOSC, EC                           |  |

| D001               |      |                                                                  | 2.0                                                                                                                                                                                                                                                             | —    | 5.5  | V     | Fosc < = 4 MHz                                         |  |

| D001C              |      |                                                                  | 3.0                                                                                                                                                                                                                                                             | —    | 5.5  | V     | Fosc < = 10 MHz                                        |  |

| D001D              |      |                                                                  | 4.5                                                                                                                                                                                                                                                             | —    | 5.5  | V     | Fosc < = 20 MHz                                        |  |

| D002*              | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                                                                                                                                                                                                                                             | —    | —    | V     | Device in Sleep mode                                   |  |

| D003               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal |                                                                                                                                                                                                                                                                 | Vss  |      | V     | See Section 14.2.1 "Power-on Reset (POR)" for details. |  |

| D004*              | Svdd | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                                                                                                                                                            |      | _    | V/ms  | See Section 14.2.1 "Power-on Reset (POR)" for details. |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# PIC16F882/883/884/886/887

# PIC16F882/883/884/886/887

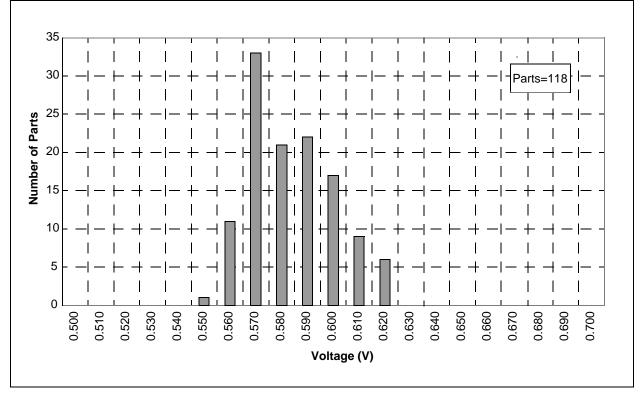

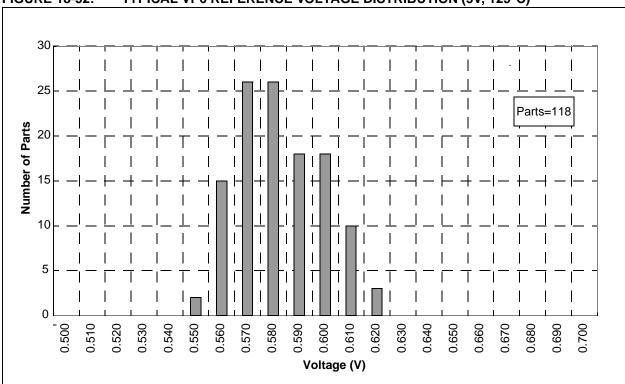

FIGURE 18-52: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (5V, 125°C)

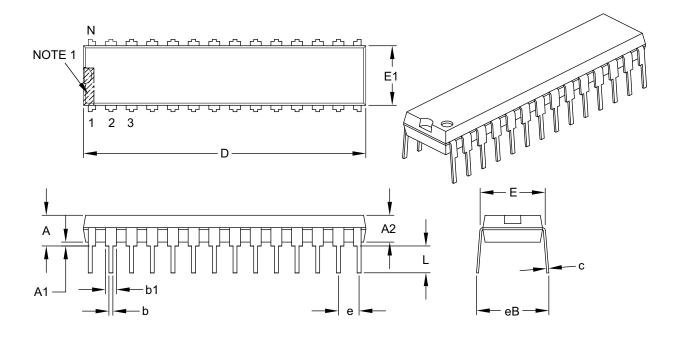

#### 19.2 Package Details

The following sections give the technical details of the packages.

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |          | INCHES |       |  |  |

|----------------------------|------------|----------|--------|-------|--|--|

| Dimens                     | ion Limits | MIN      | NOM    | MAX   |  |  |

| Number of Pins N           |            | 28       |        |       |  |  |

| Pitch                      | е          | .100 BSC |        |       |  |  |

| Top to Seating Plane       | А          | -        | -      | .200  |  |  |

| Molded Package Thickness   | A2         | .120     | .135   | .150  |  |  |

| Base to Seating Plane      | A1         | .015     | -      | -     |  |  |

| Shoulder to Shoulder Width | E          | .290     | .310   | .335  |  |  |

| Molded Package Width       | E1         | .240     | .285   | .295  |  |  |

| Overall Length             | D          | 1.345    | 1.365  | 1.400 |  |  |

| Tip to Seating Plane       | L          | .110     | .130   | .150  |  |  |

| Lead Thickness             | С          | .008     | .010   | .015  |  |  |

| Upper Lead Width           | b1         | .040     | .050   | .070  |  |  |

| Lower Lead Width           | b          | .014     | .018   | .022  |  |  |

| Overall Row Spacing §      | eB         | -        | -      | .430  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

<sup>© 2006-2015</sup> Microchip Technology Inc.