Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f883t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

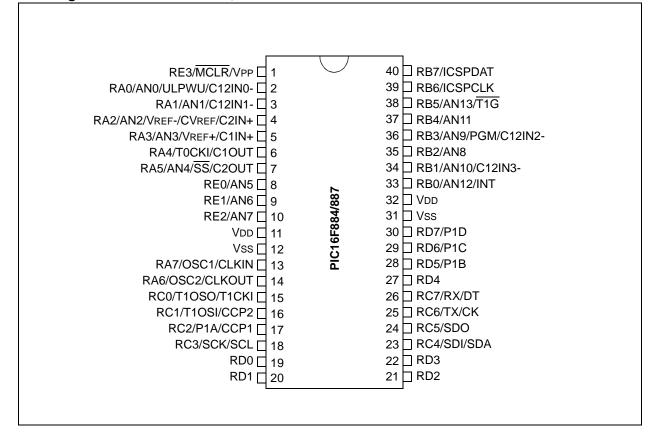

### Pin Diagrams - PIC16F884/887, 40-Pin PDIP

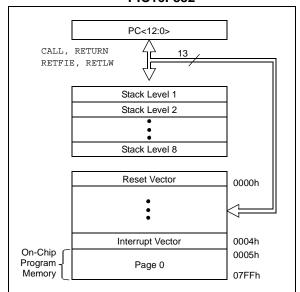

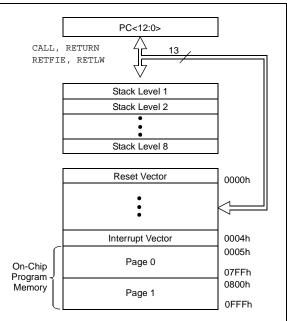

# 2.0 MEMORY ORGANIZATION

# 2.1 Program Memory Organization

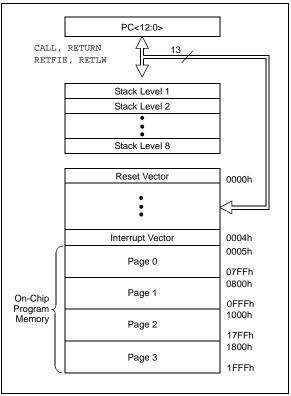

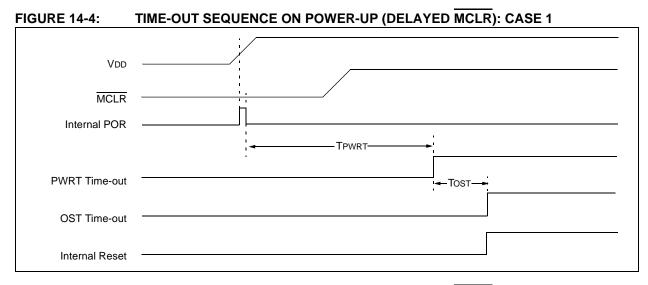

The PIC16F882/883/884/886/887 devices have a 13-bit program counter capable of addressing a  $2K \times 14$  (0000h-07FFh) for the PIC16F882,  $4K \times 14$  (0000h-0FFFh) for the PIC16F883/PIC16F884, and  $8K \times 14$  (0000h-1FFFh) for the PIC16F886/PIC16F887 program memory space. Accessing a location above these boundaries will cause a wrap-around within the first  $8K \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 2-2 and 2-3).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F882

### FIGURE 2-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F883/PIC16F884

# FIGURE 2-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F886/PIC16F887

# 3.0 I/O PORTS

There are as many as 35 general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 3.1 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 3-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 3-1 shows how to initialize PORTA.

Reading the PORTA register (Register 3-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

#### REGISTER 3-1: PORTA: PORTA REGISTER

The TRISA register (Register 3-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL register must be initialized to |

|-------|-------------------------------------------|

|       | configure an analog channel as a digital  |

|       | input. Pins configured as analog inputs   |

|       | will read '0'.                            |

| EXAMPLE 3-1:  | INITIALIZING PORTA |

|---------------|--------------------|

| BANKSEL PORTA | ;                  |

|               | THE DODER          |

| CLRF    | PORTA | ;Init PORTA            |

|---------|-------|------------------------|

| BANKSEL | ANSEL | ;                      |

| CLRF    | ANSEL | ;digital I/O           |

| BANKSEL | TRISA | ;                      |

| MOVLW   | 0Ch   | ;Set RA<3:2> as inputs |

| MOVWF   | TRISA | ;and set RA<5:4,1:0>   |

|         |       | ;as outputs            |

|         |       |                        |

| Lawawala |       |       |       |       |       |       |       |

|----------|-------|-------|-------|-------|-------|-------|-------|

|          |       |       |       |       |       |       |       |

| bit 7    |       |       |       |       |       |       | bit 0 |

| RA7      | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| Legend:           | egend:           |                                |                    |  |  |  |

|-------------------|------------------|--------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | · 'O'              |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |  |  |  |

bit 7-0 RA<7:0>: PORTA I/O Pin bit

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 3-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> | R/W-1 | R/W-1    | R/W-1  | R/W-1  | R/W-1  | R/W-1  |  |

|----------------------|----------------------|-------|----------|--------|--------|--------|--------|--|

| TRISA7               | TRISA7 TRISA6 TRISA5 |       | 5 TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |  |

| bit 7                |                      |       |          |        |        |        | bit 0  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

**Note 1:** TRISA<7:6> always reads '1' in XT, HS and LP Oscillator modes.

## 3.2 Additional Pin Functions

RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

#### 3.2.1 ANSEL REGISTER

The ANSEL register (Register 3-3) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 3-3: ANSEL: ANALOG SELECT REGISTER

| R/W-1               | R/W-1               | R/W-1               | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------------------|---------------------|---------------------|-------|-------|-------|-------|-------|

| ANS7 <sup>(2)</sup> | ANS6 <sup>(2)</sup> | ANS5 <sup>(2)</sup> | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7               |                     |                     |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 ANS<7:0>: Analog Select bits

Analog select between analog or digital function on pins AN<7:0>, respectively.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>.

- 0 = Digital I/O. Pin is assigned to port or special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: Not implemented on MemHigh.

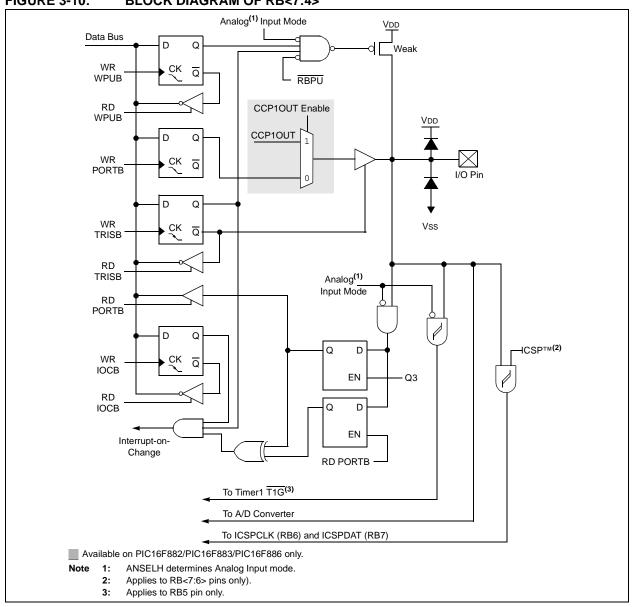

#### FIGURE 3-10: BLOCK DIAGRAM OF RB<7:4>

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELH     | —      | —      | ANS13  | ANS12  | ANS11  | ANS10  | ANS9   | ANS8   | 49                  |

| CCP1CON    | P1M1   | P1M0   | DC1B1  | DC1B0  | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 122                 |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL | _      | _      | T1GSS  | C2SYNC | 92                  |

| IOCB       | IOCB7  | IOCB6  | IOCB5  | IOCB4  | IOCB3  | IOCB2  | IOCB1  | IOCB0  | 50                  |

| INTCON     | GIE    | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 32                  |

| OPTION_REG | RBPU   | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 31                  |

| PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 49                  |

| TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 49                  |

| WPUB       | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1  | WPUB0  | 50                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTB.

© 2006-2015 Microchip Technology Inc.

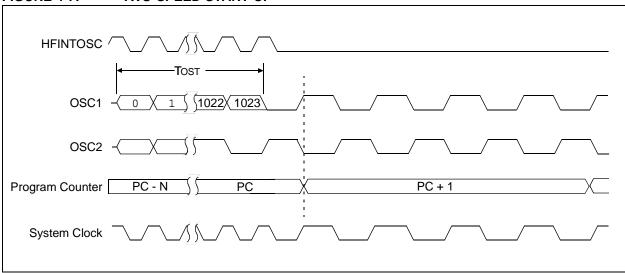

#### 4.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 4.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1), or the internal oscillator.

#### FIGURE 4-7: TWO-SPEED START-UP

# 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

# EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL | TMR0            | ;                  |

|---------|-----------------|--------------------|

| CLRWDT  |                 | ;Clear WDT         |

| CLRF    | TMR0            | ;Clear TMR0 and    |

|         |                 | ;prescaler         |

| BANKSEL | OPTION_REG      | ;                  |

| BSF     | OPTION_REG, PSA | ;Select WDT        |

| CLRWDT  |                 | ;                  |

|         |                 | ;                  |

| MOVLW   | b'11111000'     | ;Mask prescaler    |

| ANDWF   | OPTION_REG,W    | ;bits              |

| IORLW   | b'00000101'     | ;Set WDT prescaler |

| MOVWF   | OPTION_REG      | ;to 1:32           |

|         |                 |                    |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

| EXAMPLE 5-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT                             |                                                          | ;Clear WDT and<br>;prescaler                  |

|------------------------------------|----------------------------------------------------------|-----------------------------------------------|

| BANKSEL<br>MOVLW<br>ANDWF<br>IORLW | OPTION_REG<br>b'11110000'<br>OPTION_REG,W<br>b'00000011' | ;<br>;Mask TMR0 select and<br>;prescaler bits |

| MOVWF                              | OPTION_REG                                               | ;Set prescale to 1:16<br>;                    |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

# 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in the **Section 17.0 "Electrical Specifications"**.

## 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

# **REGISTER DEFINITIONS: TIMER1 CONTROL**

# REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                 | R/W-0 R/W-0                                         |  | R/W-0   | R/W-0           | R/W-0 | R/W-0  | R/W-0  |  |  |  |

|-----------------------|-----------------------------------------------------|--|---------|-----------------|-------|--------|--------|--|--|--|

| T1GINV <sup>(1)</sup> | T1GINV <sup>(1)</sup> TMR1GE <sup>(2)</sup> T1CKPS1 |  | T1CKPS0 | T1CKPS0 T1OSCEN |       | TMR1CS | TMR10N |  |  |  |

| bit 7                 |                                                     |  |         |                 |       |        |        |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | T1GINV: Timer1 Gate Invert bit <sup>(1)</sup>                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> </ul> |

| bit 6   | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup>                                                                                                                |

|         | $\frac{\text{If TMR1ON} = 0}{1000}$                                                                                                                          |

|         | This bit is ignored<br>If TMR1ON = 1:                                                                                                                        |

|         | 1 = Timer1 counting is controlled by the Timer1 Gate function                                                                                                |

|         | 0 = Timer1 is always counting                                                                                                                                |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                         |

|         | 11 = 1:8 Prescale Value                                                                                                                                      |

|         | 10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value                                                                                                           |

|         | 00 = 1:1 Prescale Value                                                                                                                                      |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit                                                                                                                    |

|         | 1 = LP oscillator is enabled for Timer1 clock                                                                                                                |

|         | 0 = LP oscillator is off                                                                                                                                     |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                                              |

|         | <u>TMR1CS = 1:</u><br>1 = Do not synchronize external clock input                                                                                            |

|         | 0 = Synchronize external clock input                                                                                                                         |

|         | $\underline{TMR1CS} = 0:$                                                                                                                                    |

| 1 1 4   | This bit is ignored. Timer1 uses the internal clock                                                                                                          |

| bit 1   | TMR1CS: Timer1 Clock Source Select bit                                                                                                                       |

|         | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                                        |

| bit 0   | TMR10N: Timer1 On bit                                                                                                                                        |

|         | 1 = Enables Timer1                                                                                                                                           |

|         | 0 = Stops Timer1                                                                                                                                             |

| Note 1: | T1GINV bit inverts the Timer1 gate logic, regardless of source.                                                                                              |

| 2.      | TMR1GE bit must be set to use either $\overline{116}$ pip or C20UT as selected by the T1GSS bit of the CM2CON1                                               |

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CM2CON1 register, as a Timer1 gate source.

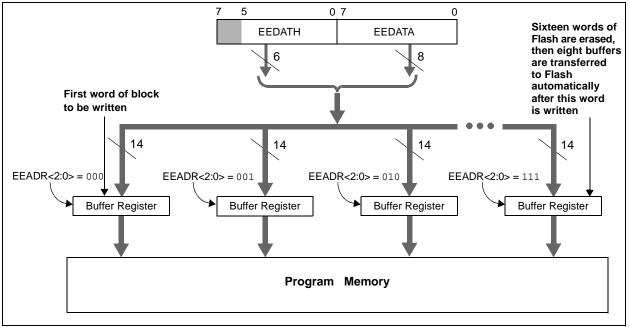

#### 12.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 12.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 12-5: ASYNCHRONOUS RECEPTION

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                   |            |                             |                    |            |                             |                  |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz             |            | Fosc                        | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             | Fosc = 8.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                             | _          | _                           |                   | _          | _                           |                    | _          | _                           | —                | _          | _                           |  |

| 1200   | 1221                          | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         | 1202             | 0.16       | 103                         |  |

| 2400   | 2404                          | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          | 2404             | 0.16       | 51                          |  |

| 9600   | 9470                          | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          | 9615             | 0.16       | 12                          |  |

| 10417  | 10417                         | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          | 10417            | 0.00       | 11                          |  |

| 19.2k  | 19.53k                        | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           | _                | _          | _                           |  |

| 57.6k  | —                             | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           | _                | _          | _                           |  |

| 115.2k | —                             | —          | —                           | _                 | —          | —                           | _                  | —          | —                           | —                | —          | —                           |  |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                   | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |                             |                  |            |                             |                  |            |                             |  |  |

|--------|------------------|------------|-----------------------------|-------------------|----------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 4.000 MHz |            | Fosc                        | Fosc = 3.6864 MHz |                                                    |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300              | 0.16       | 207                         | 300               | 0.00                                               | 191                         | 300              | 0.16       | 103                         | 300              | 0.16       | 51                          |  |  |

| 1200   | 1202             | 0.16       | 51                          | 1200              | 0.00                                               | 47                          | 1202             | 0.16       | 25                          | 1202             | 0.16       | 12                          |  |  |

| 2400   | 2404             | 0.16       | 25                          | 2400              | 0.00                                               | 23                          | 2404             | 0.16       | 12                          | —                | —          | _                           |  |  |

| 9600   | —                | _          | —                           | 9600              | 0.00                                               | 5                           | _                | _          | _                           | —                | _          | _                           |  |  |

| 10417  | 10417            | 0.00       | 5                           | —                 | _                                                  | _                           | 10417            | 0.00       | 2                           | —                | —          | _                           |  |  |

| 19.2k  | —                | _          | _                           | 19.20k            | 0.00                                               | 2                           | —                | _          | _                           | _                | _          | _                           |  |  |

| 57.6k  | —                | —          | —                           | 57.60k            | 0.00                                               | 0                           | —                | _          | —                           | —                | —          | —                           |  |  |

| 115.2k | —                | _          | _                           | _                 | _                                                  | —                           | _                | _          | _                           | —                | _          | —                           |  |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                   |            |                             |                    |            |                             |                  |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz             |            | Fosc                        | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             | Fosc = 8.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | —                             |            | _                           |                   | _          | _                           | _                  | —          | _                           | _                | —          | —                           |  |

| 1200   | —                             | —          | —                           | —                 |            | —                           | —                  | —          | —                           | —                | —          | —                           |  |

| 2400   | —                             | _          | _                           | —                 | _          | _                           | —                  | _          | _                           | 2404             | 0.16       | 207                         |  |

| 9600   | 9615                          | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          | 9615             | 0.16       | 51                          |  |

| 10417  | 10417                         | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          | 10417            | 0.00       | 47                          |  |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          | 19231            | 0.16       | 25                          |  |

| 57.6k  | 56.82k                        | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          | 55556            | -3.55      | 8                           |  |

| 115.2k | 113.64k                       | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           | _                | —          | _                           |  |

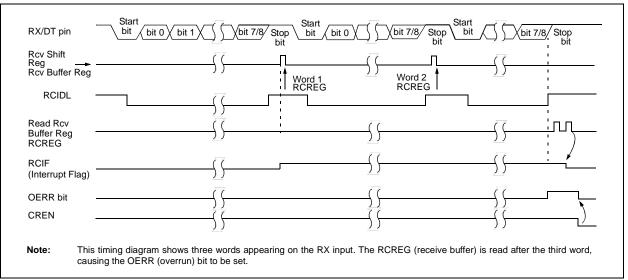

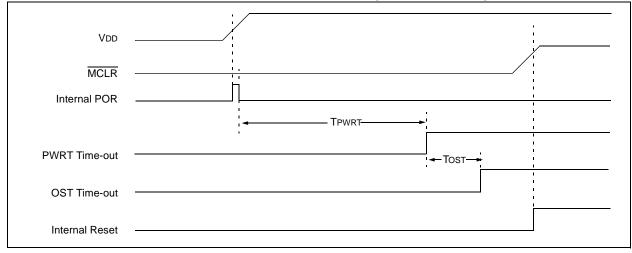

### FIGURE 14-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

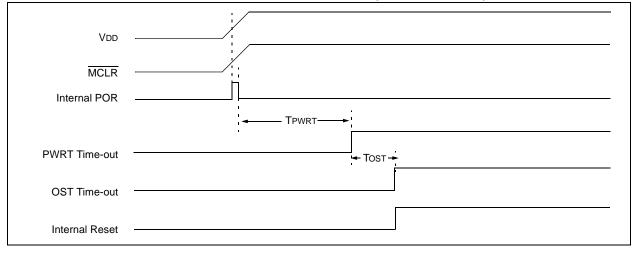

#### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD)

### 17.2 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHA | ARACTERISTICS                          |      | ard Oper<br>ing temp |      | -40°C ⊴ | ≤ TA ≤ +8 | <b>s otherwise stated)</b><br>35°C for industrial<br>125°C for extended |

|--------|----------------------------------------|------|----------------------|------|---------|-----------|-------------------------------------------------------------------------|

| Param  | Device Characteristics                 | Min. | Typ†                 | Max. | Units   |           | Conditions                                                              |

| No.    | Device onarableristics                 |      | .,,,,,               | maxi | Onits   | Vdd       | Note                                                                    |

| D010   | Supply Current (IDD) <sup>(1, 2)</sup> | _    | 13                   | 19   | μA      | 2.0       | Fosc = 32 kHz                                                           |

|        |                                        |      | 22                   | 30   | μΑ      | 3.0       | LP Oscillator mode                                                      |

|        |                                        |      | 33                   | 60   | μΑ      | 5.0       |                                                                         |

| D011*  |                                        | _    | 180                  | 250  | μΑ      | 2.0       | Fosc = 1 MHz                                                            |

|        |                                        |      | 290                  | 400  | μΑ      | 3.0       | XT Oscillator mode                                                      |

|        |                                        |      | 490                  | 650  | μΑ      | 5.0       |                                                                         |

| D012   |                                        |      | 280                  | 380  | μA      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        |      | 480                  | 670  | μΑ      | 3.0       | XT Oscillator mode                                                      |

|        |                                        |      | 0.9                  | 1.4  | mA      | 5.0       |                                                                         |

| D013*  |                                        |      | 170                  | 295  | μΑ      | 2.0       | Fosc = 1 MHz                                                            |

|        |                                        |      | 280                  | 480  | μΑ      | 3.0       | EC Oscillator mode                                                      |

|        |                                        |      | 470                  | 690  | μΑ      | 5.0       |                                                                         |

| D014   |                                        |      | 290                  | 450  | μΑ      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        | —    | 490                  | 720  | μΑ      | 3.0       | EC Oscillator mode                                                      |

|        |                                        | —    | 0.85                 | 1.3  | mA      | 5.0       |                                                                         |

| D015   |                                        |      | 8                    | 20   | μΑ      | 2.0       | Fosc = 31 kHz                                                           |

|        |                                        | —    | 16                   | 40   | μΑ      | 3.0       | LFINTOSC mode                                                           |

|        |                                        | —    | 31                   | 65   | μΑ      | 5.0       |                                                                         |

| D016*  |                                        | _    | 416                  | 520  | μΑ      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        |      | 640                  | 840  | μΑ      | 3.0       | HFINTOSC mode                                                           |

|        |                                        | —    | 1.13                 | 1.6  | mA      | 5.0       |                                                                         |

| D017   |                                        |      | 0.65                 | 0.9  | mA      | 2.0       | Fosc = 8 MHz                                                            |

|        |                                        |      | 1.01                 | 1.3  | mA      | 3.0       | HFINTOSC mode                                                           |

|        |                                        | —    | 1.86                 | 2.3  | mA      | 5.0       |                                                                         |

| D018   |                                        | _    | 340                  | 580  | μΑ      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        |      | 550                  | 900  | μΑ      | 3.0       | EXTRC mode <sup>(3)</sup>                                               |

|        |                                        | —    | 0.92                 | 1.4  | mA      | 5.0       |                                                                         |

| D019   |                                        |      | 3.8                  | 4.7  | mA      | 4.5       | Fosc = 20 MHz                                                           |

|        |                                        | _    | 4.0                  | 4.8  | mA      | 5.0       | HS Oscillator mode                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

### TABLE 17-7: COMPARATOR SPECIFICATIONS

|                                                         | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                           |         |     |       |           |    |               |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------|-----|-------|-----------|----|---------------|--|--|--|--|

| Param<br>No.Sym.CharacteristicsMin.Typ†Max.UnitsComment |                                                                                                                      |                                           |         |     |       |           |    |               |  |  |  |  |

| CM01                                                    | Vos                                                                                                                  | Input Offset Voltage                      |         | —   | ± 5.0 | ± 10      | mV | (Vdd - 1.5)/2 |  |  |  |  |

| CM02                                                    | Vсм                                                                                                                  | Input Common Mode Voltage                 |         | 0   |       | Vdd - 1.5 | V  |               |  |  |  |  |

| CM03*                                                   | CMRR                                                                                                                 | Common Mode Rejection Ratio               |         | +55 |       | _         | dB |               |  |  |  |  |

| CM04*                                                   | TRT                                                                                                                  | Response Time                             | Falling | _   | 150   | 600       | ns | (Note 1)      |  |  |  |  |

|                                                         |                                                                                                                      |                                           | Rising  |     | 200   | 1000      | ns |               |  |  |  |  |

| CM05*                                                   | Тмс2coV                                                                                                              | Comparator Mode Change to<br>Output Valid |         |     |       | 10        | μS |               |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV.

### TABLE 17-8: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +125^{\circ}C$

| Param<br>No. | Sym. | Characteristics              | Min. | Тур†             | Max.           | Units      | Comments                                    |

|--------------|------|------------------------------|------|------------------|----------------|------------|---------------------------------------------|

| CV01*        | Clsb | Step Size <sup>(2)</sup>     |      | VDD/24<br>VDD/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02*        | CACC | Absolute Accuracy            |      |                  | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03*        | CR   | Unit Resistor Value (R)      | —    | 2k               | _              | Ω          |                                             |

| CV04*        | CST  | Settling Time <sup>(1)</sup> | _    | —                | 10             | μS         |                                             |

These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

- 2: See Section 8.10 "Comparator Voltage Reference" for more information.

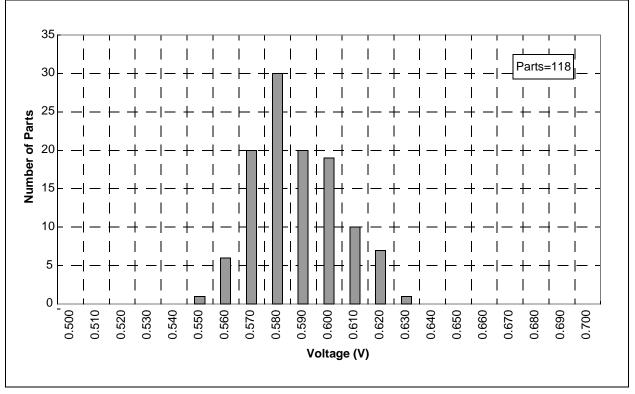

#### TABLE 17-9: VOLTAGE (VR) REFERENCE SPECIFICATIONS

| VR Voltage Reference Specifications |         |                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |          |  |

|-------------------------------------|---------|-------------------|------------------------------------------------------|------|------|-------|----------|--|

| Param<br>No.                        | Symbol  | Characteristics   | Min.                                                 | Тур. | Max. | Units | Comments |  |

| VR01                                | VROUT   | VR voltage output | 0.5                                                  | 0.6  | 0.7  | V     |          |  |

| VR02*                               | TSTABLE | Settling Time     | —                                                    | 10   | 100* | μS    |          |  |

These parameters are characterized but not tested.

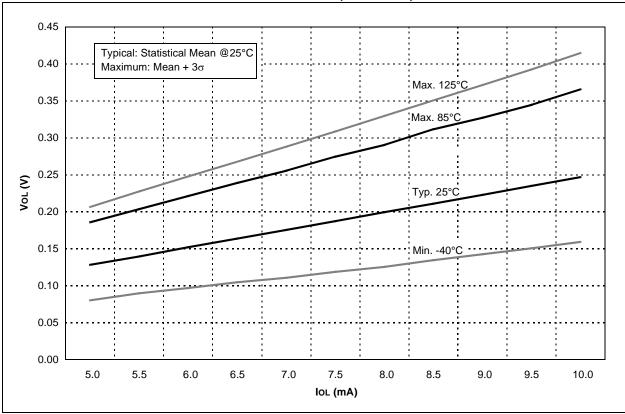

# FIGURE 18-27: Vol vs. IoL OVER TEMPERATURE (VDD = 5.0V)

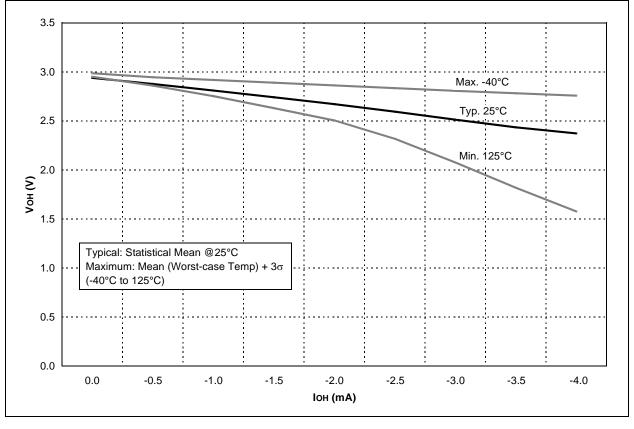

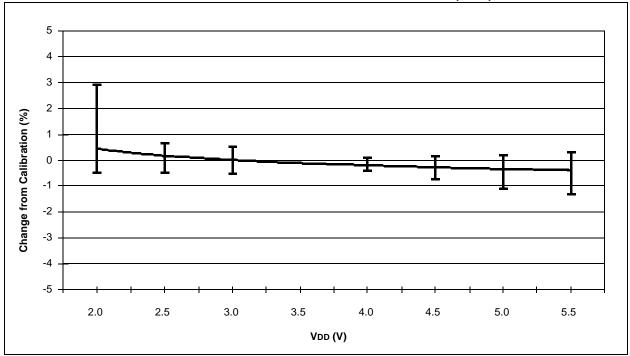

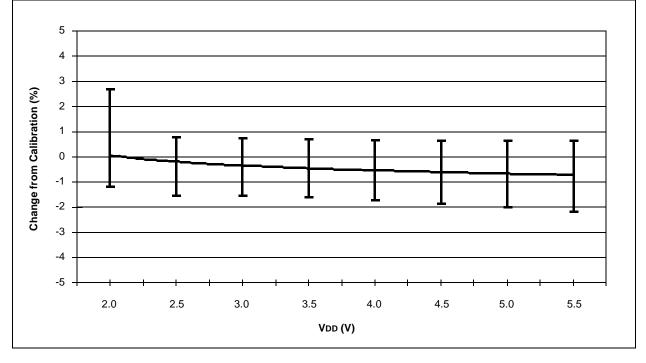

### FIGURE 18-39: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

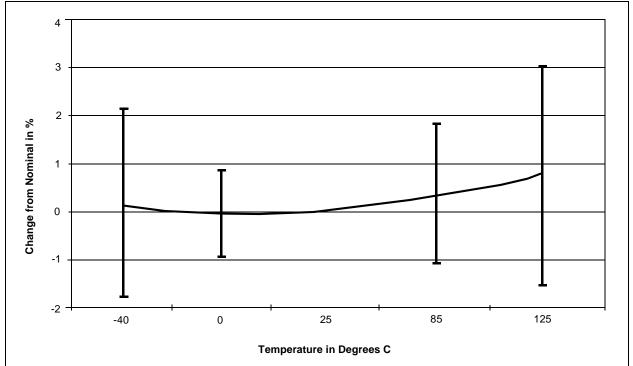

#### FIGURE 18-45: VP6 DRIFT OVER TEMPERATURE NORMALIZED AT 25°C (VDD 3V)

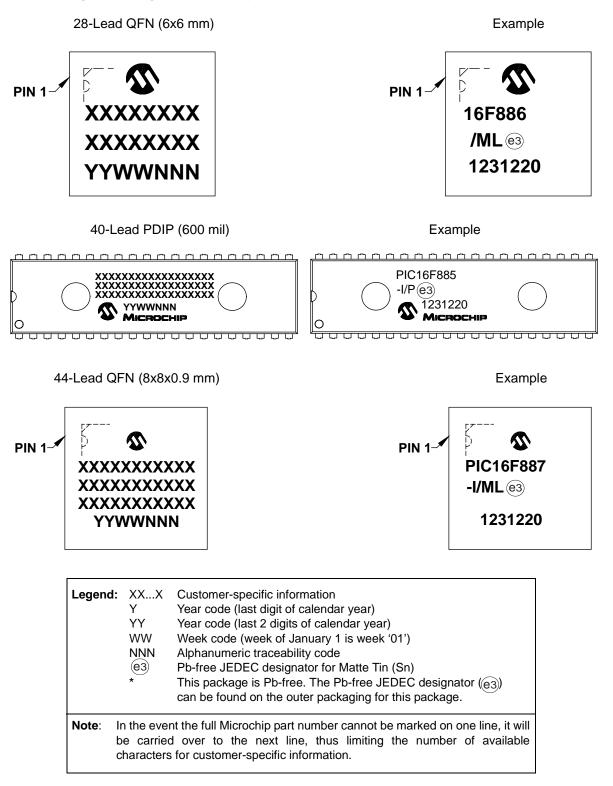

# **19.1** Package Marking Information (Continued)

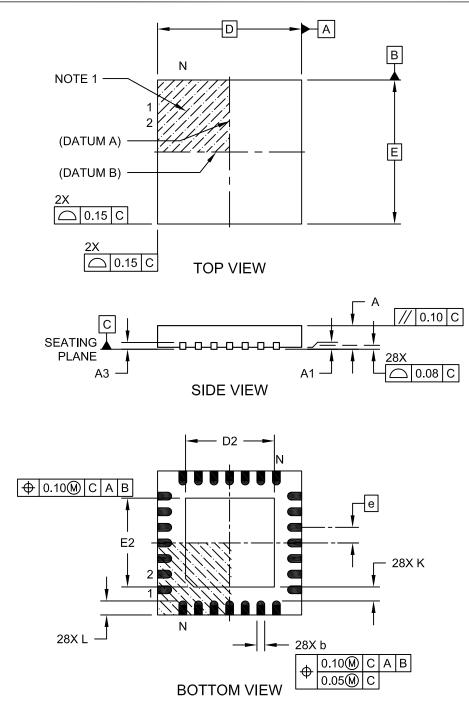

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2