Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f883t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 MEMORY ORGANIZATION

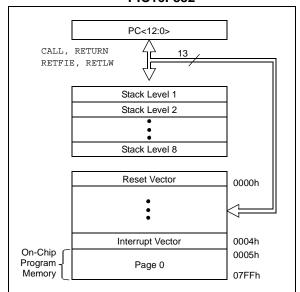

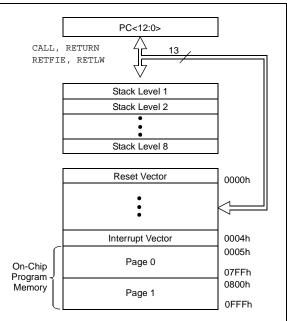

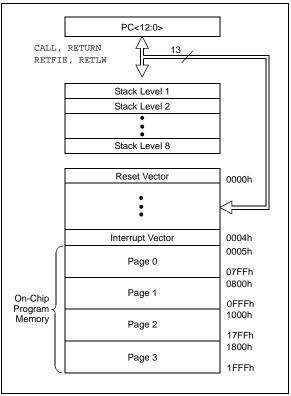

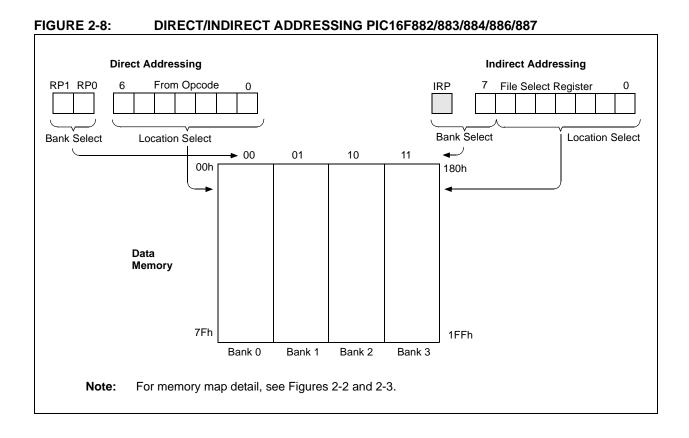

#### 2.1 Program Memory Organization

The PIC16F882/883/884/886/887 devices have a 13-bit program counter capable of addressing a  $2K \times 14$  (0000h-07FFh) for the PIC16F882,  $4K \times 14$  (0000h-0FFFh) for the PIC16F883/PIC16F884, and  $8K \times 14$  (0000h-1FFFh) for the PIC16F886/PIC16F887 program memory space. Accessing a location above these boundaries will cause a wrap-around within the first  $8K \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 2-2 and 2-3).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F882

#### FIGURE 2-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F883/PIC16F884

### FIGURE 2-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F886/PIC16F887

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### **REGISTER DEFINITIONS: PIE1**

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter (ADC) Interrupt Enable bit                                                                            |

|       | <ul><li>1 = Enables the ADC interrupt</li><li>0 = Disables the ADC interrupt</li></ul>                                    |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit                                                                                 |

|       | <ul><li>1 = Enables the EUSART receive interrupt</li><li>0 = Disables the EUSART receive interrupt</li></ul>              |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit                                                                                |

|       | <ul><li>1 = Enables the EUSART transmit interrupt</li><li>0 = Disables the EUSART transmit interrupt</li></ul>            |

| bit 3 | SSPIE: Master Synchronous Serial Port (MSSP) Interrupt Enable bit                                                         |

|       | <ul><li>1 = Enables the MSSP interrupt</li><li>0 = Disables the MSSP interrupt</li></ul>                                  |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                                                                                         |

|       | <ul><li>1 = Enables the CCP1 interrupt</li><li>0 = Disables the CCP1 interrupt</li></ul>                                  |

| bit 1 | TMR2IE: Timer2 to PR2 Match Interrupt Enable bit                                                                          |

|       | <ul> <li>1 = Enables the Timer2 to PR2 match interrupt</li> <li>0 = Disables the Timer2 to PR2 match interrupt</li> </ul> |

| bit 0 | TMR1IE: Timer1 Overflow Interrupt Enable bit                                                                              |

|       | 1 = Enables the Timer1 overflow interrupt                                                                                 |

|       | 0 = Disables the Timer1 overflow interrupt                                                                                |

|       |                                                                                                                           |

#### 3.4.4.5 RB4/AN11/P1D<sup>(1)</sup>

Figure 3-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a PWM output<sup>(1)</sup>

Note 1: P1D is available on PIC16F882/883/886 only.

#### 3.4.4.6 RB5/AN13/T1G

Figure 3-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a Timer1 gate input

#### 3.4.4.7 RB6/ICSPCLK

Figure 3-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- In-Circuit Serial Programming clock

#### 3.4.4.8 RB7/ICSPDAT

Figure 3-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- In-Circuit Serial Programming data

### 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or T1G pin

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with ECCP)

- Comparator output synchronization to Timer1 clock

Figure 6-1 is a block diagram of the Timer1 module.

#### TMR1GE T1GINV TMR10N Set flag bit TMR1IF on To C2 Comparator Module Overflow Timer1 Clock TMR1<sup>(2)</sup> Synchronized 0 ΕN clock input TMR1H TMR1L Oscillator (1) T1SYNC T1OSO/T1CKI 1 Synchronize<sup>(3)</sup> Prescaler 1, 2, 4, 8 det 0 T10SI 🖹 2 T1CKPS<1:0> TMR1CS TIG > 1 INTOSC SYNCC2OUT(4) 0 Without CLKOUT T1OSCEN Fosc/4 T1GSS Internal Clock ST Buffer is low power type when using LP osc, or high speed type when using T1CKI. Note 1: 2: Timer1 register increments on rising edge. Synchronize does not operate while in Sleep. 3: 4: SYNCC2OUT is synchronized when the C2SYNC bit of the CM2CON1 register is set.

#### FIGURE 6-1: TIMER1 BLOCK DIAGRAM

#### 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

#### 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS |  |

|--------------|--------|--|

| Fosc/4       | 0      |  |

| T1CKI pin    | 1      |  |

#### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 6.9 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

See Section 11.0 "Capture/Compare/PWM Modules (CCP1 and CCP2)" for more information.

#### 6.10 ECCP Special Event Trigger

If an ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Capture/ Compare/PWM Modules (CCP1 and CCP2)".

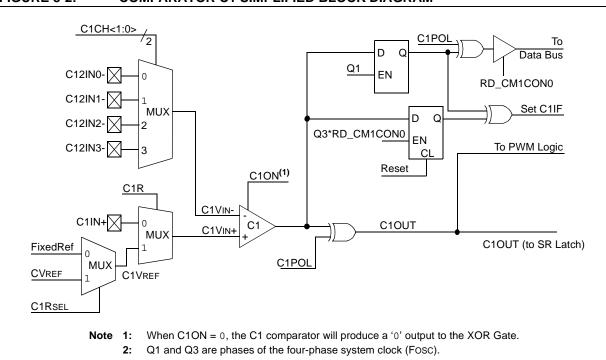

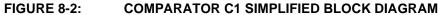

#### 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see **Section 8.0 "Comparator Module**".

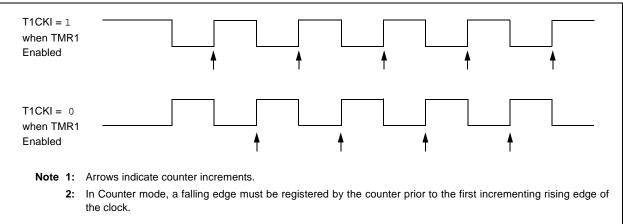

#### FIGURE 6-2: TIMER1 INCREMENTING EDGE

3: Q1 is held high during Sleep mode.

#### REGISTER 11-3: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|------------------|-----------------|--------|

| ECCPASE       |                                                                                                                                                                                                                                                                                                                                                                                                                             | ECCPAS1          | ECCPAS0       | PSSAC1           | PSSAC0           | PSSBD1          | PSSBD0 |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |               |                  |                  |                 | bit 0  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |               |                  |                  |                 |        |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |               |                  |                  |                 |        |

| R = Readabl   | e bit                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable     | bit           | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7         | <b>ECCPASE:</b> ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in shutdown state<br>0 = ECCP outputs are operating                                                                                                                                                                                                                                                              |                  |               |                  |                  |                 |        |

| bit 6-4       | ECCPAS<2:0                                                                                                                                                                                                                                                                                                                                                                                                                  | >: ECCP Auto     | -shutdown Sou | arce Select bits | 6                |                 |        |

|               | <ul> <li>000 = Auto-Shutdown is disabled</li> <li>001 = Comparator C1 output high</li> <li>010 = Comparator C2 output high<sup>(1)</sup></li> <li>011 = Either Comparators output is high</li> <li>100 = VIL on INT pin</li> <li>101 = VIL on INT pin or Comparator C1 output high</li> <li>110 = VIL on INT pin or Comparator C2 output high</li> <li>111 = VIL on INT pin or either Comparators output is high</li> </ul> |                  |               |                  |                  |                 |        |

| bit 3-2       | <b>PSSACn:</b> Pins P1A and P1C Shutdown State Control bits<br>00 = Drive pins P1A and P1C to '0'<br>01 = Drive pins P1A and P1C to '1'<br>1x = Pins P1A and P1C tri-state                                                                                                                                                                                                                                                  |                  |               |                  |                  |                 |        |

| bit 1-0       | PSSBDn: Pins P1B and P1D Shutdown State Control bits<br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state                                                                                                                                                                                                                                                         |                  |               |                  |                  |                 |        |

| Note 1: If    | Note 1: If C2SYNC is enabled, the shutdown will be delayed by Timer1.                                                                                                                                                                                                                                                                                                                                                       |                  |               |                  |                  |                 |        |

| Note 1: | The auto-shutdown condition is a level-    |

|---------|--------------------------------------------|

|         | based signal, not an edge-based signal.    |

|         | As long as the level is present, the auto- |

|         | shutdown will persist.                     |

- 2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

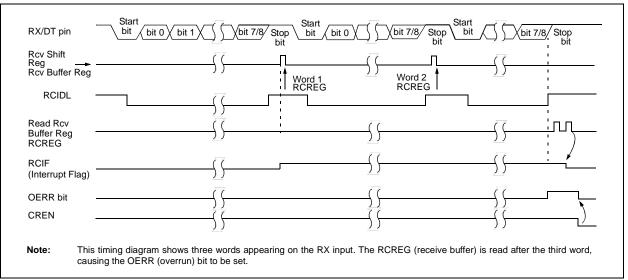

#### 12.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 12.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 12.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 12.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 12.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 12.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 12-5: ASYNCHRONOUS RECEPTION

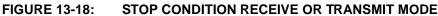

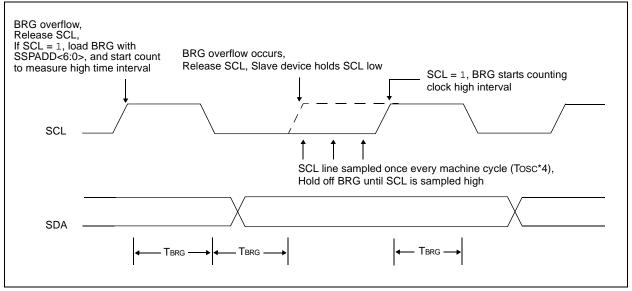

#### 13.4.12 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 13-19).

#### 13.4.13 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 13.4.14 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### FIGURE 13-19: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

| Register | Address               | Power-on<br>Reset | WDT  | Reset<br>Reset<br>ut Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|----------|-----------------------|-------------------|------|-------------------------------------------|---------------------------------------------------------------------------------------|

| W        | —                     | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| INDF     | 00h/80h/10<br>0h/180h | XXXX XXXX         | XXXX | XXXX                                      | นนนน นนนน                                                                             |

| TMR0     | 01h/101h              | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| PCL      | 02h/82h/10<br>2h/182h | 0000 0000         | 0000 | 0000                                      | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS   | 03h/83h/10<br>3h/183h | 0001 1xxx         | 000g | quuu <b>(4)</b>                           | uuuq quuu <sup>(4)</sup>                                                              |

| FSR      | 04h/84h/10<br>4h/184h | xxxx xxxx         | սսսս | uuuu                                      | นนนน นนนน                                                                             |

| PORTA    | 05h                   | xxxx xxxx         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| PORTB    | 06h/106h              | xxxx xxxx         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| PORTC    | 07h                   | xxxx xxxx         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| PORTD    | 08h                   | xxxx xxxx         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| PORTE    | 09h                   | xxxx              |      | 0000                                      | uuuu                                                                                  |

| PCLATH   | 0Ah/8Ah/10<br>Ah/18Ah | 0 0000            | 0    | 0000                                      | u uuuu                                                                                |

| INTCON   | 0Bh/8Bh/10<br>Bh/18Bh | 0000 000x         | 0000 | 000u                                      | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1     | 0Ch                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR2     | 0Dh                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu <sup>(2)</sup>                                                              |

| TMR1L    | 0Eh                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| TMR1H    | 0Fh                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| T1CON    | 10h                   | 0000 0000         | uuuu | uuuu                                      | -uuu uuuu                                                                             |

| TMR2     | 11h                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| T2CON    | 12h                   | -000 0000         | -000 | 0000                                      | -uuu uuuu                                                                             |

| SSPBUF   | 13h                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| SSPCON   | 14h                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| CCPR1L   | 15h                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| CCPR1H   | 16h                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

| CCP1CON  | 17h                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| RCSTA    | 18h                   | 0000 000x         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| TXREG    | 19h                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| RCREG    | 1Ah                   | 0000 0000         | 0000 | 0000                                      | uuuu uuuu                                                                             |

| CCPR2L   | 1Bh                   | xxxx xxxx         | uuuu | uuuu                                      | uuuu uuuu                                                                             |

#### TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- **4:** See Table 14-5 for Reset value for specific condition.

- **5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

- **6:** Accessible only when SSPCON register bits SSPM<3:0 > = 1001.

#### 14.11 In-Circuit Debugger

The PIC16F882/883/884/886/887-ICD can be used in any of the package types. The devices will be mounted on the target application board, which in turn has a 3 or 4-wire connection to the ICD tool.

When the debug bit in the Configuration Word (CONFIG<13>) is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. See Table 14-10 for more detail.

Note: The user's application must have the circuitry required to support ICD functionality. Once the ICD circuitry is enabled, normal device pin functions on RB6/ICSPCLK and RB7/ICSPDAT will not be usable. The ICD circuitry uses these pins for communication with the ICD2 external debugger.

For more information, see "Using *MPLAB*<sup>®</sup> *ICD* 2" (DS51265), available on Microchip's web site (www.microchip.com).

#### 14.11.1 ICD PINOUT

The devices in the MemHigh family carry the circuitry for the In-Circuit Debugger on-chip and on existing device pins. This eliminates the need for a separate die or package for the ICD device. The pinout for the ICD device is the same as the devices (see **Section 1.0 "Device Overview"** for complete pinout and pin descriptions). Table 14-10 shows the location and function of the ICD related pins on the 28 and 40 pin devices.

| Pin (PDIP)    |                   | Name     | Tuno | Pull-up  | Description                             |  |

|---------------|-------------------|----------|------|----------|-----------------------------------------|--|

| PIC16F884/887 | PIC16F882/883/886 | Name     | Туре | r ull-up | Description                             |  |

| 40            | 28                | ICDDATA  | TTL  | —        | In-Circuit Debugger Bidirectional data  |  |

| 39            | 27                | ICDCLK   | ST   | —        | In-Circuit Debugger Bidirectional clock |  |

| 1             | 1                 | MCLR/Vpp | ΗV   | _        | Programming voltage                     |  |

| 11,32         | 20                | Vdd      | Р    | _        |                                         |  |

| 12,31         | 8,19              | Vss      | Р    | _        |                                         |  |

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, P = Power, HV = High Voltage

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |

|                  | Before Instruction<br>REG1 = 1110 0110<br>C = 0                                                                                                                                                                      |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                    |  |  |  |  |  |

|                  | REG1 = 1110 0110<br>W = 1100 1100                                                                                                                                                                                    |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \text{PD} \end{array}$                                                         |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |  |  |  |  |

| Description:     | The power-down Status bit, $\overline{PD}$<br>is cleared. Time-out Status bit,<br>$\overline{TO}$ is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                 |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                               |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

|                  | C = 0 $W > k$                                                                                                            |  |  |  |  |  |  |

| <b>C</b> = 0  | W > k                     |

|---------------|---------------------------|

| <b>C</b> = 1  | $W \leq k$                |

| <b>DC</b> = 0 | W<3:0> > k<3:0>           |

| DC = 1        | $W < 3:0 > \le k < 3:0 >$ |

| SUBWF            | Subtract W from f                                                                                                                                                                           |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

| <b>C</b> = 0 | W > f                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq f$                |

| DC = 0       | W<3:0> > f<3:0>           |

| DC = 1       | $W < 3:0 > \le f < 3:0 >$ |

#### 17.2 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHA                          | ARACTERISTICS                          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |     |                           |

|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----|---------------------------|

| Param<br>Device Characteristics |                                        | Min.                                                                                                                                                                                    | Тур† | Max. | Units |     | Conditions                |

| No.                             | Device Gliaracteristics                |                                                                                                                                                                                         | 146. | max. | Units | Vdd | Note                      |

| D010                            | Supply Current (IDD) <sup>(1, 2)</sup> | _                                                                                                                                                                                       | 13   | 19   | μA    | 2.0 | Fosc = 32 kHz             |

|                                 |                                        |                                                                                                                                                                                         | 22   | 30   | μΑ    | 3.0 | LP Oscillator mode        |

|                                 |                                        |                                                                                                                                                                                         | 33   | 60   | μΑ    | 5.0 |                           |

| D011*                           |                                        | _                                                                                                                                                                                       | 180  | 250  | μΑ    | 2.0 | Fosc = 1 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 290  | 400  | μΑ    | 3.0 | XT Oscillator mode        |

|                                 |                                        |                                                                                                                                                                                         | 490  | 650  | μΑ    | 5.0 |                           |

| D012                            |                                        | _                                                                                                                                                                                       | 280  | 380  | μΑ    | 2.0 | Fosc = 4 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 480  | 670  | μΑ    | 3.0 | XT Oscillator mode        |

|                                 |                                        |                                                                                                                                                                                         | 0.9  | 1.4  | mA    | 5.0 |                           |

| D013*                           |                                        |                                                                                                                                                                                         | 170  | 295  | μΑ    | 2.0 | Fosc = 1 MHz              |

|                                 |                                        | _                                                                                                                                                                                       | 280  | 480  | μΑ    | 3.0 | EC Oscillator mode        |

|                                 |                                        |                                                                                                                                                                                         | 470  | 690  | μΑ    | 5.0 |                           |

| D014                            |                                        |                                                                                                                                                                                         | 290  | 450  | μΑ    | 2.0 | Fosc = 4 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 490  | 720  | μΑ    | 3.0 | EC Oscillator mode        |

|                                 |                                        |                                                                                                                                                                                         | 0.85 | 1.3  | mA    | 5.0 |                           |

| D015                            |                                        |                                                                                                                                                                                         | 8    | 20   | μΑ    | 2.0 | Fosc = 31 kHz             |

|                                 |                                        |                                                                                                                                                                                         | 16   | 40   | μΑ    | 3.0 | LFINTOSC mode             |

|                                 |                                        |                                                                                                                                                                                         | 31   | 65   | μΑ    | 5.0 |                           |

| D016*                           |                                        |                                                                                                                                                                                         | 416  | 520  | μΑ    | 2.0 | Fosc = 4 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 640  | 840  | μΑ    | 3.0 | HFINTOSC mode             |

|                                 |                                        |                                                                                                                                                                                         | 1.13 | 1.6  | mA    | 5.0 |                           |

| D017                            |                                        |                                                                                                                                                                                         | 0.65 | 0.9  | mA    | 2.0 | Fosc = 8 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 1.01 | 1.3  | mA    | 3.0 | HFINTOSC mode             |

|                                 |                                        | —                                                                                                                                                                                       | 1.86 | 2.3  | mA    | 5.0 |                           |

| D018                            |                                        | _                                                                                                                                                                                       | 340  | 580  | μΑ    | 2.0 | Fosc = 4 MHz              |

|                                 |                                        |                                                                                                                                                                                         | 550  | 900  | μΑ    | 3.0 | EXTRC mode <sup>(3)</sup> |

|                                 |                                        |                                                                                                                                                                                         | 0.92 | 1.4  | mA    | 5.0 |                           |

| D019                            |                                        |                                                                                                                                                                                         | 3.8  | 4.7  | mA    | 4.5 | Fosc = 20 MHz             |

|                                 |                                        | _                                                                                                                                                                                       | 4.0  | 4.8  | mA    | 5.0 | HS Oscillator mode        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

### TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                                                |          |          |          |          |                                            |

|----------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------|----------|----------|----------|----------|--------------------------------------------|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                                                 | Min.     | Тур†     | Max.     | Units    | Conditions                                 |

| 30                                                                                                                   | ТмсL  | MCLR Pulse Width (low)                                         | 2<br>5   |          |          | μs<br>μs | VDD = 5V, -40°C to +85°C<br>VDD = 5V       |

| 31                                                                                                                   | Twdt  | Watchdog Timer Time-out<br>Period (No Prescaler)               | 10<br>10 | 16<br>16 | 29<br>31 | ms<br>ms | VDD = 5V, -40°C to +85°C<br>VDD = 5V       |

| 32                                                                                                                   | Tost  | Oscillation Start-up Timer<br>Period <sup>(1, 2)</sup>         | -        | 1024     | —        | Tosc     | (Note 3)                                   |

| 33*                                                                                                                  | TPWRT | Power-up Timer Period                                          | 40       | 65       | 140      | ms       |                                            |

| 34*                                                                                                                  | Tioz  | I/O High-impedance from<br>MCLR Low or Watchdog<br>Timer Reset | —        | —        | 2.0      | μs       |                                            |

| 35                                                                                                                   | VBOR  | Brown-out Reset Voltage                                        | 2.0      |          | 2.2      | V        | BOR4V bit = 0 (Note 4)                     |

|                                                                                                                      |       |                                                                | 3.6      | 4.0      | 4.4      | V        | BOR4V bit = 1, -40°C to +85°C<br>(Note 4)  |

|                                                                                                                      |       |                                                                | 3.6      | 4.0      | 4.5      | V        | BOR4V bit = 1, -40°C to +125°C<br>(Note 4) |

| 36*                                                                                                                  | VHYST | Brown-out Reset Hysteresis                                     | —        | 50       | —        | mV       |                                            |

| 37*                                                                                                                  | TBOR  | Brown-out Reset Minimum<br>Detection Period                    | 100      | —        | —        | μs       | $VDD \leq VBOR$                            |

<sup>t</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- 3: Period of the slower clock.

4: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

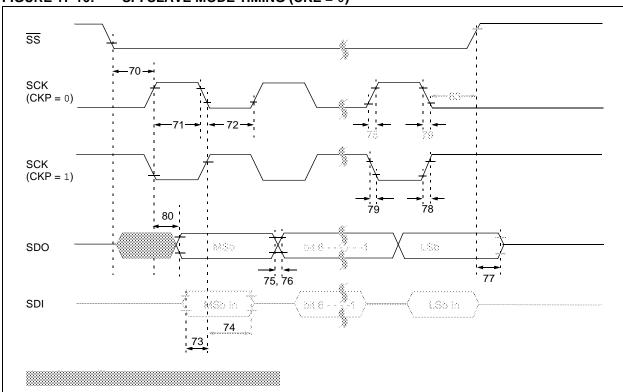

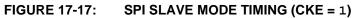

#### FIGURE 17-16: SPI SLAVE MODE TIMING (CKE = 0)

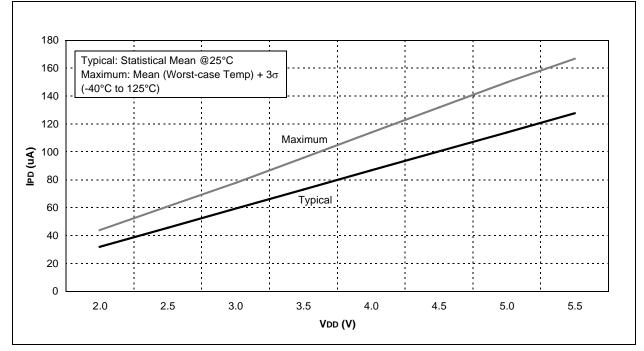

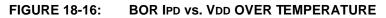

#### FIGURE 18-15: COMPARATOR IPD vs. VDD (BOTH COMPARATORS ENABLED)

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15